支持块体擦除操作的三维闪存器件及其制造方法

文献发布时间:2023-06-19 09:29:07

技术领域

本公开涉及三维闪存器件及制造三维闪存器件的方法,尤其涉及一种具有支持块体擦除操作的结构的三维闪存器件。

背景技术

闪存器件是电可擦除可编程只读存储器(EEPROM),因此可以普遍用于例如计算机、数码相机、MP3播放器、游戏系统、记忆棒等。这样的闪存器件通过福勒-诺德海姆隧穿(F-N隧穿)或热电子注入来电控制数据的输入和输出。

具体地,参考图1,图1示出现有的三维闪存的阵列,现有的三维闪存的阵列可以包括公共源极线CSL、位线BL以及在公共源极线CSL和位线BL之间的多个单元串CSTR。

位线是二维布置的,并且多个单元串CSTR与每条位线并联连接。单元串CSTR可以共同连接到公共源极线CSL。即,多个单元串CSTR可以布置在多条位线和一条公共源极线CSL之间。可以提供多条公共源极线CSL,并且可以是二维布置的。可以将电相等的电压施加到多条公共源极线CSL,或者可以电控制多条公共源极线CSL中的每条。

每个单元串CSTR可以包括连接到公共源极线CSL的接地选择晶体管GST,连接到位线BL的串选择晶体管SST,以及在接地选择晶体管GST和串选择晶体管SST之间的多个存储单元晶体管MCT。另外,接地选择晶体管GST、串选择晶体管SST和存储单元晶体管MCT可以串联连接。

公共源极线CSL可以共同连接到接地选择晶体管GST的源极。另外,可以将布置在公共源极线CSL和位线BL之间的接地选择线GSL、多条字线WL0至WL3和多条串选择线SSL分别用作接地选择晶体管GST、存储单元晶体管MCT和串选择晶体管SST的电极层。此外,每个存储单元晶体管MCT包括存储元件。

关于现有的三维闪存,为了实现消费者所需的优异性能和低价格,已通过竖直堆叠单元提高了集成度。

例如,参考图2,图2示出现有三维闪存的结构,在衬底200上布置电极结构215,在电极结构215中交替且重复地形成层间电介质211和水平结构250,以制造现有三维闪存。层间电介质211和水平结构250可以在第一方向上延伸。每个层间电介质211可以包括例如氧化硅膜,并且层间电介质211之中的最下面的层间电介质211a可以具有比其他层间电介质211的厚度小的厚度。每个水平结构250可以包括第一阻挡绝缘膜242和第二阻挡绝缘膜243以及电极层245。可以提供多个电极结构215,并且可以在第二方向上布置以彼此面对,第二方向与第一方向相交。在图2中,第一方向和第二方向可以分别对应于x轴和y轴。沟槽240可以在多个电极结构215之间沿第一方向延伸,以使多个电极结构215彼此分离。可以在由沟槽240暴露的衬底200中形成重掺杂杂质区,从而布置公共源极线CSL。尽管未示出,但是可以进一步布置隔离绝缘膜以填充沟槽240。

竖直结构230可以布置为穿过电极结构215。在示例中,在平面图中,竖直结构230可以在第一方向和第二方向上对齐,并且因此以矩阵形式布置。在另一示例中,竖直结构230可以在第二方向上对齐并且在第一方向上以之字形布置。每个竖直结构230可以包括保护膜224、电荷存储膜225、隧道绝缘膜226和沟道层227。例如,沟道层227可以具有内部为空的管状,在这种情况下,可以进一步布置填充膜228以填充沟道层227的内部。漏极区域D可以位于沟道层227上,并且导电图案229可以形成在漏极区域D上并且连接至位线BL。位线BL可以在与水平结构250相交的方向(例如第二方向)上延伸。在示例中,在第二方向上对齐的竖直结构230可以连接到一条位线BL。

水平结构250中的第一阻挡绝缘膜242和第二阻挡绝缘膜243以及竖直结构230中的电荷存储膜225和隧道绝缘膜226可以限定氧化物-氮化物-氧化物(ONO)层,其是三维闪存的信息存储元件。即,信息存储元件的一些部分可以包括在竖直结构230中,而其他部分可以包括在水平结构250中。作为示例,在信息存储元件中,电荷存储膜225和隧道绝缘膜226可以包括在竖直结构230中,并且第一阻挡绝缘膜242和第二阻挡绝缘膜243可以包括在水平结构250中。

外延图案222可以布置在衬底200和竖直结构230之间。外延图案222将衬底200连接到竖直结构230。外延图案222可以接触至少一个水平结构250。外延图案222可以被布置为接触最下面的水平结构250a。根据另一实施例,外延图案222可以被布置为接触多个水平结构250,例如,两个水平结构250。当外延图案222被布置为接触最下面的水平结构250a时,最下面的水平结构250a可以具有比其他水平结构250的厚度大的厚度。接触外延图案222的最下面的水平结构250a可以对应于参考图1描述的三维闪存的阵列的接地选择线GSL,与竖直结构230接触的其他水平结构250可以对应于多条字线WL0至WL3。

每个外延图案222具有凹入侧壁222a。因此,与外延图案222接触的最下面的水平结构250a沿着凹入侧壁222a的轮廓放置。即,最下面的水平结构250a可以沿着外延图案222的凹入侧壁222a以向内凸出的形状放置。

在具有这种结构的现有三维闪存中,随着竖直堆叠的层数增加,沟道层227的长度增加,导致单元电流的减小和单元特性的劣化。

为了增大三维闪存中随着沟道层长度的增加而减小的单元电流,并减小由于单元电流的减小而导致的单元特性的劣化,已经提出了在串的中间区域中布置至少一个中间布线层的结构。

然而,在具有布置了至少一个中间布线层的结构的三维闪存器件中,由于串中的沟道层因至少一个中间布线层而划分为上沟道层和下沟道层,所以难以应用基于衬底200的块体的擦除操作。

因此,本公开的以下实施例提出了一种用于在三维闪存器件中支持块体擦除操作的技术,所述三维闪存器件包括至少一个中间布线层以增大随着沟道层长度的增加而减小的单元电流,并减少由于单元电流减小而引起的单元特性劣化。

另外,当仅以与现有位线相同的形状实现中间布线层时,由于布线工艺的复杂度增加并且集成度降低,因此本公开的以下实施例提出了一种结构,包括通过简单的布线工艺制造的中间布线层,同时允许提高集成度。

发明内容

技术问题

本公开的实施例提供:一种三维闪存器件以及制造三维闪存器件的方法,三维闪存器件具有包括至少一个中间布线层的结构,所述中间布线层能够被重新配置以适应性地用作源电极和漏电极之一,并且三维闪存器件通过在至少一个中间布线层中形成将由至少一个中间布线层划分的至少两个沟道层彼此连接的至少一个连接件,来支持基于衬底的块体的块体擦除操作。

另外,本公开的实施例提供:一种三维闪存器件以及制造三维闪存器件的方法,三维闪存器件包括将上沟道层连接到下沟道层的沟道连接件、以及将沟道连接件连接到中间布线层的布线连接件,从而允许提高包括中间布线层的结构的集成度,并简化布线工艺。

此外,本公开的实施例提供:一种三维闪存器件以及制造三维闪存器件的方法,允许通过以倒阶梯状形成上布线层、至少一个中间布线层和下布线层为具有彼此不同的延伸长度,并因此分别连接到在单个衬底上同一条线上形成的插塞,来实现集成和尺寸减小。

解决问题的技术方案

根据本公开的一方面,一种三维闪存器件,包括:串,包括在一个方向上延伸的沟道层和相对于所述沟道层竖直堆叠的多个电极层;上布线层,布置在所述串上;至少一个中间布线层,在所述串的中间区域中穿过所述沟道层布置在所述多个电极层之间;下布线层,布置在所述串下面;以及至少一个连接件,布置在所述至少一个中间布线层中并且将至少两个沟道层彼此连接,至少两个沟道层由至少一个中间布线层划分。

根据本公开的实施例,至少一个连接件可以包括N-层和包围所述N-层并接触至少一个中间布线层的N+层。

根据本公开的另一实施例,至少一个连接件可以包括被至少一个中间布线层包围并接触的N-层。

根据本公开的又一个实施例,至少一个连接件可以包括被至少一个中间布线层包围并接触的N+层。

根据本公开的又一实施例,可以在包括P型块体和N+接触的衬底上制造三维闪存器件,并且当通过至少一个连接件彼此连接的至少两个沟道被连接到所述块体时可以支持块体擦除操作。

根据本公开的又一个实施例,至少一个连接件可以包括:在至少一个中间布线层下方沉积的N+层;以及布置在N+层上、并且被至少一个中间布线层包围和接触的N-层。

根据本公开的又一个实施例,至少一个连接件可以包括:在至少一个中间布线层下方沉积的N+层;以及被N+层和至少一个中间布线层两者包围并接触的N-层。

根据本公开的又一实施例,上布线层、至少一个中间布线层和下布线层可以形成倒阶梯形状,各层的延伸长度彼此不同。

根据本公开的又一实施例,上布线层、至少一个中间布线层和下布线层的相应延伸长度可以按上布线层、至少一个中间布线层和下布线层的顺序减小。

根据本公开的又一实施例,由于上布线层、至少一个中间布线层和下布线层形成的倒阶梯形状,上布线层、至少一个中间布线层和下布线层可以分别连接到单个衬底上同一条线上的插塞。

根据本公开的又一实施例,上布线层、至少一个中间布线层和下布线层中的每个可以被适应性地用作漏电极和源电极之一。

根据本公开的另一方面,一种制造三维闪存器件的方法包括:制备多个结构,每个结构包括包含多个电极层、多个层间电介质和沟道层的串,多个电极层和多个层间电介质交替地堆叠,并且沟道层在一个方向上延伸穿过多个电极层和多个层间电介质;通过蚀刻衬底的基层的至少部分来形成至少三个插塞孔;在至少三个插塞孔中的每个插塞孔中沉积金属插塞;形成下布线层以连接到至少三个金属插塞中的一个金属插塞;在下布线层上堆叠多个结构中的一个结构;在一个结构中形成连接插塞以在一个方向上延伸,连接插塞分别与至少三个金属插塞中除所述一个金属插塞之外的其余金属插塞连接;形成至少一个中间布线层,以连接到连接插塞中的一个连接插塞;在至少一个中间布线层上堆叠多个结构中除所述一个结构之外的其余结构中的一个其余结构;在所述一个其余结构中形成连接插塞以在一个方向上延伸,该连接插塞与其余的金属插塞中除连接至所述至少一个中间布线层的金属插塞以外的金属插塞连接;以及形成上布线层以连接到连接插塞中的一个连接插塞,其中,上布线层、至少一个中间布线层和下布线层形成倒阶梯形状,各层的延伸长度彼此不同。

根据本公开的实施例,上布线层、至少一个中间布线层和下布线层的相应延伸长度可以按上布线层、至少一个中间布线层和下布线层的顺序减小。

根据本公开的另一实施例,由于由上布线层、至少一个中间布线层和下布线层形成的倒阶梯形状,上布线层、至少一个中间布线层和下布线层可以分别连接到在衬底上的同一条线上形成的金属插塞。

根据本公开的又一实施例,形成至少一个中间布线层可以包括在至少一个中间布线层中形成至少一个连接件,至少一个连接件将包括在至少一个中间布线层下方的一个结构中的沟道层连接到包括在至少一个中间布线层上方的一个其余结构中的沟道层。

根据本公开的又一方面,一种三维闪存,包括:串,包括在一个方向上延伸的沟道层;沟道连接件,布置在所述串的中间区域中并且将所述串的上沟道层和下沟道层彼此连接;中间布线层,可选择性地用作所述串的源电极和漏电极之一;以及布线连接件,将沟道连接件连接到中间布线层,同时至少部分地掩埋在所述串中。

根据本公开的实施例,布线连接件可以包括N+型材料,并且沟道连接件可以包括金属材料和N-型材料中的一种。

根据本公开的另一个实施例,可以在包括P型块体和N+触点的衬底上制造三维闪存,并且当串的上沟道层和下沟道层通过沟道连接件连接到块体时可以支持块体擦除操作。

根据本公开的又一个实施例,中间布线层可以位于串和与所述串相邻的相邻串之间的空间中。

根据本公开的又一个实施例,中间布线层可以由串和与所述串相邻的相邻串共享。

根据本公开的又一方面,一种制造三维闪存的方法包括:形成下沟道层;在下沟道层的顶部区域的一部分上形成布线连接件;形成绝缘层以覆盖布线连接件;蚀刻绝缘层中与下沟道层的顶部区域中除形成所述布线连接件的部分之外的其余部分相对应的部分,以及绝缘层中与布线连接件的顶部区域的部分相对应的部分;在通过蚀刻绝缘层中与布线连接件的顶部区域的部分相对应的部分而得到的空间中形成中间布线层;在通过蚀刻绝缘层中与下沟道层的顶部区域中除形成布线连接件的部分之外的其余部分相对应的部分而得到的空间中形成沟道连接件;以及在沟道连接件上形成上沟道层,其中,中间布线层能够选择性地用作包括上沟道层和下沟道层的串的源电极和漏电极之一。

根据本公开的实施例,形成布线连接件可以包括在串和与所述串相邻的相邻串之间的空间中形成布线连接件。

根据本公开的另一实施例,中间布线层可以由串和与所述串相邻的相邻串共享。

本公开的有益效果

根据本公开的实施例,可以提供一种三维闪存器件以及制造三维闪存器件的方法,三维闪存器件具有包括至少一个中间布线层的结构,中间布线层能够被重新配置以适应性地用作源电极和漏电极之一,并且通过在至少一个中间布线层中形成将由至少一个中间布线层划分的至少两个沟道层彼此连接的至少一个连接件,允许支持基于衬底的块体的块体擦除操作。

另外,根据本公开的实施例,可以提供一种三维闪存器件以及制造三维闪存器件的方法,三维闪存器件包括将上沟道层连接到下沟道层的沟道连接件和将沟道连接件连接到中间布线层的布线连接件,从而允许提高包括中间布线层的结构的集成度,并且可以简化布线工艺。

因此,根据本公开的实施例,可以在解决现有的三维闪存器件的缺点(例如,单元电流的减小和单元特性的劣化)的同时,支持块体擦除操作,并且实现集成度的提高和布线工艺的简化。

此外,根据本公开的实施例,可以提供一种三维闪存器件以及制造三维闪存器件的方法,其允许通过以倒阶梯状形成上布线层、至少一个中间布线层和下布线层为具有彼此不同的延伸长度,从而分别连接到形成在单个衬底上同一条线上的插塞,来实现集成和尺寸减小。

附图说明

图1是示出现有三维闪存的阵列的示意性电路图。

图2是示出现有三维闪存的结构的透视图。

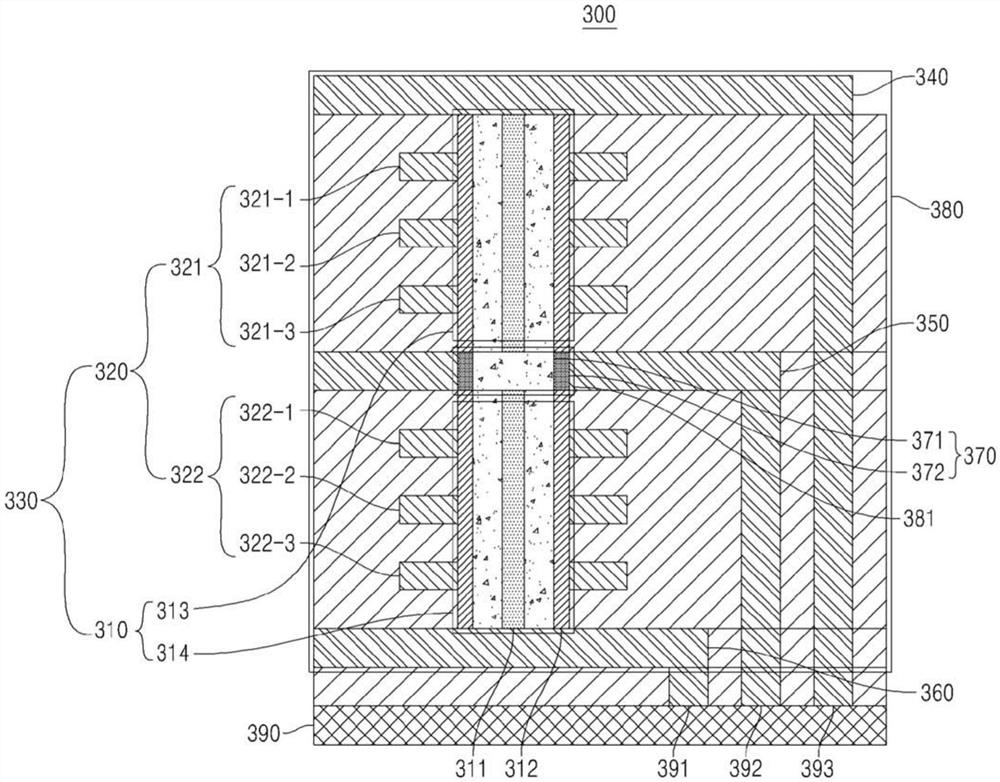

图3是示出根据本公开实施例的支持块体擦除操作的三维闪存器件的截面图。

图4示出了图3的支持块体擦除操作的三维闪存器件的区域380的底视图。

图5示出了图3的支持块体擦除操作的三维闪存器件的区域381的截面图。

图6是示出根据本公开另一实施例的支持块体擦除操作的三维闪存器件的截面图。

图7示出了图6的支持块体擦除操作的三维闪存器件的区域630的截面图。

图8是示出根据本公开又一实施例的支持块体擦除操作的三维闪存器件的截面图。

图9示出了图8的支持块体擦除操作的三维闪存器件的区域830的截面图。

图10a和图10b是各自示出根据本公开实施例的在支持块体擦除操作的三维闪存器件中形成至少一个中间布线层的图案的图。

图11a至图11e是示出根据本公开实施例的支持GIDL擦除操作的三维闪存器件的截面图。

图12是示出根据本公开实施例的制造三维闪存器件的方法的流程图。

图13至图22是示出根据本公开实施例的制造三维闪存器件的方法的图。

图23至图27是示出根据本公开实施例的制造三维闪存器件的方法中形成至少一个连接件的工艺的详细过程的图。

图28是示出根据本公开实施例的三维闪存的顶视图。

图29是沿着X轴截取的图28的三维闪存的截面图。

图30是沿着Y轴截取的图28的三维闪存的截面图。

图31是根据本公开另一实施例的图28的三维闪存的截面图。

图32是根据本公开又一实施例的图28的三维闪存的截面图。

图33是示出根据本公开实施例的制造三维闪存的方法的流程图。

图34至图39是示出根据本公开实施例的制造三维闪存的方法的截面图。

图40至图45是示出根据本公开另一实施例的制造三维闪存的方法的图。

图46至图53是示出根据本公开又一实施例的制造三维闪存的方法的图。

图54是示出根据本公开另一实施例的三维闪存的顶视图。

图55是沿着X轴截取的图54的三维闪存的截面图。

图56是根据本公开另一实施例的图54的三维闪存的截面图。

图57是根据本公开又一实施例的图54的三维闪存的截面图。

具体实施方式

在下文中,将参考附图详细描述本公开的实施例。然而,本公开不限于本文描述的实施例。另外,在整个说明书中,相似的组件将由相似的附图标记表示。

此外,本文中使用的术语仅出于适当描述本公开的实施例的目的,并且可以根据用户、操作者的意图、本领域的习惯等而变化。因此,本文中使用的术语应基于整个说明书中的描述来定义。

图3是示出根据本公开实施例的支持块体擦除操作的三维闪存器件的截面图,图4示出图3的支持块体擦除操作的三维闪存器件的区域380的底视图,图5示出了图3的支持块体擦除操作的三维闪存器件的区域381的截面图。

参考图3,根据本公开的实施例,支持块体擦除操作的三维闪存器件300包括串330,串330包括沟道层310和相对于沟道层310竖直堆叠的多个电极层320、上布线层340、至少一个中间布线层350、下布线层360和至少一个连接件370。

在下文中,尽管将支持块体擦除操作的三维闪存器件300描述为包括上述组件,但本公开不限于此,并且三维闪存器件300还可包括将沟道层310连接到多个电极层320的电荷存储层(未示出),以及与多个电极层320交替布置并且相对于沟道层310竖直堆叠的多个层间电介质(未示出)。即,三维闪存器件300可以具有进一步包括参考图2描述的现有组件的结构。

沟道层310沿一个方向延伸。例如,沟道层310可以在参考图2描述的z轴方向上延伸。沟道层310可以具有内部为空的管状,并且在这种情况下,填充膜311可以进一步布置为填充沟道层310的内部,并且侧壁312可以进一步布置为包围沟道层310的外部。

多个电极层320相对于沟道层310竖直地堆叠。多个电极层320可以在参考图2描述的x轴方向上延伸。

这里,多个电极层320可以被分组为由至少一个中间布线层350划分的至少两个块321和322。例如,第一电极层321-1、第二电极层321-2、第三电极层321-3可被分组为第一块321,并且第四电极层322-1、第五电极层322-2和第六电极层322-3可被分组为第二块322。

上布线层340布置在串330(更具体地,沟道层310)上面。这里,上布线层340可以在垂直于多个电极层320的延伸方向的方向(在平面图中垂直于多个电极层320的延伸方向的方向)上延伸。即,上布线层340可以在参考图2描述的y轴方向上延伸。

在串330的中间区域中,至少一个中间布线层350穿过沟道层310被布置在多个电极层320之间。这里,至少一个中间布线层350可以在垂直于多个电极层320的延伸方向的方向(在平面图中垂直于多个电极层320的延伸方向的方向)上延伸。例如,至少一个中间布线层350可以在平面图中,在垂直于多个电极层320的延伸方向(参考图2描述的x轴方向)的方向(参考图2描述的y轴方向)上延伸。将参考图10a和图10b详细描述形成至少一个中间布线层350的图案。

下布线层360布置在串330(更具体地,沟道层310)下方。这里,下布线层360可以在垂直于多个电极层320的延伸方向的方向上(在平面图中垂直于多个电极层320的延伸方向的方向上)延伸。即,下布线层360可以在参考图2描述的y轴方向上延伸。

具有这样结构的上布线层340、至少一个中间布线层350和下布线层360中的每个可以适应性地用作三维闪存器件300中的漏电极和源电极之一。这里,用作漏电极是指用作图1所示的位线BL,并且将布线层(例如340、350或360)用作漏电极(或源电极)的这种陈述可以表示将布线层340、350或360本身用作漏电极(或源电极),也可以表示将直接连接至布线层340、350或360的电极层用作漏电极(或源电极)。

例如,当上布线层340用作源电极时,最接近上布线层340、同时在由至少一个中间布线层350和上布线层340控制的存储单元置于两者之间的至少一个中间布线层350可以用作漏电极,并且当上布线层340用作漏电极时,最接近上布线层340、同时在由至少一个中间布线层350和上布线层340控制的存储单元置于两者之间的至少一个中间布线层350可以用作源电极。在下文中,存储单元是指电荷存储层,其是三维闪存件300中的信息存储元件,并且是指与电荷存储层直接接触的电极层。因为根据本公开实施例的三维闪存器件300包括多个电极层320,所以三维闪存器件300可以包括与多个电极层320对应的多个电荷存储层,并且因此包括包含成对的多个电极层320和多个电荷存储层的多个存储单元。

作为另一示例,当至少一个中间布线层350由包括第一中间布线层、第二中间布线层和第三中间布线层(在该示例中以所述顺序依次布置)的多个中间布线层350实现时,第一中间布线层可以用作漏电极,并且因此最接近第一中间布线层、同时由第一中间布线层和第二中间布线层控制的存储单元置于两者之间的第二中间布线层可以用作源电极。另外,第三中间布线层可以用作源电极,并且因此最接近第三中间布线层、同时由第三中间布线层和第二中间布线层控制的存储单元置于两者之间的第二中间布线层可以用作漏电极。这样,根据与第二中间布线层相邻的另一中间布线层是用作漏电极还是源电极,第二中间布线层可以用作源电极或漏电极。

即,上布线层340、至少一个中间布线层350和下布线层360中的每个,当与其相邻并在两者之间放置要被控制的存储单元的另一布线层用作漏电极和源电极之一时,布线层340、至少一个中间布线层350和下布线层360中的每个可以被适应性地用作除另一布线层用作的那种电极之外的另一电极。在下文中,根据情况使用一个布线层作为漏电极或源电极是指以可重新配置的方式形成相应的布线层,使得相应的布线层能够被适应性地用作源电极和漏电极之一。因此,可以以可重新配置的方式形成上布线层340、至少一个中间布线层350和下布线层360。

这里,上布线层340、至少一个中间布线层350和下布线层360可以被设置为对应于多个电极层320分组到的至少两个块321和322中的每个块。例如,上布线层340和至少一个中间布线层350可以被设置为对应于第一电极层321-1、第二电极层321-2和第三电极321-3分组到的第一块321,并且可以用作第一块321(第一电极层321-1、第二电极层321-2和第三电极层321-3)的漏电极或源电极;并且至少一个中间布线层350和下布线层360可以被设置为对应于第四电极层322-1、第五电极层322-2和第六电极层322-3分组到的第二块322,并且可以用作第二块322(第四电极层322-1、第五电极层322-2和第六电极层322-3)的漏电极或源电极。因此,三维闪存器件300可以选择并使用上布线层340、至少一个中间布线层350和下布线层360之一作为漏电极或源电极,从而选择性地编程、擦除并读取与使用相应布线层的电极层之一相对应的电荷存储层。在下文中,尽管描述了设置一个中间布线层350的示例,但是本公开不限于此,并且可以设置多个中间布线层350,即,两个或更多个中间布线层350。在这种情况下,同样地,多个中间布线层350中的每个可以布置在多个电极层320之间。

因此,与在沟道层上仅包括一个漏电极的现有三维闪存器件相比,根据本公开实施例的三维闪存器件300可以减小单元电流并改善单元特性的劣化。

另外,上布线层340、至少一个中间布线层350和下布线层360的延伸长度可以彼此不同。例如,参考图4,图4示出区域380的底视图(为了便于描述,除其他组件之外,图4仅示出了上布线层340、至少一个中间布线层350和下布线层360),上布线层340、至少一个中间布线层350和下布线层360可以依次且分别具有朝向三维闪存器件300的底部而减小的延伸长度。因此,在侧视图中,上布线层340、至少一个中间布线层350和下布线层360可以形成具有依次减小的阶梯长度的倒阶梯形状。

另外,即使设置多个中间布线层350,同样地,多个中间布线层350也可以依次且分别具有朝向三维闪存器件300的底部而减小的延伸长度。

由于这种倒阶梯状形状,上布线层340、至少一个中间布线层350和下布线层360可以分别连接到形成在单个衬底390上的同一条线上的插塞393、392和391,并且因此,三维闪存器件300可以实现集成和尺寸减小,并且可以降低布线工艺的复杂度。

上布线层340、至少一个中间布线层350和下布线层360可以各自包括钨(W)、钛(Ti)、钽(Ta)、铜(Cu)或金(Au)中的至少一种。然而,本公开不限于此,并且上布线层340、至少一个中间布线层350和下布线层360可以各自包括金属材料、导电非金属材料或金属材料和非金属材料的混合物。

至少一个连接件370形成在至少一个中间布线层350中,并且可以将由至少一个中间布线层350划分的至少两个沟道层313和314彼此连接。例如,至少一个连接件370可以在被至少一个中间布线层350包围的同时将至少两个沟道层313和314彼此连接。作为更具体的示例,参考图5,图5示出了区域381的截面图,至少一个连接件370可以包括N-层371以及包围N-层371并与至少一个中间布线层350接触的N+层372。这里,可以通过将N-型离子注入到与沟道层310相同的材料中的工艺来形成N-层371,并且可以通过将N+型离子注入到与沟道层310相同的材料中的工艺来形成N+层372。

然而,本公开不限于此,并且至少一个连接件370可以以各种结构形成。将参考图7至9对此进行详细描述。

因此,在包括P型块体和N+接触的衬底390上制造的三维闪存器件300可通过经由至少一个连接件370将至少两个沟道层313和314连接到块体来支持基于块体的擦除操作。这里,由于基于块体的擦除操作是根据现有技术的技术,因此将省略其描述。

至此,尽管已经描述了包括一个串330的三维闪存器件300,但是三维闪存器件300可以包括多个串330,每个串具有上述结构。

图6是示出根据本公开另一实施例的支持块体擦除操作的三维闪存器件的截面图,并且图7示出图6的支持块体擦除操作的三维闪存器件的区域630的截面图。

参考图6和图7,虽然根据本公开另一实施例的支持块体擦除操作的三维闪存器件600具有与参考图3和图4描述的三维闪存器件300相同的结构,但是至少一个连接件610具有不同的结构。

例如,在根据本公开另一实施例的三维闪存器件600中,至少一个连接件610可以包括被至少一个中间布线层620包围并接触的N+层。N+层可以通过将N+型离子注入到与沟道层相同的材料中的工艺来形成。

图8是示出根据本公开又一实施例的支持块体擦除操作的三维闪存器件的截面图,并且图9示出图8的支持块体擦除操作的三维闪存器件的区域830的截面图。

参考图8和图9,虽然根据本公开又一实施例,支持块体擦除操作的三维闪存器件800具有与参考图3和图4描述的三维闪存器件300相同的结构,但是至少一个连接件810具有不同的结构。

例如,在根据本公开又一实施例的三维闪存器件800中,至少一个连接件810可以包括被至少一个中间布线层820包围并接触的N-层。可以通过将N-型离子注入到与沟道层相同的材料中的工艺来形成N-层。

至此,在参考图3至图9描述的三维闪存器件300、600和800中,擦除电压V

[表1]

图10a和图10b是各自示出根据本公开实施例的在支持块体擦除操作的三维闪存器件中形成至少一个中间布线层的图案的图。

参考图10a和图10b,在支持块体擦除操作的三维闪存器件中,可以根据连接到三维闪存器件的位线的形状来确定其中形成至少一个中间布线层1020的图案。更具体地,可以在根据连接到与至少一个中间布线层1020相对应的串的位线的形状的图案中形成至少一个中间布线层1020。

例如,如图10a所示的顶视图,当位线1010形成为内部被填充的单条线时,可以根据位线1010的形状将至少一个中间布线层1020形成为内部被填充的单条线。

作为另一示例,如图10b所示的顶视图,当位线1010形成为在其间具有空的空间的两条线时,可以根据位线1010的形状将至少一个中间布线层1020形成为在其间具有空的空间的两条线。

至此,尽管已经描述了支持块体擦除操作的三维闪存器件,但是至少一个连接件也可以被实现为支持基于栅极感应漏极泄漏(GIDL)的擦除操作,而不是块体擦除操作。这将在下面详细描述。

图11a至图11e是示出根据本公开实施例的支持GIDL擦除操作的三维闪存器件的截面图。

参考图11a至图11e,尽管支持基于GIDL的擦除操作的三维闪存器件1100具有与参考图3描述的三维闪存器件300相同的结构和组件,但是至少一个连接件1110具有不同的结构。

例如,如图11a所示,至少一个连接件1110可以形成为一种结构,该结构包括沉积在至少一个中间布线层1120下方的N+层1111,以及布置在N+层1111上并与至少一个中间布线层1120接触同时被至少一个中间布线层1120包围的N-层1112。像沟道层一样,N-层1112可以包括填充N-层1112的内部的填充膜和包围N-层1112的外部的侧壁。作为更具体的示例,如图11a所示,尽管N-层1112可以包括填充N-层1112的内部的填充膜和包围N-层1112的外部的侧壁(例如,ONO层)两者,但是本公开不限于此,也可以如图11b所示,N-层1112可以仅包括填充N-层1112的内部的填充膜。在这种情况下,侧壁可以形成为仅达到至少一个中间布线层1120的顶部。

作为另一示例,如图11c所示,至少一个连接件1110可以形成为一种结构,该结构包括沉积在至少一个中间布线层1120下方的N+层1111,以及被N+层1111和至少一个中间布线层1120包围并接触的N-层1112的结构。与沟道层一样,N-层1112可以包括填充N-层1112的内部的填充膜和包围N-层1112的外部的侧壁。作为更具体的示例,如图11c所示,尽管N-层1112可以包括填充N-层1112的内部的填充膜和包围N-层1112的外部的侧壁(例如,ONO层),但本公开不限于此,并且N-层1112可以仅包括填充N-层1112的内部的填充膜。在这种情况下,侧壁可以仅向下形成到N+层1111的顶部,如图11d所示,或可以仅向下形成到至少一个中间布线层1120的顶部,如图11e所示。

即,在N-层1112接触N+层1111的条件下,可以以各种结构形成参考图11a至图11e描述的至少一个连接件1110。

这里,当提供在至少一个中间布线层120上沉积有N+层1111的现有结构时,必须要执行使用退火的热处理工艺,因此,可能存在至少一个中间布线层1120劣化或受损的问题。因此,根据本公开实施例的三维闪存器件1100可以在上述结构中实现至少一个连接件1110和至少一个中间布线层1120,从而防止至少一个中间布线层1120的劣化或受损。

包括至少一个连接件1110的三维闪存器件1100可以支持基于GIDL的擦除操作,而不是基于块体的擦除操作。更具体地,三维闪存器件1100可以通过将擦除电压V

[表2]

图12是示出根据本公开实施例的制造三维闪存器件的方法的流程图,并且图13至图22是示出根据本公开实施例的制造三维闪存器件的方法的图。

参考图12至图22,根据本公开实施例的制造三维闪存器件的方法由三维闪存制造系统(下文称为制造系统)执行,以及通过该制造方法制造的三维闪存器件具有参考图3、图6或图8描述的结构或参考图11a至图11d描述的结构。

首先,制造系统准备多个结构,每个结构包括串,所述串包括交替堆叠的多个电极层和多个层间电介质,以及沿一个方向延伸穿过多个电极层和多个层间电介质的沟道层(1205)。例如,由制造系统,在如图13所示,将多个电极层1311-1和1321-1以及多个层间电介质1311-2和1321-2交替地堆叠以在一个方向(参考图2描述的x轴方向)上延伸之后,形成串孔以在一个方向(参考图2描述的z轴方向)上延伸穿过交替堆叠的多个电极层1311-1和1321-1以及多个层间电介质1311-2和1321-2,并且在串孔中形成沟道层1311-3和1321-3,从而制造并准备分别包括其中形成的串1311和1321的多个结构1310和1320。

接着,如图14所示,由制造系统,通过至少部分地蚀刻衬底1400的基层1410来形成至少三个插塞孔1411、1412和1413(1210)。这里,由制造系统,可以在衬底1400上的同一条线上形成至少三个插塞孔1411、1412和1413。

接着,如图15所示,由制造系统,将金属插塞1510、1520和1530分别沉积在至少三个插塞孔1411、1412和1413中(1215)。这里,由于至少三个插塞孔1411、1412和1413形成在衬底1400上的同一条线上,因此沉积在至少三个插塞孔1411、1412和1413中的金属插塞1510、1520和1530是也位于衬底1400上的同一条线上。

接着,由制造系统将下布线层形成为连接到至少三个金属插塞1510、1520和1530之一(1220)。例如,由制造系统,可以将下布线层1610形成为在一个方向(参考图2描述的y轴方向)上延伸以连接至第一金属插塞1510、第二金属插塞1520和第三金属插塞1530中的第一金属插塞1510,如图16所示。

接着,由制造系统,将多个结构1310和1320中的一个结构1310堆叠在下布线层1610上(1225)。例如,由制造系统,可以将如图13所示准备的多个结构1310和1320中的第一结构1310堆叠在下布线层1610上,如图17所示。

接着,由制造系统,在堆叠在下布线层1610上的一个结构1310中形成连接插塞,以沿一个方向延伸,连接插塞分别连接到至少三个金属插塞1510、1520和1530中除一个金属插塞1510之外的其余金属插塞1520和1530(1230)。例如,由制造系统,可以将连接插塞1810和1820形成在第一结构1310中以在一个方向(参考图2描述的z轴方向)上延伸,连接插塞1810和1820分别连接到第一金属插塞1510、第二金属插塞1520和第三金属插塞1530中除了连接到下布线层1610的第一金属插塞1510之外的其余金属插塞1520和1530,如图18所示。

接着,由制造系统,形成至少一个中间布线层以连接到连接插塞1810和1820中的一个连接插塞1810(1235)。例如,由制造系统,可以将至少一个中间布线层1910形成为在一个方向(参考图2描述的y轴方向)上延伸以连接到第一连接插塞1810和第二连接插塞1820中的第一连接插塞1810,如图19所示。

这里,在操作1235中,由制造系统,可以在至少一个中间布线层1910中形成至少一个连接件。具体地,由制造系统,可以在至少一个中间布线层1910中形成至少一个连接件1911,至少一个连接件1911将包括在位于至少一个中间布线层1910下方的一个结构1310中的沟道层1311-3连接到包括在位于至少一个中间布线层1910上方的其余一个结构1320中的沟道层1321-3。

特别地,根据在操作1235中由制造系统在至少一个中间布线层1910中形成的至少一个连接件的结构,可以允许所制造的三维闪存器件支持基于块体的擦除操作和基于GIDL的擦除操作之一。将参考图23至图27对此进行详细描述。

另外,在操作1235中,由制造系统,可以在根据连接到串的位线的形状的图案中形成至少一个中间布线层1910。

接着,由制造系统,将多个结构1310和1320中除堆叠在下布线层1610上的结构1310之外的其余一个结构1320堆叠在至少一个中间布线层1910上(1240)。例如,由制造系统,可以将如图13所示准备的多个结构1310和1320中的第二结构1320堆叠在至少一个中间布线层1910上,如图20所示。

接着,由制造系统,在堆叠在至少一个中间布线层1910上的其余一个结构1320中形成连接插塞,以在一个方向上延伸,该连接插塞连接至其余的金属插塞1520和1530中除了连接到至少一个中间布线层1910的金属插塞1520之外的金属插塞1530。例如,由制造系统,可以将连接插塞2110形成为沿一个方向延伸(参考图2描述的z轴方向),连接插塞2110连接到第二金属插塞1520和第三金属插塞1530中除了连接到至少一个中间布线层1910的第二金属插塞1520以外的第三金属插塞1530,如图21所示。

接着,由制造系统将上布线层形成为连接至连接插塞2110(1250)。例如,由制造系统,可以将上布线层2210形成为在一个方向(参考图2描述的y轴方向)上延伸以连接到连接插塞2110,如图22所示。

特别地,通过将操作1220中的下布线层1610、操作1235中的至少一个中间布线层1910和操作1250中的上布线层2210形成为彼此不同的延伸长度,制造系统可以允许下布线层1610、至少一个中间布线层1910和上布线层2210形成倒阶梯形状。作为示例,制造系统可以通过将下布线层1610形成为最小延伸长度,将至少一个中间布线层1910形成为次最小延伸长度,并且将上布线层2210形成为最大延伸长度,允许上布线层2210、至少一个中间布线层1910和下布线层1610按照前述的顺序分别具有减小的延伸长度。

由于呈倒阶梯形状,上布线层2210、至少一个中间布线层1910和下布线层1610分别连接至形成在单个衬底1400上的相同线上的插塞1413、1412和1411,这样,如上所述,所制造的三维快闪存储器件可以被集成并减小尺寸,并且可以通过具有极低复杂度的简单布线工艺来制造。

至此,尽管已经描述了制造包括一个中间布线层1910的三维闪存器件的方法,但是即使三维闪存器件包括多个中间布线层1910,也可以基于上述操作来制造三维闪存器件。

图23至图27是示出根据本公开实施例的在制造三维闪存器件的方法中形成至少一个连接件的工艺的详细过程的图。

制造系统可以通过以下示例中的详细过程执行在至少一个中间布线层1910中形成至少一个连接件1911的工艺。然而,至少一个连接件1911的制造工艺不限于以下示例,并且可以通过各种工艺来执行,该各种工艺允许至少一个连接件1911具有用于将沟道层1311-3连接到沟道层1321-3的结构,同时至少一个连接件1911布置在至少一个中间布线层1910中,沟道层1311-3被包括在位于至少一个中间布线层1910下方的一个结构1310中,并且沟道层3121-3被包括在位于至少一个中间布线层1910上的其余一个结构1320中。这种结构由于至少一个连接件1911而允许支持基于块体的擦除操作,并且将参考图23至图26进行说明。

作为示例,参考图23,由制造系统,在蚀刻至少一个中间布线层1910的与包括在至少一个中间布线层1910下方的一个结构1310中的沟道层1311-3接触的区域1912之后,可以在蚀刻后的区域1912中形成至少一个连接件1911,其包括N-层1911-1以及包围N-层1911-1并接触至少一个中间布线层1910的N+层1911-2。

作为另一示例,参考图24,由制造系统,在蚀刻至少一个中间布线层1910的与包括在至少一个中间布线层1910下方的一个结构1310中的沟道层1311-3接触的区域1912之后,可以在蚀刻后的区域1912中形成至少一个连接件1911,其包括被至少一个中间布线层1910包围并接触的N-层。

作为又一示例,参考图25,由制造系统,在蚀刻至少一个中间布线层1910的与包括在至少一个中间布线层1910下方的一个结构1310中的沟道层1311-3接触的区域1912之后,可以在蚀刻后的区域1912中形成至少一个连接件1911,其包括被至少一个中间布线层1910包围并接触的N+层。

另一方面,以下参考图26和图27描述的至少一个连接件2610可以以允许三维闪存器件支持基于GIDL的擦除操作的结构来制造,如以下示例所述。

作为示例,参考图26,由制造系统,在形成其下沉积有N+层2611的至少一个中间布线层1910之后,蚀刻至少一个中间布线层1910的与至少一个中间布线层1910下方的一个结构1310中包括的沟道层1311-3接触的区域1912,然后,在蚀刻后的区域1912中形成被至少一个中间布线层1910包围并接触的N-层2612,从而形成至少一个连接件2610。

作为另一示例,如图27所示,由制造系统,在形成其下沉积有N+层2711的至少一个中间布线层1910之后,蚀刻至少一个中间布线层1910和N+层2711中与包括在至少一个中间布线层1910下方的一个结构1310中的沟道层1311-3对应的相应区域1912和1913,然后,在刻蚀后的区域1912和1913中形成被N+层2711和至少一个中间布线层1910两者包围并接触的N-层2712,从而形成至少一个连接件2710。

因此,由于以这种结构形成的至少一个连接件2610或2710,三维闪存器件可以支持基于GIDL的擦除操作。

图28是示出根据本公开实施例的三维闪存的顶视图,图29是沿X轴截取的图28的三维闪存器件的截面图,图30是沿Y轴截取的图28的三维闪存器件的截面图。更具体地,图28是示出三维闪存中的串的竖直中间区域的水平截面的顶视图。

参考图28至图30,三维闪存2800包括在一个方向上延伸的串2810、沟道连接件2820、中间布线层2830和布线连接件2840。

尽管串2810被描述并示出为包括沿一个方向延伸的沟道层2811和2812,但是本公开不限于此,串2810可以包括相对于沟道层2811和2812竖直堆叠的多个电极层(未示出),并且除了沟道层2811和2812之外,还在多个电极层之间分别布置多个绝缘层(未示出)。

沟道连接件2820在串2810的中间区域中将上沟道层2811连接到下沟道层2812。例如,类似于沟道层2811和2812,沟道连接件2820可以通过N-型离子的注入工艺而包括N-型材料(例如,N-型多晶硅)。然而,本公开不限于此,并且沟道连接件2820可以包括金属材料。将参考图31对此进行详细描述。这样,由于沟道连接件2820在串2810的中间区域中将上沟道层2811连接到下沟道层2812,因此上沟道层2811和下沟道层2812连接到包括P型块体和N+接触的衬底,因此可以执行基于块体的擦除操作。

中间布线层2830可以包括金属材料(例如,钨(W),钛(Ti),钽(Ta),铜(Cu)或金(Au)),使得中间布线层2830能够选择性地用作串2810的源电极或漏电极。更具体地,当三维闪存2800中包括的上布线层(未示出)用作源电极时,可以将最接近上布线层、同时由中间布线层2830和上布线层两者控制的存储单元置于其间的中间布线层2830用作漏电极,并且当上布线层用作漏电极时,可以将最接近上布线层、同时由中间布线层2830和上布线层两者控制的存储单元置于其间的中间布线层2830用作源电极。在下文中,存储单元是指电荷存储层,其是三维闪存器件2800中的信息存储元件,并且是指与电荷存储层直接接触的电极层。

这里,中间布线层2830可以被实现为多个中间布线层2830。例如,当中间布线层2830被实现为包括第一中间布线层、第二中间布线层和第三中间布线层(其中第一中间布线层、第二中间布线层和第三中间布线层按照前述顺序竖直布置)的多个中间布线层2830时,第一中间布线层可以用作漏电极,因此,可以将最接近第一中间布线层、同时由第一中间布线层和第二中间布线层两者控制的存储单元置于两者之间的第二中间布线层用作源电极。另外,第三中间布线层可以用作源电极,因此可以将最接近第三中间布线层、同时由第三中间布线层和第二中间布线层两者控制的存储单元置于两者之间的第二中间布线层可以用作漏电极。即,响应于将与中间布线层2830相邻的另一布线层用作源电极和漏电极之一,同时由另一布线层和中间布线层2830两者控制的存储单元置于两者其间,可以将中间布线层2830适应性地用作除在用的一个电极以外的其余一个电极。在下文中,根据情况使用一个布线层作为漏电极或源电极是指以可重新配置的方式形成相应的布线层,使得相应的布线层能够适应性地用作源电极和漏电极之一。因此,可以以可重新配置的方式形成中间布线层2830。

特别地,中间布线层2830位于串之间的空间中,从而允许三维闪存2800被集成并减小尺寸。例如,中间布线层2830可以位于第一串2810和第二串2850之间的空间中,并且因此在串2810和2850之间共享,第二串2850是与第一串2810相邻的相邻串。此外,共享中间布线层2830的串2810和2850可以是三维闪存2800中包括的多个串中的彼此对角相邻的串2810和2850。

在下文中,在串2810和串2850之间共享中间布线层2830的表述是指,中间布线层2830被选择性地用作第一串2810的源电极和漏电极之一,同时被选择性地用作第二串2850的源电极和漏电极之一。为此,中间布线层2830可以连接到第一串2810的沟道连接件2820,并且同时连接到第二串2850的沟道连接件(未示出)。

布线连接件2840将沟道连接件2820连接至中间布线层2830,同时至少部分地掩埋在串2810中。例如,通过N+型离子的注入工艺,布线连接件2840可以由N+型材料(例如,N+型多晶硅)形成以被至少部分地掩埋在串2810中。

至此,尽管已经基于一个串2810描述了三维闪存2800的结构,但是本公开不限于此,并且根据本公开实施例的三维闪存2800可以具有基于共享中间布线层2830的多个串2810和2850的结构。在这种情况下,三维闪存2800可以被描述为具有包括以下的结构:多个串中的对角相邻的串2810和2850;将对角相邻的串2810和2850中的每个的上沟道层2811连接到下沟道层2812的沟道连接件2820;由对角相邻的串2810和2850共享的并且能够选择性地用作对角相邻的串2810和2850中的每个的源电极和漏电极之一的中间布线层2830;以及,将每个对角相邻的串2810和2850的沟道连接件2820和中间布线层2830彼此连接,同时至少部分地掩埋在每个对角相邻的串2810和2850中的布线连接件2840。当共享中间布线层2830的串不是对角相邻的串2810和2850而是水平相邻的串时,三维闪存2800可以具有基于水平相邻的串的结构。将参考图54至57对此进行详细描述。

这样,三维闪存2800在相邻的串2810和2850之间包括中间布线层2830,中间布线层2830能够选择性地用作源电极和漏电极之一,同时三维闪存2800包括串2810和2850中的将上沟道层2811连接到下沟道层2812的沟道连接件2820,由此,可以增大随着沟道层2811和2812的长度增加而减小的单元电流,可以改善由于单元电流的减小而引起的单元特性的劣化,可以支持基于衬底的块体的块体擦除操作,并且可以实现集成度的提高和布线工艺的简化。

图31是根据本公开另一实施例的图28的三维闪存的截面图。

参考图31,尽管根据本公开另一实施例的三维闪存3100具有与参考图28至30描述的三维闪存2800相同的结构,但是不同之处在于沟道连接件3110包括金属材料。更具体地,根据本公开另一实施例的包括在三维闪存3100中的沟道连接件3110可以包括与中间布线层3120相同的金属材料(例如,钨(W)、钛(Ti)、钽(Ta)、铜(Cu)或金(Au)中的至少一种)。

如上所述制造的根据本公开另一实施例的三维闪存3100与根据本公开实施例的三维闪存2800在构成沟道连接件3110的材料上有所不同,同时就制造工艺而言,三维闪存3100可与三维闪存2800在基于掩模的蚀刻工艺的数量上有所不同。例如,因为中间布线层2830和沟道连接件2820包括彼此不同的材料,因此根据本公开实施例的参考图28描述的三维闪存2800通过总共三个基于掩模的蚀刻工艺来制造,包括用于形成布线连接件2840的第一掩模工艺、用于形成中间布线层2830的第二掩模工艺和用于形成沟道连接件2820的第三掩模工艺,而由于中间布线层3120和沟道连接件3110包括相同的材料,因此可以通过总共两个基于掩模的蚀刻工艺来制造根据本公开另一实施例的三维闪存3100,包括用于形成布线连接件3130的第一掩模工艺和用于同时形成中间布线层3120和沟道连接件3110的第二工艺。然而,本公开不限于此,并且可以通过允许实现上述结构的各种工艺来制造根据本公开实施例的三维闪存2800和根据本公开另一实施例的三维闪存3100。将参考图33至图36详细描述制造方法。

另外,除了上述结构之外,还可以以包括附加连接件(未示出)的结构来实现根据本公开实施例的三维闪存2800和根据本公开另一实施例的三维闪存3100,该附加连接件将中间布线层2830和3120分别连接到布线连接件2840和3130。将参考图32对此进行详细描述。

图32是根据本公开又一实施例的图28的三维闪存的截面图。

参考图32,尽管根据本公开又一实施例的三维闪存器件3200具有与参考图28至30描述的三维闪存2800相同的结构,但是不同之处在于三维闪存器件3200还包括附加连接件3210。具体地,与在Y轴方向上延伸的中间布线层3220不同,类似于布线连接件3230,作为用于将中间布线层3220连接到布线连接件3230的附加组件的附加连接件3210可以是不在图28所示的Y轴方向延伸的组件。因此,当难以应用中间布线层3220直接接触布线连接件3230的结构时,可以使用包括附加连接件3210的结构。

尽管图32示出了根据本公开又一实施例的三维闪存器件3200包括包含N-型材料的沟道连接件3240,但是本公开不限于此,并且即使沟道连接件3240包括金属材料,也可以应用包括附加连接件3210的结构。

根据本公开又一实施例的如上所述制造的三维闪存3200与根据本公开实施例的三维闪存2800以及根据本公开另一实施例的三维闪存3100不同,其不同之处仅在于进一步包括附加连接件3210,同时就制造工艺而言,三维闪存3200在基于掩模的蚀刻工艺的数量上可以不同。例如,如以上参考图31所述,根据本公开实施例的三维闪存2800通过总共三个基于掩模的蚀刻工艺制造,并且根据本公开另一实施例的三维闪存3100通过总共两个基于掩模的蚀刻工艺制造,而根据本公开又一实施例的三维闪存3200可以通过总共四个基于掩模的蚀刻工艺来制造,包括用于形成布线连接件3230的第一掩模工艺、用于形成附加连接件3210的第二掩模工艺、用于形成中间布线层3220的第三掩模工艺以及用于形成沟道连接件3240的第四掩模工艺。

图33是示出根据本公开实施例的制造三维闪存的方法的流程图,图34至图39是示出根据本公开实施例的制造三维闪存的方法的截面图,图40至图45是示出根据本公开另一实施例的制造三维闪存的方法的图,并且图46至图53是示出根据本公开又一实施例的制造三维闪存的方法的图。

在下文中,假定将参考图33至图53描述的制造三维闪存的方法由自动化和机械化的制造系统执行,并且制造三维闪存的方法是指制造参考图28至图30描述的三维闪存2800、参考图31描述的三维闪存3100和参考图32描述的三维闪存3200的方法。

另外,图34至图53的截面图指的是沿X轴方向截取的图28的串2810和2860的截面图,用于描述制造三维闪存的方法。尽管描述了通过以下描述的制造方法来制造基于图28所示的串2810的三维闪存,但是也可以通过所描述的制造方法来同样地制造基于串2850的三维闪存。

首先,在操作S3310中,由制造系统,形成下沟道层3410、4010和4610。例如,由制造系统,下沟道层3410、4010和4610可以由N-型材料形成,如图34、图40和图46所示。这里,下沟道层3410、4010和4610可分别具有内部为空的管状形状,并且在这种情况下,可以进一步布置分别填充下沟道层3410、4010和4610的内部的填充膜3411、4011和4611,以及分别包围下沟道层3410、4010和4610的外部的侧壁3412、4012和4612。

接着,在操作S3320中,由制造系统,在下沟道层3410、4010和4610的顶部区域的部分上分别形成布线连接件3420、4020和4620。例如,如图35、图41和图47所示,由制造系统,可以分别从下沟道层3410、4010和4610的顶部区域的部分到串之间的空间,通过N+型离子的注入工艺由N+型材料形成布线连接件3420、4020和4620。作为更具体的示例,由制造系统,可以通过使用掩模工艺,将布线连接件3420、4020和4620分别形成为与下沟道层3410、4010和4610的顶部区域的部分部分地重叠。

接着,在操作S3330中,由制造系统,分别形成绝缘层3430、4030和4630以覆盖布线连接件3420、4020和4620。例如,由制造系统,绝缘层3430、4030和4630可以分别由绝缘材料形成,如图36、图42和图48所示。这里,绝缘层3430、4030和4630可以包括与布置在串中包括的多个电极层(未示出)之间的层间电介质(未示出)相同的材料。

接着,在操作S3340中,由制造系统,蚀刻绝缘层3430、4030和4630中分别与下沟道层3410、4010和4610的顶部区域中除了形成布线连接件3420、4020和4620的部分以外的其余部分相对应的部分、以及绝缘层3430、4030和4630中分别与布线连接件3420、4020和4620的顶部区域的部分相对应的部分。

接着,在操作S3350中,由制造系统,将中间布线层3440、4040和4640分别形成在通过蚀刻绝缘层3430、4030和4630中与布线连接件3420、4020和4620的顶部区域的部分相对应的部分而得到的空间中。

接着,在操作S3360中,由制造系统,将沟道连接件3450、4050和4650分别形成在通过蚀刻绝缘层3430、4030和4630中与下沟道层3410、4010和4610的顶部区域中除了形成布线连接件3420、4020和4620的部分以外的其余部分相对应的部分而得到的空间3432、4032和4632中。

这里,根据打算制造参考图28描述的三维闪存2800、参考图31描述的三维闪存3100和参考图32描述的三维闪存3200中的哪一个,可以在其细节方面不同地执行操作S3340至S3360。

例如,当打算制造参考图28描述的三维闪存2800时,在由制造系统通过掩模工艺蚀刻绝缘层3430中与布线连接件3420的顶部区域的部分相对应的部分之后,如图37所示,可以由制造系统将中间布线层3440形成在通过蚀刻绝缘层3430中与布线连接件3420的顶部区域的部分相对应的部分而得到的空间中。接着,由制造系统,在通过掩模工艺蚀刻绝缘层3430中与下沟道层3410的顶部区域中除了形成布线连接件3420的部分以外的其余部分相对应的部分之后,如图38所示,可以在通过蚀刻绝缘层3430中与下沟道层3410的顶部区域中除了形成布线连接件3420的部分之外的其余部分相对应的部分而得到的空间3432中形成沟道连接件3450。这里,由制造系统,可以形成中间布线层3440和沟道连接件3450,使得至少部分地掩埋在串中的布线连接件3420接触中间布线层3440和沟道连接件3450两者。

作为另一示例,当打算制造参考图31所述的三维闪存3100时,在由制造系统通过掩模工艺蚀刻绝缘层4030中与布线连接件4020的顶部区域的部分相对应的部分以及绝缘层4030中与下沟道层4010的顶部区域中除了形成布线连接件4020的部分之外的其余部分相对应的部分之后,如图43所示,可以由制造系统将中间布线层4040形成在通过蚀刻绝缘层4030中与布线连接件4020的顶部区域的部分相对应的部分而得到的空间4031中,并且如图44所示,可以由制造系统在通过蚀刻绝缘层4030中与下沟道层4010的顶部区域中除了形成布线连接件4020的部分之外的其余部分相对应的部分而得到的空间4032中形成沟道连接件4050。这里,由制造系统,可以形成中间布线层4040和沟道连接件4050,使得至少部分地掩埋在串中的布线连接件4020接触中间布线层4040和沟道连接件4050两者。

作为又一示例,当打算制造参考图32描述的三维闪存3200时,在由制造系统通过掩模工艺蚀刻绝缘层4630中与布线连接件4620的顶部区域的部分相对应的部分之后,如图49所示,可以由制造系统在通过蚀刻绝缘层4630中与布线连接件4620的顶部区域的部分相对应的部分而得到的空间4631中形成附加连接件4660。接着,由制造系统,在通过掩模工艺在附加连接件4660上形成中间布线层4640之后,如图50所示,形成附加绝缘层4633以覆盖中间布线层4640,如图51所示。因此,如图52所示,由制造系统,在通过掩模工艺蚀刻绝缘层4630和附加绝缘层4633中分别与下沟道层4610的顶部区域中除了形成布线连接件4620的部分之外的其余部分相对应的部分之后,可以在通过蚀刻绝缘层4630和附加绝缘层4633中分别与下沟道层4610的顶部区域中除了形成布线连接件4620的部分之外的其余部分相对应的部分而得到的空间4632和4634中形成沟道连接件4650。在此,由制造系统,可以将附加连接件4660和沟道连接件4650形成为使得至少部分地掩埋在串中的布线连接件4620接触附加连接件4660和沟道连接件4650两者,附加连接件4660接触中间布线层4640。

接着,在操作S3370中,由制造系统,在沟道连接件3450、4050和4650上分别形成上沟道层3460、4060和4670。例如,由制造系统,上沟道层3460、4060和4670可以分别由N-型材料形成,如图39,图45和图53所示。这里,和下沟道层3410、4010和4610一样,上沟道层3460、4060和4670可以分别具有内部为空的管状形状,并且在这种情况下,可以进一步布置分别填充上沟道层3460、4060和4670的内部的填充膜3461、4061和4671,以及分别包围上沟道层3460、4060和4670的外部的侧壁3462、4062和4672。

图54是示出根据本公开另一实施例的三维闪存的顶视图,并且图55是沿X-轴截取的图54的三维闪存的截面图。

参考图54和图55,根据本公开另一实施例的三维闪存5400具有与参考图28至30描述的三维闪存2800相似的结构,而不同之处在于布置在串5410和5420之间的中间布线层5430由彼此水平相邻的串5410和5420共享,而不是由对角相邻的串共享。

更具体地,为了由彼此水平相邻的串5410和5420共享中间布线层5430,可以形成布线连接件5440以至少部分地掩埋在串5410和5420的每个中,从而将相应串5410和5420的沟道连接件5411、5421连接到中间布线层5430。

因为分别构成布线连接件5440、沟道连接件5411、5421和中间布线层5430的材料与参考图28至30描述的三维闪存2800中包括的布线连接件2840、沟道连接件2820和中间布线层2830的材料相同,因此将省略其描述。

图56是根据本公开另一实施例的图54的三维闪存的截面图。

参考图56,三维闪存5600中的沟道连接件5611和5621包括金属材料(例如,钨(W),钛(Ti),钽(Ta),铜(Cu)或金(Au))类似于参考图31描述的三维闪存3100中包括的沟道连接件3110,而不同之处在于中间布线层5630由水平相邻的串5610和5620共享,而不是由对角相邻的串共享,如参考图54和55所述。同样,为了使中间布线层5630由水平相邻的串5610和5620共享,可以形成布线连接件5640以至少部分地掩埋在每个串5610和5620中,从而将相应串5610和5620的沟道连接件5611、5621连接到中间布线层5630。

因为分别构成布线连接件5640、沟道连接件5611、5621和中间布线层5630的材料与参考图31描述的三维闪存3100中包括的布线连接件3130、沟道连接件3110和中间布线层3120的材料相同,因此将省略其描述。

图57是根据本公开又一实施例的图54的三维闪存的截面图。

参考图57,类似于参考图32所述的三维闪存3200,三维闪存5700具有进一步包括附加连接件5730的结构,同时中间布线层5740被水平相邻的串5710和5720共享,而不是由对角相邻的串共享,如参考图54和55所述。类似地,为了使中间布线层5740由水平相邻的串5710和5720共享,可以将布线连接件5750形成为至少部分地掩埋在每个串5710和5720中,从而将相应串5710和5720的沟道连接件5711和5721连接到附加连接件5730。

因为分别构成布线连接件5750、沟道连接件5711、5721,中间布线层5740和附加连接件5730的材料与参考图32描述的三维闪存3200中包括的布线连接件3230、沟道连接件3240、中间布线层3220和附加连接件3210的材料相同,因此将省略其描述。

参考图54至图57描述的制造三维闪存5400、5600和5700的方法与参考图33至图53描述的制造三维闪存的方法相同,而不同之处在于,制造了由水平相邻的串而不是对角相邻的串共享的中间布线层。因此,将省略其制造方法的描述。

至此,尽管已经结合附图参考特定实施例描述了本公开,但是应当理解,本领域普通技术人员可以在不脱离本公开的精神和范围的情况下进行各种修改和改变。例如,即使当所描述的操作以与所描述的顺序不同的顺序执行和/或所描述的组件(例如系统、结构、器件和电路)以与所描述的方式不同的方式彼此耦合或组合,或者被其他组件或其等同物替代或替换时,也可以获得适当的结果。

因此,应当理解,所附权利要求的其他实现方式、其他实施例以及等同方案也落入所附权利要求的范围内。

- 支持块体擦除操作的三维闪存器件及其制造方法

- 闪存器件以及擦除闪存器件的方法