驱动电路及半导体模块

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及对IGBT等开关元件进行驱动的驱动电路及半导体模块。

背景技术

如果驱动电路向开关元件的栅极供给输出电流,则栅极电压逐渐上升。如果栅极电压超过开关元件的阈值电压,则开关元件从断开切换为接通。提出了以下技术,即,在对多个开关元件进行驱动时,通过减小向阈值电压低的开关元件供给的栅极电压而防止由电流集中引起的破坏(例如,参照专利文献1(图2))。在专利文献1中,NchMOS36和PchMOS50生成输出电流。双方都以使开关元件导通为前提,在栅极电压达到开关元件的阈值电压之后也继续保持电流输出能力。

专利文献1:国际公开第2016/207956号

如果在开关元件的导通时驱动电路的输出电流大,则栅极电压的上升变得陡峭,集电极电流开始急剧地流动,因此通断噪声增大。为了防止该情况,需要限制驱动电路的输出电流,抑制栅极电压超过开关元件的阈值电压时的dv/dt。但是,如果限制输出电流,则从驱动电路开始供给电流起至超过开关元件的阈值电压为止的期间变长。通常,在该期间开关元件为断开状态,因此如果该期间变长,则通断损耗增大。

发明内容

本发明就是为了解决上述这样的课题而提出的,其目的在于得到能够抑制通断噪声并且降低通断损耗的驱动电路及半导体模块。

本发明涉及的驱动电路的特征在于,具有彼此并联连接的第1及第2驱动部,在开关元件的导通操作时,所述第1及第2驱动部两者开始向所述开关元件的栅极供给栅极电流,即使所述开关元件的栅极电压达到所述开关元件的阈值电压,所述第1驱动部也继续供给所述栅极电流,所述第2驱动部在所述栅极电压达到所述阈值电压之前停止所述栅极电流的供给。

发明的效果

在本发明中,在开关元件的导通操作时,第1及第2驱动部两者开始供给栅极电流。由此,从驱动电路开始供给电流起至栅极电压超过开关元件的阈值电压为止的期间变短,因此能够降低通断损耗。另外,即使栅极电压达到阈值电压,第1驱动部也继续供给栅极电流,但第2驱动部在栅极电压达到阈值电压之前停止栅极电流的供给。由此,在开关元件导通时,栅极电压缓慢地超过阈值电压。因此,能够抑制在开关元件导通时产生的通断噪声。

附图说明

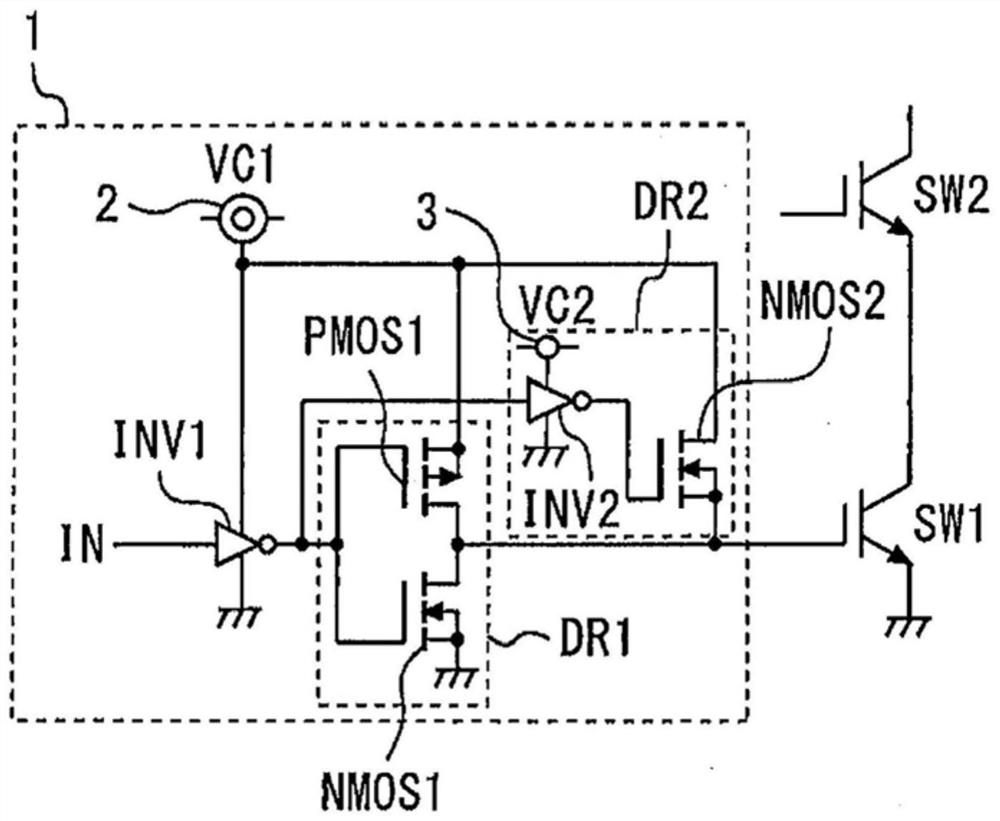

图1是表示实施方式1涉及的半导体模块的电路图。

图2是表示实施方式1涉及的半导体模块的动作的时序图。

图3是表示实施方式2涉及的半导体模块的电路图。

图4是表示实施方式2涉及的第2驱动部的前置放大器的电路图。

图5是表示实施方式2涉及的第2驱动部的前置放大器的动作的时序图。

图6是表示实施方式3涉及的半导体模块的电路图。

图7是表示实施方式3涉及的半导体模块的动作的时序图。

图8是表示实施方式4涉及的半导体模块的电路图。

标号的说明

1驱动电路,3、4电源,DR1第1驱动部,DR2第2驱动部,INV2、INV3反相器(前置放大器),NMOS2 NMOS晶体管,PMOS3 PMOS晶体管,R1、R2、R3、R4电阻,SW1开关元件

具体实施方式

参照附图,对实施方式涉及的驱动电路及半导体模块进行说明。对相同或相应的结构要素标注相同的标号,有时省略重复说明。

实施方式1.

图1是表示实施方式1涉及的半导体模块的电路图。该半导体模块在例如将交流电力变换为直流电力之后,再次变换为交流电力时使用。开关元件SW1、SW2被级联连接。开关元件SW1、SW2例如是IGBT、MOSFET、SiCMOSFET等功率器件,将从商用电源升压而生成的电压作为电源。

驱动电路1是根据输入信号IN而对开关元件SW1的栅极进行偏置,将开关元件SW1控制为接通或断开的控制用集成电路。驱动电路1具有作为前置放大器的反相器INV1和彼此并联连接的第1及第2驱动部DR1、DR2。反相器INV1使输入信号IN逻辑反转。第1及第2驱动部DR1、DR2根据反相器INV1的输出信号而向开关元件SW1的栅极供给栅极电流。INV1的电源是驱动电路1的电源2。

第1驱动部DR1具有彼此并联连接的NMOS晶体管NMOS1和PMOS晶体管PMOS1。NMOS1和PMOS1的栅极与反相器INV1的输出连接。NMOS1的源极与GND连接。PMOS1的源极与电源2连接。NMOS1的漏极和PMOS1的漏极连接于开关元件SW1的栅极。

第2驱动部DR2具有NMOS晶体管NMOS2、对NMOS2进行驱动的前置放大器即反相器INV2、以及反相器INV2的高电位侧的电源3。反相器INV2使反相器INV1的输出信号逻辑反转。NMOS2的栅极与反相器INV2的输出连接。NMOS2的漏极与驱动电路1的电源2连接。NMOS2的源极与开关元件SW1的栅极连接。电源3在驱动电路1内部生成比驱动电路1的电源2的电压VC1低的电压VC2。

INV2的高电平输出的电压成为INV2的电源3的电压VC2。通过该电压VC2对NMOS2的栅极进行偏置,通过NMOS2的源极电压对开关元件SW1的栅极进行偏置。NMOS2的栅极-源极间电压Vgs是电压VC2与开关元件SW1的栅极电压Vg之差。因此,如果开关元件SW1的栅极电压Vg变得比电压VC2与NMOS2的阈值电压Vth2之差高(Vg>VC2-Vth2),则Vgs变得比Vth2小,NMOS2断开,从而不再向开关元件SW1供给栅极电流。因此,越是使INV2的电源3的电压VC2低,则在越低的栅极电压Vg下停止由第2驱动部DR2进行的电流供给。

在本实施方式中,使INV2的电源3的电压VC2比将开关元件SW1的阈值电压Vth1和NMOS2的阈值电压Vth2相加而得到的合计电压低。由此,第2驱动部DR2在开关元件SW1的栅极电压Vg达到阈值电压Vth1之前丧失输出能力,停止栅极电流的供给。

图2是表示实施方式1涉及的半导体模块的动作的时序图。图2(a)是对开关元件SW1进行导通操作的输入信号IN的波形。(b)是开关元件SW1的栅极偏置波形。(c)是仅第1驱动部DR1的情况下的栅极偏置波形。(d)是仅第2驱动部DR2的情况下的栅极偏置波形。(b)的波形是(c)的波形和(d)的波形的合计。

如果输入高电平信号作为输入信号IN,则驱动电路1进行使开关元件SW1导通的操作。在该开关元件SW1的导通操作时,PMOS1和NMOS2接通,使开关元件SW1的栅极电压上升。这样,第1及第2驱动部DR1、DR2两者开始供给栅极电流,因此从驱动电路1开始供给电流起至栅极电压超过开关元件SW1的阈值电压Vth1为止的期间变短。由此,能够降低通断损耗。

然后,即使栅极电压上升而达到阈值电压Vth1,第1驱动部DR1也继续供给栅极电流。另一方面,第2驱动部DR2在栅极电压达到阈值电压Vth1之前停止栅极电流的供给。因此,栅极电压超过阈值电压Vth1时的栅极电压的上升速度与仅第1驱动部DR1的情况相同。因此,在开关元件SW1导通时,栅极电压缓慢地超过阈值电压Vth1。由此,能够抑制在开关元件SW1导通时产生的通断噪声。但是,需要限制PMOS1的输出,以使得通断噪声成为容许值。

实施方式2.

图3是表示实施方式2涉及的半导体模块的电路图。图4是表示实施方式2涉及的第2驱动部的前置放大器的电路图。INV2具有彼此并联连接的PMOS晶体管PMOS2和NMOS晶体管NMOS3。与实施方式1不同,INV2的电源不是电源3,而是驱动电路1的电源2。在INV2的输出与基准电位即GND之间设置有串联连接了电阻R1、R2的分压电路。电阻R1、R2的连接点与NMOS2的栅极连接。其它结构与实施方式1相同。

图5是表示实施方式2涉及的第2驱动部的前置放大器的动作的时序图。图5(a)是INV2的输入电压的波形。(b)是电阻R1、R2的连接点的电压、即NMOS2的栅极电压的波形。电阻R1、R2的连接点的电压通过电阻分配而变得比驱动电路1的电源2的电压VC1低。

使电阻R1、R2的连接点的电压比将开关元件SW1的阈值电压Vth1和NMOS2的阈值电压Vth2相加而得到的合计电压低。因此,第2驱动部DR2在开关元件SW1的栅极电压Vg达到阈值电压Vth1之前丧失输出能力,停止栅极电流的供给。因此,能够得到与实施方式1相同的效果。并且,由于不需要像实施方式1那样另外使用电源3,因此电路的结构变得简单。另外,通过将电阻R1、R2的电阻值设为适当的值,从而能够容易地设定与电源3的电压VC2相当的电压。

实施方式3.

图6是表示实施方式3涉及的半导体模块的电路图。驱动电路1使在开关元件SW1的栅极蓄积的电荷放电而进行开关元件SW1的截止操作。第2驱动电路DR2的结构与实施方式1不同。

第2驱动电路DR2具有PMOS晶体管PMOS3、对PMOS3进行驱动的前置放大器即INV3、以及INV3的低电位侧的电源4。PMOS3的源极与GND连接。PMOS2的漏极与开关元件SW1的栅极连接。PMOS2的栅极与INV3的输出连接。其它结构与实施方式1相同。

INV3的高电位侧的电源是驱动电路1的电源2。使用电源4作为INV3的低电位侧的电源。电源4在驱动电路1内部生成比驱动电路1的GND高的电压VC3。

INV3的低电平输出的电压成为INV3的基准电位即电源4的电压VC3。通过该电压VC3对PMOS3的栅极进行偏置,如果PMOS3接通,则使在开关元件SW1的栅极积蓄的电荷放电。PMOS3的栅极-源极间电压Vgs是开关元件SW1的栅极电压Vg与VC3之差。因此,如果开关元件SW1的栅极电压Vg变得比电压VC3和PMOS3的阈值电压Vth3之和低(Vg<VC3+Vth3),则Vgs变得比Vth3小,PMOS3断开,从而不再使电荷放电。因此,越是使INV3的基准电位即电压VC3高,则在越高的栅极电压Vg下停止由第2驱动部DR2进行的放电。

因此,使电压VC3比从开关元件SW1的阈值电压Vth1减去PMOS3的阈值电压Vth3而得到的电压差高。由此,第2驱动部DR2在开关元件SW1的栅极电压达到阈值电压Vth1之前停止电荷的放电。

图7是表示实施方式3涉及的半导体模块的动作的时序图。图7(a)是对开关元件SW1进行截止操作的输入信号IN的波形。(b)是开关元件SW1的栅极偏置波形。(c)是仅第1驱动部DR1的情况下的栅极偏置波形。(d)是仅第2驱动部DR2的情况下的栅极偏置波形。(b)的波形是(c)的波形和(d)的波形的合计。

如果输入低电平信号作为输入信号IN,则驱动电路1进行使开关元件SW1截止的操作。在该开关元件SW1的截止操作时,NMOS1和PMOS3接通,使开关元件SW1的栅极电压下降。这样,第1及第2驱动部DR1、DR2两者开始使在开关元件SW1的栅极蓄积的电荷放电,因此从驱动电路1开始放电起至栅极电压下降至低于开关元件SW1的阈值电压Vth1为止的期间变短。由此,能够降低通断损耗。

然后,即使栅极电压下降而达到阈值电压Vth1,第1驱动部DR1也继续使电荷放电。另一方面,第2驱动部DR2在栅极电压达到阈值电压Vth1之前停止电荷的放电。因此,栅极电压下降至低于阈值电压Vth1时的栅极电压的下降速度与仅第1驱动部DR1的情况相同。因此,在开关元件SW1截止时,栅极电压缓慢地下降至低于阈值电压Vth1。由此,能够抑制在开关元件SW1截止时产生的通断噪声。

实施方式4.

图8是表示实施方式4涉及的半导体模块的电路图。与实施方式3不同,INV3的基准电位不是电源4的输出电位,而是驱动电路1的GND。在INV3的输出与驱动电路1的电源2之间设置有串联连接了电阻R3、R4的分压电路。电阻R3、R4的连接点与PMOS3的栅极连接。其它结构与实施方式3相同。

电阻R3、R4的连接点的电压比驱动电路1的GND电位高。使电阻R3、R4的连接点的电压比从开关元件SW1的阈值电压Vth1减去PMOS3的阈值电压Vth3而得到的电压差高。由此,第2驱动部DR2在开关元件SW1的栅极电压达到阈值电压Vth1之前停止电荷的放电。因此,能够得到与实施方式3相同的效果。并且,由于不需要像实施方式3那样另外使用电源4,因此电路的结构变得简单。另外,通过将电阻R3、R4的电阻值设为适当的值,从而能够容易地设定与电源4的电压VC3相当的电压。

此外,开关元件SW1、SW1不限于由硅形成,也可以由与硅相比带隙大的宽带隙半导体形成。宽带隙半导体例如是碳化硅、氮化镓类材料、或金刚石。由这样的宽带隙半导体形成的半导体芯片由于耐电压性、容许电流密度高,因此能够小型化。通过使用该小型化的半导体芯片,从而组装了该半导体芯片的半导体模块也能够小型化、高集成化。另外,由于半导体芯片的耐热性高,因此能够使散热器的散热鳍片小型化,能够使水冷部空冷化,因而能够使半导体模块进一步小型化。另外,由于半导体芯片的电力损耗低且高效,因此能够使半导体模块高效化。