薄膜晶体管衬底

文献发布时间:2023-06-19 09:32:16

技术领域

本公开涉及一种薄膜晶体管衬底。

背景技术

包括氧化物半导体材料(诸如铟镓锌氧化物(IGZO))的薄膜晶体管(TFT)被用于显示装置,其包括液晶显示面板和有机发光二极管(OLED)显示装置以及其他种类的装置。氧化物半导体TFT生成小的泄漏电流,并且因此导致装置的低功耗。然而,氧化物半导体TFT与低温多晶硅TFT相比具有低迁移率。为了解决该问题,US 2017/0184893 A公开了显示装置,其通过包括具有不同迁移率的氧化物半导体TFT实现了低功耗和窄边框二者。

发明内容

存在对显示装置或其他种类的装置的各种要求。例如,一个装置需要更低的功耗、更小的电路尺寸和更高的可靠性。为了满足氧化物半导体TFT的这种不同要求,必须在同一衬底上制造包括具有不同特性的(由不同材料制成的)氧化物半导体膜的氧化物半导体TFT。为了适当地满足各种要求,重要的是,每个氧化物半导体TFT的材料可从各种氧化物半导体材料中选择。

本公开的一个方面是薄膜晶体管衬底,其包括:绝缘衬底;设置在绝缘衬底上的第一绝缘层;设置在绝缘衬底上的第一薄膜晶体管并且包括第一氧化物半导体膜;设置在绝缘衬底上且位于比第一绝缘层更靠上部的第二绝缘层;以及设置在绝缘衬底上的第二薄膜晶体管并且包括与第一氧化物半导体膜成分不同的第二氧化物半导体膜。第一氧化物半导体膜的至少一部分设置在第一绝缘层的上方并与其接触。第一绝缘层是位于比第一氧化物半导体膜更靠下部且与其接触的绝缘层中的最上面的绝缘层。第二氧化物半导体膜的至少一部分设置在第二绝缘层的上方并与其接触。第二绝缘层是位于比第二氧化物半导体膜更靠下部且与其接触的绝缘层中的最上面的绝缘层。

本公开的另一方面是制造薄膜晶体管衬底的方法,该方法包括:在绝缘衬底上形成第一绝缘层;在形成第一绝缘层后形成包括第一薄膜晶体管的沟道区的第一氧化物半导体层;形成第二绝缘层以覆盖第一氧化物半导体层;以及在第一氧化物半导体层被第二绝缘层覆盖的状态下形成包括第二薄膜晶体管的沟道区的第二氧化物半导体膜。

本公开的一个方面提供了一种在同一衬底上正确制造氧化物半导体TFT的技术,氧化物半导体TFT由不同特性的氧化物半导体材料制成,所述氧化物半导体材料选自跟中氧化物半导体材料。

应该理解的是,前面的一般性描述和以下的详细描述均为示例性及说明性的并且均非对本公开的限制。

附图说明

图1示意性地示出了液晶显示面板的构造示例;

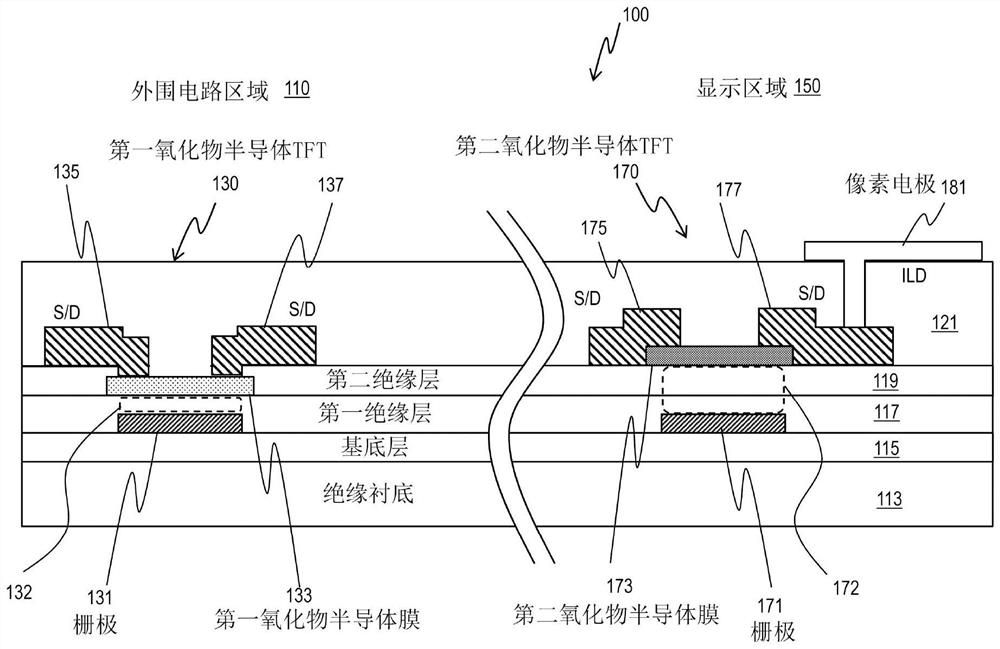

图2示意性地示出了用于液晶显示面板的TFT衬底的构造示例的截面;

图3A示出了图2中示出的TFT衬底的制造方法的步骤;

图3B示出了图2中示出的TFT衬底的制造方法的步骤;

图3C示出了图2中示出的TFT衬底的制造方法的步骤;

图3D示出了图2中示出的TFT衬底的制造方法的步骤;

图3E示出了图2中示出的TFT衬底的制造方法的步骤;

图3F示出了图2中示出的TFT衬底的制造方法的步骤;

图3G示出了图2中示出的TFT衬底的制造方法的步骤;

图3H示出了图2中示出的TFT衬底的制造方法的步骤;

图4示意性地示出了用于液晶显示面板的TFT衬底的另一构造示例的截面;

图5A示出了图4中示出的TFT衬底的制造方法的步骤;

图5B示出了图4中示出的TFT衬底的制造方法的步骤;

图5C示出了图4中示出的TFT衬底的制造方法的步骤;

图5D示出了图4中示出的TFT衬底的制造方法的步骤;

图5E示出了图4中示出的TFT衬底的制造方法的步骤;

图5F示出了图4中示出的TFT衬底的制造方法的步骤;

图5G示出了图4中示出的TFT衬底的制造方法的步骤;

图5H示出了图4中示出的TFT衬底的制造方法的步骤;

图6示意性地示出了用于液晶显示面板的TFT衬底的又一构造示例的截面;

图7A示出了图6中示出的TFT衬底的制造方法的步骤;

图7B示出了图6中示出的TFT衬底的制造方法的步骤;

图7C示出了图6中示出的TFT衬底的制造方法的步骤;

图7D示出了图6中示出的TFT衬底的制造方法的步骤;

图7E示出了图6中示出的TFT衬底的制造方法的步骤;

图7F示出了图6中示出的TFT衬底的制造方法的步骤;

图7G示出了图6中示出的TFT衬底的制造方法的步骤;

图7H示出了图6中示出的TFT衬底的制造方法的步骤;

图8示意性地示出了用于液晶显示面板的TFT衬底的又一构造示例的截面;

图9A示出了图8中示出的TFT衬底的制造方法的步骤;

图9B示出了图8中示出的TFT衬底的制造方法的步骤;

图9C示出了图8中示出的TFT衬底的制造方法的步骤;

图9D示出了图8中示出的TFT衬底的制造方法的步骤;

图9E示出了图8中示出的TFT衬底的制造方法的步骤;

图9F示出了图8中示出的TFT衬底的制造方法的步骤;

图9G示出了图8中示出的TFT衬底的制造方法的步骤;

图10示意性地示出了用于液晶显示面板的TFT衬底的又一构造示例的截面;

图11A示出了图10中示出的TFT衬底的制造方法的步骤;

图11B示出了图10中示出的TFT衬底的制造方法的步骤;

图11C示出了图10中示出的TFT衬底的制造方法的步骤;

图11D示出了图10中示出的TFT衬底的制造方法的步骤;

图11E示出了图10中示出的TFT衬底的制造方法的步骤;

图11F示出了图10中示出的TFT衬底的制造方法的步骤;

图11G示出了图10中示出的TFT衬底的制造方法的步骤;

图12示出了移位寄存器的一级电路的示例;

图13示出了用于OLED显示装置的像素电路的示例;

图14示意性地示出了用于液晶显示面板的TFT衬底的又一构造示例的截面;

图15示意性地示出了用于液晶显示面板的TFT衬底的又一构造示例的截面;

图16A示出了图15中示出的TFT衬底的制造方法的步骤;

图16B示出了图15中示出的TFT衬底的制造方法的步骤;

图16C示出了图15中示出的TFT衬底的制造方法的步骤;

图16D示出了图15中示出的TFT衬底的制造方法的步骤;

图16E示出了图15中示出的TFT衬底的制造方法的步骤;

图16F示出了图15中示出的TFT衬底的制造方法的步骤;

图16G示出了图15中示出的TFT衬底的制造方法的步骤;

图16H示出了图15中示出的TFT衬底的制造方法的步骤;

图16I示出了图15中示出的TFT衬底的制造方法的步骤;并且

图17示意性地示出了用于顶发射型OLED显示装置的TFT衬底的像素区域的构造示例的截面。

具体实施方式

以下,将参考附图描述本公开的实施例。应当注意,这些实施例仅仅是实现本公开的示例,并不限制本公开的技术范围。图中常用的元件用相同的参考符号表示,图中的一些元件在尺寸或形状上被夸大,以便清楚地理解描述。

概述

以下,描述了本公开的包括氧化物半导体TFT的TFT衬底的结构和制造方法。本公开的TFT衬底可用于各种装置,诸如传感器装置和显示装置。

对器件的要求是多种多样的,诸如对低功耗的要求、对较小电路尺寸的要求和对更高可靠性的要求。为了满足氧化物半导体TFT的这种不同要求,必须在同一衬底上制造包括具有不同特性的(由不同材料制成的)氧化物半导体膜的氧化物半导体TFT。为了适当地满足各种要求,重要的是,每个氧化物半导体TFT的氧化物半导体材料可从各种氧化物半导体材料中选择。

本公开的TFT沉底包括氧化物半导体TFT,包括由不同材料(具有不同的元素组成)制成的氧化物半导体膜。不同的材料满足了对TFT衬底的不同要求。第一种氧化物半导体TFT的氧化物半导体膜的至少一部分设置在所述第一绝缘层的上方并与第一绝缘层接触,而第二种氧化物半导体TFT的氧化物半导体膜的至少一部分设置在不同于第一绝缘层的第二绝缘层的上方并与其接触层。这种构造允许从各种氧化物半导体材料中选择用于TFT的不同氧化物半导体材料。

与低温多晶硅TFT相比,氧化物半导体TFT展现出低泄漏电流和低温度依赖性,但是具有低迁移率和低可靠性。特别是氧化物半导体TFT具有低的负偏压照明温度应力(NBITS)可靠性。NBITS可靠性是指TFT被置于负栅偏压、光照和高温的应力条件下的可靠性。氧化物半导体TFT的栅极阈值电压随NBITS而显著变化。

认为光产生的载流子引起了栅极阈值电压的变化。因此,为了提高氧化物半导体TFT的可靠性,采用具有宽带隙的氧化物半导体材料是重要的。另一方面,为了实现更小的电路尺寸,其中的氧化物半导体TFT的迁移率应该高,即采用具有高迁移率的氧化物半导体材料是重要的。

例如,为了使显示装置具有薄边框和高可靠性,TFT衬底可以包括采用在外围电路中具有高迁移率的氧化物半导体材料的氧化物半导体TFT以及采用在显示区域(像素电路)中具有宽带隙的氧化物半导体材料的氧化物半导体TFT。在下文中,作为本公开的TFT衬底的应用示例,描述了用于显示装置的TFT衬底。

实施例1

显示装置的构造

图1示出了液晶显示面板1的构造示例。液晶显示面板1包括薄膜晶体管(TFT)衬底10,其上设置有用于向液晶施加电场的TFT和像素电极、相对的衬底20和用于将TFT衬底10与相对的衬底20接合的密封剂30。液晶材料被封闭在TFT衬底10和相对的衬底20之间。在TFT衬底10或相对的衬底20上设置有公共电极,其用于产生与像素电极一起施加在液晶上的电场。

在TFT衬底10和相对的衬底20彼此相对的面上,设置有用于液晶初始配向的配向膜(未示出)。在TFT衬底10和相对的衬底20的其它外表面上,设置偏光板(未示出)。液晶显示面板还包括未示出的背光单元。

在比TFT衬底10的显示区域25更靠外的外周中,设置外围电路。比设置外围电路的显示区域25更靠外的区域称为外围电路区域。外围电路的示例包括第一扫描驱动器31、第二扫描驱动器32、保护电路33和多路解调器36。此外,在显示区域25之外设置驱动器IC 34。

保护电路33包括静电放电(ESD)保护元件以及保护像素电路中的元件免受ESD损坏。驱动器IC 34经由柔性印刷电路(FPC)35被连接至外部装置。驱动器IC 34安装有例如各向异性导电膜(ACF)。

扫描驱动器31和32驱动TFT衬底10上的扫描线。驱动器IC 34向扫描驱动器31和32供应电力和定时信号(控制信号),并且进一步通过多路解调器36向数据线供应对应于视频数据的信号。多路解调器36将驱动器IC 34的一个引脚的输出串联输出到d个数据线(d是大于1的整数)。多路解调器36将来自驱动IC 34的每扫描周期d次的数据信号的输出数据线改变为驱动d倍于驱动器IC 34的输出引脚的数据线。

有机发光二极管(OLED)显示装置具有类似于图1所示的构造的构造。OLED显示装置包括有机发光元件(OLED元件)和TFT设置于其上的TFT衬底,用于封装OLED元件的封装衬底,以及用于将TFT衬底与封装衬底接合的接合件(玻璃熔块密封剂)。TFT衬底与封装衬底之间的空间充满例如干燥氮气,并且利用接合件30密封。封装衬底和接合件构成结构封装单元。结构封装单元可以具有薄膜封装(TFE)结构。

在比TFT衬底的显示区域的更靠外的外围设置有一个或多个扫描驱动器、保护电路、驱动器IC和多路解调器。扫描驱动器和保护电路是设置在TFT衬底上的外围电路。例如,第一扫描驱动器驱动TFT衬底上的扫描线;第二扫描驱动器驱动控制线以控制像素的发光周期并向像素供应参考电位。驱动器IC向扫描驱动器提供电力和定时信号(控制信号),并且进一步向多路解调器提供电力和数据信号。多路解调器具有与液晶显示面板1中的多路解调器36相同的功能。

TFT衬底的构造

图2示意性地示出了用于液晶显示面板的TFT衬底100的构造示例的截面。图2借由示例示出了在TFT衬底100的外围电路区域110中的一个第一氧化物半导体TFT 130和在TFT衬底100的显示区域150中的一个第二氧化物半导体TFT 170。外围电路区域110位于比显示区域150更靠外,并且是安装外围电路的区域。显示区域150是包括像素的区域。例如,第一氧化物半导体TFT 130是扫描驱动器中的氧化物半导体TFT,并且第二氧化物半导体TFT170是用于选择像素以提供数据信号的开关TFT。

第一氧化物半导体TFT 130和第二氧化物半导体TFT 170构建在由树脂或玻璃制成的柔性或非柔性的绝缘衬底113上。在以下描述中,在彼此相互接触的两个层叠层(两个具有界面的层)之间,更靠近绝缘衬底113的层是较下层,而距离绝缘衬底113较远的层是较上层。

第一氧化物半导体TFT 130的氧化物半导体膜(第一氧化物半导体膜)133和第二氧化物半导体TFT 170的氧化物半导体膜(第二氧化物半导体膜)173由不同的氧化物半导体材料制成,并且具有不同的特性。在该示例中,第一氧化物半导体膜133的迁移率高于第二氧化物半导体膜173的迁移率,并且第二氧化物半导体膜173的带隙比第一氧化物半导体膜133的带隙宽。由于两种氧化物半导体膜在特性上的差异,两种膜都实现了窄边框和高可靠性。

可以用于第一氧化物半导体膜133的氧化物半导体材料的示例包括ITZO、IGZTO、In-Zn-Ti-O和In-W-Z-O。可以用于第二氧化物半导体膜173的氧化物半导体材料的示例包括IGZO、GaZnO和IGO。

第一氧化物半导体TFT 130的氧化物半导体膜(第一氧化物半导体膜)133设置在第一绝缘层117的上方并与其接触。第一氧化物半导体TFT 170的氧化物半导体膜(第二氧化物半导体膜)173设置在第二绝缘层119的上方并与其接触。第二绝缘层119位于比第一绝缘层117更靠上部。第一氧化物半导体膜133位于比第二氧化物半导体膜173更靠下部。第一绝缘层117和第二绝缘层119可以由氮化硅或氧化硅制成。

在图2中的构造示例中,在第一绝缘层117的上方并与其接触设置有整个第一氧化物半导体膜133,并且在第二绝缘层119的上方并与其接触设置有整个第二氧化物半导体膜173。第二绝缘层119设置在第一绝缘层117的上方并与其接触。第一氧化物半导体膜133和第二绝缘层119均设置在第一绝缘层117的上方并与其接触。

第一氧化物半导体TFT 130包括第一氧化物半导体膜133、位于比第一氧化物半导体膜133更靠下部的栅极131和位于栅极131与第一氧化物半导体膜133之间的栅极绝缘膜132(在层结构方向中)。栅极131设置在绝缘基底层115上方并与其接触。栅极绝缘膜132是第一绝缘层117的一部分。基底层115可以由氮化硅或氧化硅制成。

第一氧化物半导体膜133包括两个源/漏区(未示出)和源/漏区之间的沟道区(未示出)。源/漏区为低电阻区,而沟道区为高电阻区。源/漏区是与源/漏极135和137接触的部分。源/漏极135和137被设置在第二绝缘层119上方并与其接触,并且它们在第二绝缘层119中形成的开口内与第一氧化物半导体膜133的顶面接触。尽管在图2的示例中的源/漏极135和137仅与第一氧化物半导体膜133的顶面接触,但源/漏极135和137可以与第一氧化物半导体膜133的端面和顶面接触。

第二氧化物半导体TFT 170包括第二氧化物半导体膜173、位于比第一氧化物半导体膜173更靠下部的栅极171和位于栅极171与第二氧化物半导体膜173之间的栅极绝缘膜172(在层结构方向中)。栅极171设置在绝缘基底层115上方并与其接触。栅极绝缘膜172具有由第一绝缘层117的一部分和第二绝缘层119的一部分组成的层叠结构。第二氧化物半导体TFT 170的栅极绝缘膜172比第一氧化物半导体TFT 130的栅极绝缘膜132更厚,以增加第二氧化物半导体TFT 170的栅极绝缘膜172的可靠性。

第二氧化物半导体TFT 173包括两个源/漏区(未示出)和源/漏区之间的沟道区(未示出)。源/漏区是与源/漏极175和177接触的部分。源/漏极175和177设置在第二绝缘层119的上方并与其接触。源/漏极175和177与包括其任一端的第二氧化物半导体膜173的部分接触。

第一氧化物半导体膜133和第二氧化物半导体膜173被层间介电(ILD)层或层间绝缘层121覆盖。层间绝缘层121可以由无机或有机材料制成。像素电极181设置在层间绝缘层121的上方并与其接触,并且通过层间绝缘层121中的过孔中设置的通孔与第二氧化物半导体TFT 170的源/漏极177连接。像素电极181可以由铟锡氧化物(ITO)制成。

绝缘基底层115设置在绝缘衬底113上方并与其接触;两个栅极131、171和第一绝缘层117设置在基底层115上方并与其接触。栅极131和171是包含在同一金属层中的部分。可以理想地选择用于栅极131和171的材料;栅电极131和171可以是单层的Mo、W、Nb、Al、Ta、Cr、Ti,从这些材料中选择的金属层叠或从这些材料中选择的金属合金。栅极131和171用第一绝缘层117完全覆盖。

第一氧化物半导体TFT 130和第二氧化物半导体TFT 170的源/漏极135、137、175和177是包含在同一金属层中的部分。源/漏极135、137、175和177可以通过沉积和图案化Ti/Al/Ti或Mo/Al/Mo的导电膜来制备。源/漏极135、137、175和177可以具有单层结构或由不同于这些金属的金属制成。

TFT衬底的制造方法

描述了图2中示出的制造TFT衬底100的方法的示例。如图3A中所示,制造TFT衬底100的方法通过CVD在绝缘衬底113上形成厚度约为100nm的基底层115。接下来,该方法在基底层115上形成包括栅极131和171的金属层(栅极层)。具体地,该方法通过溅射形成厚度约为300nm的金属膜,并且通过光刻和刻蚀而图案化金属膜。此外,该方法通过CVD形成厚度约300nm的第一绝缘层117以覆盖栅极层。

接下来,如图3B中所示,该方法在第一绝缘层117上形成包括第一氧化物半导体膜133的氧化物半导体层(第一氧化物半导体层)。具体地,该方法通过溅射形成约50nm厚的氧化物半导体层,并且通过光刻和刻蚀而图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。

接下来,如图3C中所示,该方法通过CVD形成厚度约为100nm的第二绝缘层119以覆盖第一氧化物半导体膜133。接下来,如图3D中所示,该方法在第二绝缘层119上形成包括第二氧化物半导体膜173的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成约50nm厚的氧化物半导体层,并且通过光刻和刻蚀而图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。

接下来,如图3E中所示,该方法通过光刻和刻蚀在第二绝缘层119中打开开口120。形成开口120以将第一氧化物半导体膜133的顶面暴露在开口中。尽管在本示例中第一氧化物半导体膜133的端面未暴露在开口120中,但它们可以暴露。

接下来,如图3F中所示,该方法通过溅射形成厚度约为300nm的金属层(源/漏电层)140。金属层140包括源/漏极135、137、175和177,并且覆盖第二绝缘层119、第一氧化物半导体膜133和第二氧化物半导体膜173。金属层140填充设置在第二绝缘层119中的开口120并且接触第一氧化物半导体膜133的顶面。接下来,如图3G中所示,该方法通过光刻和刻蚀图案化金属层140,以形成源/漏极135、137、175和177。

接下来,如图3H中所示,该方法通过CVD形成厚度约400nm的层间绝缘层121,以覆盖源/漏极135、137、175、177、第一氧化物半导体膜133和第二氧化物半导体膜173,并且通过光刻和刻蚀在层间绝缘层121中打开过孔,以暴露源/漏极177的顶面的一部分。此外,该方法在层间绝缘层121上形成像素电极181、以及用于连接像素电极181和层间绝缘层121中的源/漏极177的通孔。具体地,该方法通过溅射形成厚度约为50nm的ITO膜,并且通过光刻和刻蚀图案化ITO膜。

如图3D中所示,在形成第二氧化物半导体膜173时,第一氧化物半导体膜133用第二绝缘层119覆盖。因此,第一氧化物半导体膜133不受形成和图案化第二氧化物半导体膜173的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜133和第二氧化物半导体膜173。

实施例2

TFT衬底的构造

在下文中,描述了TFT衬底的另一构造示例和制造TFT衬底的方法。图4示意性地示出了用于液晶显示面板的另一TFT衬底200的构造示例的截面。在下文中,主要描述了与图2中所示的构造示例的区别。

TFT衬底200包括外围电路区域210中的第一氧化物半导体TFT 230和显示区域150中的第二氧化物半导体TFT 170。第二氧化物半导体TFT 170的构造与图2中的构造相同。除了图2中的第一氧化物半导体TFT 130的构造之外,第一氧化物半导体TFT 230还包括刻蚀停止膜233。刻蚀停止膜233被设置为与第一氧化物半导体膜133接触。刻蚀停止膜233位于源/漏极135和137之间以及第一氧化物半导体膜133的沟道区上方。

刻蚀停止膜233是第二绝缘层219的一部分。刻蚀停止膜233防止氧化物半导体膜133的沟道区在刻蚀用于氧化物半导体膜133与源/漏极135和137之间的接触的第二绝缘层219的过程中暴露于刻蚀剂。

TFT衬底的制造方法

描述了图4中示出的制造TFT衬底200的方法的示例。如图5A中所示,制造TFT衬底200的方法通过CVD在绝缘衬底113上形成基底层115。接下来,该方法在基底层115上形成包括栅极131和171的金属层(栅极层)。具体地,该方法通过溅射形成金属膜,并且通过光刻和刻蚀图案化金属膜。此外,该方法通过CVD形成第一绝缘层117以覆盖栅极层。

接下来,如图5B中所示,该方法在第一绝缘层117上形成包括第一氧化物半导体膜133的氧化物半导体层(第一氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体层,并且通过光刻和刻蚀图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。

接下来,如图5C中所示,该方法通过CVD形成第二绝缘层219以覆盖第一氧化物半导体膜133。接下来,如图5D中所示,该方法在第二绝缘层219上形成包括第二氧化物半导体膜173的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体层,并且通过光刻和刻蚀图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。

接下来,如图5E中所示,该方法通过光刻和刻蚀在第二绝缘层219中打开开口235和236。开口235用于源/漏极135与第一氧化物半导体膜133之间的接触,而开口236用于源/漏极137与第一氧化物半导体膜133之间的接触。形成开口235和236以将第一氧化物半导体膜133的顶面暴露在开口中。作为形成开口235和236的结果,制备蚀刻停止膜233。尽管在第一氧化物半导体膜133的端面未暴露在开口235和236中,但它们可以暴露。

接下来,如图5F中所示,该方法通过溅射形成包括源/漏极135、137、175和177的金属层(源/漏电层)140。金属层140覆盖第二绝缘层219和第二氧化物半导体膜173。金属层140填充第二绝缘层219中的开口235和236并且接触第一氧化物半导体膜133的顶面。接下来,如图5G中所示,该方法通过光刻和刻蚀图案化金属层140,以形成源/漏极135、137、175和177。

接下来,如图5H中所示,该方法通过CVD形成层间绝缘层121,以覆盖源/漏极135、137、175、177,刻蚀停止膜233和第二绝缘层219,并且通过光刻和刻蚀在层间绝缘层121中打开过孔,以暴露源/漏极177的顶面的一部分。此外,该方法在层间绝缘层121上形成像素电极181、以及用于连接像素电极181和层间绝缘层121中的源/漏极177的通孔。具体地,该方法通过溅射形成ITO膜,并且通过光刻和刻蚀图案化ITO膜。

如图5D中所示,在形成第二氧化物半导体膜173时,第一氧化物半导体膜133用第二绝缘层219覆盖。因此,第一氧化物半导体膜133不受形成和图案化第二氧化物半导体膜173的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜133和第二氧化物半导体膜173。

实施例3

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例和制造TFT衬底的方法。图6示意性地示出了用于液晶显示面板的另一TFT衬底300的构造示例的截面。图6示出了在TFT衬底300的显示区域350中的一个第一氧化物半导体TFT 370和在TFT衬底300的外围电路区域310中的一个第二氧化物半导体TFT 330。外围电路区域310位于比显示区域350更靠外部,并且是安装外围电路的区域。显示区域350是包括像素的区域。图6省略了覆盖第一氧化物半导体TFT370和第二氧化物半导体TFT 330的像素电极和层间绝缘层。

第一氧化物半导体TFT 370是用于选择像素以供应数据信号的开关TFT。第二氧化物半导体TFT 330可以是扫描驱动器中的氧化物半导体TFT。第一氧化物半导体TFT 370和第二氧化物半导体TFT 330具有顶栅结构。

第一氧化物半导体TFT 370和第二氧化物半导体TFT 330制造在由树脂或玻璃制成的柔性或非柔性的绝缘衬底313上。第一氧化物半导体TFT 370的氧化物半导体膜(第一氧化物半导体膜)373和第二氧化物半导体TFT 330的氧化物半导体膜(第二氧化物半导体膜)333由不同的氧化物半导体材料制成,具有不同的特性。在该示例中,第二氧化物半导体膜333的迁移率高于第一氧化物半导体膜173的迁移率,并且第一氧化物半导体膜373的带隙比第二氧化物半导体膜333的带隙更宽。由于两种氧化物半导体膜在特性上的差异,两种膜都实现了窄边框和高可靠性。

可以用于第二氧化物半导体膜333的氧化物半导体材料的示例包括ITZO、IGZTO、In-Zn-Ti-O和In-W-Z-O。可以用于第一氧化物半导体膜373的氧化物半导体材料的示例包括IGZO、GaZnO和IGO。

第二氧化物半导体TFT 330的氧化物半导体膜(第二氧化物半导体膜)333设置在第二绝缘层中包括的绝缘膜317的上方并与其接触。包括绝缘膜317的第二绝缘层位于比第一绝缘层315更靠上部。第一氧化物半导体TFT 370的氧化物半导体膜(第一氧化物半导体膜)373设置在第一绝缘层315的上方并与其接触。第一绝缘层315是基底层。第二氧化物半导体膜333位于比第一氧化物半导体膜373更靠上部。第一绝缘层315和包括第二绝缘膜317的第二绝缘层可以由氮化硅或氧化硅制成。

在图6中的构造示例中,在绝缘膜317的上方并与其接触设置有整个第二氧化物半导体膜333,并且在第一绝缘层315的上方并与其接触设置有整个第一氧化物半导体膜373。包括绝缘膜317的第二绝缘层设置在第一绝缘层315的上方并与其接触。第二氧化物半导体膜333和包括绝缘膜317的第二绝缘层均设置在第一绝缘层315的上方并与其接触。

第二氧化物半导体TFT 330包括第二氧化物半导体膜333、位于比第二氧化物半导体膜333更靠上部的栅极331和位于栅极331与第二氧化物半导体膜333之间的栅极绝缘膜339(在层结构方向中)。

第二氧化物半导体膜333包括源/漏区334和336和源/漏区334和336之间的沟道区332。源/漏区334和336为低电阻区,而沟道区332为电阻未降低的区域,即高电阻区。栅极绝缘膜339设置在沟道区332的上方并与其接触。栅极331设置在栅极绝缘膜339上方并与其接触。

源/漏极335和337设置在层间绝缘层321的上方并与其接触。源/漏极335和337通过设置在层间绝缘层321中的通孔340和341与源/漏区334和336连接。通孔340和341从源/漏极335和337继续,并且设置在源/漏区334和336上方并与其接触。

第一氧化物半导体TFT 370包括第一氧化物半导体膜373、位于比第一氧化物半导体膜373更靠上部的栅极371和具有包括绝缘膜378和379的层叠结构的设置在栅极371与第一氧化物半导体膜373之间的栅极绝缘膜(在层结构方向中)。

第一氧化物半导体膜373包括源/漏区374和376和源/漏区374和376之间的沟道区372。源/漏区374和376为低电阻区,而沟道区372为电阻未降低的区域,即高电阻区。更下部的栅极绝缘膜378设置在沟道区372的上方并与其接触。更下部的栅极绝缘膜378是第二绝缘层(例如绝缘膜317)的一部分。更上部的栅极绝缘膜379是与绝缘膜339相同绝缘层的一部分。栅极371设置在栅极绝缘膜379的上方并与其接触。

源/漏极375和377设置在层间绝缘层321的上方并与其接触。源/漏极375和377通过设置在层间绝缘层321中的通孔380和381与源/漏区374和376连接。通孔380和381从源/漏极375和377继续,并且设置在源/漏区374和376上方并与其接触。

层间绝缘层321覆盖除第二氧化物半导体TFT 330和第一氧化物半导体TFT 370的源/漏极335、337、375和377之外的组成元件。层间绝缘层321可以由氧化硅或氮化硅制成。包括绝缘膜339和379的绝缘层(第三绝缘层)可以由氧化硅或氮化硅制成。

栅极331和371是包含在同一金属层中的部分。例如,栅极331和371的材料可以理想地从Mo、W、Nb和Al中选择。第二氧化物半导体TFT 330和第一氧化物半导体TFT 370的源/漏极335、337、375和377是包含在同一金属层中的部分。源/漏极335、337、375和377可以通过沉积和图案化(例如)Ti/Al/Ti的导电膜来制备。源/漏极335、337、375和377可以具有单层结构或由不同于这些金属的金属制成。

TFT衬底的制造方法

描述了图6中示出的制造TFT衬底300的方法的示例。如图7A中所示,制造TFT衬底300的方法通过CVD在绝缘衬底313上形成基底层的第一绝缘层315。接下来,该方法在第一绝缘层315上形成包括第一氧化物半导体膜373的氧化物半导体层(第一氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体膜,并且通过光刻和刻蚀图案化氧化物半导体膜。作为结果,形成氧化物半导体膜的图案。

接下来,如图7B中所示,该方法通过CVD形成第二绝缘层318以覆盖第一氧化物半导体膜373。第二绝缘层318包括图6中的绝缘膜317和378。

接下来,如图7C中所示,该方法在第二绝缘层318上形成包括第二氧化物半导体膜333的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体膜,并且通过光刻和刻蚀图案化氧化物半导体膜。作为结果,形成氧化物半导体膜的图案。

接下来,如图7D中所示,该方法通过CVD形成第三绝缘层319以覆盖第二氧化物半导体膜333和第二绝缘层318。第三绝缘层319包括图6中的绝缘膜339和379。此外,该方法在第三绝缘层319上通过溅射形成包括栅极331和371的金属层(栅极层)320。

接下来,如图7E所示,该方法将第二绝缘层318、第三绝缘层319和栅极层320一起刻蚀以制备绝缘膜339、317,绝缘膜379、378和栅极331、371。接下来,如图7F所示,通过将这些部分暴露于He等离子体中,该方法降低了在第二氧化物半导体膜333中未被栅极绝缘膜339覆盖的部分和在第二氧化物半导体膜373中未被栅极绝缘膜378覆盖的部分的电阻。作为结果,制备了源/漏区334、336、374和376。

接下来,如图7G所示,该方法通过CVD形成层间绝缘层321,以覆盖所制备的第一氧化物半导体TFT 370的组成元件、所制备的第二氧化物半导体TFT 330的组成元件以及第一绝缘层315。接下来,如图7H所示,该方法通过光刻和刻蚀在层间绝缘层321中打开过孔,进一步制备源/漏极335、337、375、377和通孔340、341、380、381。具体地,该方法通过溅射在层间绝缘层321(包括过孔内)上形成金属层并通过光刻和刻蚀形成源/漏极335、337、375、377和通孔340、341、380、381。这里省略以下用于覆盖第一氧化物半导体TFT 370和第二氧化物半导体TFT 330以及像素电极的层间绝缘层的形成的描述。

如图7C中所示,在形成第二氧化物半导体膜333时,第一氧化物半导体膜373被第二绝缘层318覆盖。因此,第一氧化物半导体膜373不受形成和图案化第二氧化物半导体膜333的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜373和第二氧化物半导体膜333。

实施例4

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例和制造TFT衬底的方法。图8示意性地示出了用于液晶显示面板的另一TFT衬底400的构造示例的截面。在下文中,主要描述了与图2中所示的构造示例的区别。

TFT衬底400包括外围电路区域110中的第一氧化物半导体TFT 130和显示区域450中的第二氧化物半导体TFT 470。第一氧化物半导体TFT 130的构造与图2中的构造相同。在图2所示的构造示例中,第二氧化物半导体TFT 470在第二氧化物半导体膜473、栅极绝缘膜472和源/漏极475、477的形状上与第二氧化物半导体TFT 170不同。

设置在第一绝缘层117的上方并与其接触的第二绝缘层419具有开口;第二氧化物半导体膜473的一部分设置在开口中。第二氧化物半导体膜473在第二绝缘层419的开口内与第一绝缘层117接触。包括其端部的第二氧化物半导体膜473的一部分位于第二绝缘层419的上方。从该描述可知,第二氧化物半导体膜473部分地位于第二绝缘层419的上方并与其接触,并且部分地位于第一绝缘层117的上方并与其接触。

第一绝缘层117是位于比第二氧化物半导体膜473更靠下部且与其接触的绝缘层中的最下面的绝缘层。第二绝缘层419是位于比第二氧化物半导体膜473更靠下部且与其接触的绝缘层中的最上面的绝缘层。

栅极绝缘膜472具有单层结构并且是第一绝缘层117的一部分。薄化栅极绝缘膜472增强了第二氧化物半导体TFT 470的驱动能力。每个源/漏极475和477与第二绝缘层419上的第二氧化物半导体膜473的一部分和开口中的第二氧化物半导体膜473的一部分接触。这种接触结构在第二氧化物半导体膜473和源/漏极475、477之间实现低接触电阻。

TFT衬底的制造方法

描述了图8中示出的制造TFT衬底400的方法的示例。在执行参照图3A和3B所述的步骤之后,如图9A所示,该方法通过CVD形成第二绝缘层419以覆盖第一氧化物半导体膜133。

接下来,如图9B中所示,该方法通过光刻和刻蚀在第二绝缘层419中打开开口420。第一绝缘层117的顶面暴露在开口420中。接下来,如图9C中所示,该方法在第二绝缘层419上形成包括第二氧化物半导体膜473的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体层,并且通过光刻和刻蚀图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。第二氧化物半导体膜473的一部分位于第二绝缘层419的开口420中,并且包括其端部的另一部分位于第二绝缘层419的上方并与其接触。

接下来,如图9D中所示,该方法通过光刻和刻蚀在第二绝缘层419中打开开口421。形成开口421以将第一氧化物半导体膜133的顶面暴露在开口内。在该示例中,在第一氧化物半导体膜133的端面未暴露在开口421中,但是可以被暴露。

接下来,如图9E中所示,该方法通过溅射形成包括源/漏极135、137、475和477的金属层(源/漏极层)440。金属层440覆盖第二绝缘层419、第一氧化物半导体膜133和第二氧化物半导体膜473。金属层440填充第二绝缘层419中的开口421并且接触第一氧化物半导体膜133的顶面。接下来,如图9F中所示,该方法通过光刻和刻蚀图案化金属层440,以形成源/漏极135、137、475和477。

接下来,如图9G所示,该方法通过CVD形成层间绝缘层121,以覆盖源/漏极135、137、475、477,第一氧化物半导体膜133,第二氧化物半导体膜473和第二绝缘层419,并通过光刻和刻蚀在层间绝缘层121中进一步打开过孔以暴露源/漏极477顶面的一部分。此外,该方法在层间绝缘层121上形成像素电极181、以及用于连接像素电极181和层间绝缘层121中的源/漏极477的通孔。具体地,该方法通过溅射形成ITO膜,并且通过光刻和刻蚀图案化ITO膜。

如图9C中所示,在形成第二氧化物半导体膜473时,第一氧化物半导体膜133被第二绝缘层419覆盖。因此,第一氧化物半导体膜133不受形成和图案化第二氧化物半导体膜473的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜133和第二氧化物半导体膜473。

第一氧化物半导体TFT连同或代替第二氧化物半导体TFT,可具有类似于第二氧化物半导体TFT 470的结构。例如,可以在第一绝缘层和第二绝缘层之间设置具有开口的第三绝缘层。第一氧化物半导体TFT的第一氧化物半导体膜以一部分位于第三绝缘层中的开口内的第一绝缘层的上方并与其接触且另一部分位于开口外的第三绝缘层的上方并与其接触的方式形成。第三绝缘层是位于比第一氧化物半导体膜更靠下部且与其接触的绝缘层中的最上面的绝缘层。

实施例5

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例和制造TFT衬底的方法。图10示意性地示出了用于液晶显示面板的另一TFT衬底500的构造示例的截面。在下文中,主要描述了与图2中所示的构造示例的区别。

TFT衬底500包括外围电路区域110中的第一氧化物半导体TFT 130和显示区域550中的第二氧化物半导体TFT 570。第一氧化物半导体TFT 130的构造与图2中的构造相同。在图2所示的构造示例中,第二氧化物半导体TFT 570在第二氧化物半导体膜573、栅极绝缘膜572和源/漏极575、577的形状上与第二氧化物半导体TFT 170不同。

设置在第一绝缘层117的上方并与其接触的第二绝缘层519具有开口。在开口中设置第二氧化物半导体膜573。第二氧化物半导体膜573在第二绝缘层519中的开口内与第一绝缘层117接触。第二氧化物半导体膜573的端部远离开口的内壁。

栅极绝缘膜572具有单层结构并且是第一绝缘层117的一部分。薄化栅极绝缘膜572增强了第二氧化物半导体TFT 570的驱动能力。源/漏极575和577与包括其该端的第二氧化物半导体膜573的部分接触。源/漏极575和577与第二氧化物半导体膜573的端面和顶面接触。这种接触结构在第二氧化物半导体膜573和源/漏极575、577之间实现低接触电阻。

TFT衬底的制造方法

描述了图10中示出的制造TFT衬底500的方法的示例。在执行参照图3A和3B所述的步骤之后,如图11A所示,该方法通过CVD形成第二绝缘层519以覆盖第一氧化物半导体膜133。

接下来,如图11B中所示,该方法通过光刻和刻蚀在第二绝缘层519中打开开口520。第一绝缘层117的顶面暴露在开口520中。接下来,如图11C中所示,该方法在第二绝缘层519上形成包括第二氧化物半导体膜573的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体层,并且通过光刻和刻蚀图案化氧化物半导体层。作为结果,形成氧化物半导体膜的图案。第二氧化物半导体膜573在第二绝缘层519的开口520内设置在第一绝缘层117的上方并与其接触。

接下来,如图11D中所示,该方法通过光刻和刻蚀在第二绝缘层519中打开开口521。形成开口521以将第一氧化物半导体膜133的顶面暴露在开口内。在该示例中,第一氧化物半导体膜133的端面未暴露在开口521中,但是可以被暴露。

接下来,如图11E中所示,该方法通过溅射形成包括源/漏极135、137、575和577的金属层(源/漏电层)540。金属层540覆盖第二绝缘层519、第一氧化物半导体膜133和第二氧化物半导体膜573。金属层540填充第二绝缘层519中的开口521并且接触第一氧化物半导体膜133的顶面。接下来,如图11F中所示,该方法通过光刻和刻蚀图案化金属层540,以形成源/漏极135、137、575和577。

接下来,如图11G所示,该方法通过CVD形成层间绝缘层121,以覆盖源/漏极135、137、575、577,第一氧化物半导体膜133,第二氧化物半导体膜573和第二绝缘层519,并通过光刻和刻蚀在层间绝缘层121中进一步打开过孔以暴露源/漏极577顶面的一部分。此外,该方法在层间绝缘层121上形成像素电极181、以及用于连接像素电极181和层间绝缘层121中的源/漏极577的通孔。具体地,该方法通过溅射形成ITO膜,并且通过光刻和刻蚀图案化ITO膜。

如图11C中所示,在形成第二氧化物半导体膜573时,第一氧化物半导体膜133被第二绝缘层519覆盖。因此,第一氧化物半导体膜133不受形成和图案化第二氧化物半导体膜573的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜133和第二氧化物半导体膜573。

实施例6

在显示区域(像素电路)中,具有宽带隙的氧化物半导体TFT占TFT的大多数(超过一半),以获得高可靠性。在外围电路中,具有高迁移率的氧化物半导体TFT占小电路尺寸的大多数(超过一半)。然而,显示区域中的一些氧化物半导体TFT可以是具有高迁移率的氧化物半导体TFT,并且外围电路中的一些氧化物半导体TFT可以是具有宽带隙的氧化物半导体TFT,这取决于单个氧化物半导体TFT所需的特性。

预期主要接收负栅极偏置(栅极电压)的氧化物半导体TFT可以通过采用具有宽带隙的氧化物半导体TFT来获得高可靠性。相比之下,预期主要接收正栅极偏置的氧化物半导体TFT可以通过采用具有高迁移率的氧化物半导体TFT来贡献小电路尺寸。

向主要接收负栅极偏置的氧化物半导体TFT供应负栅极偏置的时间长于在装置的工作时间期间供应正栅极偏置的时间。负栅极偏置关闭氧化物半导体TFT,而正栅极偏置打开氧化物半导体TFT。零栅极偏置既不是负栅极偏置也不是正栅极偏置。

如果TFT需要高驱动能力,则外围电路中的TFT通过采用具有高迁移率的氧化物半导体TFT来实现小电路尺寸;如果不需要这样的高驱动能力,则外围电路中的TFT通过采用具有宽带隙的氧化物半导体TFT来实现高可靠性。

在外围电路中,用于静电放电保护元件的TFT或测试TFT是二极管连接的TFT或具有用作高电阻元件的浮动栅极的TFT。这种TFT不需要很高的驱动能力,如果驱动能力太高,TFT就会干扰外围电路的整体工作。因此,具有宽带隙的氧化物半导体TFT可以用作静电放电保护元件或测试TFT。

图12示出了移位寄存器的一级电路的示例。移位寄存器包括晶体管TR1到TR9和电容器CA1和CA2。电位VGH为高供电电位,并且电位VGL为低供电电位。信号ST是开始脉冲或前一级的输出。信号OUT1是输出。信号OUT2是来自下一级的反馈信号。信号RST是复位信号。信号CK是时钟信号并且信号XCK是反转时钟信号。

在图12所示的电路中,晶体管TR1是主要接收负栅极偏置的晶体管。因此,晶体管TR1可以通过采用具有宽带隙的氧化物半导体TFT具有高可靠性。另一方面,晶体管TR2到TR9是主要接收负栅极偏置的晶体管。因此,通过将具有高迁移率的氧化物半导体TFT用于这些晶体管TR2至TR9,可以实现较小的电路尺寸。特别地,晶体管TR6是用于输出到下一级的驱动晶体管和数据线;将具有高迁移率的氧化物半导体TFT用于晶体管TR6有效地有助于减小电路的尺寸。

图13示出了用于OLED显示装置的像素电路的示例。像素电路控制供给OLED元件E1的阳极的电流。像素电路包括驱动晶体管T1、选择晶体管T2、控制晶体管T3和存储电容器C1。像素电路控制OLED元件E1的光发射。图13的示例中的晶体管T1到T3是n沟道型的氧化物半导体TFT。

选择晶体管T2是用于选择像素的开关。选择晶体管T2的栅极端子接收扫描信号S1。其源/漏端子之一与数据线15连接。另一源/漏端子与驱动晶体管T1的栅极端子连接。

驱动晶体管T1是用于驱动OLED元件E1的晶体管。驱动晶体管T1的栅极端子与选择晶体管T2的源/漏端子连接。驱动晶体管T1的源/漏端子之一与电力线(Vdd)18连接。另一源/漏端子与控制晶体管T3的源极端子连接。存储电容器C1设置于驱动晶体管T1的栅极端子和源/漏端子之间。

当选择晶体管T2导通时,通过数据线15供应的数据电压被存储到存储电容器C1。在一帧的周期期间,存储电容器C1保存所存储的电压。驱动晶体管T1的电导率根据所存储的电压以模拟方式改变,使得驱动晶体管T1向OLED元件E1供应对应于光发射电平的正向偏置电流。

控制晶体管T3控制用于供应参考电压Vref的参考电压供应线11与OLED元件E1的阳极之间的电连接。控制信号S2被供应给用于该控制的控制晶体管T3的栅极端子。控制晶体管T3可以用于各种用途。控制晶体管T3可以用于将OLED元件E1的阳极复位一次,使其具有低于黑色信号电平的足够低的电压,以阻止泄漏电流引起OLED元件E1之间的串扰。

控制晶体管T3还可以用于测量驱动晶体管T1的特性。例如,在选择的偏置条件下,通过测量从电源线18流向参考电压供应线11的电流,可以精确地测量驱动晶体管T1的电压电流特性,使得驱动晶体管T1在饱和区域工作,并且控制晶体管T3在线性区域工作。如果通过在外部电路处生成数据信号来补偿用于单个像素的驱动晶体管T1之间的电压-电流特性的差异,则可以获得高度均匀的显示图像。

同时,当驱动晶体管T1截止并且控制晶体管T3在线性区域中工作时,通过施加电压以从参考电压供应线11点亮OLED元件E1,可以精确地测量OLED元件E1的电压电流特性。在OLED元件E1由于长期使用而劣化的情况下,例如,如果通过在外部电路处生成数据信号来补偿劣化,则显示装置可以具有长寿命。

在图13的像素电路中,晶体管T2和T3采用具有宽带隙的氧化物半导体TFT。这些晶体管主要由负栅极偏置供应,并展现出高可靠性。另一方面,驱动晶体管T1采用具有高迁移率的氧化物半导体TFT。驱动晶体管T1主要由正栅极偏置供应,并且有助于减小晶体管尺寸。在液晶显示面板中,用于控制到像素电极的信号输入的开关TFT采用具有宽带隙的氧化物半导体TFT。开关TFT主要由负栅极偏置供应,并展现出高可靠性。

如上所述,通过在具有宽带隙的氧化物半导体TFT和具有高迁移率的氧化物半导体TFT之间的适当选择,显示装置获得了高可靠性和窄边框。

实施例7

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例。图14示意性地示出了用于液晶显示面板的另一TFT衬底600的构造示例的截面。在下文中,主要描述了与图2中所示的构造示例的区别。

TFT衬底600包括外围电路区域110中的第一氧化物半导体TFT 130和电容器CA 10以及显示区域150中的第二氧化物半导体TFT 170。第一氧化物半导体TFT 130和第二氧化物半导体TFT 170具有与图2中所示的相应的构造相同的构造,并且与图2的区别在于添加了电容器CA 10。

电容器CA 10由栅极131、设置在栅极131上方的第一绝缘层117和设置在第一绝缘层117上方的第一氧化物半导体膜133构成。第一氧化物半导体膜133在第二绝缘层119中设置的开口中与源/漏极137接触。

第一绝缘层117是第一氧化物半导体TFT 130的栅极绝缘膜。该栅极绝缘膜比第一绝缘层117和第二绝缘层119的层叠的第二氧化物半导体TFT 170的栅极绝缘膜薄,因此,它可以具有更大的电容。因此,可以使电容器CA 10的面积变小。

图14所示的TFT衬底600可以通过与图3A至3H所示的相同步骤来制造,并且因此,此处省略制造方法的说明。

实施例8

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例。图15示意性地示出了用于液晶显示面板的另一TFT衬底700的构造示例的截面。在下文中,主要描述了与图6中所示的构造示例的区别。

TFT衬底700包括外围电路区域310中的第二氧化物半导体TFT 330和电容器CA 20以及显示区域350中的第一氧化物半导体TFT 370。第一氧化物半导体TFT 370和第二氧化物半导体TFT 330具有与图6中所示的相应的构造相同的构造,并且与图6的区别在于添加了电容器CA 20。

电容器CA 20由设置在第一绝缘层315上方的第一氧化物半导体膜342、第二绝缘层的一部分的绝缘膜317和设置在绝缘膜317上方的第二氧化物半导体膜343组成。第一氧化物半导体膜342由与第一氧化物半导体膜373相同的材料制成,并且像源/漏区374和376一样减小电阻以成为电容器CA 20的一个电极。第二氧化物半导体膜343由与第二氧化物半导体膜333相同的材料制成,并且像源/漏区334和336一样减小电阻以成为电容器CA 20的其他电极。此外,第一氧化物半导体膜342经由通孔344与电容器线345连接,并且第二氧化物半导体膜343经由通孔346与电容器线347连接。

绝缘膜317比第二氧化物半导体TFT 330的栅极绝缘膜339薄。作为结果,与将下栅极绝缘膜378和上栅极绝缘膜379的层叠作为第一氧化物半导体TFT 370的栅极绝缘膜使用的情况或使用第二氧化物半导体TFT 330的栅极绝缘膜339的情况相比,电容器CA 20可以具有薄的绝缘膜,并且因此,电容器CA 20可以存储更多的电荷。因此,可以使电容器CA 20的面积变小。

TFT衬底的制造方法

描述了图15中示出的制造TFT衬底700的方法的示例。如图16A中所示,制造TFT衬底700的方法通过CVD在绝缘衬底313上形成基底层的第一绝缘层315。接下来,该方法在第一绝缘层315上形成包括第一氧化物半导体膜373的氧化物半导体层(第一氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体膜,并且通过光刻和刻蚀图案化氧化物半导体膜。作为结果,形成氧化物半导体膜的图案。

接下来,该方法通过光刻形成抗蚀图案799,以覆盖除第一氧化物半导体膜373之外的区域,其中提供如图16B所示的电容器,并且进一步将衬底暴露于He等离子体以降低第一氧化物半导体膜373的电阻。作为结果,制备了第一氧化物半导体膜342作为电容器CA20的电极。

在移除抗蚀图案799之后,如图16C所示,该方法通过CVD形成第二绝缘层318以覆盖包括第一氧化物半导体膜373和342的层。第二绝缘层318包括图15中的绝缘膜317和378。

接下来,如图16D中所示,该方法在第二绝缘层318上形成包括第二氧化物半导体膜333的氧化物半导体层(第二氧化物半导体层)。具体地,该方法通过溅射形成氧化物半导体膜,并且通过光刻和刻蚀图案化氧化物半导体膜。作为结果,形成氧化物半导体膜的图案。

接下来,如图16E中所示,该方法通过CVD形成第三绝缘层319以覆盖第二氧化物半导体膜333和第二绝缘层318。第三绝缘层319包括图15中的绝缘膜339和379。此外,该方法在第三绝缘层319上通过溅射形成包括栅极331和371的金属层(栅极层)320。

接下来,如图16F所示,该方法将第二绝缘层318、第三绝缘层319和栅极层320一起刻蚀以制备绝缘膜339、317,绝缘膜379、378和栅极331、371。接下来,如图16G所示,通过将这些部分暴露于He等离子体中,该方法降低了在第二氧化物半导体膜333中未被栅极绝缘膜339覆盖的部分和在第一氧化物半导体膜373未被栅极绝缘膜378覆盖的部分的电阻。作为结果,制备了作为电容器CA20的另一电极的源/漏区334、336、374、376和第二氧化物半导体膜343。

接下来,如图16H所示,该方法通过CVD形成层间绝缘层321,以覆盖所制备的第一氧化物半导体TFT 370的组成元件、所制备的第二氧化物半导体TFT 330的组成元件、所制备的电容器CA20的组成元件和第一绝缘层315。

接下来,如图16I所示,该方法通过光刻和刻蚀在层间绝缘层321中打开通孔,并且进一步制备源/漏极335、337、375、377,电容器线345、347和过孔340、341、380、381、344、346。具体地,该方法通过溅射在层间绝缘层321(包括通孔内)上形成金属层,并通过光刻和刻蚀形成源/漏极335、337、375、377,电容器线345、347和过孔340、341、380、381、344、345。这里省略以下用于覆盖第一氧化物半导体TFT 370和第二氧化物半导体TFT 330以及像素电极的层间绝缘层的形成的描述。

如图16D中所示,在形成第二氧化物半导体膜333时,第一氧化物半导体膜373被第二绝缘层318覆盖。因此,第一氧化物半导体膜373不受形成和图案化第二氧化物半导体膜333的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜373和第二氧化物半导体膜333。

实施例9

TFT衬底的构造

在下文中,描述了TFT衬底的又一构造示例。图17示意性地示出了用于顶发射型OLED显示装置的TFT衬底800的像素区域的构造示例的截面。

TFT衬底800包括用于向OLED提供电流的驱动TFT、存储电容器CA 30和用于向驱动TFT发送信号的开关TFT。开关TFT对应于图17中的第一氧化物半导体TFT 370,并且驱动TFT对应于第二氧化物半导体TFT 330。第一氧化物半导体TFT 370和第二氧化物半导体TFT330具有图6中所示的相应的构造相同的构造。

电容器CA 30由在第一绝缘层315上方形成的第一氧化物半导体膜373的一部分、在第一氧化物半导体膜373上方形成的第二绝缘层的一部分的绝缘膜317和在绝缘膜317上方形成的第二氧化物半导体膜333的一部分组成。包括在电容器CA 30中的第一氧化物半导体膜373的部分是第一氧化物半导体TFT 370的源/漏区374的延伸。包括在电容器CA 30中的第二氧化物半导体膜333的部分是第二氧化物半导体TFT 330的源/漏区336的延伸。

绝缘膜317比第二氧化物半导体TFT 330的栅极绝缘膜339薄。作为结果,与将下栅极绝缘膜378和上栅极绝缘膜379的层叠作为第一氧化物半导体TFT 370的栅极绝缘膜使用的情况或使用第二氧化物半导体TFT 330的栅极绝缘膜339的情况相比,电容器CA 30可以具有薄的绝缘膜,并且因此,电容器CA 30可以存储更多的电荷。因此,可以使电容器CA 30的面积变小。

第二氧化物半导体TFT 330的栅极331经由通孔390与栅极线391连接。尽管图17中未示出,但是栅线391与第一氧化物半导体TFT 370的源/漏极375连接。

在源/漏极335、337、375、377,栅极391和层间绝缘膜321上方设置平坦化膜392。平坦化膜392可以通过应用具有良好平滑性能的有机材料(例如丙烯酸或聚酰亚胺)来形成。阳极394设置在平坦化膜392的上方。阳极394通过设置在平坦化膜392中的通孔393与第二氧化物半导体TFT 330的源/漏极337连接。阳极394可以是ITO膜和具有高反射率的金属膜(例如铝或银)的层叠。像素定义层395设置在阳极394上方。像素定义层395可以由有机材料例如丙烯酸或聚酰亚胺制成。

图17所示的制造TFT衬底800的方法可以通过图16A到16I中所示的如下相同步骤,制备第一氧化物半导体TFT 370的组成元件、第二氧化物半导体TFT 330的组成元件、电容器CA 30的组成元件和层间绝缘膜321。平坦化膜392的以下形成和随后的处理可以通过已知的成膜技术、光刻技术和刻蚀技术来执行,因此,这里省略详细描述。

如图16D中所示,在形成第二氧化物半导体膜333时,第一氧化物半导体膜373被第二绝缘层318覆盖。因此,第一氧化物半导体膜373不受形成和图案化第二氧化物半导体膜333的影响。因此,可以将理想的氧化物半导体材料用于第一氧化物半导体膜373和第二氧化物半导体膜333。

如以上阐述的,描述了本公开的实施例;然而,本公开并不限于前述实施例。本领域技术人员可以在本公开的范围内容易地修改、增加或改变前述实施例中的每个元件。一个实施例的构造的一部分可以用另一个实施例的构造替换,或者可以将一个实施例的构造合并到另一个实施例的构造中。

- 薄膜晶体管阵列衬底、其制造方法以及包括薄膜晶体管阵列衬底的有机发光显示装置

- 薄膜晶体管衬底、薄膜晶体管的制造方法以及显示装置