一种应用于地铁闸机内的直流续电装置

文献发布时间:2023-06-19 09:41:38

技术领域

本发明涉及适用于地铁领域关键设备续电保障领域,更具体涉及一种应用于地铁闸机内的直流续电装置。

背景技术

随着城市的发展,地铁在越来越多的城市开始普及,常规的地铁安全问题经过多年的发展,基本已经得到保障。近些年,随着数字信息技术的发展,数字信息技术已经渗透到各大领域,城市地铁系统也提出智慧地铁概念,越来越多的智能设备被集成到地铁系统中,这样在传统的地铁系统安全技术之外,这些智能设备的安全可靠性给当前的地铁运行增加了新的风险点。

智能设备的供电可靠性是保障智能设备稳定运行和执行其各项功能的基础,智能设备一般均采用芯片控制,供电电源采用24V、12V或者5V的三种直流电源中某一种供电,正常工作时通过开关电源连接地铁站内供电电源为其供电,为保障安全当前地铁站的供电电源一般采用双电源供电,当主供电电源出现故障时切换到备用电源,由于电力系统切换倒闸需要时间,在该期间内存在短暂的失电空隙,会导致站内相关智能设备断电,断电期间智能设备无法工作,导致受其控制的站内操作设备(闸机,读卡器等)无法工作,如果断电发生在操作设备工作过程中(很大概率,因为地铁相关操作在其工作期间大部分时间均在动作)则会出现闸机卡机等安全事件,需要通过配置后备电源在该期间提供续电支撑,当前地铁系统中智能设备的续电支撑一般通过UPS后备电源来实现,例如,中国专利公开号CN102025187A,公开了一种地铁弱电综合UPS并联系统,由双电源切换箱、UPS主机、智能配电屏和电池模块组成;其中,双电源切换箱,引接变电所的电源给UPS主机;UPS主机,给电池模块充电;智能配电屏,启动UPS主机工作,监控整个系统;电池模块,给系统负载供电。双电源切换箱的输出端电连接两台UPS主机,两台UPS主机统一由智能配电屏监控工作。工作时,两台UPS各分配一半的电池容量,而当其中一台UPS故障时,全部电池组能为另一台正常使用的UPS系统供电,使地铁弱电UPS系统不间断工作。UPS技术成熟,通过蓄电池可以维持对所保护设备一定时间段的应急供电,但是应用于地铁系统时存在以下几种缺点:

(一)蓄电池安全性问题,现有常规UPS基本都是采用铅酸蓄电池,该电池在特定环境下存在火灾的可能,目前已有地铁系统在正常运行时,出现UPS充电冒烟的实际案例。

(二)使用寿命有限,目前基于蓄电池的的UPS系统受制于蓄电池的充放电次数限制,均存在一定使用寿命。

(三)功能单一,仅提供所接智能设备的应急供电功能,用户需要其他的数据信息,通信传输,关联控制均需要通过增加其他控制设备来实现。

综上所述,随着社会朝向数字化智能化的发展,传统的仅满足功能性需求的设备需增加配套其数据处理传输控制功能的设备才能实现数字化和智能化,但这不仅提高系统运行成本,而且多种设备的冗余和协调配合也会增加额外的安全风险。

发明内容

本发明所要解决的技术问题在于现有技术的应用于地铁闸机内的直流续电装置存在安全风险、寿命有限且功能单一的问题。

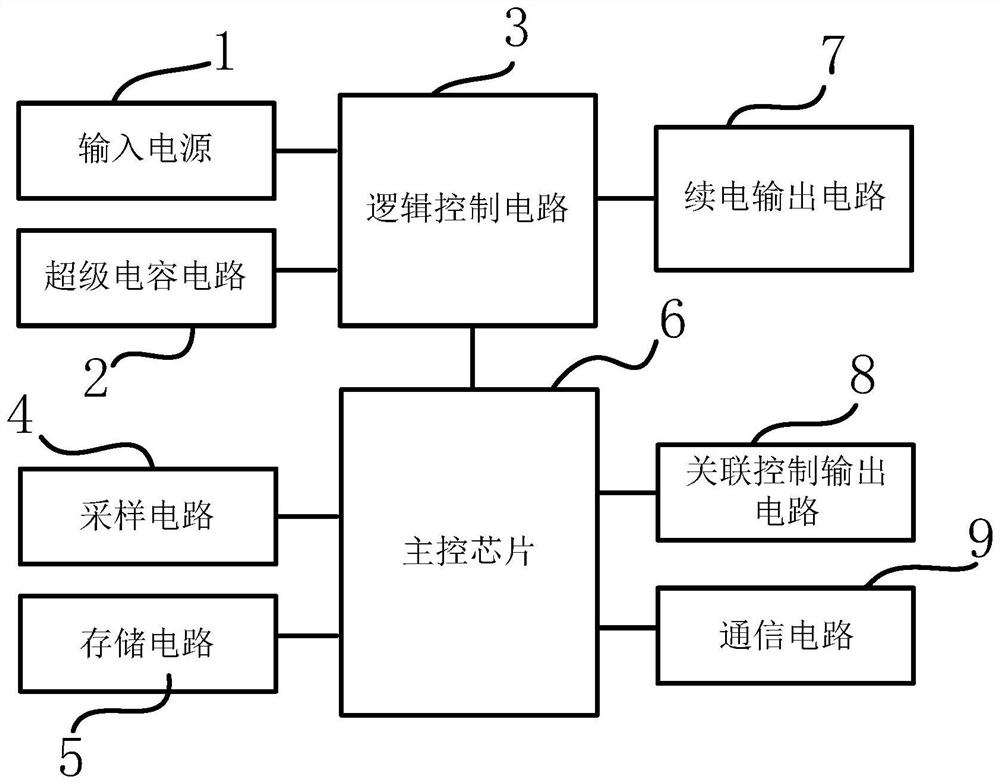

本发明通过以下技术手段实现解决上述技术问题的:一种应用于地铁闸机内的直流续电装置,包括输入电源、超级电容电路、逻辑控制电路、采样电路、存储电路、主控芯片、续电输出电路、关联控制输出电路以及通信电路,所述输入电源、超级电容电路以及续电输出电路均与逻辑控制电路连接,所述逻辑控制电路与主控芯片连接,所述采样电路、存储电路、关联控制输出电路以及通信电路均与主控芯片连接。

本发明逻辑控制电路控制输入电源和超级电容电路工作时的逻辑,正常时,输入电源给电路供电,超级电容电路充满电且无输出,应急供电时,通过逻辑控制电路关断输入电源,投入超级电容作为应急续电电源,通过超级电容进行完成应急供电,避免使用蓄电池而存在安全风险以及寿命有限的问题,同时续电输出电路提供待供电设备的直流电压,关联控制输出电路提供现场关联设备的供电电压,通信电路将续电装置的数据传输到后台,便于工作人员操作和查看,相比现有地铁闸机的续电装置功能较多。

进一步地,所述输入电源包括降压电路和稳压电路,所述降压电路包括二极管D6、二极管D7、电容C19、电容C15、电容C12、电阻R19、电阻R18、电容C14、电容C18、芯片U2、电容C25、电阻R36、电容C24、电阻R25、电阻R26、二极管D10、电感L5、电容C36、电容C35以及电容C39,所述二极管D6的阳极与电源Vin连接,二极管D7的阳极与电源Vsc连接,二极管D6的阴极分别与电容C19的正极、电容C15的一端、二极管D7的阴极、电容C12的一端、电阻R19的一端以及芯片U2的第二引脚连接,电容C19的负极、电容C15的另一端、电容C12的另一端、电阻R18的一端以及电容C14的一端连接并接地,电阻R18的另一端与电阻R19的另一端以及芯片U2的第三引脚连接,电容C14的另一端与芯片U2的第四引脚连接;电容C18的一端与芯片U2的第一引脚连接,电容C18的另一端分别与电感L5的一端、芯片U2的第八引脚以及二极管D10的阴极连接,电感L5的另一端与电容C36的一端、电容C35的一端以及电容C39的正极连接,电容C39的正极作为电源VCC5V的输出端口,芯片U2的第七引脚、二极管D10的阳极、电容C36的另一端、电容C35的另一端以及电容C39的阴极均接地;芯片U2的第六引脚分别与电容C25的一端以及电容C24的一端连接,电容C25的另一端通过电阻R36与电容C24的另一端以及电阻R25的一端连接并接地,电阻R25的另一端分别接芯片U2的第五引脚以及电阻R26的一端,电阻R26的另一端作为电源VCC5V的输出端口;

所述稳压电路包括电容C41、电容C37、芯片U5、电容C40、电容C51以及电容C50,所述电容C41的一端、电容C37的一端以及芯片U5的第三引脚均与电源VCC5V连接,芯片U5的第二引脚和第四引脚、电容C40的一端、电容C51的一端以及电容C50的阳极连接,电容C51的一端作为电源VCC3V3的输出端,电容C41的另一端、电容C37的另一端、芯片U5的第一引脚、电容C40的另一端、电容C51的另一端以及电容C50的阴极均连接并接地。

更进一步地,所述超级电容电路包括顺次串联连接的电容C1至电容C10,电容C1至电容C10为极性电容,超级电容电路的输出Vsc与逻辑控制电路连接。

再进一步地,所述逻辑控制电路包括芯片Q2、电阻R10、电阻R21、三极管Q7、电阻R39、电容C31、电阻R46、电阻R47以及二极管D2,所述芯片Q2的第一引脚、第二引脚以及第三引脚连接并接电阻R10的一端以及超级电容电路的输出Vsc,电阻R10的另一端接电阻R21的一端以及芯片Q2的第四引脚,电阻R21的另一端接三极管Q7的集电极,三极管Q7的基极分别接电阻R39的一端、电容C31的一端以及电阻R46的一端,电阻R47的一端与电阻R46的另一端连接并接主控芯片的第八十引脚,电阻R47的另一端、电容C31的另一端、电阻R39的另一端以及三极管Q7的发射极均接地,芯片Q2的第五引脚、第六引脚、第七引脚以及第八引脚均连接二极管D2的阳极,二极管D2的阴极接续电输出电路。

再进一步地,所述续电输出电路包括电容C22、电容C23、电容C112、电容C116、电容C117以及芯片U15,所述电容C116的一端、电容C117的一端以及芯片U15的第一引脚连接并接二极管D2的阴极,电容C116的另一端、电容C117的另一端以及芯片U15的第二引脚均接地,芯片U15的第三引脚、电容C112的一端、电容C23的一端以及电容C22的阳极均连接且电容C22的阳极接待供电设备,电容C112的另一端、电容C23的另一端以及电容C22的阴极均接地。

进一步地,采样电路包括电容C55、芯片U6、电容C66、电容C56、电阻R7、电阻R61、电容C47、运放U4A、电阻R60、二极管D15以及电容C46,电容C55的一端和芯片U6的第一引脚均接电源VCC3V3,芯片U6的第二引脚、电容C66的一端以及电容C56的一端均连接,电容C55的另一端、芯片U6的第三引脚、电容C66的另一端以及电容C56的另一端均接地;电阻R7的一端作为采样输入端,电阻R7的另一端分别与电阻R61的一端、电容C47的一端以及运放U4A的同相端连接,电阻R61的另一端、电容C47的另一端以及运放U4A的电源负端均接地,运放U4A的反相端接其输出端,运放U4A的电源正端接电源VCC5V,电阻R60的一端与运放U4A的输出端连接,电阻R60的输出端与电容C46的一端、二极管D15的阳极以及主控芯片的AD端口连接,电容C46的另一端接地,二极管D15的阴极接电源VCC3V3。

进一步地,所述主控芯片的型号为ST32F207VC。

进一步地,所述存储电路包括电阻R101、芯片U11、电阻R109以及电容C105,电阻R101的一端与电源VCC3V3连接,电阻R101的另一端与芯片U11的第三引脚连接,芯片U11的第一引脚、第二引脚、第三引脚、第四引脚、第五引脚以及第八引脚分别一一对应的与主控芯片的第六十十引脚、第六十一引脚、第五十九引脚、第五十八引脚、第五十七引脚以及第六十二引脚连接,芯片U11的第七引脚接地,芯片U11的第六引脚接电阻R109的一端以及电容C105的一端并接电源VCC3V3,电阻R109的另一端接芯片U11的第五引脚,电容C105的另一端接地。

进一步地,所述关联控制输出电路包括电阻R30、电容C21、电阻R31、三极管Q4、二极管D以及继电器,所述继电器包括线圈和常开触点K1,所述电阻R30的一端与主控芯片的第八十六引脚连接,电阻R30的另一端分别与电容C21的一端、电阻R31的一端以及三极管Q4的基极连接,电容C21的另一端、电阻R31的另一端以及三极管Q4的发射极均连接并接地,三极管Q4的集电极接线圈的一端以及二极管D的阳极,二极管D的阴极以及线圈的另一端均接电源Vboost,常开触点K1的两端接关联设备。

进一步地,所述通信电路包括有线通信单元和无线通信单元,所述有线通信单元包括电容C109、电池E1、电感L7、电阻R93、电阻R90、电阻R91、电容C92、电阻R96、电阻R104、电阻R100、电阻R97、电阻R94、电阻R92、芯片U10、电容C103、电容C102、电阻R95、电阻R99、电容C101、电阻R89、电阻R88、电容C85、芯片T2、电阻R111、电阻R107、电容C104、晶振LFX1、电容C108以及电阻R105,电阻R93的一端接电源VCC3V3,电阻R93的另一端以及主控芯片的第二十五引脚均接芯片U10的第十二引脚,芯片U10的第十七引脚、第十八引脚、第十六引脚、第七引脚、第八引脚以及第十一引脚分别一一对应的与主控芯片的第五十一引脚、第五十二引脚、第四十八引脚、第三十四引脚、第三十三引脚以及第三十二引脚连接,芯片U10的第十四引脚通过电阻R91与主控芯片的第二十四引脚连接,电阻R90的一端接电源VCC3V3,电阻R90的另一端分别与主控芯片的第三十五引脚、电容C92的一端以及芯片U10的第十五引脚连接,电阻R96的一端与芯片U10的第十引脚连接,电阻R96的另一端与电容C92的另一端以及电阻R104的一端连接并接地,电阻R104的另一端通过电阻R100与芯片U10的第二十四引脚连接,电阻R97的一端、电阻R94的一端以及电阻R92的一端分别一一对应的与芯片U10的第七引脚、第八引脚以及第十一引脚连接,电阻R97的另一端、电阻R94的另一端以及电阻R92的另一端均与芯片U10的第二十五引脚连接并接地,电阻R105的一端与芯片U10的第五引脚连接,电阻R105的另一端分别与电容C108的一端以及晶振LFX1的一端连接,芯片U10的第四引脚分别与电容C104的一端以及晶振LFX1的另一端连接,电容C104的另一端以及电容C108的另一端均接地;电阻R107的一端与芯片U10的第二引脚连接,电阻R111的一端与芯片U10的第三引脚连接,电阻R111的另一端以及电阻R107的另一端均接地;芯片U10的第二十二引脚分别与电阻R95的一端以及芯片T2的TN引脚连接,芯片U10的第二十三引脚分别与电阻R99的一端以及芯片T2的TP引脚连接,芯片U10的第二十引脚分别与电阻R88的一端以及芯片T2的RN引脚连接,芯片U10的第二十一引脚分别与电阻R89的一端以及芯片T2的RP引脚连接,电容C101的一端以及电容C85的一端均接地,电阻R95的另一端、电阻R99的另一端、电容C101的另一端、电阻R89的另一端、电阻R88的另一端以及电容C85的另一端均与电源VCC33A连接;芯片U10的第一引脚、第十九引脚均与电感L7的一端连接并接电源VCC33A,电感L7的另一端分别与电池E1的正极以及电容C109的一端连接并接电源VCC3V3,电容C109的另一端以及电池E1的负极连接并接地,芯片U10的第九引脚接电源VCC3V3,芯片U10的第六引脚分别与电容C103的一端以及电容C102的一端连接,电容C103的另一端以及电容C102的另一端均接地;

所述无线通信单元包括电容C75、电阻R83、电阻R81、电阻R80、电阻R79、芯片W1、电阻R77、电容C65、电容C77、电阻R69、电阻R72、电阻R73、电阻R75、电容C71、电容C79以及无线天线,电阻R83的一端、电阻R81的一端、电阻R89的一端、电阻R79的一端、电阻R69的一端、电阻R72的一端、电阻R73的一端以及电阻R75的一端分别一一对应的与主控芯片的第五十六引脚、第五十五引脚、第七引脚、第五引脚、第一引脚、第二引脚、第三引脚以及第四引脚连接,电阻R83的另一端、电阻R81的另一端、电阻R89的另一端、电阻R79的另一端、电阻R69的另一端、电阻R72的另一端、电阻R73的另一端以及电阻R75的另一端分别一一对应的与芯片W1的第八引脚、第九引脚、第十引脚、第十六引脚、第三十引脚、第三十一引脚、第三十四引脚以及第三十七引脚连接,电容C75的一端与芯片W1的第一引脚以及第二引脚连接并接电源VCC3V3,电容C75的另一端接地,电容C65的一端以及电容C77的一端与芯片W1的第二十五引脚连接并接电源VCC3V3,电容C65的另一端以及电容C77的另一端接地;电容C71的一端、电容C79的一端、无线天线的第一引脚以及芯片W1的第四十七引脚连接,电容C71的另一端、电容C79的另一端以及无线天线的第二引脚至第五引脚均接地。

本发明的优点在于:本发明逻辑控制电路控制输入电源和超级电容电路工作时的逻辑,正常时,输入电源给电路供电,超级电容电路充满电且无输出,应急供电时,通过逻辑控制电路关断输入电源,投入超级电容作为应急续电电源,通过超级电容进行完成应急供电,避免使用蓄电池而存在安全风险以及寿命有限的问题,同时续电输出电路提供待供电设备的直流电压,关联控制输出电路提供现场关联设备的供电电压,通信电路将续电装置的数据传输到后台,便于工作人员操作和查看,相比现有地铁闸机的续电装置功能较多。

附图说明

图1为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的结构框图;

图2为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的输入电源的一部分原理图;

图3为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的输入电源的另一部分原理图;

图4为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的超级电容电路的原理图;

图5为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的逻辑控制电路原理图;

图6为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的续电输出电路原理图;

图7为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的采样电路的一部分原理图;

图8为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的采样电路的另一部分原理图;

图9为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的存储电路原理图;

图10为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的关联控制输出电路原理图;

图11为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的通信电路中有线通信单元原理图;

图12为本发明实施例所提供的一种应用于地铁闸机内的直流续电装置的通信电路中无线通信单元原理图。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1所示,一种应用于地铁闸机内的直流续电装置,包括输入电源1、超级电容电路2、逻辑控制电路3、采样电路4、存储电路5、主控芯片6、续电输出电路7、关联控制输出电路8以及通信电路9,所述输入电源1、超级电容电路2以及续电输出电路7均与逻辑控制电路3连接,所述逻辑控制电路3与主控芯片6连接,所述采样电路4、存储电路5、关联控制输出电路8以及通信电路9均与主控芯片6连接。

所述主控芯片6,采用32位MCU芯片ST32F207VC,该芯片主频高达120MHz,片内1Mbyte的FLASH和128Kbyte的SRAM,具有多个串口,1路网口,多路12-bit的高速AD采样通道,满足装置其他各模块控制所需。

如图2和图3所示,所述输入电源1包括降压电路和稳压电路,所述降压电路包括二极管D6、二极管D7、电容C19、电容C15、电容C12、电阻R19、电阻R18、电容C14、电容C18、芯片U2、电容C25、电阻R36、电容C24、电阻R25、电阻R26、二极管D10、电感L5、电容C36、电容C35以及电容C39,所述二极管D6的阳极与电源Vin连接,二极管D7的阳极与电源Vsc连接,二极管D6的阴极分别与电容C19的正极、电容C15的一端、二极管D7的阴极、电容C12的一端、电阻R19的一端以及芯片U2的第二引脚连接,电容C19的负极、电容C15的另一端、电容C12的另一端、电阻R18的一端以及电容C14的一端连接并接地,电阻R18的另一端与电阻R19的另一端以及芯片U2的第三引脚连接,电容C14的另一端与芯片U2的第四引脚连接;电容C18的一端与芯片U2的第一引脚连接,电容C18的另一端分别与电感L5的一端、芯片U2的第八引脚以及二极管D10的阴极连接,电感L5的另一端与电容C36的一端、电容C35的一端以及电容C39的正极连接,电容C39的正极作为电源VCC5V的输出端口,芯片U2的第七引脚、二极管D10的阳极、电容C36的另一端、电容C35的另一端以及电容C39的阴极均接地;芯片U2的第六引脚分别与电容C25的一端以及电容C24的一端连接,电容C25的另一端通过电阻R36与电容C24的另一端以及电阻R25的一端连接并接地,电阻R25的另一端分别接芯片U2的第五引脚以及电阻R26的一端,电阻R26的另一端作为电源VCC5V的输出端口;

所述稳压电路包括电容C41、电容C37、芯片U5、电容C40、电容C51以及电容C50,所述电容C41的一端、电容C37的一端以及芯片U5的第三引脚均与电源VCC5V连接,芯片U5的第二引脚和第四引脚、电容C40的一端、电容C51的一端以及电容C50的阳极连接,电容C51的一端作为电源VCC3V3的输出端,电容C41的另一端、电容C37的另一端、芯片U5的第一引脚、电容C40的另一端、电容C51的另一端以及电容C50的阴极均连接并接地。采用电源转换芯片TPS54331也即芯片U2实现24V到5V的转换,通过SPX1117也即芯片U5实现5V到3.3V的转换,3.3V实现对装置中各控制芯片和元器件的供电。

如图4所示,所述超级电容电路2包括顺次串联连接的电容C1至电容C10,电容C1至电容C10为极性电容,超级电容电路的输出Vsc与逻辑控制电路连接。因为输入电压为24V,输出的续电电压最高也是24V,考虑到输入电压对超级电容充电,续电时以超级电容两端电压为输出电压,则超级电容的电压,容量和个数需要配合24V电压,本装置选择MAXWELL的2.7V电压,25F的超级电容10个,串联后电压满足设计要求。

如图5所示,所述逻辑控制电路3包括芯片Q2、电阻R10、电阻R21、三极管Q7、电阻R39、电容C31、电阻R46、电阻R47以及二极管D2,所述芯片Q2的第一引脚、第二引脚以及第三引脚连接并接电阻R10的一端以及超级电容电路的输出Vsc,电阻R10的另一端接电阻R21的一端以及芯片Q2的第四引脚,电阻R21的另一端接三极管Q7的集电极,三极管Q7的基极分别接电阻R39的一端、电容C31的一端以及电阻R46的一端,电阻R47的一端与电阻R46的另一端连接并接主控芯片的第八十引脚,电阻R47的另一端、电容C31的另一端、电阻R39的另一端以及三极管Q7的发射极均接地,芯片Q2的第五引脚、第六引脚、第七引脚以及第八引脚均连接二极管D2的阳极,二极管D2的阴极接续电输出电路7。逻辑控制电路主要是实现通过主控芯片的管脚控制电源的连通与断开,主控芯片的管脚不可以直接控制,通过控制场效应晶体管AO4407也即Q7来实现,当单片机的IO引脚为高电平时候,场效应管Q7导通,输入端电压连接到输出端,提供输出端电压。

如图6所示,所述续电输出电路7包括电容C22、电容C23、电容C112、电容C116、电容C117以及芯片U15,所述电容C116的一端、电容C117的一端以及芯片U15的第一引脚连接并接二极管D2的阴极,电容C116的另一端、电容C117的另一端以及芯片U15的第二引脚均接地,芯片U15的第三引脚、电容C112的一端、电容C23的一端以及电容C22的阳极均连接且电容C22的阳极接待供电设备,电容C112的另一端、电容C23的另一端以及电容C22的阴极均接地。续电输出电路按照设计可输出三个目前大部分智能设备的供电电压,24V,12V和5V,其中24V输出直接取自超级电容的端电压,12V和5V的电压输出需将超级电容的24V输出电压通过电压转换芯片转换到对应的电压等级,如图6所示,本装置采用的电压转换芯片为L7812CV-DG,如果要提供5V电压则电压转换芯片替换成L7805CV-DG即可。

如图7和图8所示,采样电路4包括电容C55、芯片U6、电容C66、电容C56、电阻R7、电阻R61、电容C47、运放U4A、电阻R60、二极管D15以及电容C46,电容C55的一端和芯片U6的第一引脚均接电源VCC3V3,芯片U6的第二引脚、电容C66的一端以及电容C56的一端均连接,电容C55的另一端、芯片U6的第三引脚、电容C66的另一端以及电容C56的另一端均接地;电阻R7的一端作为采样输入端,电阻R7的另一端分别与电阻R61的一端、电容C47的一端以及运放U4A的同相端连接,电阻R61的另一端、电容C47的另一端以及运放U4A的电源负端均接地,运放U4A的反相端接其输出端,运放U4A的电源正端接电源VCC5V,电阻R60的一端与运放U4A的输出端连接,电阻R60的输出端与电容C46的一端、二极管D15的阳极以及主控芯片6的AD端口连接,电容C46的另一端接地,二极管D15的阴极接电源VCC3V3。采样电路为采集装置中的输入电压,输出电压,电容电压等直流量,通过主控芯片6内自带的12bit高速AD采样模块来实现,主控芯片6内部AD模块的基准电压为2.5V,通过REF3025芯片也即芯片U6调整3.3V电压实现,电压直流量通过电阻分压和运放电路调整到适合主控芯片6管脚采样的信号,运放芯片可选择具有高增益和内部频率补偿的集成运放LM2904。

如图9所示,所述存储电路5包括电阻R101、芯片U11、电阻R109以及电容C105,电阻R101的一端与电源VCC3V3连接,电阻R101的另一端与芯片U11的第三引脚连接,芯片U11的第一引脚、第二引脚、第三引脚、第四引脚、第五引脚以及第八引脚分别一一对应的与主控芯片6的第六十十引脚、第六十一引脚、第五十九引脚、第五十八引脚、第五十七引脚以及第六十二引脚连接,芯片U11的第七引脚接地,芯片U11的第六引脚接电阻R109的一端以及电容C105的一端并接电源VCC3V3,电阻R109的另一端接芯片U11的第五引脚,电容C105的另一端接地。存储电路5选择常用的FLASH存储芯片AT45DB321,通过SPI接口连接到主控芯片6的SPI接口,用于装置中一些用户设置的电压阈值和用户其他配置参数的存储。

如图10所示,所述关联控制输出电路8包括电阻R30、电容C21、电阻R31、三极管Q4、二极管D以及继电器,所述继电器包括线圈和常开触点K1,所述电阻R30的一端与主控芯片6的第八十六引脚连接,电阻R30的另一端分别与电容C21的一端、电阻R31的一端以及三极管Q4的基极连接,电容C21的另一端、电阻R31的另一端以及三极管Q4的发射极均连接并接地,三极管Q4的集电极接线圈的一端以及二极管D的阳极,二极管D的阴极以及线圈的另一端均接电源Vboost,常开触点K1的两端接关联设备。关联控制输出电路为一路遥控输出,装置通过一个主控芯片6的引脚控制继电器实现输出端子的开/合,继电器采用松下功率型继电器ALDP112W,输出端可控制高达5A电流的回路,满足一般关联设备的控制。

如图11所示,所述通信电路9包括有线通信单元和无线通信单元,所述有线通信单元包括电容C109、电池E1、电感L7、电阻R93、电阻R90、电阻R91、电容C92、电阻R96、电阻R104、电阻R100、电阻R97、电阻R94、电阻R92、芯片U10、电容C103、电容C102、电阻R95、电阻R99、电容C101、电阻R89、电阻R88、电容C85、芯片T2、电阻R111、电阻R107、电容C104、晶振LFX1、电容C108以及电阻R105,电阻R93的一端接电源VCC3V3,电阻R93的另一端以及主控芯片6的第二十五引脚均接芯片U10的第十二引脚,芯片U10的第十七引脚、第十八引脚、第十六引脚、第七引脚、第八引脚以及第十一引脚分别一一对应的与主控芯片6的第五十一引脚、第五十二引脚、第四十八引脚、第三十四引脚、第三十三引脚以及第三十二引脚连接,芯片U10的第十四引脚通过电阻R91与主控芯片6的第二十四引脚连接,电阻R90的一端接电源VCC3V3,电阻R90的另一端分别与主控芯片6的第三十五引脚、电容C92的一端以及芯片U10的第十五引脚连接,电阻R96的一端与芯片U10的第十引脚连接,电阻R96的另一端与电容C92的另一端以及电阻R104的一端连接并接地,电阻R104的另一端通过电阻R100与芯片U10的第二十四引脚连接,电阻R97的一端、电阻R94的一端以及电阻R92的一端分别一一对应的与芯片U10的第七引脚、第八引脚以及第十一引脚连接,电阻R97的另一端、电阻R94的另一端以及电阻R92的另一端均与芯片U10的第二十五引脚连接并接地,电阻R105的一端与芯片U10的第五引脚连接,电阻R105的另一端分别与电容C108的一端以及晶振LFX1的一端连接,芯片U10的第四引脚分别与电容C104的一端以及晶振LFX1的另一端连接,电容C104的另一端以及电容C108的另一端均接地;电阻R107的一端与芯片U10的第二引脚连接,电阻R111的一端与芯片U10的第三引脚连接,电阻R111的另一端以及电阻R107的另一端均接地;芯片U10的第二十二引脚分别与电阻R95的一端以及芯片T2的TN引脚连接,芯片U10的第二十三引脚分别与电阻R99的一端以及芯片T2的TP引脚连接,芯片U10的第二十引脚分别与电阻R88的一端以及芯片T2的RN引脚连接,芯片U10的第二十一引脚分别与电阻R89的一端以及芯片T2的RP引脚连接,电容C101的一端以及电容C85的一端均接地,电阻R95的另一端、电阻R99的另一端、电容C101的另一端、电阻R89的另一端、电阻R88的另一端以及电容C85的另一端均与电源VCC33A连接;芯片U10的第一引脚、第十九引脚均与电感L7的一端连接并接电源VCC33A,电感L7的另一端分别与电池E1的正极以及电容C109的一端连接并接电源VCC3V3,电容C109的另一端以及电池E1的负极连接并接地,芯片U10的第九引脚接电源VCC3V3,芯片U10的第六引脚分别与电容C103的一端以及电容C102的一端连接,电容C103的另一端以及电容C102的另一端均接地。有线通信单元采用网络通信方式,网络物理芯片采用常用的物理芯片LAN8702AI,一端接到MCU内部的MAC模块引脚,一端接到网络个隔离变压器芯片也即芯片T2,网络隔离变压器可采用11FB-05NL芯片。

如图12所示,所述无线通信单元包括电容C75、电阻R83、电阻R81、电阻R80、电阻R79、芯片W1、电阻R77、电容C65、电容C77、电阻R69、电阻R72、电阻R73、电阻R75、电容C71、电容C79以及无线天线,电阻R83的一端、电阻R81的一端、电阻R89的一端、电阻R79的一端、电阻R69的一端、电阻R72的一端、电阻R73的一端以及电阻R75的一端分别一一对应的与主控芯片6的第五十六引脚、第五十五引脚、第七引脚、第五引脚、第一引脚、第二引脚、第三引脚以及第四引脚连接,电阻R83的另一端、电阻R81的另一端、电阻R89的另一端、电阻R79的另一端、电阻R69的另一端、电阻R72的另一端、电阻R73的另一端以及电阻R75的另一端分别一一对应的与芯片W1的第八引脚、第九引脚、第十引脚、第十六引脚、第三十引脚、第三十一引脚、第三十四引脚以及第三十七引脚连接,电容C75的一端与芯片W1的第一引脚以及第二引脚连接并接电源VCC3V3,电容C75的另一端接地,电容C65的一端以及电容C77的一端与芯片W1的第二十五引脚连接并接电源VCC3V3,电容C65的另一端以及电容C77的另一端接地;电容C71的一端、电容C79的一端、无线天线的第一引脚以及芯片W1的第四十七引脚连接,电容C71的另一端、电容C79的另一端以及无线天线的第二引脚至第五引脚均接地。无线通信单元采用集成的无线模块实现,通过MCU的串口控制无线模块收发数据,考虑到地铁系统的环境状况,无线模块可采用目前无线通信领域中热门的Lora方式,借助Lora无线传输穿透性强,传输距离远的特点实现装置的信息交互。

通过以上技术方案,本发明提供的一种应用于地铁闸机内的直流续电装置,逻辑控制电路3控制输入电源1和超级电容电路2工作时的逻辑,正常时,输入电源1给电路供电,超级电容电路2充满电且无输出,应急供电时,通过逻辑控制电路3关断输入电源1,投入超级电容作为应急续电电源,通过超级电容进行完成应急供电,避免使用蓄电池而存在安全风险以及寿命有限的问题,同时续电输出电路7提供待供电设备的直流电压,关联控制输出电路8提供现场关联设备的供电电压,通信电路9将续电装置的数据传输到后台,便于工作人员操作和查看,相比现有地铁闸机的续电装置功能较多。

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 一种应用于地铁闸机内的直流续电装置

- 一种应用于地铁闸机内的直流续电装置