功率放大电路、半导体器件以及半导体器件的制造方法

文献发布时间:2023-06-19 10:00:31

技术领域

本发明涉及功率放大电路、半导体器件以及半导体器件的制造方法。

背景技术

公开了对构成功率放大器的晶体管的温度特性进行补偿的技术(例如,专利文献1)。

在先技术文献

专利文献

专利文献1:美国专利申请公开第2017/0187331号说明书

近年来,作为构成功率放大电路的半导体器件的半导体材料,推进了使用砷化镓(GaAs)等的化合物半导体、硅锗(SiGe)等的Si的半导体器件的开发。在使用这样的半导体器件设计功率放大电路的情况下,如果晶体管的工艺偏差大,则存在变得不能满足增益特性等的要求性能的情况。

发明内容

发明要解决的课题

本发明是鉴于上述而完成的,目的在于,实现能够对半导体器件的工艺偏差所导致的增益偏差进行补偿的功率放大电路、半导体器件以及半导体器件的制造方法。

用于解决课题的手段

本发明的一个方面的功率放大电路是将包括放大用晶体管的放大部设置在半导体器件的芯片上的功率放大电路,具备:检测用晶体管,设置在所述半导体器件的芯片上;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于所述偏置电平设定值,生成所述可变衰减器的偏置值。

在该结构中,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

包括:放大部,包括放大用晶体管;检测用晶体管;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于所述偏置电平设定值,生成所述可变衰减器的偏置值,至少所述放大用晶体管以及所述电流放大率检测用晶体管设置在相同的芯片上。

在该结构中,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

本发明的一个方面的半导体器件的制造方法是如下半导体器件的制造方法,该半导体器件包括:放大部,包括放大用晶体管;检测用晶体管;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于所述偏置电平设定值,生成所述可变衰减器的偏置值,至少所述放大用晶体管和所述检测用晶体管设置在相同的芯片上,所述制造方法具有:计算所述检测用晶体管的放大率的步骤;基于所述放大率,生成所述偏置电平设定值的步骤;和将所述偏置电平设定值写入所述偏置电平设定保持部的步骤。

由此,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

发明效果

根据本发明,能够实现能够对半导体器件的工艺偏差所导致的增益偏差进行补偿的功率放大电路、半导体器件以及半导体器件的制造方法。

附图说明

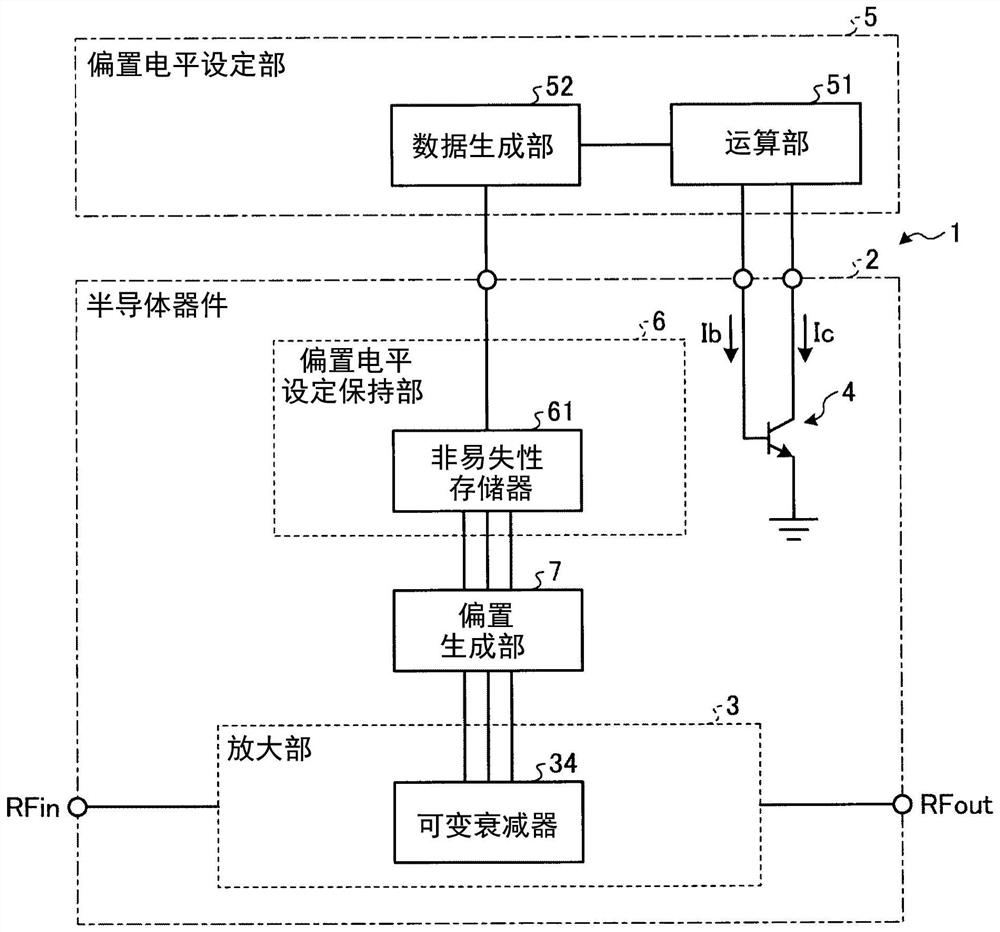

图1是示出实施方式1涉及的功率放大电路的概略结构的图。

图2A是示出放大部的第1结构例的图。

图2B是示出放大部的第2结构例的图。

图2C是示出放大部的第3结构例的图。

图2D是示出放大部的第4结构例的图。

图3是示出可变衰减器的一个方式的框图。

图4是示出构成实施方式1涉及的功率放大电路的半导体器件的芯片(die)上的各个块的配置例的概念图。

图5是示出由实施方式1涉及的偏置电平设定部的数据生成部生成的3bit数据的一个例子的图。

图6是示出构成实施方式1涉及的偏置电平设定保持部的非易失性存储器的一个方式的框图。

图7是示出实施方式1涉及的半导体器件的制造方法的一个例子的流程图。

图8是示出偏置生成部的一个方式的框图。

图9是示出实施方式2涉及的功率放大电路的概略结构的图。

图10是示出实施方式2涉及的偏置电平设定保持部的动作定时和构成偏置电平设定保持部的锁存电路的写入定时的一个例子的时序图。

图11是示出实施方式2涉及的半导体器件的制造方法的一个例子的流程图。

附图标记说明

1、1a:功率放大电路

2、2a:半导体器件

3、3a、3b、3c:放大部

4:检测用晶体管

5、5a:偏置电平设定部

6、6a:偏置电平设定保持部

7:偏置生成部

31:第1功率放大器

31a:放大用晶体管

32:第2功率放大器

32a:放大用晶体管

33:第3功率放大器

33a:放大用晶体管

34:可变衰减器

51:运算部

52:数据生成部

53:脉冲生成电路

54:A/D变换电路

55:延迟电路

61:非易失性存储器

611:写入控制电路

612:缓冲电路。

具体实施方式

以下,基于附图详细地说明实施方式涉及的功率放大电路。另外,本发明不受该实施方式限定。各实施方式是例示,在不同的实施方式中示出的结构能够部分地置换或组合,这是不言而喻的。在实施方式2以后,省略关于与实施方式1共同的事项的描述,仅对不同的点进行说明。特别地,对于同样的结构所带来的同样的作用效果,未在每个实施方式逐次提及。

(实施方式1)

图1是示出实施方式1涉及的功率放大电路的概略结构的图。实施方式1涉及的功率放大电路1在半导体器件2的芯片上设置有放大部3、检测用晶体管4、偏置电平设定保持部6和偏置生成部7。在本实施方式中,将检测用晶体管记载为双极晶体管,但是在该情况下,关于构成放大部3的放大用晶体管,也是双极晶体管。另外,检测用晶体管4和放大用晶体管也可以是场效应晶体管。在本发明中所称的芯片是指小片,并以与半导体芯片(semiconductor chip)相同的含义使用。因此,作为芯片虽然未图示,但是指搭载了半导体器件2本身的构造。

在本实施方式中,例示了使用硅锗(SiGe)作为半导体器件2的半导体材料的结构。在将放大部3构成于半导体器件2的芯片上的情况下,如果构成放大部3的晶体管的放大率(在场效应晶体管的情况下是跨导)的工艺偏差大,则存在放大部3的增益变得有偏差,不能满足作为功率放大电路的要求性能的情况。

放大部3放大高频输入信号RFin,并输出高频输出信号RFout。放大部3包括用于对放大部3中的增益进行补偿的可变衰减器34。图2A是示出放大部的第1结构例的图。图2B是示出放大部的第2结构例的图。图2C是示出放大部的第3结构例的图。图2D是示出放大部的第4结构例的图。

在图2A、图2B、图2C、图2D所示的一个例子中,放大部3、3a、3b、3c是具有第1功率放大器31、第2功率放大器32以及第3功率放大器33的3级结构的RF功率放大器。另外,在本实施方式中,示出了将功率放大器设为3级结构的例子,但是例如也可以是2级结构,还可以由4级以上的功率放大器构成。

构成第1功率放大器31、第2功率放大器32以及第3功率放大器33的放大用晶体管将多个单位晶体管电并联连接而构成。所谓单位晶体管,是指构成放大用晶体管的最小限度的结构。通过使构成第1功率放大器31、第2功率放大器32以及第3功率放大器33的放大用晶体管包括多个单位晶体管构成,能够确保放大部3的驱动所需要的功率。

构成第1功率放大器31的放大用晶体管例如包括2个单位晶体管。此外,构成第2功率放大器32的放大用晶体管例如包括8个单位晶体管。此外,构成第3功率放大器33的放大用晶体管例如包括22个单位晶体管。另外,构成上述第1功率放大器31、第2功率放大器32以及第3功率放大器33的放大用晶体管的单位晶体管数是一个例子,并不限定于此。

如图2A所示,可变衰减器34优选设置于第1功率放大器31的前级、即放大部3的输入级,但如图2B所示,也可以设置在第1功率放大器31与第2功率放大器32之间,如图2C所示,也可以设置在第2功率放大器32与第3功率放大器33之间。此外,如图2D所示,可变衰减器34也可以是设置于第3功率放大器33的后级、即放大部3的输出级的结构。

另外,虽然未图示,但在第1功率放大器31的前级、即放大部3的输入级,设置有输入匹配电路。如图2A所示,在将可变衰减器34设置于第1功率放大器31的前级的情况下,输入匹配电路也可以是包括可变衰减器34的结构。

此外,虽然未图示,但在第1功率放大器31与第2功率放大器32之间、以及第2功率放大器32与第3功率放大器33之间,分别设置有级间匹配电路。如图2B所示,在将可变衰减器34设置在第1功率放大器31与第2功率放大器32之间的情况下,或者如图2C所示,在将可变衰减器34设置在第2功率放大器32与第3功率放大器33之间的情况下,级间匹配电路也可以是包括可变衰减器34的结构。

此外,虽然未图示,但在第3功率放大器33的后级、即放大部3的输出级,设置有输出匹配电路。如图2D所示,在将可变衰减器34设置于第3功率放大器33的后级的情况下,输出匹配电路也可以是包括可变衰减器34的结构。

图3是示出可变衰减器的一个方式的框图。另外,可变衰减器34的结构不限于此,能够应用任意的π型、T型的结构。

在图3中,BIASin[0]、BIASin[1]示出了从偏置生成部7输出的偏置值的输入值。另外,偏置值的数量只要根据半导体器件2的工艺偏差的程度设为合适的数量即可。

图4是示出构成实施方式1涉及的功率放大电路的半导体器件的芯片上的各个块的配置例的概念图。

如图4所示,检测用晶体管4构成在半导体器件2的芯片上。此外,检测用晶体管4具有使用与构成第1功率放大器31、第2功率放大器32以及第3功率放大器33的放大用晶体管31a、32a、33a相同的工艺的晶体管。因此,在检测用晶体管4以及放大用晶体管31a、32a、33a是双极晶体管的情况下,可看作放大用晶体管31a、32a、33a的放大率与检测用晶体管4的放大率等价。因此,只要能够对检测用晶体管4的放大率进行检测,就能够通过将可变衰减器34的衰减量设为与检测用晶体管4的放大率相应的值,从而对半导体器件2的工艺偏差所导致的放大部3的增益偏差进行补偿。

此外,在检测用晶体管4以及放大用晶体管31a、32a、33a是场效应晶体管的情况下,可看作放大用晶体管31a、32a、33a的跨导与检测用晶体管4的跨导等价。因此,只要能够对检测用晶体管4的跨导进行检测,就能够通过将可变衰减器34的衰减量设为与检测用晶体管4的跨导相应的值,从而对半导体器件2的工艺偏差所导致的放大部3的增益偏差进行补偿。

在本实施方式中,如图1所示,在构成功率放大电路1的半导体器件2的制造工序中,连接偏置电平设定部5。偏置电平设定部5例如能够在制造工序的给定工序中,通过与半导体器件2连接的PC等的设定夹具(setting jig)而实现。偏置电平设定部5包括运算部51以及数据生成部52。

在检测用晶体管4以及放大用晶体管31a、32a、33a是双极晶体管的情况下,运算部51对流过检测用晶体管4的集电极电流Ic以及基极电流Ib进行检测。检测用晶体管4的放大率β可以使用下述式(1)来计算。

β=Ic/Ib···(1)

运算部51使用上述式(1)对检测用晶体管4的放大率β进行计算。

或者,在检测用晶体管4以及放大用晶体管31a、32a、33a是场效应晶体管的情况下,检测用晶体管4的栅极电压Vb在至少2个点处摆动,至少在2个点处检测漏极电流Id。检测用晶体管4的跨导gm可以使用下述式(2)来计算。

gm=ΔId/ΔVg=(Id2-Id1)/(Vg2-Vg1)···(2)

运算部51使用上述式(2),对检测用晶体管4的跨导gm进行计算。

数据生成部52输出与由运算部51计算的放大率β(或跨导gm)相应的3bit数据。作为数据生成部52,例示了例如A/D变换电路。图5是示出由实施方式1涉及的偏置电平设定部的数据生成部生成的3bit数据的一个例子的图。在图5中,示出了对检测用晶体管4以及放大用晶体管31a、32a、33a是双极晶体管的情况下的放大率β进行了3bit数据化的例子。

具体地,数据生成部52在放大率β的值为A以上且小于B时(A≤β<B),输出数据值“000”。

此外,数据生成部52在放大率β的值为B以上且小于C时(B≤β<C),输出数据值“001”。

此外,数据生成部52在放大率β的值为C以上且小于D时(C≤β<D),输出数据值“010”。

此外,数据生成部52在放大率β的值为D以上且小于E时(D≤β<E),输出数据值“011”。

此外,数据生成部52在放大率β的值为E以上且小于F时(E≤β<F),输出数据值“100”。

此外,数据生成部52在放大率β的值为F以上且小于G时(F≤β<G),输出数据值“101”。

此外,数据生成部52在放大率β的值为G以上且小于H时(G≤β<H),输出数据值“101”。

此外,数据生成部52在放大率β的值为H以上且小于I时(H≤β<I),输出数据值“111”。

另外,数据生成部52输出的数据值的比特数不限于3bit,也可以是2bit,还可以是4bit以上。数据生成部52输出的数据值的比特数只要根据半导体器件2的工艺偏差的程度设为合适的比特数即可。

图6是示出构成实施方式1涉及的偏置电平设定保持部的非易失性存储器的一个方式的框图。在本实施方式中,作为偏置电平设定保持部6,具备非易失性存储器61。

在图6中,LEVELout[n]示出了由从数据生成部52输出的数据值决定的偏置电平设定值的输出值。另外,偏置电平设定值的数量n只要根据半导体器件2的工艺偏差的程度设为合适的数量即可。

在本实施方式中,作为非易失性存储器61的结构,在半导体器件2的芯片上设置有多个熔丝F。例示了通过这些多个熔丝F的导通/非导通,来对可变衰减器34的偏置电平设定进行保持的结构。

在本实施方式中,非易失性存储器61包括写入控制电路611以及缓冲电路612。

写入控制电路611根据从数据生成部52输出的数据值,使电流向与数据值对应的熔丝F流动。此时,流动超过电流容量的电流的熔丝F的电阻值变化。

缓冲电路612输出与多个熔丝F的导通/非导通相应的偏置电平设定值。

通过设为这样的结构,能够使偏置电平设定保持部6的电路规模变小。

另外,作为非易失性存储器61的方式,不限于上述结构,只要是在构成功率放大电路1的半导体器件2的制造工序中仅能够写入一次的OTP(One Time Programmable readonly memory,一次性可编程只读存储器)存储器即可。

图7是示出实施方式1涉及的半导体器件的制造方法的一个例子的流程图。在本实施方式中,在构成功率放大电路1的半导体器件2的制造工序中,实施图7所示的偏置电平设定处理。

在构成功率放大电路1的半导体器件2的制造工序中,首先运算部51检测流过检测用晶体管4的集电极电流Ic以及基极电流Ib,并使用上述式(1),对检测用晶体管4的放大率β进行计算(步骤S101)。

接着,数据生成部52生成并输出与由运算部51计算的放大率β相应的3bit数据(步骤S102)。

偏置电平设定保持部6将与从数据生成部52输出的3bit数据的数据值相应的值,作为偏置电平设定值写入非易失性存储器61(步骤S103)。

通过上述实施方式1涉及的偏置电平设定处理,与检测用晶体管4的放大率β相应的偏置电平被设定。

图8是示出偏置生成部的一个方式的框图。如图8所示,偏置生成部7例如是包括多个MOSFET的电路。

在功率放大电路1的实际工作时,从偏置电平设定保持部6输出的偏置电平设定值被输入到偏置生成部7。在图8中,LEVELin[0]、LEVELin[1]、LEVELin[2]示出了从数据生成部52输出的偏置电平设定值的输入值。另外,偏置电平设定值的数量只要如上述那样根据半导体器件2的工艺偏差的程度设为合适的数量即可。

此外,作为偏置生成部7的方式,不限于图8所示的结构,能够适当变更。

偏置生成部7输出与偏置电平设定值的输入值LEVELin[0]、LEVELin[1]、LEVELin[2]相应的偏置值。在图8中,BIASout[0]、BIASout[1]示出了从数据生成部52输出的偏置值的输出值。另外,偏置值的数量只要如上述那样根据半导体器件2的工艺偏差的程度设为合适的数量即可。

实施方式1涉及的功率放大电路1通过设为上述结构,能够对构成功率放大电路1的半导体器件2的工艺偏差所导致的增益偏差进行补偿。

(实施方式2)

图9是示出实施方式2涉及的功率放大电路的概略结构的图。另外,对与实施方式1相同的构成要素标注相同的参照附图标记,并省略说明。

如图9所示,实施方式2涉及的功率放大电路1a在半导体器件2a的芯片上设置有偏置电平设定部5a。因此,在以下说明的实施方式2的结构中,在构成功率放大电路1a的半导体器件2a的制造工序中不设置PC等的设定夹具,就能够设定可变衰减器34的偏置电平。

如图9所示,偏置电平设定部5a包括脉冲生成电路53、A/D变换电路54以及延迟电路55。

脉冲生成电路53例如是随着向半导体器件2a的电源供给,产生在给定期间成为“H”电平的脉冲信号Pulse1的电路。

在从脉冲生成电路53输出的脉冲信号Pulse1的“H”期间中,集电极电流Ic流过检测用晶体管4。

A/D变换电路54将通过集电极电流Ic流过检测用晶体管4而生成的集电极电压Vc变换为数字信号,并作为并行数据输出到偏置电平设定保持部6a。并行数据的输出数量只要根据半导体器件2a的工艺偏差的程度设为合适的数量即可。

延迟电路55输出使从脉冲生成电路53输出的脉冲信号Pulse1延迟了的脉冲信号Pulse2。

此外,在本实施方式中,作为偏置电平设定保持部6a,取代实施方式1的非易失性存储器61而具备锁存电路62。

图10是示出实施方式2涉及的偏置电平设定保持部的动作定时以及构成偏置电平设定保持部的锁存电路的写入定时的一个例子的时序图。

在图10所示的脉冲信号Pulse1的“H”期间中,集电极电流Ic流过检测用晶体管4。

延迟电路55输出脉冲信号Pulse2,该脉冲信号Pulse2从由脉冲生成电路53输出的脉冲信号Pulse1的上升时起,延迟给定的延迟期间DP而成为“H”电平,该给定的延迟期间DP比脉冲信号Pulse1的“H”期间短。由此,生成脉冲信号Pulse1和脉冲信号Pulse2都成为“H”电平的锁存期间LP。锁存电路62在该锁存期间LP中,将从A/D变换电路54输出的并行数据作为偏置电平设定值而进行保持。

图11是示出实施方式2涉及的半导体器件的制造方法的一个例子的流程图。在此,对在构成功率放大电路1a的半导体器件2a的制造工序中,实施图11所示的偏置电平设定处理的例子进行说明。

在构成功率放大电路1a的半导体器件2a的制造工序中,首先,脉冲生成电路53输出脉冲信号Pulse1(步骤S201)。由此,集电极电流Ic流过检测用晶体管4。

接着,A/D变换电路54对通过集电极电流Ic流过检测用晶体管4而生成的集电极电压Vc进行A/D变换(步骤S202),并作为并行数据输出到偏置电平设定保持部6a。

偏置电平设定保持部6a在锁存期间LP中,将从A/D变换电路54输出的并行数据作为偏置电平设定值写入锁存电路62(步骤S203)。

通过上述实施方式2涉及的偏置电平设定处理,设定与检测用晶体管4的放大率β相应的偏置电平。

在功率放大电路1a的实际工作时,从偏置电平设定保持部6a输出的偏置电平设定值输入到偏置生成部7。之后的动作与实施方式1相同。

实施方式2涉及的功率放大电路1a通过设为上述结构,能够对构成功率放大电路1a的半导体器件2a的工艺偏差所导致的增益偏差进行补偿。

另外,在本实施方式中,如上述那样,作为偏置电平设定保持部6a,取代实施方式1的非易失性存储器61而具备锁存电路62。锁存电路62a与非易失性存储器61不同,能够通过偏置电平设定部5a的动作来改写。因此,在上述例子中,虽然对在构成功率放大电路1a的半导体器件2a的制造工序中,实施图11所示的偏置电平设定处理的例子进行了说明,但是在本实施方式涉及的结构中,能够通过在任意的时刻使偏置电平设定部5a进行动作,来设定可变衰减器34的偏置电平。因此,在本实施方式的结构中,不仅如上述那样在构成功率放大电路1a的半导体器件2a的制造工序中不设置PC等的设定夹具,就能够设定可变衰减器34的偏置电平,而且在构成功率放大电路1a的半导体器件2a的出厂后等,也能够设定可变衰减器34的偏置电平。进而,通过设为在功率放大电路1a的实际工作时,例如,在功率放大电路1a的启动时,执行图11所示的偏置电平设定处理的方式,也能够对构成放大部3的放大用晶体管的温度特性进行补偿。

另外,在上述各实施方式中,虽然对放大部3是3级结构的RF功率放大器的例子进行了说明,但是构成放大部3的功率放大器的级数不限定于此。只要是能够通过可变衰减器34,对构成放大部3的放大用晶体管的放大率(或跨导)的工艺偏差所导致的放大部3的增益偏差进行补偿的结构即可,例如,放大部3也可以包括2级结构或4级以上的功率放大器,还可以是包括1个功率放大器的方式。

此外,上述各实施方式用于使本发明的理解变得容易,不是用于对本发明进行限定和解释。本发明能够不脱离其主旨而进行变更/改进,并且其等价物也包括在本发明中。

如上述那样,或者取代上述,本公开可以采用以下的结构。

(1)本发明的一个方面的功率放大电路是将包括放大用晶体管的放大部设置在半导体器件的芯片上的功率放大电路,具备:检测用晶体管,设置在所述半导体器件的芯片上;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于从所述偏置电平设定保持部输出的偏置电平设定值,生成所述可变衰减器的偏置值。

在该结构中,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

(2)在上述(1)的功率放大电路中,从与所述半导体器件连接的偏置电平设定部输入用于设定所述偏置电平设定值的数据。

在该结构中,不将偏置电平设定部设置在半导体器件的芯片上,就能够进行偏置电平设定。

(3)在上述(2)的功率放大电路中,优选为,所述偏置电平设定保持部是非易失性存储器。

(4)在上述(3)的功率放大电路中,所述非易失性存储器包括:多个熔丝,设置在所述半导体器件的芯片上。

(5)在上述(4)的功率放大电路中,所述非易失性存储器的多个所述熔丝中的若干个的电阻值,根据所述偏置电平设定值而变化。

在该结构中,能够减小偏置电平设定保持部的电路规模。

(6)在上述(1)的功率放大电路中,还具备:偏置电平设定部,至少基于所述检测用晶体管的检测值,设定所述偏置电平设定值,所述偏置电平设定部设置在所述半导体器件的芯片上。

在该结构中,不在半导体器件的制造工序中设置用于进行偏置电平设定的PC等的设定夹具,就能够进行偏置电平设定。

(7)在上述(6)的功率放大电路,所述偏置电平设定保持部是锁存电路。

在该结构中,在功率放大电路的实际工作时,能够进行偏置电平设定。

(8)在上述(1)至(7)的任意一项的功率放大电路中,优选为,所述偏置生成部是包括多个晶体管的电路。

(9)在上述(1)至(8)的任意一项的功率放大电路中,所述半导体器件使用硅锗作为半导体材料。

在该结构中,能够抑制使用硅锗而构成的放大用晶体管的电流放大率的工艺偏差。

(10)本发明的一个方面的半导体器件包括:放大部,包括放大用晶体管;检测用晶体管;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于所述偏置电平设定值,生成所述可变衰减器的偏置值,至少所述放大用晶体管以及所述检测用晶体管设置在相同的芯片上。

在该结构中,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

(11)在上述(10)的半导体器件中,从设置于外部的偏置电平设定部输入用于设定所述偏置电平设定值的数据。

在该结构中,不将偏置电平设定部设置在半导体器件的芯片上,就能够进行偏置电平设定。

(12)在上述(11)的半导体器件中,优选为,所述偏置电平设定保持部是非易失性存储器。

(13)在上述(12)的半导体器件中,所述非易失性存储器包括:多个熔丝,与所述放大用晶体管以及所述检测用晶体管设置在相同的芯片上。

(14)在上述(13)的半导体器件中,所述非易失性存储器的多个所述熔丝中的若干个的电阻值根据所述偏置电平设定值而变化。

在该结构中,能够减少偏置电平设定保持部的电路规模。

(15)在上述(11)的半导体器件中,至少基于所述检测用晶体管的检测值而设定所述偏置电平设定值的偏置电平设定部与所述放大用晶体管以及所述检测用晶体管设置在相同的芯片上。

在该结构中,不在半导体器件的制造工序中设置用于进行偏置电平设定的PC等的设定夹具,就能够进行偏置电平设定。

(16)在上述(15)的半导体器件中,所述偏置电平设定保持部是锁存电路。

在该结构中,在功率放大电路的实际工作时,能够进行偏置电平设定。

(17)在上述(10)至(16)的任意一项的半导体器件中,优选为,所述偏置生成部是包括多个晶体管的电路。

(18)在上述(10)至(17)的任意一项的半导体器件中,作为半导体材料而使用硅锗。

在该结构中,能够抑制使用硅锗而构成的放大用晶体管的电流放大率的工艺偏差。

(19)本发明的一个方面的半导体器件的制造方法是如下半导体器件的制造方法,该半导体器件包括:放大部,包括放大用晶体管;检测用晶体管;可变衰减器,对所述放大部的增益进行补偿;偏置电平设定保持部,对至少基于所述检测用晶体管的检测值而设定的偏置电平设定值进行保持;和偏置生成部,基于所述偏置电平设定值,生成所述可变衰减器的偏置值,至少所述放大用晶体管以及所述检测用晶体管设置在相同的芯片上,该制造方法具有:对所述检测用晶体管的放大率进行计算的步骤;基于所述放大率,生成所述偏置电平设定值的步骤;和将所述偏置电平设定值写入所述偏置电平设定保持部的步骤。

由此,能够对半导体器件的工艺偏差所导致的放大部的增益偏差进行补偿。

根据本公开,能够实现能够对半导体器件的工艺偏差所导致的增益偏差进行补偿的功率放大电路、半导体器件以及半导体器件的制造方法。

- 功率放大电路、半导体器件以及半导体器件的制造方法

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置