半导体存储装置

文献发布时间:2023-06-19 10:11:51

[相关申请]

本申请享有以日本专利申请2019-166333号(申请日:2019年9月12日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的全部内容。

技术领域

本实施方式涉及一种半导体存储装置。

背景技术

近年来,随着半导体存储装置的大容量化,位线或字线的根数变得非常多。如果位线或字线的根数增多,那么导致选择位线或字线的解码器的配置面积也随之变大。所以,期望减小解码器中选择位线或字线的多工器的配置面积。

另一方面,如果为了减小配置面积而随便省略多工器的晶体管,那么,例如有将选择电压误施加于非选择位线或非选择字线,或者选择电压会影响与选择位线或选择字线邻接的非选择位线或非选择字线的电压的疑虑。

发明内容

实施方式提供一种具有能够减小配置面积、并且能够抑制选择电压误施加于非选择位线或非选择字线或者起因于邻接的选择位线或选择字线的变动的多工器的半导体存储装置。

本实施方式的半导体存储装置具备分为各m根(m为2以上的整数)的多个群组的多个第1信号线、及多个第2信号线。记忆胞阵列具有与多个第1信号线和多个第2信号线的交点对应设置的多个记忆胞。m根全局信号线对多个第1信号线的任一者施加选择电压。多个第1晶体管对应多个第1信号线的各者分别设置1个,连接于多个第1信号线与全局信号线之间。多个第1选择信号线与多个群组的各者对应设置,共通连接于该对应的群组中所包含的第1晶体管的栅极电极。多个第1虚设信号线配置于相互邻接的群组间,被施加非选择电压。

附图说明

图1是表示第1实施方式的半导体存储装置的构成例的框图。

图2是表示列解码器、感测放大器及位线的构成例的框图。

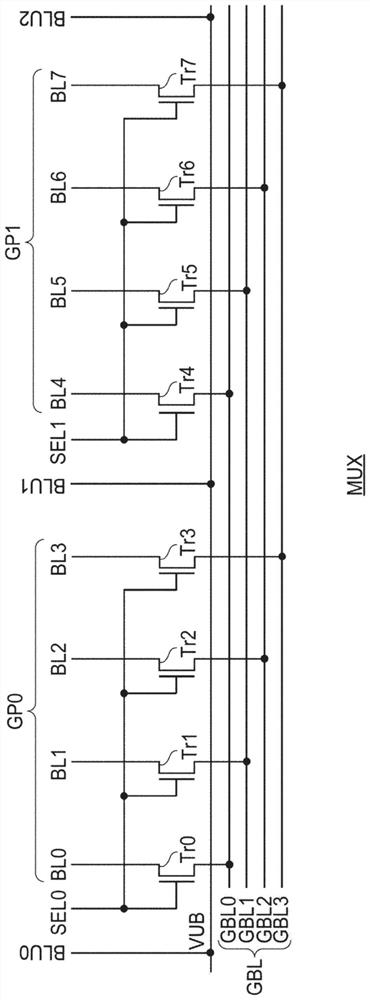

图3是表示第1实施方式的列解码器内的多工器的构成例的电路图。

图4是表示在选择群组GP0的情况下的状况的图。

图5是表示第2实施方式的列解码器内的多工器的构成例的电路图。

图6是表示在选择群组GP0的情况下的状况的图。

图7是表示第3实施方式的列解码器内的多工器的构成例的电路图。

图8是表示在选择群组GP0的情况下的状况的图。

图9是表示第4实施方式的列解码器内的多工器的构成例的电路图。

图10是表示在选择群组GP1的位线BL27的情况下的状况的图。

图11是表示第4实施方式的变形例的列解码器内的多工器的构成例的电路图。

图12是表示在选择群组GP0的位线BL27的情况下的状况的图。

图13是表示全局位线与感测放大器或非选择电压生成部之间的多工器的构成例的电路图。

图14是表示全局位线与感测放大器或非选择电压生成部之间的多工器MUX2的其它构成例的电路图。

具体实施方式

以下,参照图式对本发明的实施方式进行说明。本实施方式并不限定本发明。图式为模式性或概念性图,各部分的比例等不一定与现实的各部分相同。在说明书及图式中,关于与已提出的图式中相同的要素标注相同的符号并适当省略详细的说明。

(第1实施方式)

图1是表示第1实施方式的半导体存储装置的构成例的框图。半导体存储装置1例如可为DRAM(Dynamic Random Access Memory,动态随机存取存储器)等易失性存储器、NAND(Not And,与非)型EEPROM(Electrically Erasable and Programmable Read-Only-Memory,电可擦编程只读存储器)、ReRAM(Resistive Random Access Memory,电阻式随机存取存储器)、MRAM(Magnetic Random Access Memory,磁阻式随机存取存储器)、PCM(Phase Change Memory,相变存储器)等非易失性存储器。另外,半导体存储装置1例如可为1个存储器芯片,也可为如包含多个存储器芯片的DIMM(Dual Inline Memory Module,双列直插内存模块)这样的模块。

图1所示的半导体存储装置1例如作为1个存储器芯片而构成。以下,将半导体存储装置1称为存储器芯片1。存储器芯片1具备记忆胞阵列MCA、列解码器CD、行解码器RD、感测放大器SA、读写缓冲器RWB、及周边电路PC。

记忆胞阵列MCA例如具备二次元配置为矩阵状的多个记忆胞MC。记忆胞MC例如为PCM。记忆胞MC例如与位线BL和字线WL的交点对应配置。即,记忆胞阵列MCA为所谓的交叉点型记忆胞阵列。从半导体基板的上方观察时,位线BL与字线WL大致正交。多个位线BL连接于各记忆胞阵列MCA的记忆胞MC的一端。多个字线WL有时也作为各记忆胞阵列MCA的记忆胞MC的栅极电极发挥功能。记忆胞阵列MCA在1芯片内分割到多个存储库BNK,针对各个存储库BNK设有感测放大器SA、数据锁存器DL、地址锁存器AL等。

感测放大器SA例如经由列解码器CD及位线BL连接于记忆胞MC,经由位线BL将写入电压(例如VDD、VSS)或读出电压施加于记忆胞MC。感测放大器SA通过向记忆胞MC施加写入电压而将数据写入记忆胞MC中,或者通过向记忆胞MC施加读出电压而自记忆胞MC读出数据。

读写缓冲器RWB针对每页暂时性保持感测放大器SA检测出的数据或地址,或者针对每页暂时性保持写入记忆胞阵列MCA中的数据或地址。

行解码器RD及列解码器CD基于存储库地址或页地址访问记忆胞阵列MCA,向字线WL或位线BL施加写入电压或读出电压。行解码器RD向自多个字线WL中选择的选择字线施加写入电压或读出电压。列解码器CD将自多个位线BL中选择的选择位线连接于感测放大器SA。感测放大器SA向选择位线施加写入电压或读出电压。由此,存储器芯片1能够向记忆胞MC内的所需的记忆胞MC写入数据,或者能够自所需的记忆胞MC读出数据。

周边电路PC例如具备未图示的电压发生器、读写引擎、地址控制器、命令控制器、输入输出电路等。

电压发生器生成数据读出动作及数据写入动作所需要的字线WL的电压或位线BL的电压。

读写引擎按照命令及地址,以将数据写入存储库BNK内的所需的记忆胞MC中的方式控制列解码器CD及行解码器RD,或者自存储库BNK内的所需的记忆胞MC读出数据。读写引擎将读出数据传送至输入输出电路的DQ缓冲器。

地址控制器接收列地址及行地址等,对这些地址进行解码。命令控制器接收表示数据读出动作、数据写入动作等各种动作的命令,将这些命令传送至读写引擎。

输入输出电路(IO)自CA端子CA获取命令及地址,将命令传送至命令控制器,将地址传送至地址控制器。命令可为指示写入动作的写入命令,或者可为指示读出动作的读出命令。地址可为表示记忆胞阵列MCA的任一存储库BNK的存储库地址、及表示存储库BNK内的读出或写入对象的页或记忆胞MC的地址。在多个存储库BNK构成1个存储库群组的情况下,地址可为存储库群组的地址。

另外,输入输出电路自DQ端子获取写入数据,将写入数据传送至读写缓冲器RWB。或者,输入输出电路接收保持于数据锁存器DL的读出数据,自DQ端子输出该读出数据。

在存储器芯片1的外部,可设有控制多个存储器芯片1整体的存储器控制器(未图示)。

图2是表示列解码器CD、感测放大器SA及位线BL的构成例的框图。列解码器CD具备多工器MUX。

多工器MUX设于位线BL与感测放大器SA之间。多工器MUX以接收选择电压VSA及非选择电压VBLU,可向各个位线BL施加选择电压VSA及非选择电压VBLU的任一者的方式构成。关于多工器MUX的内部构成将于下文叙述。

感测放大器SA例如将写入电压(例如VDD、VSS)或读出电压作为选择电压VSA施加于所选择的记忆胞MC。

非选择电压生成部VBLUGEN生成施加于未被选择的非选择的记忆胞MC的非选择电压VBLU。非选择电压生成部VBLUGEN可组装于周边电路PC内,或者也可设于存储器芯片1的外部。

图3是表示第1实施方式的列解码器CD内的多工器MUX的构成例的电路图。以下,多工器MUX设于选择性驱动位线BL作为第1信号线的列解码器CD内。在此情况下,第2信号线为字线WL。但是,多工器MUX也可设于选择性驱动字线WL的行解码器RD内。在此情况下,第2信号线为位线BL。另外,多工器MUX也可设于列解码器CD及行解码器RD两者。

作为第1信号线的位线BL被分割为各m根(m为2以上的整数)的多个群组。例如,在本实施方式中,8根位线BL分割为各4根的2个群组GP0、GP1。即,在本实施方式中,m=4。此外,多个位线BL的分割意指关于对位线BL进行电压施加的操作的概念性分割。另外,位线BL的总数、群组数、各群组中所包含的位线BL的数量并无特别限定。

作为全局信号线的全局位线GBL0~GBL3相对于位线BL整体(全群组GP0、GP1)共通设置。全局位线GBL0~GBL3设置有与1个群组内所包含的位线BL的数量相同的数量(即,m根)。例如,在本实施方式中,4根位线BL包含于各群组GP0、GP1的各者中,4根全局位线GBL0~GBL3与群组GP0、GP1对应设置。此处,各群组GP0、GP1为连接于相互不同的全局位线GBL0~GBL3的位线的群组。因此,全局位线GBL0~GBL3的数量(下述式1的j)与各群组中所包含的位线的数量(下述式1的m)相等或为其以上。

各群组GP0、GP1内的4根位线BL0~BL3或BL4~BL7经由晶体管Tr0~Tr3或Tr4~Tr7连接于全局位线GBL0~GBL3的各者。群组GP0的位线BL0~BL3分别经由晶体管Tr0~Tr3连接于全局位线GBL0~GBL3。群组GP1的位线BL4~BL7分别经由晶体管Tr4~Tr7连接于全局位线GBL0~GBL3。即,位线BL0、BL4共通连接于全局位线GBL0,位线BL1、BL5共通连接于全局位线GBL1,位线BL2、BL6共通连接于全局位线GBL2,位线BL3、BL7共通连接于全局位线GBL3。全局位线GBL0~GBL3中的1根传递选择电压VSA,其它3根维持为非选择电压VBLU或者为电性浮动状态。非选择电压VBLU施加于连接于与选择位线邻接的非选择位线(邻接位线)的全局位线。连接于并非与选择位线邻接的非选择位线的全局位线也可为电性浮动状态。

作为第1晶体管的晶体管Tr0~Tr7对应位线BL0~BL7的各者分别设置1个,并连接于位线BL0~BL7与全局位线GBL0~GBL3之间。晶体管Tr0~Tr7例如由n型MOSFET(MetalOxide Semiconductor Field Effect Transistor,金属氧化物半导体场效应晶体管)构成。但是,晶体管Tr0~Tr7也可由p型MOSFET构成。另外,如果具有能够切换连接的切换功能,那么并不限于晶体管。

作为第1选择信号线的选择信号线SEL0、SEL1与群组GP0、GP1的各者对应连接,分别共通连接于对应的群组GP0、GP1中所包含的晶体管Tr0~Tr3、Tr4~Tr7的栅极电极。例如,选择信号线SEL0共通连接于群组GP0的晶体管Tr0~Tr3的栅极电极。选择信号线SEL1共通连接于群组GP1的晶体管Tr4~Tr7的栅极电极。由此,晶体管Tr0~Tr7按各群组GP0、GP1驱动。选择信号线SEL0、SEL1的电压由周边电路PC启动或者停止。

例如,设定晶体管Tr0~Tr7为n型MOSFET。此时,如果选择群组GP0,那么周边电路PC启动选择信号线SEL0,使与群组GP0对应的晶体管Tr0~Tr3成为接通状态。由此,群组GP0中所包含的位线BL0~BL3分别连接于全局位线GBL0~GBL3。即,在选择群组为GP0的情况下,晶体管Tr0~Tr3将选择群组GP0中所包含的4根位线BL0~BL3与4根全局位线GBL0~GBL3分别电性连接。另一方面,如果选择群组GP1,那么周边电路PC启动选择信号线SEL1,使与群组GP1对应的晶体管Tr4~Tr7成为接通状态。由此,群组GP1中所包含的位线BL4~BL7分别连接于全局位线GBL0~GBL3。即,在选择群组为GP1的情况下,晶体管Tr4~Tr7将选择群组GP1中所包含的4根位线BL4~BL7与4根全局位线GBL0~GBL3分别电性连接。

如上所述,全局位线GBL0~GBL3中的1根为选择电压VSA,其它3根全局位线维持为非选择电压VBLU或者为电性浮动状态。所以,仅对选择群组中所包含的4根位线中的1根位线施加选择电压VSA,对其它3根位线施加非选择电压VBLU或者为电性浮动状态。非选择电压VBLU施加于连接于与选择位线邻接的非选择位线(邻接位线)的全局位线。连接于并非与选择位线邻接的非选择位线的全局位线也可为电性浮动状态。

与非选择群组对应的选择信号线SEL1(或SEL0)仍为低水平,4个晶体管Tr4~Tr7(或Tr0~Tr3)维持断开状态。因此,非选择群组中所包含的位线BL4~BL7(或BL0~BL3)为电性浮动状态。

作为第1虚设信号线的虚设位线BLU0~BLU2配置于相互邻接的群组GP0与群组GP1之间。虚设位线BLU0~BLU2沿着位线BL0~BL7,延伸到与位线BL0~BL7相同或为其以上的长度。例如,虚设位线BLU1于位线BL3与位线BL4之间沿着位线BL3及位线BL4配置。由此,位线BL3及位线BL4未相互邻接,而介隔虚设位线BLU1配置。虚设位线BLU0、BLU2与虚设位线BLU1也相同。虚设位线BLU0配置于群组GP0与群组GP0的左邻的群组(未图示)之间,虚设位线BLU2配置于群组GP1与群组GP1的右邻的群组(未图示)之间。

全虚设位线BLU0~BLU2共通连接于供给非选择电压VBLU的非选择信号线VUB,维持为非选择电压VBLU。如此,于各群组GP0、GP1的两侧配置有维持为非选择电压VBLU的虚设位线BLU0~BLU2。

此处,图4是表示在选择群组GP0的情况下的状况的图。例如,如图4所示,在选择群组为GP0,选择位线为BL3的情况下,全局位线GBL0~GBL2传递非选择电压VBLU,全局位线GBL3传递选择电压VSA。此外,全局位线GBL0、GBL1也可为电性浮动状态。进而,选择群组GP0的晶体管Tr0~Tr3成为接通状态。由此,选择群组GP0内的选择位线BL3上传递选择电压VSA,选择群组GP0内的其它非选择位线BL0~BL2上传递非选择电压VBLU。此外,连接于全局位线GBL0、GBL1的非选择位线BL0、BL1也可为电性浮动状态。另一方面,因为非选择群组GP1的晶体管Tr4~Tr7维持断开状态,所以非选择群组GP1的位线BL4~BL7成为电性浮动状态。

如果在虚设位线BLU1未设置于位线BL3与BL4之间的情况下,浮动状态的非选择位线BL4与选择位线BL3直接邻接。所以,非选择位线BL4的电压不稳定,在选择位线BL3变化为选择电压VSA时容易受到其影响。如果非选择位线BL4的电压发生变动,那么有对连接于位线BL4的记忆胞MC带来不良影响的疑虑。另外,由连接于选择位线BL3的记忆胞MC产生的热量容易传递至连接于非选择位线BL4的记忆胞MC。

相对于此,在本实施方式的半导体存储装置中,维持为非选择电压VBLU的虚设位线BLU1配置于位线BL3与BL4之间。浮动状态的非选择位线BL4相对于选择位线BL3未直接邻接,而介隔虚设位线BLU1配置。即,非选择位线BL4并非与选择位线BL3邻接,而与虚设位线BLU1邻接。由此,位线BL3与位线BL4的电容耦合得到抑制,选择位线BL3的选择电压VSA不太影响非选择位线BL4。其结果,非选择位线BL4虽然为电性浮动状态,但其电压不太变动且稳定化。另外,由连接于选择位线BL3的记忆胞MC产生的热量不易传递至连接于非选择位线BL4的记忆胞MC。

虽未图示,但反之,在选择群组为GP1,选择位线为BL4的情况下,全局位线GBL1~GBL3传递非选择电压VBLU,全局位线GBL0传递选择电压VSA。此外,在此情况下,全局位线GBL2、GBL3可为电性浮动状态。进而,选择群组GP1的晶体管Tr4~Tr7成为接通状态。由此,选择群组GP1内的选择位线BL4上传递选择电压VSA,选择群组GP1内的其它非选择位线BL5~BL7上传递非选择电压VBLU。此外,连接于全局位线GBL2、GBL3的非选择位线BL6、BL7也可为电性浮动状态。另一方面,因为非选择群组GP0的晶体管Tr0~Tr3维持断开状态,所以非选择群组GP0的位线BL0~BL3成为电性浮动状态。在此情况下,因为维持为非选择电压VBLU的虚设位线BLU1也配置于位线BL3与BL4之间,所以位线BL3与位线BL4的电容耦合得到抑制,选择位线BL4的选择电压VSA不太影响浮动状态的非选择位线BL3。另外,由连接于选择位线BL4的记忆胞MC产生的热量不易传递至连接于非选择位线BL3的记忆胞MC。

关于虚设位线BLU0、BLU2,也与虚设位线BLU1同样地发挥功能。所以,虚设位线BLU0能够抑制群组GP0与其左邻的群组(未图示)之间的电容耦合或热量的影响。另外,虚设位线BLU2能够抑制群组GP1与其右邻的群组(未图示)之间的电容耦合或热量的影响。

根据本实施方式,晶体管Tr0~Tr7相对于位线BL0~BL7的各者分别设置1个,未设置追加的晶体管。所以,能够减小配置面积。另外,通过在位线BL的群组间配置虚设位线BLU0~BLU2,能够抑制非选择位线BL的电压变动。

所述构成及功能不仅可应用于列解码器CD,也可应用于行解码器RD。在应用于行解码器RD的情况下,可除“位线”以外或取而代之而改称为“字线”。例如,在所述构成中,与包含多个作为第1信号线的位线的选择群组邻接设有作为第1虚设信号线的虚设位线,但也可与包含多个作为第2信号线的字线的选择群组邻接设置作为第2虚设信号线的虚设字线。

(第2实施方式)

图5是表示第2实施方式的列解码器CD内的多工器MUX的构成例的电路图。在第2实施方式中,于各群组GP0、GP1的两侧设有虚设位线,各群组GP0、GP1被2根虚设位线夹持。例如,在群组GP0的两侧,设有虚设位线BLU10、BLU11,群组GP0夹于虚设位线BLU10与虚设位线BLU11之间。在群组GP1的两侧,设有虚设位线BLU12、BLU13,群组GP1夹于虚设位线BLU12与虚设位线BLU13之间。

虚设位线BLU10~BLU13与第1实施方式的虚设位线BLU0~BLU2同样地,沿着位线BL0~BL7,延伸到与位线BL0~BL7相同或为其以上的长度。

于虚设位线BLU10~BLU13与非选择信号线VUB之间,连接有作为第2晶体管的各个晶体管Tr10~Tr13。晶体管Tr10~Tr13与虚设位线BLU10~BLU13对应设置,将虚设位线BLU10~BLU13选择性地连接于非选择信号线VUB。晶体管Tr10~Tr13例如由n型MOSFET构成。但是,晶体管Tr10~Tr13也可由p型MOSFET构成。另外,如果具有能够切换连接的切换功能,那么并不限于晶体管。

晶体管Tr10、Tr11的栅极电极共通连接于虚设选择信号线SELU0,晶体管Tr12、Tr13的栅极电极共通连接于虚设选择信号线SELU1。作为第2选择信号线的虚设选择信号线SELU0、SELU1与群组GP0、GP1的各者对应设置。虚设选择信号线SELU0共通连接于与其对应的群组GP0的晶体管Tr10、Tr11的栅极电极。虚设选择信号线SELU1共通连接于与其对应的群组GP1的晶体管Tr12、Tr13的栅极电极。

虚设选择信号线SELU0可与选择信号线SEL0为同一信号,可在选择群组GP0时与选择信号线SEL0同时启动。此时,晶体管Tr0~Tr3成为接通状态,同时晶体管Tr10、Tr11也成为接通状态。通过使晶体管Tr10、Tr11成为接通状态,从而,虚设位线BLU10、BLU11连接于非选择信号线VUB,成为非选择电压VBLU。由此,即便选择群组GP0的一端的位线BL0或另一端的位线BL3被选择,与其邻接的群组的位线的电压也不易受到选择位线BL0或BL3的选择电压VSA的影响。

虚设选择信号线SELU1可与选择信号线SEL1为同一信号,可在选择群组GP1时与选择信号线SEL1同时启动。此时,晶体管Tr4~Tr7成为接通状态,同时晶体管Tr12、Tr13也成为接通状态。通过使晶体管Tr12、Tr13成为接通状态,虚设位线BLU12、BLU13连接于非选择信号线VUB,成为非选择电压VBLU。由此,即便选择群组GP1的一端的位线BL4或另一端的位线BL7被选择,与其邻接的群组的位线的电压也不易受到选择位线BL4或BL7的选择电压VSA的影响。如此,在第2实施方式中,连接于选择群组的位线及虚设位线的晶体管都成为接通状态。连接于非选择群组的位线及虚设位线的晶体管都维持断开状态。

此处,图6是表示在选择群组GP0的情况下的状况的图。例如,如图6所示,在选择群组为GP0,选择位线为BL3的情况下,全局位线GBL0~GBL2传递非选择电压VBLU,全局位线GBL3传递选择电压VSA。此外,全局位线GBL0、GBL1也可为电性浮动状态。进而,选择信号线SEL0启动,选择群组GP0的晶体管Tr0~Tr3成为接通状态。由此,选择群组GP0的选择位线BL3上传递选择电压VSA,选择群组GP0的其它非选择位线BL0~BL2上传递非选择电压VBLU。此外,连接于全局位线GBL0、GBL1的非选择位线BL0、BL1也可为电性浮动状态。另一方面,因为非选择群组GP1的晶体管Tr4~Tr7维持断开状态,所以非选择群组GP1的位线BL4~BL7成为电性浮动状态。

也可与选择信号线SEL0同时启动虚设选择信号线SELU0。由此,晶体管Tr10、Tr11与晶体管Tr0~Tr3一起(大致同时)成为接通状态,处于选择群组GP0两侧的虚设位线BLU10、BLU11成为非选择电压VBLU。另一方面,虚设选择信号线SELU1维持断开状态,非选择群组GP1的虚设位线BLU12、BLU13与位线BL4~BL7同样地成为电性浮动状态。即,在群组GP1为非选择的情况下,与非选择群组GP1对应的选择信号线SEL1及虚设选择信号线SELU1维持断开状态。

浮动状态的非选择位线BL4相对于选择位线BL3未直接邻接,而介隔非选择电压VBLU的虚设位线BLU11配置。由此,位线BL3与位线BL4的电容耦合得到抑制,选择位线BL3的选择电压VSA不太影响非选择位线BL4。其结果,虽然非选择位线BL4为电性浮动状态,但其电压不太变动且稳定化。另外,由连接于选择位线BL3的记忆胞MC产生的热量不易传递至连接于非选择位线BL4的记忆胞MC。

反之,虽未图示,但例如在选择群组为GP1,选择位线为BL4的情况下,全局位线GBL1~GBL3传递非选择电压VBLU,全局位线GBL0传递选择电压VSA。此外,在此情况下,全局位线GBL2、GBL3也可为电性浮动状态。进而,选择群组GP1的晶体管Tr4~Tr7成为接通状态。由此,选择群组GP1的选择位线BL4上传递选择电压VSA,选择群组GP1的其它非选择位线BL5~BL7上传递非选择电压VBLU。此外,连接于全局位线GBL2、GBL3的非选择位线BL6、BL7也可为电性浮动状态。另一方面,因为非选择群组GP0的晶体管Tr0~Tr3维持断开状态,所以非选择群组GP0的位线BL0~BL3成为电性浮动状态。

在此情况下,可与选择信号线SEL1同时启动虚设选择信号线SELU1。由此,晶体管Tr12、Tr13与晶体管Tr4~Tr7一起(大致同时)成为接通状态,处于选择群组GP1两侧的虚设位线BLU12、BLU13成为非选择电压VBLU。另一方面,虚设选择信号线SELU0维持断开状态,非选择群组GP0的虚设位线BLU10、BLU11与位线BL0~BL3同样地成为电性浮动状态。

浮动状态的非选择位线BL3相对于选择位线BL4未直接邻接,而介隔非选择电压VBLU的虚设位线BLU12配置。由此,位线BL3与位线BL4的电容耦合得到抑制,选择位线BL4的选择电压VSA不太影响非选择位线BL3。其结果,虽然非选择位线BL3为电性浮动状态,但其电压不太变动且稳定化。另外,由连接于选择位线BL4的记忆胞MC产生的热量不易传递至连接于非选择位线BL3的记忆胞MC。

另外,在第2实施方式中,例如,仅使图6所示的与选择群组GP0对应的晶体管Tr10、Tr11为接通状态而对于虚设位线对BLU10、BLU11施加非选择电压VBLU。与其它非选择群组GP1对应的晶体管Tr12、Tr13维持断开状态,不对于虚设位线对BLU12、BLU13施加非选择电压VBLU。如此,在第2实施方式中,因为只要仅驱动与选择群组对应的虚设位线即可,所以能够降低消耗电力。

本实施方式的构成及功能也不仅可应用于列解码器CD,也可应用于行解码器RD。即,不仅可应用于“位线”,也可应用于“字线”。

(变形例)

在第2实施方式中,不论在选择群组的哪一位线被选择的情况下,周边电路PC都向选择群组的虚设位线施加非选择电压VBLU。

相对于此,在本变形例中,例如,仅在图6所示的位于选择群组GP0的一端的位线BL0、BL3被选择时,周边电路PC启动选择群组GP0的虚设选择信号线SELU0。在此情况下,在位于选择群组GP0的中间的位线BL1、BL2被选择时,周边电路PC不启动虚设选择信号线SELU0。

在位线BL1被选择的情况下,在邻接于选择位线BL1两侧的非选择位线BL0、BL2上施加非选择电压VBLU。另外,在位线BL2被选择的情况下,在邻接于选择位线BL2两侧的非选择位线BL1、BL3上施加非选择电压VBLU。所以,在位于选择群组GP0的中间的位线BL1、BL2被选择的情况下,该选择位线两侧的非选择位线上施加非选择电压VBLU。所以,在此情况下,选择电压VSA不易影响邻接的其它非选择位线,不需要启动选择群组GP0的虚设选择信号线SELU0。

对此,仅在位于选择群组GP0的一端的位线BL0、BL3被选择时,启动选择群组GP0的虚设选择信号线SELU0,在位于选择群组GP0的中间的位线BL1、BL2被选择时,不启动选择群组GP0的虚设选择信号线SELU0。由此,能够进一步降低消耗电力。

通常,各群组中所包含的位线BL的数量例如为64或者128等较大的数量。所以,各群组两端的位线数量为各2根,但中间的位线数量像62或者126一样,各群组中所包含的位线数量越增加就越增大。在此情况下,认为与各群组的中间的位线被选择的频率相比而言,各群组两端的位线被选择的频率比较小。所以,像本变形例这样,通过仅在位于选择群组的一端的位线被选择时,启动虚设选择信号线,能够大幅度削减消耗电力。

(第3实施方式)

图7是表示第3实施方式的列解码器CD内的多工器MUX的构成例的电路图。在第3实施方式中,在位于各群组GP0、GP1的各者的两端的位线BL0、BL3、BL4、BL7与非选择信号线VUB之间分别连接有作为第2晶体管的晶体管Tr10~Tr13。即,在位于各群组GP0、GP1的各者的两端的位线BL0、BL3、BL4、BL7各连接有2个晶体管,在其它中间的位线BL1、BL2、BL5、BL6各连接有1个晶体管。作为第2选择信号线的虚设选择信号线SELU0、SELU1与群组GP0、GP1的各者对应设置。虚设选择信号线SELU0共通连接于晶体管Tr10、Tr11的栅极电极,虚设选择信号线SELU1共通连接于晶体管Tr12、Tr13的栅极电极。在第3实施方式中,未设置虚设位线。晶体管Tr10~Tr13例如由p型MOSFET构成。所以,在第3实施方式中,虚设选择信号线SELU0、SELU1通过停止而活化(低活性(low active))。但是,晶体管Tr10~Tr13也可由n型MOSFET构成。另外,如果具有能够切换连接的切换功能,那么并不限定于晶体管。第3实施方式的其它构成可与第2实施方式的对应的构成相同。

在第3实施方式中,未设置虚设位线,位于各群组GP0、GP1的各者的两端的位线BL0、BL3、BL4、BL7兼具虚设位线的功能。

虚设选择信号线SELU0、SELU1在邻接的群组为选择群组的情况下停止,并活化。例如,在群组GP0为选择群组的情况下,与选择群组GP0邻接的邻接群组GP1的虚设选择信号线SELU1停止。虽未图示,但选择群组GP0的左邻的邻接群组的虚设选择信号线也停止。另一方面,在群组GP1为选择群组的情况下,与选择群组GP1邻接的邻接群组GP0的虚设选择信号线SELU0停止。另外,虽未图示,但选择群组GP1的右邻的邻接群组的虚设选择信号线也停止。邻接群组的虚设选择信号线可在启动选择群组的选择信号线的同时停止。

例如,图8是表示在选择群组GP0的情况下的状况的图。如图8所示,在群组GP0为选择群组的情况下,在选择群组GP0的选择信号线SEL0启动的同时,邻接群组GP1的虚设选择信号线SELU1停止。由此,在选择群组GP0的晶体管Tr0~Tr3成为接通状态的同时,邻接群组GP1的晶体管Tr12、Tr13也成为接通状态。通过使晶体管Tr12、Tr13成为接通状态,从而,位线BL4、BL7连接于非选择信号线VUB,成为非选择电压VBLU。即,位于邻接群组GP1两端的位线BL4、BL7成为非选择电压VBLU。由此,即便选择群组GP0的一端的位线BL3被选择,邻接群组GP1的位线BL4的电压也成为非选择电压VBLU。所以,位线BL4不易受到选择位线BL3的选择电压VSA的影响。在选择群组GP0的另一端的位线BL0被选择的情况下,未图示的左邻的邻接群组的端部的位线的电压成为非选择电压VBLU。所以,邻接群组的端部的位线也不易受到选择位线BL0的选择电压VSA的影响。此外,在位线BL3被选择的情况下,连接于邻接位线BL2的全局位线GBL2需要为非选择电压VBLU,但连接于其它非选择位线BL0、BL1的全局位线GBL0、GBL1可为浮动状态。

反之,虽未图示,但在群组GP1为选择群组的情况下,在选择群组GP1的选择信号线SEL1启动的同时,邻接群组GP0的虚设选择信号线SELU0停止。由此,在选择群组GP1的晶体管Tr4~Tr7成为接通状态的同时,邻接群组GP0的晶体管Tr10、Tr11也成为接通状态。通过使晶体管Tr10、Tr11成为接通状态,位线BL0、BL3连接于非选择信号线VUB,成为非选择电压VBLU。即,位于邻接群组GP0两端的位线BL0、BL3成为非选择电压VBLU。由此,即便选择群组GP1的一端的位线BL4被选择,邻接群组GP0的位线BL3的电压也成为非选择电压VBLU。所以,位线BL3不易受到选择位线BL4的选择电压VSA的影响。此外,在位线BL4被选择的情况下,连接于邻接位线BL5的全局位线GBL1需要为非选择电压VBLU,但连接于其它非选择位线BL6、BL7的全局位线GBL2、GBL3可为浮动状态。

另外,在选择群组GP1的另一端的位线BL7被选择的情况下,未图示的右邻的邻接群组的端部的位线的电压成为非选择电压VBLU。所以,邻接群组的端部的位线不易受到选择位线BL7的选择电压VSA的影响。

如此,可省略虚设位线,使各群组GP0、GP1两端的位线BL0、BL3、BL4、BL7具有虚设位线的功能。由此,虽然各群组GP0、GP1两端的位线BL0、BL3、BL4、BL7上需要追加的晶体管Tr10~Tr13,但因为不需要虚设位线,所以可减小列解码器CD整体的配置面积。进而,第3实施方式的周边电路PC仅将邻接于选择群组两侧的邻接群组的端部的位线设定为非选择电压VBLU。所以,第3实施方式与第2实施方式同样地能够降低消耗电力。

本实施方式的构成及功能也不仅可应用于列解码器CD,也可应用于行解码器RD。即,不仅可应用于“位线”,也可应用于“字线”。

(变形例)

在第3实施方式中,例如,不论在选择群组GP0的哪一位线被选择的情况下,周边电路PC都将邻接群组GP1的虚设选择信号线SELU1停止。

相对于此,在本变形例中,例如,仅在图8所示的位于选择群组GP0的一端的位线BL0、BL3被选择时,将邻接群组GP1的虚设选择信号线SELU1停止。在此情况下,在位于选择群组GP0的中间的位线BL1、BL2被选择时,周边电路PC不将虚设选择信号线SELU1停止。

在位线BL1被选择的情况下,在邻接于选择位线BL1两侧的非选择位线BL0、BL2上,经由晶体管Tr0、Tr2施加非选择电压VBLU。另外,在位线BL2被选择的情况下,在邻接于选择位线BL2两侧的非选择位线BL1、BL3上,经由晶体管Tr1、Tr3施加非选择电压VBLU。所以,在位于选择群组GP0的中间的位线BL1、BL2被选择的情况下,无需将邻接群组GP1的虚设选择信号线SELU1停止并活化。

对此,仅在位于选择群组GP0的一端的位线BL0、BL3被选择时,将邻接群组GP1的虚设选择信号线SELU1停止,在位于选择群组GP0的中间的位线BL1、BL2被选择时,不停止邻接群组GP1的虚设选择信号线SELU1。由此,能够进一步降低消耗电力。

如上所述,通常,各群组中所包含的位线BL的数量例如为64或者128等较大的数量。所以,像本变形例这样,通过仅在位于选择群组的一端的位线被选择时,将邻接群组的虚设选择信号线停止(活化),能够大幅度降低消耗电力。

(第4实施方式)

图9是表示第4实施方式的列解码器CD内的多工器MUX的构成例的电路图。在第4实施方式中,省略虚设位线,且在晶体管Tr20~Tr35对应位线BL20~BL35的各者分别设置1个这一方面与第3实施方式相同。

另一方面,在第4实施方式中,选择信号线SEL20~SEL27分别与2个晶体管或2根位线对应设置。例如,选择信号线SEL20共通连接于晶体管Tr20、Tr21的栅极电极。选择信号线SEL21共通连接于晶体管Tr22、Tr23的栅极电极。选择信号线SEL22共通连接于晶体管Tr24、Tr25的栅极电极。同样地,选择信号线SEL23~SEL27分别共通连接于晶体管Tr26、Tr27的栅极电极、晶体管Tr28、Tr29的栅极电极、晶体管Tr30、Tr31的栅极电极、晶体管Tr32、Tr33的栅极电极、及晶体管Tr34、Tr35的栅极电极。

在第1~第3实施方式中,各群组的4个晶体管藉由1根选择信号线共通地同时控制。另一方面,在第4实施方式中,群组GP0~GP3的各者中所包含的位线BL的数量为4,与此相对,选择信号线的数量为2。即,各群组GP0~GP3的4个晶体管由2个选择信号线分开控制。例如,群组GP0的晶体管Tr20、Tr21由选择信号线SEL20控制,晶体管Tr22、Tr23由选择信号线SEL21控制。如此,通过使1个群组内的晶体管的控制单位变小(变细),可进行更加灵活的控制。

例如,图10是表示在选择群组GP1的位线BL27的情况下的状况的图。如图10所示,在选择群组GP1的位线BL27的情况下,全局位线GBL0~GBL2传递非选择电压VBLU,全局位线GBL3传递选择电压VSA。此外,全局位线GBL1也可为电性浮动状态。进而,选择信号线SEL23、SEL24启动,选择群组GP1的晶体管Tr26、Tr27及非选择群组GP2的晶体管Tr28、Tr29成为接通状态。由此,选择群组GP1的选择位线BL27上传递选择电压VSA,选择群组GP1的非选择位线BL26、非选择群组GP2的非选择位线BL28、BL29上传递非选择电压VBLU。此外,连接于全局位线GBL1的非选择位线BL29也可为电性浮动状态。因为其它晶体管Tr20~Tr25、Tr30~Tr35维持断开状态,所以与这些晶体管对应的非选择位线BL20~BL25、BL30~BL35成为电性浮动状态。

在此情况下,邻接于选择位线BL27两侧的非选择位线BL26、BL28成为非选择电压VBLU。由此,非选择位线BL26、BL28不受选择位线BL27的选择电压VSA影响。另外,因为其它非选择位线并非与选择位线BL27直接邻接,所以不易受到选择位线BL27的选择电压VSA的影响。

虽未图示,但例如,在选择群组GP1的位线BL26的情况下,全局位线GBL0、GBL1、GBL3传递非选择电压VBLU,全局位线GBL2传递选择电压VSA。此外,全局位线GBL0也可为电性浮动状态。进而,选择信号线SEL22、SEL23启动,选择群组GP1的晶体管Tr24~Tr27成为接通状态。由此,选择群组GP1的选择位线BL26上传递选择电压VSA,选择群组GP1的非选择位线BL24、BL25、BL27上传递非选择电压VBLU。此外,连接于全局位线GBL0的非选择位线BL24也可为电性浮动状态。因为其它晶体管Tr20~Tr23、Tr28~Tr35维持断开状态,所以与这些晶体管对应的非选择位线BL20~BL23、BL28~BL35成为电性浮动状态。

在此情况下,邻接于选择位线BL26两侧的非选择位线BL25、BL27成为非选择电压VBLU。由此,非选择位线BL25、BL27不受选择位线BL26的选择电压VSA影响。另外,因为其它非选择位线并非与选择位线BL26直接邻接,所以不易受到选择位线BL26的选择电压VSA的影响。

如果将1个群组中所包含的位线BL的数量设为m(m为2以上的整数),将全局位线的数量设为j,那么全局位线的数量j成为与m相等或者其以上的整数。另外,如果将与1个群组对应的选择信号线的数量设为k,那么k成为1以上的整数。所以,式1成立。

m≦j×k (式1)

另外,因为1个群组的选择信号线的数量k不会超过1个群组的位线的数量m,所以式2成立。

m≧k (式2)

结合式1及式2,成为式3。

k≦m≦j×k (式3)

以满足式3的方式设定j、k、m即可。

在第1~第3实施方式中,m=j且k=1。在第4实施方式中,m=j且k=2。如果增大1个群组的选择信号线的数量k,那么1个群组内的位线BL的控制单位变小。所以,第4实施方式与第1~第3实施方式相比,位线BL的控制单位变小,即便不设置虚设位线及追加的晶体管,也可将与选择位线邻接的非选择位线设定为非选择电压VBLU。

另外,通过将位线BL20~BL27的控制单位分割得较小,可避免将并非与选择位线邻接的其它非选择位线以非选择电压VBLU驱动。例如,在图10的选择位线BL27的情况下,非选择位线BL20~BL25、BL30~BL35无需以非选择电压VBLU驱动,可仍为浮动状态。由此,与位线BL的控制单位较大的情况相比可降低消耗电力。此外,并非与选择位线邻接的其它非选择位线可为了使解码器部的面积最优化而以非选择电压VBLU驱动。

本实施方式的构成及功能也不仅可应用于列解码器CD,也可应用于行解码器RD。即,不仅可应用于“位线”,也可应用于“字线”。

(变形例)

图11是表示第4实施方式的变形例的列解码器CD内的多工器MUX的构成例的电路图。在本变形例中,省略虚设位线,且在晶体管Tr20~Tr35对应位线BL20~BL35的各者分别设置1个这一方面与第4实施方式相同。另外,本变形例在所述式3成立这一方面也与第4实施方式相同。其中,全局位线的数量j(j=m)为8,随之,1个群组中所包含的位线BL的数量m也为8。与1个群组对应的选择信号线的数量k为2。另外,各选择信号线SEL20~SEL23所控制的位线的数量分别为4。即,位线BL20~BL35的控制单位成为4。所以,虽然本变形例的位线BL20~BL35的控制单位、m、j与第4实施方式的这些不同,但本变形例在满足式3这一方面与第4实施方式相同。此外,位线BL20~BL35的控制单位为4,因为大于第4实施方式的位线BL20~BL35的控制单位,所以本变形例的消耗电力的降低效果小于第4实施方式的消耗电力的降低效果。

例如,图12是表示在选择群组GP0的位线BL27的情况下的状况的图。如图12所示,在选择群组GP0的位线BL27的情况下,全局位线GBL0~GBL6传递非选择电压VBLU,全局位线GBL7传递选择电压VSA。此外,全局位线GBL1~GBL5也可为电性浮动状态。进而,选择信号线SEL21、SEL22启动,选择群组GP0的晶体管Tr24~Tr27及非选择群组GP1的晶体管Tr28~Tr31成为接通状态。由此,选择群组GP0的选择位线BL27上传递选择电压VSA,选择群组GP0的非选择位线BL24~BL26、非选择群组GP1的非选择位线BL28~BL31上传递非选择电压VBLU。此外,连接于全局位线GBL1~GBL5的非选择位线BL24、BL25、BL29~BL31也可为电性浮动状态。因为其它晶体管Tr20~Tr23、Tr32~Tr35维持断开状态,所以与这些晶体管对应的非选择位线BL20~BL23、BL32~BL35成为电性浮动状态。

在此情况下,邻接于选择位线BL27两侧的非选择位线BL26、BL28成为非选择电压VBLU。由此,非选择位线BL26、BL28不受选择位线BL27的选择电压VSA影响。另外,因为其它非选择位线并非与选择位线BL27直接邻接,所以不易受到选择位线BL27的选择电压VSA的影响。

(全局位线的MUX)

图13是表示全局位线GBL0~GBL3与感测放大器SA或非选择电压生成部VBLUGEN之间的多工器MUX2的构成例的电路图。多工器MUX2为设定全局位线GBL0~GBL3的电压的电路。多工器MUX2对任一根全局位线GBL0~GBL3施加选择电压VSA,对其它3根施加非选择电压VBLU,或者成为电性浮动状态。

多工器MUX2具备n型MOSFETN0~N3(以下为晶体管N0~N3)及p型MOSFETP0~P3(以下为晶体管P0~P3)。晶体管N0~N3共通连接于感测放大器SA且传递选择电压VSA。晶体管P0~P3共通连接于非选择电压生成部VBLUGEN且传递非选择电压VBLU。此外,晶体管N0~N3可由p型MOSFET构成,晶体管P0~P3可由n型MOSFET构成。另外,如果具有能够切换连接的切换功能,那么并不限于晶体管。

晶体管N0~N3的栅极电极分别连接于电压选择信号线GSEL0~GSEL3。另外,晶体管P0~P3的栅极电极分别连接于电压非选择信号线GSELU0~GSELU3。此外,晶体管N0及晶体管P0的栅极电极可共通连接于电压选择信号线GSEL0。晶体管N1及晶体管P1的栅极电极可共通连接于电压选择信号线GSEL1。晶体管N2及晶体管P2的栅极电极可共通连接于电压选择信号线GSEL2。晶体管N3及晶体管P3的栅极电极可共通连接于电压选择信号线GSEL3。此时,晶体管N0~N3与晶体管P0~P3互补动作,将选择电压VSA或非选择电压VBLU的任一者向全局位线GBL0~GBL3传递。此外,在使全局位线成为电性浮动状态的情况下,只要使与该全局位线对应的晶体管(P0~P3的任一者)成为断开状态即可。

例如,在全局位线GBL3上传递选择电压VSA,其它全局位线GBL0~GBL2上传递非选择电压VBLU的情况下,周边电路PC启动电压选择信号线GSEL3,停止电压非选择信号线GSELU0~GSELU2。由此,晶体管N3向全局位线GBL3传递选择电压VSA,晶体管P0~P2向全局位线GBL0~GBL2传递非选择电压VBLU。此外,在使全局位线GBL0、GBL1成为浮动状态的情况下,只要使晶体管P0、P1成为断开状态即可。

如此,多工器MUX2可选择性地使全局位线GBL0~GBL3的任一者成为选择电压VSA。

图14是表示全局位线GBL0~GBL7与感测放大器SA或非选择电压生成部VBLUGEN之间的多工器MUX2的其它构成例的电路图。图14表示与8根全局位线GBL0~GBL7对应的多工器MUX2的构成例。

多工器MUX2具备晶体管N0~N7及晶体管P0~P7。晶体管N0~N7及晶体管P0~P7的构成可与图13所示的晶体管N0~N7及晶体管P0~P7的构成相同。

晶体管N0~N7的栅极电极分别连接于电压选择信号线GSEL0~GSEL7。另外,晶体管P0~P7的栅极电极分别连接于电压非选择信号线GSELU0~GSELU7。在分别连接电压选择信号线GSEL0~GSEL7及电压非选择信号线GSELU0~GSELU7时,各晶体管N0~N7与晶体管P0~P7互补动作,各晶体管N0~N7及晶体管P0~P7将选择电压VSA或非选择电压VBLU的任一者向全局位线GBL0~GBL7传递。此外,在使全局位线成为电性浮动状态的情况下,只要使与该全局位线对应的晶体管(P0~P7的任一者)成为断开状态即可。

例如,在全局位线GBL3上传递选择电压VSA,其它全局位线GBL0~GBL2、GBL4~GBL7上传递非选择电压VBLU的情况下,周边电路PC启动电压选择信号线GSEL3,停止电压非选择信号线GSELU0~GSELU2、GSELU4~GSELU7。由此,晶体管N3向全局位线GBL3传递选择电压VSA,晶体管P0~P2、P4~P7向全局位线GBL0~GBL2、GBL4~GBL7传递非选择电压VBLU。此外,在使全局位线GBL0、GBL1、GBL5~GBL7成为浮动状态的情况下,只要使晶体管P0、P1、P5~P7成为断开状态即可。

如此,多工器MUX2可选择性地使全局位线GBL0~GBL7的任一者成为选择电压VSA。此外,多工器MUX2的构成并不限定于这些。

已对本发明的若干实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些实施方式能以其它多种方式实施,且能够在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

[符号说明]

1 存储器芯片

MCA 记忆胞阵列

CD 列解码器

RD 行解码器

SA 感测放大器

PC 周边电路

MUX 多工器

BL 位线

WL 字线

GP0、GP1 群组

GBL0~GBL3 全局位线

Tr0~Tr7 晶体管

SEL0、SEL1 选择信号线

VUB 非选择信号线

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统