一种局部放电UHF传感器及数据采集系统

文献发布时间:2023-06-19 10:16:30

技术领域

本发明涉及气体绝缘开关领域,特别涉及一种局部放电UHF传感器及数据采集系统。

背景技术

气体绝缘开关设备(Gas lnsulated Switchgear,GIS)是特高压电网中的重要组成设备之一,它将一座变电站中的断路器、电流互感器、电压互感器、避雷器、隔离开关、接地开关、母线、电缆终端、进出线套管等优化设计后分别装在各自密封间中最后集中组装在一个充以SF6作为绝缘介质的整体外壳中。尽管高压GIS基本属于检修周期较长的高压开关设备,但是从近40年的投入使用的GIS运行状况看,其内部的绝缘缺陷会引起内导体和外壳之间的绝缘部分击穿,即发生局部放电。局部放电发生时伴随有物理的、化学的、光的、电以及磁的效应。实用的GIS的局部放电检测方法大致可以分为耦合电容法、超声波法、超高频法、化学法、光学法。

在现有技术当中,对用于高压GIS局部放电检测的超高频传感器进行了研究,设计了灵敏度及抗干扰能力强的超高频传感器,并对其进行了频率响应特性分析,研发出了基于UHF法的高压GIS局部放电在线监测系统。也有在超高频传感器电磁耦合及电磁波信号传输特性方面展开了专门的研究,针对GIS同轴结构中局部放电脉冲所激发的电磁波宽频带特性,设计出一种新型局部放电超高频检测非频变超高宽带天线,可满足GIS局部放电超高频检测要求,建立的系统可以方便地实现GIS局部放电检测和局部放电源的定位。同时,现有技术中还建立了基于超高频包络检波的GIS局部放电检测系统,分析了检测系统测量过程中可能混入的几种噪声,证明了包络检波后信号中的噪声主要是白躁声,并采用基于小波变换的滤波算法对白噪声进行了抑制,提出了改进阀值的小波滤波算法。在GIS PD信号的理论仿真方面,现有技术均采用传统的脉冲波形描述PD信号,如单指数衰减脉冲、双指数衰减脉冲、单指数衰减震荡脉冲、双指数衰减振荡脉冲。

以上的研究都是建立在天线和高速示波器构成的局放仪上,但所使用的天线如对数周期天线和阿基米德螺旋天线具有尺寸大的缺点,高速示波器具有体积大和笨重的劣势。

发明内容

本发明所要解决的技术问题是:提供一种结构简单、空间占有率高的分形天线结构,来提高UHF传感器的灵敏度;再基于这种UHF传感器设计一套高速大容量数据采集系统。

本发明解决上述问题所采用的技术方案为:一种局部放电UHF传感器,所述UHF传感器置于盆式绝缘子金属环的法兰孔上,所述UHF传感器包括天线和腔体,所述腔体包括与金属环接触的腔体面和金属腔体面,所述腔体内设有吸波材料,所述天线置于吸波材料上,所述天线与一同轴馈线连接。

优选的,所述腔体面为透波材料,所述金属腔体为金属屏蔽材料。这样,透波材料的透波性能提高UHF传感器的灵敏度;金属屏蔽材料屏蔽干扰信号的作用,同时也能够保护天线免受腐蚀的作用。

优选的,所述天线为Hilbert分形天线,所述Hilbert分形天线的阶数为3,FR4介质板厚度为1.6mm,导线宽度为2mm,天线边长为8mm。这样设计的天线具有宽频带和小尺寸的优点。

本申请还包括一种局部放电数据采集系统,包括信号调理电路、AD转换电路、FPGA最小系统、SDRAM数据缓存模块、STM32最小系统、LCD数据显示模块、SD卡数据记录模块和以太网数据传输模块;

所述信号调理电路通过一对数检波器与UHF传感器连接,所述信号调理电路通过AD转换电路与FPGA最小系统连接,所述FPGA最小系统通过STM32最小系统与以太网数据传输模块,所述FPGA最小系统与SDRAM数据缓存模块连接,所述STM32最小系统与LCD数据显示模块和SD卡数据记录模块连接。

这样设计的局部放电数据采集系统具有体积小,便于携带,采样速率高,存储容量大的优点,并集数据记录、数据显示和数据传输三种功能于一体,特别适合于制作便携式GIS超高频局放仪用。

优选的,FPGA最小系统包括:

PLL,与外部有源晶振连接,输出时钟信号;

系统控制模块,与STM32最小系统连接;

串并转换模块,所述PLL与一ADC08200连接,所述串并转换模块将ADC08200输出的8bit位宽数据转换为32bit位宽数据后,在系统控制模块的控制下写入异步FIFO;

SDRAM控制模块,与系统控制模块连接,产生SDRAM的初始化配置及SDRAM的数据读写指令;

SDRAM IP核,与SDRAM控制模块连接,所述SDRAM IP核接收异步FIFO的数据,且接收SDRAM控制模块的控制指令后产生相应的SDRAM芯片的控制时序;

同步FIFO,接收SDRAM IP核的数据,用于SDRAM数据读出速率和相对低速的SPI接口通信速率的匹配;

SPI控制模块,接收同步FIFO的数据,并将FIFO的数据转换成遵守SPI总线协议的数据。

优选的,所述PLL输出两路时钟信号,包括一路200MHz的时钟,与ADC08200连接;另一路100MHz的时钟,与系统控制模块和SDRAM芯片连接。

与现有技术相比,本发明的优点在于:采用有限元软件仿真和天线实测的方法,解决局部放电检测用天线的尺寸和低谐振频率的矛盾;采用传输线理论中的透射系数和反射系数的求解方法分析材料的透波性能,从理论上建立一套电介质材料透波性能的计算方法;采用FPGA+SDRAM的方法解决对数据采集系统的采样速率指标和存储容量指标较高的问题,另外加入数据显示、数据传输和数据保存等功能,达到局放仪对便携式的要求。

附图说明

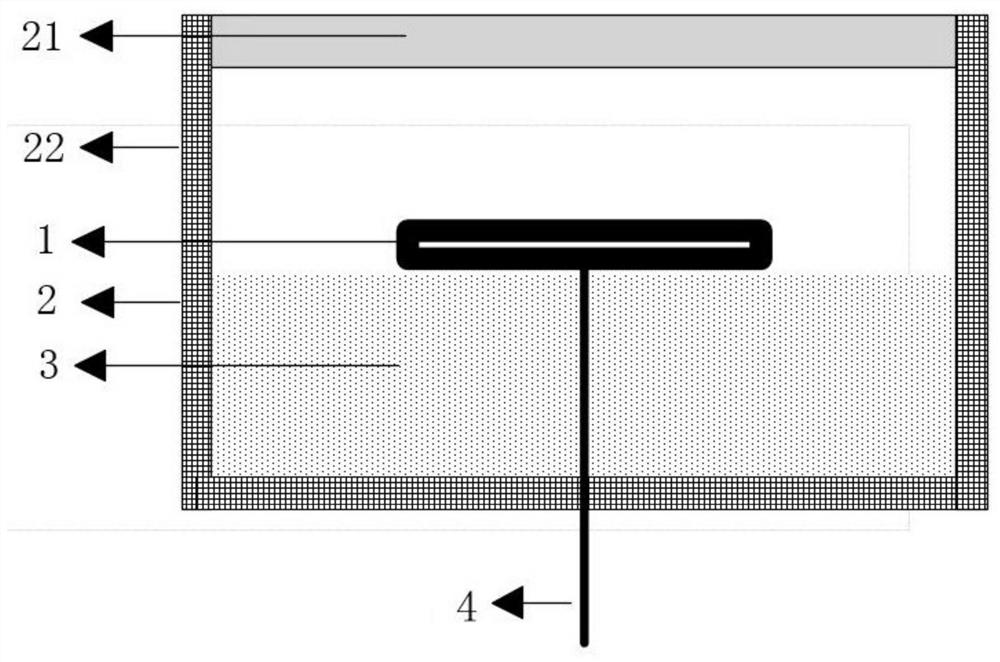

图1本发明局部放电UHF传感器结构示意图;

图2本发明局部放电数据采集系统连接示意图;

图3本发明天线结构示意图;

图4本发明天线驻波比图;

图5本发明局部放电数据采集系统框架图;

图6本发明FPGA最小系统结构示意图。

图中附图标记:1、天线、2、腔体、21、腔体面,22、金属腔体面,3、吸波材料,4、同轴馈线。

具体实施方式

下面结合附图对本发明的实施例作进一步描述。

通信领域应用的小型化超高频天线的谐振频率通常高于数千兆赫兹,而且通频带非常窄。局部放电超高频检测频带通常介于300MHz至3000MHz之间,如将超高频天线用于GIS局部放电测量中,需通过增大天线尺寸来降低谐振频率,以满足测量要求,这与GIS局部放电在线监测对小型化超高频天线设计的要求相矛盾,故需研制一种尺寸小同时谐振频率较低的天线。

如图1所示,本实施例涉及一种局部放电UHF传感器,UHF传感器置于盆式绝缘子金属环的法兰孔上,UHF传感器包括天线1和腔体2,腔体2包括与金属环接触的腔体面21和金属腔体面22,所述腔体2内设有吸波材料3,天线1置于吸波材料3上,天线1与一同轴馈线4连接。传感器腔体的主要作用有:安装固定的作用;屏蔽干扰信号的作用;保护天线免受腐蚀的作用。从金属法兰处泄露的超高频信号比较微弱,所以透波材料的透波性能对外置式GIS超高频传感器的灵敏度有重要影响。

在本实施例中,腔体面21为透波材料,金属腔体面22为金属屏蔽材料。这样,透波材料的透波性能提高UHF传感器的灵敏度;金属屏蔽材料屏蔽干扰信号的作用,同时也能够保护天线免受腐蚀的作用。

如图3-4所示,在本实施例中,采用HFSS软件建立Hilbert分形天线模型:

Hilbert分形曲线是一种结构简单、空间占有率高的分形结构。在外围尺寸不变的情况下,随着分形阶数的增加,曲线总长度呈几何级数增长,并且呈现严格的自相似性。小型化Hilbert分形天线的谐振频率较高,通过优化设计天线的几何结构及参数,使天线最低谐振频率处于局部放电超高频检测频带中,从而用于GIS局部放电。图3中Hilbert分形天线的结构参数:阶数为3,FR4介质板厚度为1.6mm,导线宽度为2mm,天线边长为8mm,最终HFSS仿真出天线的VSWR如图4所示。驻波比小于5的带宽包括616MHz-660MHz,699MHz-747MHz,781MHz-941MHz and 968MHz-1.461GHz,共745MHz,具有宽频带和小尺寸的优点。

如图2所示,局放信号经过对数检波后,其包络信号在2MHz-20MHz之间,所以用于超高频局放仪的数据采集系统,采样频率至少需在200MHz及以上,缓存容量至少需要能够连续存储两个工频周期的数据,即对局放信号的一次采样就至少需要64Mb的缓存容量。但通用型数据采集卡很难在采样速率指标和缓存容量指标上同时满足GIS超高频局放仪的要求,故需针对局放信号设计一套高速大容量数据采集系统。

如图5所示,在本实施例中,高速大容量的数据采集系统采用FPGA+STM32的架构,包括信号调理电路、AD转换电路、FPGA最小系统、SDRAM数据缓存模块、STM32最小系统、LCD数据显示模块、SD卡数据记录模块和以太网数据传输模块。本实施例实现以200MHz的采样速率、8bit的精度连续采样8个工频周期数据的性能指标,具有体积小,便于携带,采样速率高,存储容量大的优点,并集数据记录、数据显示和数据传输三种功能于一体,特别适合于制作便携式GIS超高频局放仪用。

如图6所示,在本实施例中,FPGA内部逻辑电路包括PLL、串并转换模块、异步FIFO、SDRAM IP核、同步FIFO、SPI控制模块、SDRAM控制模块、系统控制模块。

其中,PLL将由外部有源晶振输入的时钟倍频产生两路时钟,一路200MHz的时钟通过FPGA的专用时钟输出引脚作为ADC08200的驱动时钟,一路100MHz的时钟作为FPGA内部逻辑电路的驱动时钟和SDRAM的驱动时钟。

串并转换模块将ADC08200输出的8bit位宽数据转换为32bit位宽数据后,在系统控制模块的控制下写入异步FIFO。

异步FIFO的作用是匹配200M的AD采样速率和100MHz的SDRAM数据写入速率。

SDRAM IP核为ATERA公司发布的开源代码,作用是接收SDRAM控制模块的控制指令后产生相应的SDRAM芯片的控制时序。

同步FIFO用于100M的SDRAM数据读出速率和相对低速的SPI接口通信速率的匹配。

SDRAM控制模块用于产生SDRAM的初始化配置及SDRAM的数据读写指令。

SPI控制模块用于将并行数据转换成遵守SPI总线协议的数据。

FPGA内部逻辑电路中的SPI控制模块作为SPI从机,STM32最小系统中的SPI控制器作为SPI主机。

系统控制模块用于解析STM32最小系统发送的控制命令以及协调FPGA内部逻辑电路中的异步FIFO、SDRAM控制模块、同步FIFO和SPI控制模块的工作。

可以看出,数据流在FPGA内部逻辑电路中的流向为串并转换模块→异步FIFO→SDRAM IP核→写入SDRAM芯片→从SDRAM芯片中读出→同步FIFO→SPI控制模块。

本发明的有益效果为:采用有限元软件仿真和天线实测的方法,解决局部放电检测用天线的尺寸和低谐振频率的矛盾;采用传输线理论中的透射系数和反射系数的求解方法分析材料的透波性能,从理论上建立一套电介质材料透波性能的计算方法;采用FPGA+SDRAM的方法解决对数据采集系统的采样速率指标和存储容量指标较高的问题,另外加入数据显示、数据传输和数据保存等功能,达到局放仪对便携式的要求。

上述说明示出并描述了本发明的若干优选实施例,但如前所述,应当理解本发明并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述发明构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

- 一种局部放电UHF传感器及数据采集系统

- 一种局部放电UHF检测的蝶形天线及UHF检测传感器