在晶圆测试过程中检测电子位图中坐标偏移的方法

文献发布时间:2023-06-19 10:19:37

技术领域

本发明涉及集成电路中晶圆测试数据验证领域,尤其涉及一种在晶圆测试过程中检测电子位图中坐标偏移的方法。

背景技术

半导体电路初始形态是以晶圆的形式被制造出来,晶圆是一个圆形硅片,在这个硅片基础之上,建立了许多独立的电路,一片晶圆上这种单个独立电路被称为芯片(die)。当晶圆制造完成后,需要经过晶圆测试(CP,Circuit probing)进行筛选测试,符合器件特征或测试规格书要求的芯片为良品(good die);反之,不符合要求的芯片为不良品(baddie)。任何一颗芯片在晶圆上有其确定的坐标位置,完成晶圆测试以后,测试系统会产生一个电子位图(map),用以记录芯片在晶圆上的坐标以及良品/不良品的CP筛选测试结果。经过晶圆测试以后的晶圆需经过减薄/划片/引线键合等一系列封装加工工艺过程,最终得到一颗合格的封装芯片。早期的芯片加工过程是在晶圆测试后,根据晶圆测试的筛选测试结果,在晶圆上将不良芯片打上墨点,良品芯片不作任何标记,以区分良品和不良品。在其后的封装过程中,封装设备可以识别出没有墨点标识的良品,进行摘片和封装,将有墨点标识的不良品留在晶圆上。随着技术的发展,芯片尺寸越来越小,在如此小尺寸的芯片上打墨点已经变得不太可能,目前已采用非打点技术进行封装摘片,即封装设备通过识别未打墨点的电子位图(inkless map)的电子文件进行良品和不良品芯片的识别区分,省去了在不良芯片上打点的工艺过程。在晶圆测试过程后,晶圆测试厂将晶圆和其电子位图交给封装厂,封装厂将通过晶圆测试的最终站点的电子位图挑选良品,再经过FT测试厂Final test(FT测试),筛选出的良品才是最后被使用的合格芯片。

但是由于各种原因,在电子位图生成中,电子位图中的芯片坐标可能会有偏移,将会引起封装摘片错误,将不良品作为良品摘取并完成封装;反之,也会将良品作为不良品丢弃在晶圆上。从晶圆测试厂转移到封装厂的晶圆电子位图尤为重要,一个有着坐标偏移的电子位图会导致良品的大量损失和不良品流向市场的巨大风险。所以检查晶圆测试过程中电子位图是否有坐标偏移的现象就变得十分重要。早先的方法是将最后一道晶圆测试的电子位图当作封装厂摘片的电子位图,这个方法很容易出现坐标偏移的情况,这有很大风险。如果前几道晶圆测试过程中有一次出现了电子位图坐标偏移,或者选错电子位图模板,就会使接下来的封装摘片错误,不可避免地造成损失。特别是如今为了满足消费者对高品质生活的追求,芯片做的越来越小,一些芯片需要在磨薄后直接与其他芯片合封,坐标偏移会造成合封后大批量的合封片不能使用,造成极大的损失。

发明内容

本发明的目的在于提供一种在晶圆测试过程中检测电子位图中坐标偏移的方法,在晶圆测试过程中及时发现并阻止电子位图坐标偏移现象的发生,消除了测试厂的隐患和风险,提高了晶圆测试后的产品良率,大大降低了封装厂挑错芯片的可能性,减少了晶圆损失,减小了晶圆流入市场的风险,提高了量产的合格率。

为了达到上述目的,本发明提供一种在晶圆测试过程中检测电子位图中坐标偏移的方法,包含以下步骤:依次对晶圆上的待测芯片进行多道晶圆测试,将每道晶圆测试后产生的所有电子位图叠加形成一张叠加电子位图,所述叠加电子位图上的叠加测试结果按照测试先后顺序显示了所述晶圆上的每个待测芯片的每道测试结果,自动统计叠加电子位图上的叠加测试结果,当叠加测试结果中显示至少一个芯片的前道测试结果为不良品,而后道测试结果为良品,和/或当叠加测试结果中显示了至少一道测试结果,同时至少一个芯片缺少了至少一道测试结果,则判断电子位图出现了坐标偏移。

只有在前道晶圆测试中显示为良品的芯片,才能够进行下道晶圆测试。

当叠加测试结果中显示所有芯片的每道测试结果完全一致,则判断某道晶圆测试程序出现错误。

根据预先设定的测试模板所规定的测试范围进行晶圆测试:位于测试模板范围内的芯片允许被进行晶圆测试,获得测试结果,位于测试模板范围外的芯片不允许被进行晶圆测试,无法获得测试结果。

只有叠加测试结果中显示某个芯片的所有测试结果都为良品,才能判断该芯片确为良品。

只要叠加测试结果中显示某个芯片的某道测试结果为不良品,就判断该芯片为不良品。

本发明可以在晶圆测试过程中及时发现并阻止电子位图坐标偏移现象的发生,消除了测试厂的隐患和风险,提高了晶圆测试后的产品良率,大大降低了封装厂挑错芯片的可能性,减少了晶圆损失,减小了晶圆流入市场的风险,提高了量产的合格率。本发明适用于晶圆测试中生成的任何电子位图,且适用于对任何芯片的晶圆测试。

附图说明

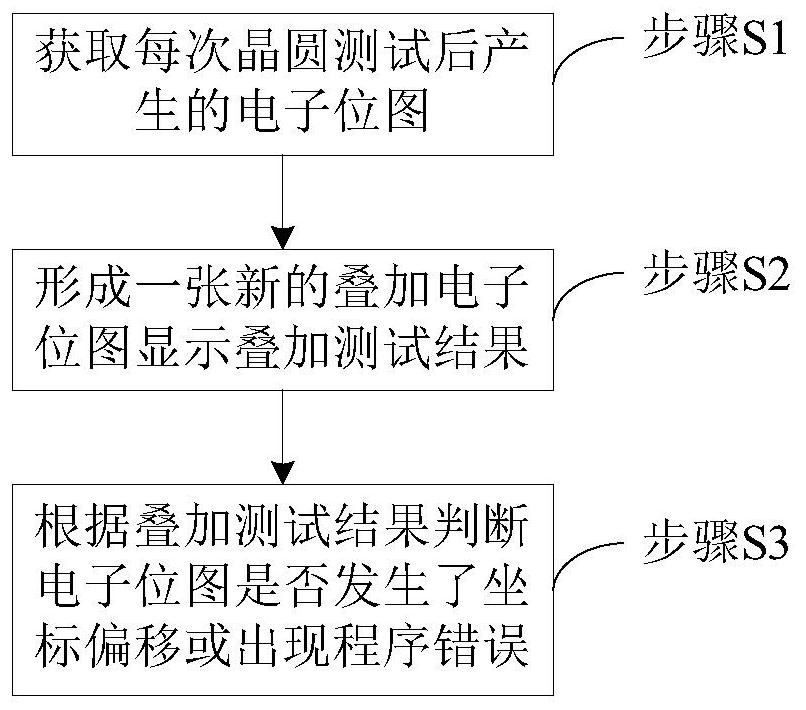

图1是本发明实施例中一种在晶圆测试过程中检测电子位图中坐标偏移的方法的流程图。

图2是本发明实施例中晶圆测试产生的电子位图的示意图。

图3是本发明实施例中叠加电子位图的示意图。

具体实施方式

以下根据图1~图3,具体说明本发明的较佳实施例。

如图1所示,本发明提供一种在晶圆测试过程中检测电子位图中坐标偏移的方法,包含以下步骤:

步骤S1、获取每道晶圆测试后产生的电子位图;

步骤S2、将所有电子位图叠加,形成一张新的叠加电子位图,该叠加电子位图中同时显示同一个位置上的芯片的每道测试结果,形成叠加测试结果;

步骤S3、自动统计叠加电子位图中所有位置上的芯片的叠加测试结果,根据叠加测试结果判断电子位图是否发生了坐标偏移或出现程序错误;

其中,如果叠加测试结果中显示所有芯片的每道测试结果完全一致,则说明某道测试程序出现错误,或者某道晶圆测试没有进行;

如果叠加测试结果中显示至少一个芯片的前道测试结果为不良品,而后道测试结果为良品,则说明发生了坐标偏移,或者出现了程序错误。

在本发明的一个实施例中,如图2所示,以字符“A”代表“良品”,以字符“X”代表“不良品”,以字符“·”代表“非测试芯片”,进行说明。“良品”、“不良品”、“非测试芯片”都可以使用别的字符代替。

晶圆上的芯片不是所有都能用的,在晶圆从制造厂出厂时,通常会将能用的芯片设定一个范围,这个芯片范围内的芯片全部被认为是“A”,然后不能使用的芯片一律被认为是“·”,从而制作出测试模板(goldenmap)。该测试模板会被发送至晶圆测试厂,以确定测试范围。在测试模板范围内的芯片才能使用,在测试模板范围外的芯片哪怕能通过所有的晶圆测试,也会因为其具有风险,不会被采用(这一部分芯片不会被进行晶圆测试)。

晶圆测试一般会包含2~3道测试过程,在本实施例中,以进行第一道晶圆测试CP1和第二道晶圆测试CP2为例,客户或封装厂接收晶圆测试厂发送的第一道晶圆测试CP1产生的第一电子位图和第二道晶圆测试CP2产生的第二电子位图,将需要叠加的第一电子位图和第二电子位图放入一个文件夹下,调取该文件夹内的第一电子位图和第二电子位图,将第一电子位图和第二电子位图叠放在一起,将叠加后的值作为新的电子位图的状态,形成一张新的叠加电子位图。所述叠加电子位图中相同的位置会出现相同芯片两道晶圆测试的结果,所述叠加电子位图显示各芯片的状态和坐标。

如图3所示,若在CP1测试时,芯片的测试结果为A,在CP2测试时,位于同一位置上的这颗芯片的测试结果为A,则叠加电子位图中这颗芯片的叠加测试结果为AA;若在CP1测试时,芯片的测试结果为A,在CP2测试时,位于同一位置上的这颗芯片的测试结果为X,则叠加电子位图中这颗芯片的叠加测试结果为AX;若在CP1测试时,芯片的测试结果为X,在CP2测试时,位于同一位置上的这颗芯片的测试结果为A,则叠加电子位图中这颗芯片的叠加测试结果为XA;若在CP1测试时,芯片的测试结果为X,在CP2测试时,位于同一位置上的这颗芯片的测试结果为X,则叠加电子位图中这颗芯片的叠加测试结果为XX;若在CP1测试时,芯片的测试结果为·,在CP2测试时,位于同一位置上的这颗芯片的测试结果为·,则叠加电子位图中这颗芯片的叠加测试结果为··;若缺少CP1测试的测试结果或缺少CP2测试的测试结果,则叠加电子位图中这颗芯片的叠加测试结果为error(错误)。Error有·A,·X,A·,X·这4种情况,即此颗芯片只测试了一次。

在本实施例中,将叠加电子位图中每个芯片的叠加测试结果用不同颜色标注出来,例如,用绿色标注AA,用蓝色标注AX,用红色标注XA,用黄色标注XX,用紫色标注error,一目了然,以便查找结果和确定位置。

将叠加电子位图中所有位置上的芯片的叠加测试结果分别统计归类,形成统计表格,如表1所示,叠加测试结果为AA的芯片数量为6305个,叠加测试结果为AX的芯片数量为739个,叠加测试结果为XA的芯片数量为0个,叠加测试结果为XX的芯片数量为517个,叠加测试结果为··的芯片数量为456个,叠加测试结果为error的芯片数量为0个。

表1

当芯片的叠加测试结果为AA,说明第一道晶圆测试CP1和第二道晶圆测试CP2对该芯片的测试结果一致,该芯片确实为良品;当芯片的叠加测试结果为XX时,说明第一道晶圆测试CP1和第二道晶圆测试CP2对该芯片的测试结果一致,该芯片确实为不良品。

当芯片的叠加测试结果为AX,说明该芯片在第一道晶圆测试CP1时为良品,在第二道晶圆测试CP2时为不良品,则该芯片最终被定为不良品,且这种情况在逻辑上是允许的。

在进行晶圆测试时,是按照顺序进行多道测试的。在本实施例中,先进行第一道晶圆测试CP1,再进行第二道晶圆测试CP2,第一道晶圆测试CP1的所有测试项通过为良品,则在芯片内部存储区写入良品标识A,在第二道晶圆测试CP2开始时先读第一道晶圆测试CP1的良品标识,只有读出良品标识A成功的芯片,才继续完成当前第二道晶圆测试CP2的全部测试。所以在逻辑上不会出现芯片在CP1测试时为不良品,却在CP2测试时为良品的情况,也就是说,如果芯片的叠加测试结果为XA,则说明叠加测试结果不符合逻辑规律,说明发生了坐标偏移。CP1测试的不良品在逻辑上是不可能参加CP2测试的。但是事实上,叠加测试结果为XA和error的可能性都会出现。XA的出现可能在于测试机或者测试针卡被动过,或者接触不好导致没有读出在CP1测试的不良品中做的标记。而如果在CP1和CP2测试项不同,极可能导致XA的情况出现。曾经遇到过一种情况,因为测试机中一颗钉子凸出,导致CP2测试中的电子位图被整体移动了。如果不是因为查出这个问题,有问题的电子位图流通到市场上,那么部分的不良品芯片将会被当做良品芯片使用,会造成莫大损失。如果测试程序出现了错误,但是没有将该错误写入标记,也可能会导致出现XA的情况,因此,是否出现XA的情况,也可被用来验证测试程序的可靠性。因为第二道晶圆测试CP2相当于是第一道晶圆测试CP1的补测,所以不允许出现第一道晶圆测试CP1产生的第一电子位图和第二道晶圆测试CP2产生的第二电子位图的格式完全相同的情况,即,不允许出现叠加测试结果中只有AA和XX有值,而AX为0的情况。如果发生了第一电子位图和第二电子位图的格式完全相同的情况,则说明第二道晶圆测试CP2可能出现错误,或者第二道晶圆测试CP2没有测试的情况,也需要重新调查,此时的第二道晶圆测试CP2为无效测试。

因为第一道晶圆测试CP1产生的第一电子位图和第二道晶圆测试CP2产生的第二电子位图的外形不一定会完全重合,所以在叠加电子位图中可能仅有CP1测试的结果,或者仅有CP2测试的结果,导致叠加测试结果可能会产生error。

不同大小的晶圆对应不同的测试模板,以Flash为例,不同产品,例如2M产品和64M产品,芯片存储的大小不同,那么芯片的大小也是有区别的,即使同样使用10寸的晶圆,芯片在晶圆上的分布、数量和排列都不同,相应地,不同产品的晶圆划分的测试模板自然也不同。同样一个产品,例如2M产品,不同大小的晶圆,在10寸晶圆上和12寸晶圆上的分布、数量和排列也不同,划分的测试模板也不同。这就会产生不同的测试模板,晶圆测试厂可能会有用错测试模板的风险。当叠加电子位图中晶圆的相同位置只出现了芯片的单次测试的结果时,说明发生了坐标偏移,或者改变了测试模板的范围或者用错了对应的测试模板,这些情况是不允许出现的,需要发出异常状态的警告,提醒人工介入处理异常。

如果在晶圆测试过程中,出现了坐标偏移现象,这些坐标偏移可能是机台测试中运动痕迹异常或者接测异常等情况导致的,坐标偏移会导致叠加电子位图中出现大量的XA或者error,此为异常情况,需要重新调查。

本发明可以在晶圆测试过程中及时发现并阻止电子位图坐标偏移现象的发生,消除了测试厂的隐患和风险,提高了晶圆测试后的产品良率,大大降低了封装厂挑错芯片的可能性,减少了晶圆损失,减小了晶圆流入市场的风险,提高了量产的合格率。本发明适用于晶圆测试中生成的任何电子位图,且适用于对任何芯片的晶圆测试。

尽管本发明的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本发明的限制。在本领域技术人员阅读了上述内容后,对于本发明的多种修改和替代都将是显而易见的。因此,本发明的保护范围应由所附的权利要求来限定。

- 在晶圆测试过程中检测电子位图中坐标偏移的方法

- 晶圆的测试方法、晶圆测试机、电子装置和存储介质