用于字符串处理的字节比较方法以及指令处理装置

文献发布时间:2023-06-19 10:32:14

技术领域

本公开涉及处理器技术领域,更具体地,涉及用于字符串处理的字节比较方法以及指令处理装置。

背景技术

目前,处理器的主流架构包括X86架构、ARM架构和MIPS架构。随着精简指令集RISC的发展,期望进一步开发基于第五代精简指令集RISC-V的新型处理器架构。RISC-V是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),不仅具有完全开源、架构简单、模块化设计的优点,而且该架构的定义使得硬件实现简单,从而可以减少处理器芯片的开发周期和成本。此外,RISC-V架构可以支持32位元或者64位元的寄存器宽度,从而可以兼顾多种应用场景的性能需求。

随着处理器应用于人工智能(AI)应用领域,处理器的自然语言处理能力越来越重要。为了将自然语言的文本内容分析成处理器可以理解的含义,处理器对文本内容进行语法分析和分词,其中涉及处理器中实现字符串比较指令的功能。如果在处理器架构中采用扩展指令集,例如字节比较指令,则可以显著提高处理器的文字处理能力,从而在提高文本检索和自然语言处理的处理效率和速度方面有优势。

在现有的ARM架构和MIPS架构中,在字符串比较操作中判断字符串结尾和是否相等的汇编指令序列包括多条标准指令(例如,在ARM架构中的mov/sub/orr/bic指令)。现有的处理器架构并未提供适于字符串处理的高性能的专用指令,而是执行标准指令。由于执行的指令数量多,因此字符串处理速度达不到自然语言处理的性能需求。

诸如RISC-V架构的精简指令集则需要增强字符串处理能力,才能符合AI应用领域对字符串处理能力的需求。然而,处理器的指令集是内嵌的微代码,需要占用宝贵的系统资源。而且,如果指令集采用复杂的代码设计方式,反而会造成处理器的性能劣化。因此,将实现何种功能的字符串处理指令嵌入处理器中作为扩展指令是处理器的指令系统设计的难点之一。

发明内容

有鉴于此,本公开实施例提供适于执行字节比较指令的指令处理装置,从而采用字节比较指令以提升处理器字符串的处理能力。

根据本公开的第一方面,提供一种指令处理装置,包括:第一寄存器,适于指示源字符串,所述源字符串包括至少一个字节;

译码单元,适于接收字节比较指令并进行译码,所述字节比较指令至少指示所述第一寄存器;

以及

执行单元,耦接到所述第一寄存器和所述译码单元,并执行所述译码后的字节比较指令,以便获取所述源字符串;将所述源字符串中的至少一个字节逐个地与结尾标识符进行比较;以及根据所述比较的结果获得与所述源字符串相对应的结果值。

根据本公开的第二方面,提供一种用于字符串处理的字节比较方法,包括:获取源字符串;将所述源字符串逐个字节地与结尾标识符进行比较;以及根据所述比较结果获得与所述源字符串相对应的结果值。

根据本公开的第三方面,提供一种字符串比较方法,包括:按照寄存器位宽加载所述第一字符串和第二字符串彼此相对应的内容;执行字节比较指令,将所述第一字符串的内容作为所述源字符串,产生相对应的第一结果值,根据所述第一结果值判断所述第一字符串的内容是否包含结尾标识符;以及在所述第一字符串的内容未包含结尾标识符的情形下,对所述第一字符串的内容和所述第二字符串的内容进行大小比较。

根据本公开的第四方面,提供一种计算机系统,包括:存储器;以及处理器,耦接到所述存储器,并包括:第一寄存器,适于指示源字符串,所述源字符串包括至少一个字节;译码单元,适于接收字节比较指令并进行译码,所述字节比较指令至少指示所述第一寄存器;以及执行单元,耦接到所述第一寄存器和所述译码单元,并执行所述译码后的字节比较指令,以便获取所述源字符串;将所述源字符串中的至少一个字节逐个地与结尾标识符进行比较;以及根据所述比较的结果获得与所述源字符串相对应的结果值。

根据本公开的第五方面,提供一种片上系统,包括上述的指令处理装置。

根据本公开实施例的指令执行装置,适于执行字节比较指令,其中,根据源字符串的内容产生结果值用于快速定位结尾标识符的位置,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

根据本公开实施例的指令执行装置,采用上述的字节比较指令判断第一字符串的内容中是否存在结尾标识符,在连续的字节比较操作中无需多条指令组合实现判断包含结尾标识符的功能,因而可以减少实现该功能所需指令的数量,提高字符串比较操作的性能。

在优选的实施例中,该指令执行装置在执行字节比较指令、异或指令和或指令三条指令之后才进行第一字符串的内容和第二字符串的内容的大小比较,因而可以进一步减少实现该功能所需的减法运算的数量,进一步提高字符串比较操作的性能。

附图说明

通过参考以下附图对本公开实施例的描述,本公开的上述以及其它目的、特征和优点将更为清楚,在附图中:

图1示出根据本公开一个实施例的处理器的示意性框图;

图2示出根据本公开一个实施例的指令处理装置的示意性框图;

图3示出根据本公开一个实施例的指令处理装置的示意性框图;

图4示出根据本公开一个实施例的字节比较方法的流程图;

图5示出根据本公开一个实施例的字符串比较方法的流程图;以及

图6示出根据本公开一个实施例的检索系统的框图。

图7示出根据本公开一个实施例的计算机系统的结构示意图;以及

图8示出根据本公开一个实施例的片上系统的结构示意图。

具体实施方式

以下基于实施例对本公开进行描述,但是本公开并不仅仅限于这些实施例。在下文对本公开的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本公开。为了避免混淆本公开的实质,公知的方法、过程、流程没有详细叙述。另外附图不一定是按比例绘制的。

在本文中使用以下术语。

指令集,在处理器内嵌的用来计算和控制处理器系统的全部指令的集合。在设计时,处理器就已经嵌入与硬件电路相配合的指令集。程序员采用各种语言编写的程序要翻译(编译或解释)成以指令形式表示的机器语言之后,才能在处理器上运行。因此,指令集反映处理器的基本功能,关系到处理器的性能发挥,构成处理器性能的重要标志。处理器可以根据其内嵌的指令集分成不同的类型,例如X86架构的处理器、ARM架构的处理器、MIPS架构的处理器。

程序计数器:简称PC,用于存放下一条指令的指令地址的寄存器。处理器根据程序计数器的指令地址从内存或高速缓存中获取和执行指令。

图1示出根据本公开一个实施例的处理器的示意性框图。

处理器100包括用于处理指令的一个或多个处理器核110。应用程序和/或系统平台可以控制多个处理器核110处理和执行指令。

每个处理器核110可以用于处理特定的指令集。在一些实施例中,指令集可以支持复杂指令集计算(Complex Instruction Set Computing,CISC)、精简指令集计算(ReducedInstruction Set Computing,RISC)或基于超长指令字(Very Long Instruction Word,VLIW)的计算。不同的处理器核110可以各自处理不同或相同的指令集。在一些实施例中,处理器核110还可以包括其他处理模块,例如数字信号处理器(Digital Signal Processor,DSP)等。

处理器100还可以包括多级存储结构,例如,寄存器堆116、多级高速缓存L1至L3、以及经由存储总线访问的存储器110。

寄存器堆116可以包括用于存储不同类型的数据和/或指令的多个寄存器,这些寄存器可以是不同类型的。例如,寄存器堆116可以包括:整数寄存器、浮点寄存器、状态寄存器、指令寄存器和指针寄存器等。寄存器堆116中的寄存器可以选用通用寄存器来实现,也可以根据处理器100的实际需求采用特定的设计。

高速缓存L1至L3可以全部或部分集成于各个处理器核110中。例如,第一级高速缓存L1位于各个处理器核110的内部,包括用于存放指令的指令高速缓存118和用于存放数据的数据高速缓存119。根据不同架构,至少一级高速缓存(例如,图1所示的第三级高速缓存L3)可以位于多个处理器核110的外部并且由多个处理器核共享。处理器100还可以包括外部高速缓存。

处理器100可以包括内存管理单元(Memory Management Unit,MMU)112,用于实现虚拟地址到物理地址的转译。内存管理单元112中高速缓存有了一部分虚拟地址到物理地址的映射关系,内存管理单元112也可以从内存中获取未被高速缓存的映射关系。每个处理器核110中可以设置一个或多个内存管理单元112,不同处理器核110中的内存管理单元110也可以与位于其他处理器或处理器核中的内存管理单元110实现同步,使得每个处理器或处理器核可以共享统一的虚拟存储系统。

处理器100用于执行指令序列(即应用程序)。处理器100执行每个指令的过程包括:从存放指令的存储器中取出指令、对取出的指令进行译码、执行译码后的指令、保存指令执行结果等步骤,如此循环,直到执行完指令序列中的全部指令或遇到停机指令。

为了实现上述过程,处理器100可以包含取指令单元114、译码单元115、指令发射单元(未示出)、执行单元111和指令退休单元(未示出)等。

取指令单元114作为处理器100的启动引擎,用于将指令从指令高速缓存118或存储器110中迁移至指令寄存器(例如,寄存器堆116中的一个用于存放指令的寄存器)中,并接收下一个取指地址或根据取指算法计算获得下一个取指地址,取指算法例如包括:根据指令长度递增地址或递减地址。

取出指令后,处理器100进入指令译码阶段,译码单元115按照预定的指令格式,对取回的指令进行解释和译码,识别并区分出不同的指令类别以及操作数获取信息(操作数获取信息可以指向立即数或用于存储操作数的寄存器),为执行单元111的操作做准备。

指令发射单元通常存在于高性能的处理器100中,位于译码单元115与执行单元111之间,用于指令的调度和控制,以将各个指令高效地分配至不同的执行单元111,使得多个指令的并行操作成为可能。指令经取指、译码并被调度到相应的执行单元111之后,相应的执行单元111开始执行该指令,即执行该指令所指示的操作、实现相应的功能。

指令退休单元主要用于负责将执行单元111产生的执行结果写回到相应的存储位置(例如为处理器100内部的寄存器)中,以使后续指令能够从该存储位置处快速获取相应的执行结果。

对于不同类别的指令,可以在处理器100中相应地设置不同的执行单元111。执行单元111可以是运算单元(例如包含算术逻辑单元、矢量运算单元等,用于根据操作数进行运算并输出运算结果)、内存执行单元(例如用于根据指令访问内存以读取内存中的数据或向内存写入指定的数据等)以及协处理器等。在处理器100中,各个执行单元111可以并行运行并输出相应的执行结果。

在该实施例中,处理器100是多核处理器,包括共用第三级缓存L3的多个处理器核110。在替代的实施例中,处理器100可以是单核处理器,或者电子系统中用于处理指令的逻辑元件。本公开不限于任何特定类型的处理器。

根据该实施例的处理器100,不仅包括处理器的指令集架构的标准指令,而且包括下文描述的字节比较指令tstnbz,作为字符串处理的扩展指令。在执行字节比较指令tstnbz时,根据源字符串的内容产生结果值用于快速定位结尾标识符的位置,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

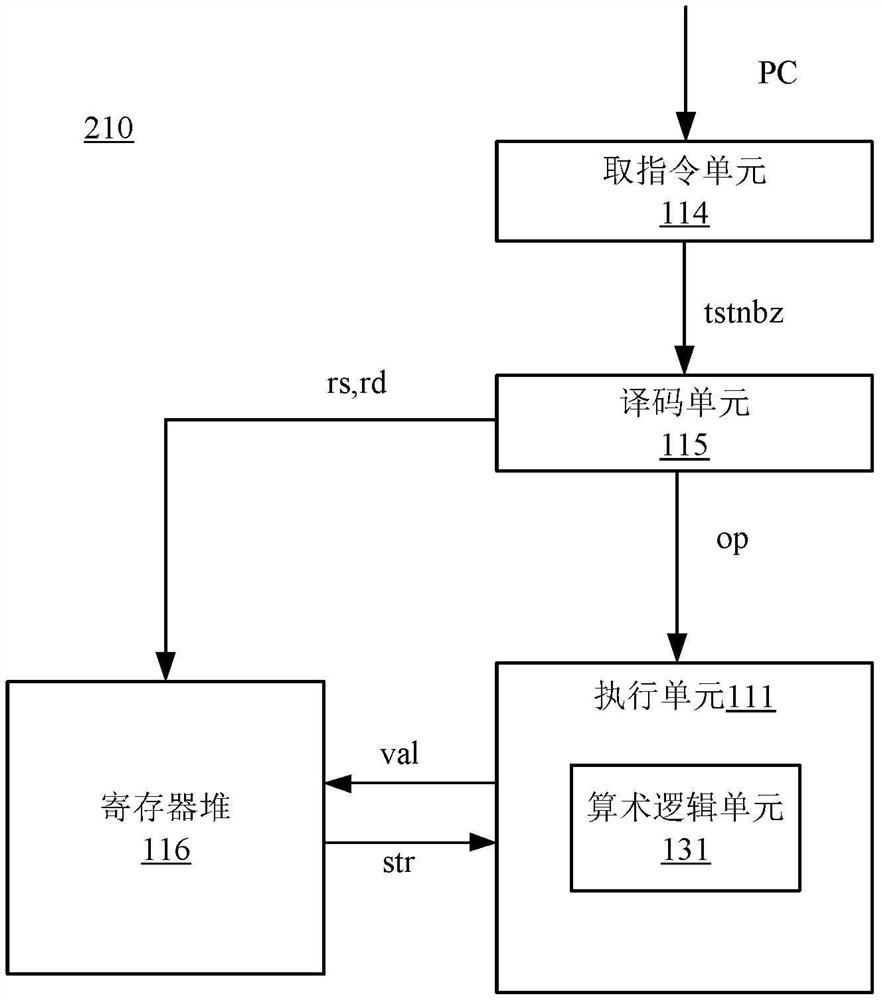

图2示出根据本公开一个实施例的指令处理装置的示意性框图。为了清楚起见,在图2中仅示出了指令处理装置210与字节比较指令相关的单元。

指令处理装置210包括但不限于理器、多核处理器的处理器核、或者电子系统中的处理元件。在该实施例中,指令处理装置210例如是图1所示的处理器100的处理器核,并且与图1相同的单元或模块采用与图1相同的附图标记。

指令处理装置210例如基于精简指令集RISC架构,不仅包括精简指令集RISC的标准指令,而且包括作为扩展指令的字节比较指令tstnbz,以提高处理器的字符串处理性能。

在指令处理装置210上运行应用程序时,应用程序已经编译成包括多条指令的指令序列。程序计数器PC用于保存将要执行的指令的指令地址。取指令单元114根据程序计数器PC的数值,从第一级高速缓存L1中的指令高速缓存118或指令处理装置210外部的存储器210中获取指令。

在该实施例中,取指令单元114从指令高速缓存118中获取字节比较指令tstnbz,具有如下的形式:

tstnbz rd rs

字节比较指令tstnbz包括指定了第一寄存器rs的第一操作数、指定了第二寄存器rd的第二操作数。第一操作数例如是源字符串str的内容或地址信息,第二操作数例如是结果值val的内容或地址信息。

译码单元115对指令进行译码,以确定指令的操作码op、以及寄存器堆116中与第一操作数对应的第一寄存器rs、以及与第二操作数对应的第二寄存器rd。

执行单元111例如包括算术逻辑单元131,根据操作码op执行相应的操作。

下文以64位位宽的寄存器为例进行描述,第一寄存器rs和第二寄存器rd均为64位的寄存器。然而,本公开不受限于寄存器的位宽和类型,所有能在其中存储数值或地址信息的寄存器都在本公开的保护范围之内,包括但不限于8位、16位、32位、64位、128位、512位位宽的寄存器。

进一步地,下文以直接存储内容的寄存器为例进行描述,第一寄存器rs和第二寄存器rd分别保存源字符串str和结果值val的内容。在执行单元111中的算术逻辑单元131根据操作码op执行字节比较指令时,从第一寄存器rs获取源字符串str的内容,以及将结果值保存在第二寄存器rd中。

在替代的实施例中,第一寄存器rs和第二寄存器rd例如分别保存源字符串str和结果值val的地址信息。在执行单元111中的算术逻辑单元131根据操作码op执行字节比较指令时,执行单元111根据第一寄存器rs中保存的源字符串的地址信息访问存储器以获得源字符串str的内容,将源字符串str逐个字节与结尾符相比较以获得结果值,以及将结果值保存在第二寄存器rd的地址信息相对应的存储器位置。

另外,考虑到字节比较指令在执行时需要指令流水线的多拍处理第一寄存器中的多个字节的源字符串,会导致在指令流水线的处理开销,因此,根据本发明的一种实施方式,指令处理装置210还可以包括硬件寄存器,在硬件寄存器中设置指令使能标识,用于控制是否允许执行字节比较指令的使能标识。执行单元111根据该使能标识的值来确定是否执行字节比较指令tstnbz。当指示使能标识指示不允许执行字节比较指令tstnbz(例如将使能标识设置为0),则执行单元140不执行该指令,并且可选地产生异常信息。

以下结合图4详细描述字节比较指令tstnbz的执行过程。

在步骤S01中,将源字符串str的一个寄存器位宽内容从存储器加载至通用寄存器。例如,在64位的寄存器位宽的处理器中,加载源字符串str的64位数据,从最高位字节开始至最低位字节结束,共计加载了8个字节的数据。

在步骤S02中,将源字符串的1个字节内容与结尾标识符进行比较。例如,如果结尾标识符为00H(十六进数字表示的字节数值),则比较步骤例如包括将源字符串的1个字节内容与00H进行比较。

在步骤S03中,根据比较结果判断是否为结尾标识符。例如,如果结尾标识符为00H,则判断步骤包括在源字符串的1个字节内容等于00H时判断为结尾标识符,在源字符串的1个字节内容不等于00H时决定为普通字符。

在步骤S04和S05中,根据判断结果设置结果值的相应字节的数值。如果源字符串的字节为结尾标识符,则将结果值的相应字节的所有位均置1。如果源字符串的字节为普通字符,则将结果值的相应字节的所有位置0。

在步骤S06中,读取源字符串的下一个字节内容,例如,从最高位字节开始至最低位字节结束的顺序读取下一个字节内容。然后,返回至步骤S01以判断源字符串的下一个字节是否为结尾标识符。

在源字符串加载到通用寄存器中的全部字节内容均进行比较,并且产生相应的结果值之后,则结束上述步骤S01-S06,产生比较结果。该结果值为源字符串的定位标记,与源字符串的字节长度相同,并且在结尾符相应的字节所有位均置1,在普通字符相应的字节所有位置0。该结果值非零则表示存在所述结尾标识符,按照字节宽度移位从非零至零的移位次数表示所述字符结尾符的字节位置。

在上述的实施例,描述了采用循环的方式遍历源字符串加载至通用寄存器的全部字节内容,从而在未能获得处理器的通用寄存器位宽的情形下也能完成全部字节内容的判断。

如果已知处理器的通用寄存器位宽,则上述字节比较指令可以进一步简化,其中从最高位字节开始中至最低位字节结束,执行预定数量的比较指令即可遍历源字符串加载至通用寄存器的全部字节内容。

在优选的实施例中,以64位寄存器位宽的处理器为例,上述字节比较指令tstnbz的汇编代码如下:

tstnbz rd,rs

Rd[63:56]=(rs[63:56]!=0)?8’h0:8’hff

Rd[55:48]=(rs[55:48]!=0)?8’h0:8’hff

Rd[47:40]=(rs[47:40]!=0)?8’h0:8’hff

Rd[39:32]=(rs[39:32]!=0)?8’h0:8’hff

Rd[31:24]=(rs[31:24]!=0)?8’h0:8’hff

Rd[23:16]=(rs[23:16]!=0)?8’h0:8’hff

Rd[15:8]=(rs[15:8]!=0)?8’h0:8’hff

Rd[7:0]=(rs[7:0]!=0)?8’h0:8’hff

在该汇编代码中,字节比较指令tstnbz判断通用寄存器中的源字符串str是否包含结尾标识符,以及在通用寄存器保存结果值val。源字符串str和结果值val分别为64位,共计8个字节。该字节比较指令tstnbz的流程包括从最高位字节开始至最低位字节结束,逐个字节测试源字符串str选定字节的所有位是否全部为0。如果源字符串str选定字节的所有位全部为0,则结果值中rd相应字节的所有位均置1。如果源字符串str选定字节的至少1位不为0,则结果值中rd相应字节的所有位置0。

根据该实施例的tstnbz指令按字节为单位将源字符串str与结尾标识符比较,并且按字节为单位回写结果值。该结果值为源字符串的定位标记,与源字符串的字节长度相同,并且在结尾符相应的字节所有位均置1,在普通字符相应的字节所有位置0。该结果值用于快速定位结尾符的位置。根据结果值是否非零,可以进一步采用减法指令比较源字符串与另一个字符串的大小,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

可以理解,该汇编代码形式的字节比较指令tstnbz兼容所有的寄存器位宽,例如,兼容的寄存器位宽包括但不限于8位、16位、32位、64位、128位、512位位宽。

在上述的实施例中,描述了结尾标识符为00H的实施例。在替代的实施例中,结尾标识符可以为符合系统规范的任意数值,例如0FFH。

在上述的实施例中,描述了结果值在对应于结尾标识符的相应字节所有位均置1的实施例。

在替代的实施例中,在结果值与结尾标识符相应的字节和与普通字符相应的字节分别设置不同的数值,而不限于特定的数值。例如,将结果值与结尾标识符相应的字节设置0FFH、01H、080H中的任意一个,将结果值与普通字符相应的字节设置为00H、010H中的任意一个。

在上述的实施例中,在基于精简指令集RISC架构的处理器中实现了字节比较指令tstnbz,然而,本公开不限于此。根据字节比较指令tstnbz的汇编代码可以理解,在复杂指令集(CISC)架构、精简指令集(RISC)架构、超长指令字(VLIW)架构的处理器均可以实现该字节比较指令tstnbz,以实现结尾标识符的快速定位,从而提升处理器的字符串处理能力。

图3示出根据本公开一个实施例的指令处理装置的示意性框图。为了清楚起见,在图3中仅示出了指令处理装置310与字节比较指令相关的单元。

指令处理装置310包括但不限于理器、多核处理器的处理器核、或者电子系统中的处理元件。在该实施例中,指令处理装置310例如是图1所示的处理器100的处理器核,并且与图1相同的单元或模块采用与图1相同的附图标记。

指令处理装置210例如基于精简指令集RISC架构,不仅包括精简指令集RISC的标准指令,而且包括作为扩展指令的字节比较指令tstnbz,以提高处理器的字符串处理性能。

在指令处理装置310上运行应用程序时,应用程序已经编译成包括多条指令的指令序列。程序计数器PC用于保存将要执行的指令的指令地址。取指令单元114根据程序计数器PC的数值,从第一级高速缓存L1中的指令高速缓存118或指令处理装置310外部的存储器310中获取指令。

在该实施例中,取指令单元114从指令高速缓存118中获取字节比较指令tstnbz,具有如下的形式:

tstnbz rs

字节比较指令tstnbz包括指定了第一寄存器rs的第一操作数。第一操作数例如是源字符串str的内容或地址信息。

译码单元115对指令进行译码,以确定指令的操作码op、以及寄存器堆116中与第一操作数对应的第一寄存器rs。

执行单元111例如包括算术逻辑单元131,根据操作码op执行相应的操作。

下文以直接存储内容的寄存器为例进行描述,第一寄存器rs保存源字符串str和结果值val的内容。在执行单元111中的算术逻辑单元131根据操作码op执行字节比较指令时,从第一寄存器rs获取源字符串str的内容,以及根据结果值设置标志寄存器ZF。

在替代的实施例中,第一寄存器rs例如保存源字符串str的地址信息。在执行单元111中的算术逻辑单元131根据操作码op执行字节比较指令时,执行单元111根据第一寄存器rs中保存的源字符串的地址信息访问存储器以获得源字符串str的内容,将源字符串str逐个字节与结尾符相比较以获得结果值,以及根据结果值设置标志寄存器ZF。

另外,考虑到字节比较指令在执行时需要指令流水线的多拍处理第一寄存器中的多个字节的源字符串,会导致在指令流水线的处理开销,因此,根据本发明的一种实施方式,指令处理装置310还可以包括硬件寄存器,在硬件寄存器中设置指令使能标识,用于控制是否允许执行字节比较指令的使能标识。执行单元111根据该使能标识的值来确定是否执行字节比较指令tstnbz。当指示使能标识指示不允许执行字节比较指令tstnbz(例如将使能标识设置为0),则执行单元140不执行该指令,并且可选地产生异常信息。

以下详细描述字节比较指令tstnbz的执行过程。

上述字节比较指令tstnbz的汇编代码如下:

tstnbz rs

clr zf

Rd[63:56]=(rs[63:56]==0)?stc zf

Rd[55:48]=(rs[55:48]==0)?stc zf

Rd[47:40]=(rs[47:40]==0)?stc zf

Rd[39:32]=(rs[39:32]==0)?stc zf

Rd[31:24]=(rs[31:24]==0)?stc zf

Rd[23:16]=(rs[23:16]==0)?stc zf

Rd[15:8]=(rs[15:8]==0)?stc zf

Rd[7:0]=(rs[7:0]==0)?stc zf

在该汇编代码中,字节比较指令tstnbz判断通用寄存器中的源字符串str是否包含结尾标识符,以及根据判断结果设置标志寄存器ZF的标志位。源字符串str为64位,共计8个字节。该字节比较指令tstnbz的流程包括将标志寄存器ZF置0之后,从最高位字节开始至最低位字节结束,逐个字节测试源字符串str选定字节的所有位是否全部为0。如果源字符串str选定字节的所有位全部为0,则将标志寄存器ZF置1。如果源字符串str选定字节的至少1位不为0,则继续判断下一字节。

根据该实施例的tstnbz指令按字节为单位将源字符串str与结尾标识符比较,并且根据结果值设置标志寄存器ZF。如果标志寄存器ZF为0则表示源字符串str未包含结尾标识符,如果标志寄存器ZF为1则表示源字符串str包含结尾标识符。因此,根据标志寄存器ZF的标志位是否非零,可以进一步采用跳转指令执行减法指令以比较源字符串与另一个字符串的大小,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

图5示出根据本公开实施的字符串比较方法的流程图。在该实施例中的指令处理装置例如是基于精简指令集RISC架构的处理器核,不仅包括精简指令集RISC的标准指令,而且包括扩展的字节比较指令tstnbz,以提高处理器的字符串处理性能。

字符串比较函数:string compare(str1,str2)的缩写,用于比较两个源字符串str和str2并根据比较结果返回整数。若str1=str2,则返回零;若str1

在步骤S11中,将源字符串str和str2的各自一个寄存器位宽内容分别从存储器加载至第一通用寄存器和第二通用寄存器。例如,在64位的寄存器位宽的处理器中,加载源字符串str和str2的64位数据,从最高位字节开始至最低位字节结束,各自共计加载了8个字节的数据。

在步骤S12中,采用上述的字节比较指令tstnbz获得结果值val。该结果值的数值表示源字符串是否包含字符串的结尾。如上所述,该实施例的字节比较指令tstnbz按字节为单位将结果值回写至寄存器中。

因此,可以更便捷地知道哪个字节为0,进而快速定位出结尾符的位置。

在步骤S13中,通过异或指令xor,判断第一通用寄存器和第二通用寄存器的内容是否相等。如果内容相等并且未包含字符串结尾,则跳转到步骤S14。如果内容不相等或者包含字符串结尾,则跳转至步骤S15。

在步骤S14中,存储地址增加(地址增加值由寄存器位宽决定),然后,返回步骤S11,取源字符串str、str2的各自下一个寄存器位宽的内容分别加载至第一通用寄存器和第二通用寄存器。

在步骤S15中,通过减法指令sub,判断第一通用寄存器和第二通用寄存器中数据的的大小关系,结束运算,返回相应结果。

在优选的实施例中,以64位寄存器位宽的处理器为例,字符串比较函数strcmp的汇编代码如下:

<.Lloop>

<.Lmismatch>

根据字符串比较函数strcmp的汇编代码可以理解,上述步骤S12至S14仅需要三条指令即可完成,依次为:字节比较指令tstnb、异或指令xor和或指令or。

字节比较指令tstnb的功能是,通过判断第一通用寄存器中的每一个字节是否等于0H,来判断该第一通用寄存器是否包含字符串的结尾。具体操作为:如果某个字节等于0H,则结果值t0对应的字节写0FFH,反之,则结果值t0对应的字节写0H。

异或指令xor的功能是,通过异或运算来判断第一通用寄存器和第二通用寄存器的内容是否相等。具体操作为:如果第一通用寄存器和第二通用寄存器中的内容相等,则结果值t1的数值为0H,反之,则结果值t1的数值为0FFH。

或指令or的功能是,如果存在结尾标识符(结果值t0的数值非零),或者两个源字符串的一个寄存器位宽内容不相等(结果值t1的数值非零),则进一步通过减法操作,判断第一通用寄存器和第二通用寄存器中数据的大小关系。

在该实施例的字符比较方法中,字符比较函数strcmp采用处理器架构中扩展的字节比较指令tstnbz,在连续的字节比较操作中无需多条指令组合实现判断包含结尾标识符的功能,因而可以减少实现该功能所需指令的数量,提高字符串比较操作的性能。

图6示出根据本公开一个实施例的检索系统的框图。该检索系统包括检索引擎201、网络202、分词处理器211和词典存储模块212。

检索引擎201可以是任意的终端,例如个人计算机、手机、平板、智能家电。该智能家电例如是嵌入片上系统的智能音箱、电视、冰箱、洗衣机等。检索引擎201包括处理器,用于将用户经由键盘、鼠标、遥控器、触摸屏、麦克风等交互设备输入的语音内容或文字内容转换成自然语言形式的文本。例如,智能音箱上的检索引擎201将用户的语音转换成文本,产生自然语言形式的文本内容,例如,“北京今天的天气怎么样?”,该检索引擎201将文本内容处理成检索请求发送至网络202,以获取与查询要素(例如,时间、地点、查询内容)相关的检索结果。

分词处理器211和词典存储模块212例如分别是图1所示的计算机系统100的处理器和存储器。该分词处理器211不仅包括精简指令集RISC的标准指令,而且包括扩展的字节比较指令tstnbz,以提高处理器的字符串处理性能。

在该实施例中,检索引擎201和分词处理器211分别是不同的硬件设备。在替代的实施例中,如果检索引擎201的处理器包括字节比较指令tstnbz,则检索引擎201的处理器可以兼有分词处理器211的功能,因而可以省去独立的分词处理器211。

以下以智能音箱作为检索引擎201的实施例,以中文语言为例进一步说明图6所示检索系统的工作原理。

检索引擎201将用户经由麦克风输入的语音内容处理成自然语言形式的文本内容,例如,“北京今天的天气怎么样?”。在自然语言处理技术中,上述中文的文本内容是无词边界标记的语言文本。计算机系统难以根据自然语言形式的文本内容中理解查询要素以建立检索式,因而难以获得期望的检索结果。

进一步地,为了将自然语言处理成是查询要素,检索引擎201将文本内容发送至分词处理器211中。词典存储模块212中预先存储多个词条,形成分词词典。分词处理器211按照分词算法,对文本内容进行分词处理。

基于词典的分词算法,本质上就是字符串匹配。将待匹配的字符串基于一定的算法策略,和一个足够大的词典进行字符串匹配,如果匹配命中,则可以分词。根据不同的匹配策略,又分为正向最大匹配法,逆向最大匹配法,双向匹配分词,全切分路径选择等。比如在最大匹配方法中,若在词典中找到能够匹配该输入文本的最长的词条,则识别出一个词,将识别出的词作为一个切分单元。依次类推,从而将给定文本分词为由切分单元组成的切分单元序列(当然,切分单元不仅包含匹配成功的词,也可能包含单字或者动态识别出来的词)。

该检索系统中的分词处理器211将检索引擎201提供的文本内容,“北京今天的天气怎么样?”,经过分词处理产生多个词条,“北京”、“今天”、“天气”、“怎么样”,从而产生多个查询要素(例如,时间、地点、查询内容)。检索引擎201从分词处理器211获得查询要素,从而可以构建检索式:“北京”AND“今天”AND“天气”,生成检索请求,将该检索请求发送至网络202以获得检索结构。

在本实施例的自然语言处理中,分词处理器211执行大量的字符串比较操作,即将文本内容与分词词典的词典进行比较,在文本内容的部分内容与分词词典的词条一致时获得命中的词条,作为分词结果,从而产生计算机可以理解的查询要素。在本实施例中,分词处理器211不仅包括精简指令集RISC的标准指令,而且包括扩展的字节比较指令tstnbz,从而可以提高处理器的字符串处理性能,因而可以大幅提升自然语言处理的速度。

图7示出根据本公开一个实施例的计算机系统的结构示意图。

计算机系统1000是“中心”系统架构的示例。计算机系统1000可基于目前市场上各种型号的处理器构建,并由WINDOWS

如图7所示,计算机系统1000包括处理器1002。处理器1002具有本领域所公知的数据处理能力。它可以是复杂指令集(CISC)架构、精简指令集(RISC)架构、超长指令字(VLIW)架构的处理器、或者是实现上述指令集组合的处理器、或者是任何为了专用目标构建的处理器设备。

处理器1002耦接到系统总线1001,系统总线1001可以在处理器1002和其它单元之间传输数据信号。

计算机系统1000还包括存储器1004和显卡1005。存储器1004可以是动态随机存取存储器(DRAM)设备、静态随机存取存储器(SRAM)设备、闪速存储器设备或其它存储器设备。存储器1004可以存储由数据信号表示的指令信息和/或数据信息。显卡1005包括显示驱动器,用于控制显示信号在显示屏上的正确显示。

经由存储器控制器1003,显卡1005和存储器1004被耦接到系统总线1001上。处理器1002可以经由系统总线1001与存储器控制器1003通信。存储器控制器1003向存储器1004提供高带宽存储器访问路径421,用于指令信息和数据信息的存储和读取。同时,存储器控制器1003和显卡1005基于显卡信号输入输出接口420进行显示信号的传输。显卡信号输入输出接口420例如为DVI、HDMI等接口类型。

存储器控制器1003不仅在处理器1002、存储器1003和显卡1005之间传输数字信号,而且,实现了在系统总线1001和存储器1004以及输入/输出控制器1006桥接数字信号。

计算机系统1000还包括输入/输出控制器1006,通过专用集线器接口总线422耦接到存储器控制器1003,并经由局部I/0总线将一些I/0设备到输入/输出控制器1006上。局部I/0总线用于将外围设备耦接到输入/输出控制器1006,进而耦接到存储器控制器1003和系统总线1001上。外围设备包括但不限于以下设备:硬盘1007、光盘驱动器1008、声卡1009、串行扩展端口1010、音频控制器1011、键盘1012、鼠标1013、GPIO接口1014、闪存1015和网卡1016。

当然,不同的计算机系统根据主板,操作系统和指令集架构的不同,其结构图也有所变化。例如目前很多计算机系统将存储器控制器1003集成到处理器1002的内部,这样输入/输出控制器1006会成为和处理器1002耦接的控制中心。

根据该实施例的计算机系统1000,处理器1002不仅包括的指令集架构的标准指令,而且包括上文描述的字节比较指令tstnbz,作为字符串处理的扩展指令。在执行字节比较指令tstnbz时,根据源字符串的内容产生结果值用于快速定位结尾标识符的位置,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

图8示出根据本公开一个实施例的片上系统的结构示意图。

片上系统2000是单芯片集成的完整系统,可以作为一个独立器件生产和销售,也可以和其他组件结合,形成新的器件进行生产和销售。

片上系统2000可以使用目前市场上多种型号的处理器来制造,并可由WINDOWS

如图8所示,片上系统2000包括经由AHB(Advanced High performance Bus,系统总线)总线2001耦接的处理器2002、静态随机存取存储器2005、LCD控制器2004和闪存2006以及AHB/APB桥2007。

处理器2002可以为复杂指令集(CISC)微处理器、精简指令集(RISC)微处理器、超长指令字(VLIW)微处理器、实现上述指令集组合的微处理器、或任何其它处理器设备中的一种。处理器2002还包括根据本公开实施例提供的技术方案进行改进的处理器核20021,其具体细节将在下文提供。

静态随机存取存储器2005和闪存2006用于存储由数字信号表示的指令信息和/或数据信息。例如,静态随机存取存储器2005可以作为各种应用程序的运行空间,为各种应用程序创建堆、栈、存储中间数据等,闪存2006可以存储各种应用程序的可执行代码和操作系统的可执行代码。

AHB总线2001用于在片上系统2000的高性能模块之间传输数字信号,例如在处理器2002和静态随机存取存储器2005、处理器2002和LCD控制器2004、处理器2002和闪存2006、处理器2002和AHB/APB桥2007之间传输数字信号。

AHB/APB桥2007用于在AHB总线和APB总线之间进行数据传输的桥接,通过锁存来自AHB总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

片上系统2000还可以包括与APB总线耦接的各种接口。各种接口包括但不限于通过以下接口类型:高容量SD存储卡(SDHC,Secure Digital High Capacity)、I2C总线、串行外设接口(SPI,Serial Peripheral Interface)、通用异步收发传输器(UART,UniversalAsynchronous Receiver/Transmitter)、通用串行总线(USB,Universal Serial Bus)、通用型之输入输出(GPIO,General-purpose input/output)和蓝牙UART。与接口耦接的外围设备例如为USB设备、存储卡、报文收发传输器、蓝牙设备等。

值得指出的是,随着SoC设计复杂性的增加以及处理器处理能力的不断提升,总线结构的性能局限导致总线结构也在更新换代,例如ARM公司在上述AHB总线的基础上又推出更高性能的AXI(Advanced eXtensible Interface)总线,因此可以采用AXI总线取代图上的AHB总线2001,而且,本领域的研发人员也可以基于自身的实际需求改进现有总线结构,或者构建新的总线结构。因此,虽然图上示出AHB总线,但是实际上,SoC对于总线的选择可以是多种多样的。

根据该实施例的片上系统2000,不仅包括处理器2002的指令集架构的标准指令,而且包括上文描述的字节比较指令tstnbz,作为字符串处理的扩展指令。在执行字节比较指令tstnbz时,根据源字符串的内容产生结果值用于快速定位结尾标识符的位置,从而可以减少字符串比较所需的指令数量,以减少字符串比较操作的执行时间。

另外,对于图7和图8所示的系统,还应该指出的是,这些系统仅用于示例本公开实施例的一些应用场景,但不作为对本公开实施例的限制。本公开实现的是对现有的处理器或者处理器核的改进,因此理论上可以适用于具有任意处理器架构和指令集架构的系统。

对于本公开,可以在硬件或专用电路、软件、逻辑或其任何组合中实现上述处理单元、处理系统和电子设备。举例来说,可以在硬件中实现一些方面,而可以在可由控制器、微处理器或其它计算设备执行的固件或软件中实现其它方面,尽管本公开并不限于此。虽然可以将本公开的各个方面说明和描述为框图、流程图或使用一些其它的图形表示来说明和描述本公开的各个方面,但是很好理解的是,作为非限制性例子,可以以硬件、软件、回件、专用电路或逻辑、通用硬件或控制器或其它计算设备,或者其某种组合来实现文中所描述的这些块、装置、系统、技术或方法。如果涉及的话,可以在诸如集成电路模块的各种组件中实施本公开的电路设计。

以上所述仅为本公开的优选实施例,并不用于限制本公开,对于本领域技术人员而言,本公开可以有各种改动和变化。凡在本公开的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

- 用于字符串处理的字节比较方法以及指令处理装置

- 用于提高Java处理器取指令带宽的字节码缓冲装置及其使用方法