参考电压缓冲器

文献发布时间:2023-06-19 10:55:46

技术领域

本发明总体上关于参考电压缓冲器(reference voltage buffer),并且更具体地,关于具有更快的稳定时间和较大的满量程的参考电压缓冲器。

背景技术

模数转换器(analog-to-digital converter,ADC)通常具有参考电压缓冲器,以向量化器(quantizer)内的比较器提供多个参考电压。随着先进半导体工艺的发展和时钟信号变得越来越快,参考电压缓冲器遭遇了许多设计上的问题,例如稳定问题、信号质量和工艺-电压-温度(process-voltage-temperature,PVT)变化。具体而言,当量化器内的比较器开始使用参考电压对输入信号采样时,参考电压有可能会突然下降,参考电压缓冲器需要稳定时间(settling time)来使得参考电压回到原来的电平。由于时钟信号的频率和采样率变得更快,因此参考电压缓冲器的稳定时间需要被设计得更短,以提供稳定的参考电压。另外,考虑到由量化器处理的信号的噪声容限,参考电压缓冲器的满量程(full scale)应当优选地被设计为更大,即,最高参考电压和最低参考电压之间的差应当被设计得尽可能大。但是,较大的满量程设计可能会导致参考电压不稳定。此外,如果参考电压缓冲器使用有源器件作为负载来生成参考电压,则参考电压缓冲器可能会遭受PVT问题,参考电压变得不稳定,从而给量化器造成问题。

发明内容

因此,本发明的目的是提供具有更快的稳定时间和较大的满量程的参考电压缓冲器,并且即使由于PVT问题导致参考电压的电平改变时,参考电压缓冲器也可以向量化器提供合适的参考电压,以解决上述问题。

根据本发明的一个实施例,参考电压缓冲器包括用于产生参考电压的参考电压生成器、第一运算放大器、第一晶体管、第一组电阻器、第一负载、第二晶体管、第二组电阻器和第二负载。第一运算放大器被配置为接收参考电压和反馈信号以产生控制信号。第一晶体管被配置为由控制信号控制。第一组电阻器耦接到第一晶体管,其中反馈信号是从第一组电阻器的内部节点产生的。第一负载耦接到第一组电阻器。第二晶体管被配置为由控制信号控制。第二组电阻器耦接到第二晶体管。第二负载耦接到第二组电阻器。另外,参考电压生成器、第一负载和第二负载响应于温度变化具有相同的特性。

根据本发明的另一个实施例,参考电压缓冲器包括参考电压生成器、第一运算放大器、第一晶体管、第一组电阻器、第一负载、第二晶体管、第二组电阻器和第二负载。参考电压生成器被配置为产生参考电压。第一运算放大器被配置为接收参考电压和反馈信号以产生控制信号。第一晶体管被配置为由控制信号控制。第一组电阻器耦接到第一晶体管,其中反馈信号是从第一组电阻器的内部节点产生的。第一负载耦接到第一组电阻器。第二晶体管被配置为由控制信号控制。第二组电阻器耦接到第二晶体管。第二负载耦接到第二组电阻器。另外,第一负载和第二负载均包括有源器件。

本发明的参考电压缓冲器可以以更快的稳定时间为后续电路提供合适的输出参考电压。

在阅读了在各个附图中示出的优选实施例的以下详细描述之后,本发明的这些和其他目的无疑对于本领域技术人员将变得显而易见。

附图说明

在下面的详细描述中,出于解释的目的,阐述了许多具体细节以便提供对所公开的实施例的透彻理解。然而,显而易见的是,可以在没有这些具体细节的情况下实践一个或多个实施例。在其他情况下,示意性地示出了公知的结构和设备,以简化附图。

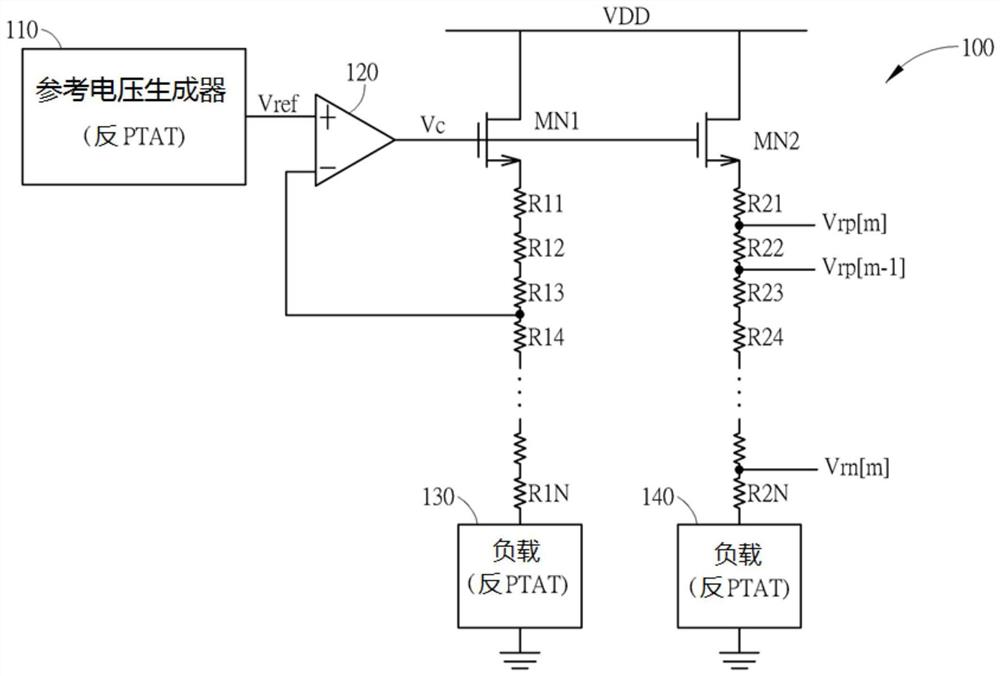

图1是示出根据本发明的一个实施例的参考电压缓冲器的示意图。

图2示出了根据本发明的一个实施例的参考电压缓冲器的详细的示意电路。

图3是示出根据本发明的一个实施例的量化器的示意图。

具体实施方式

图1是示出根据本发明的一个实施例的参考电压缓冲器100的示意图。如图1所示,参考电压缓冲器100包括参考电压生成器110、运算放大器120、第一晶体管MN1、包括电阻器R11~R1N的第一组电阻器、负载130、第二晶体管MN2、包括电阻器R21~R2N的第二组电阻器、以及负载140。运算放大器120具有正输入端、负输入端和输出端,其中正输入端耦接到参考电压生成器110,负输入端耦接到第一组电阻器内的节点(在该实施例中,负输入端耦接到电阻器R13和R14之间的节点,即接收反馈信号),输出端被配置为输出控制信号Vc至第一晶体管MN1和第二晶体管MN2。晶体管MN1通过使用具有漏极、源极和栅极的N型金属氧化物半导体(N-type metal-oxide-semiconductor,NMOS)来实现,其漏极耦接到电源电压VDD,源极耦接到电阻器R11,栅极接收由运算放大器120产生的控制信号Vc。电阻器R11~R1N串联连接,其中,电阻器R11耦接到晶体管MN1的源极,电阻器R1N耦接到负载130。晶体管MN2通过使用具有漏极、源极和栅极的NMOS来实现,其中漏极耦接到电源电压VDD,源极耦接到电阻器R21,栅极接收由运算放大器120产生的控制信号Vc。电阻器R21~R2N串联连接,其中,电阻器R21耦接到晶体管MN2的源极,电阻器R2N耦接到负载140。

在参考电压缓冲器100的操作期间,参考电压生成器110生成参考电压Vref至运算放大器120的正输入端,运算放大器120将参考电压Vref与来自第一组电阻器的信号进行比较,以产生控制信号Vc到晶体管MN1和MN2的栅极。通过使用运算放大器120和晶体管MN1的闭环结构,电阻器R13和R14之间的节点上的电压电平可以被控制为等于参考电压Vref。另外,晶体管MN2、第二组电阻器和负载140分别是晶体管MN1、第一组电阻器和负载130的副本,并且如图1所示的,第二组电阻器被配置为生成多个输出参考电压,例如,Vrp[m]、Vrp[m-1]……Vrn[m]。

在图1所示的参考电压缓冲器100中,由于运算放大器120、晶体管MN1和第一组电阻器形成闭环,晶体管MN2和第二组电阻器用于提供输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]到后续电路,因而输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]的生成将更加稳定。具体地,当后续电路使用输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]时,输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]可能会突然下降。此时,由于运算放大器120仍然提供稳定的控制信号Vc至晶体管MN2的栅电极,所以输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]会立即回到原来的电平,即参考电压缓冲器100具有更好的稳定时间。另外,当参考电压缓冲器100用于具有快速采样率的ADC中时,稳定时间需要被设计得更短以稳定输出参考电压。在该实施例中,负载130和140使用诸如NMOS或PMOS的有源器件可以使稳定时间更短。

尽管可以通过使用具有有源器件的负载130和140来改善参考电压缓冲器100的稳定时间,但是有源器件可能容易遭受PVT问题,即,输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]容易受到PVT变化的影响。为了解决这个问题,负载130、负载140和参考电压生成器110被设计为针对PVT变化具有相同的特性,也就是说,如果温度变化使负载130/140具有更大的压差(dropout voltage)(例如,电阻器R1N与负载130之间的节点处的电压变得更高),温度变化还使得参考电压生成器110产生具有更高电平的参考电压Vref。例如,负载130和140均是与绝对温度成反比(inverse proportional to absolute temperature,inversePTAT)(即,反PTAT)的负载,并且参考电压生成器110是反PTAT参考电压生成器。

通过将负载130和140以及参考电压生成器110设计为响应于PVT变化具有相同的特性,即使输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]的绝对值发生变化,输出参考电压Vrp[m]、Vrp[m-1]……Vrn[m]也适合于量化器的比较器。具体地,量化器内的每个比较器接收参考电压缓冲器100产生的两个输出参考电压,例如,一个比较器使用输出参考电压Vrp[m]和Vrn[m],另一个比较器使用输出参考电压Vrp[m-1]和Vrn[m-1]……依此类推。当温度变化使得负载140具有更大的压差(即,输出参考电压Vrn[m]的电压电平增加)时,由参考电压生成器提供的参考电压Vref增加,从而使电阻器R13和R14之间的节点具有更高的电压电平,电阻器R23和R24之间的节点相应地也具有较高的电压电平。因此,由于所有的输出参考电压均具有增加的电压电平,因此两个输出参考电压(例如Vrp[m]和Vrn[m])之间的电压差将保持稳定,并且比较器可以正常工作。

图2示出了根据本发明的一个实施例的参考电压缓冲器100的详细的示意电路。如图2所示,负载130由具有栅极、源极和漏极的PMOS MP1实现,其中,源极耦接至电阻器R1N,漏极和栅极耦接至接地电压。负载140由具有栅极、源极和漏极的PMOS MP2实现,其中,源极耦接到电阻器R2N,漏极和栅极耦接至接地电压。参考电压生成器110包括带隙参考电路(bandgap reference circuit)210、运算放大器220、晶体管MP0、MP3和MP4以及电阻器R1、R2和R3。运算放大器220具有正输入端、负输入端和输出端,其中负输入端接收由带隙参考电路210产生的带隙参考电压Vbg,正输入端耦接到晶体管MP3和电阻器R1之间的节点,输出端被配置为输出控制信号Vc'至晶体管MP3和MP4。晶体管MP3通过使用具有漏极、源极和栅极的PMOS来实现,其中,源极耦接至电源电压VDD,漏极耦接至电阻器R1,栅极接收由运算放大器220产生控制信号Vc'。晶体管MP4通过使用具有漏极、源极和栅极的PMOS来实现,其中源极耦接到电源电压VDD,漏极耦接到电阻R2,栅极接收由运算放大器220产生的控制信号Vc'。晶体管MP0通过使用具有漏极、源极和栅极的PMOS来实现,其中源极耦接到电阻器R3,漏极和栅极连接到接地电压。另外,电阻器R2和R3之间的节点用于生成参考电压Vref至运算放大器120。

在其他实施例中,晶体管MP3和MP4可以由NMOS实现,和/或可以在晶体管MP3和电阻器R1之间插入另一个电阻器。

在图2所示的实施例中,由于负载130和晶体管MP0具有相同的特性(例如,两者均由PMOS实现),所以响应于温度变化,晶体管MP1的源极处的电压变化与晶体管MP0的源极处的电压变化非常相似,即,晶体管MP1的源极处的电压变化与参考电压Vref的电压变化非常相似。因此,两个输出参考电压(例如Vrp[m-2]和Vrn[m-2])之间的电压差将保持稳定。

另外,为了提高噪声容忍度,优选地,输出参考电压具有大的满量程,即,最高输出参考电压Vrp[m]和最低输出参考电压Vrn[m]之间的差应当被设计得尽可能大。在该实施例中,为了降低输出参考电压Vrn[m]的电压,通过具有开环设计的PMOS MP1/MP2来实现负载130/140。通过使用负载130/140的开环设计,即,不设置运算放大器来接收源极处的电压对栅极进行控制,当PMOS MP1/MP2工作在饱和区时其源极可以具有较低的电压电平。

图3是示出根据本发明的一个实施例的量化器300的示意图。如图3所示,量化器300包括多个比较器(例如310、320和330)、多个电容器(例如C1~C6)以及多个开关。在该实施例中,量化器300的开关由控制信号

请注意,量化器300仅用于说明目的,只要量化器300内的每个比较器使用两个输出参考电压,量化器300的内部电路可以具有不同的设计。另外,因为本发明着重于参考电压缓冲器100提供输出参考电压,所以这里省略了关于量化器300的进一步描述。

简要地概述,在本发明的参考电压缓冲器中,参考电压缓冲器使用有源负载来减少稳定时间,该负载和参考电压缓冲器的参考电压生成器被设计为响应于温度变化具有相同的特性,以克服PVT问题,并且参考电压缓冲器的负载使用开环设计以使输出参考电压具有较大的满量程。因此,参考电压缓冲器可以以更快的稳定时间为后续电路提供合适的输出参考电压。

本领域技术人员将容易地认识到,在保持本发明的教导的同时,可以对装置和方法进行多种修改和变更。因此,以上公开内容应被解释为仅由所附权利要求来限定。

- 参考电压缓冲器

- 一种带有交叉耦合滤波网络的高速参考电压缓冲器