一种多载波调制装置及其调制方法

文献发布时间:2023-06-19 10:58:46

技术领域

本发明涉一种多载波调制装置及其相应的调制方法。

背景技术

着通信技术、嵌入式计算技术和传感器技术的飞速发展和日益成熟,具有感知能力、计算能力和通信能力的无线传感器节点开始出现,并且引起了人们的极大关注。这种无线传感器节点构成无线传感网能够协调地感知、采集和处理网络覆盖区域内的各种环境或监测对象信息,并发布给需要这些信息的用户。无线传感网将逻辑上的信息世界与真实的物理世界融合在一起,深刻地改变了人与自然的交互方式;可以广泛地应用于军事、工农业控制、生物医疗、环境监测等诸多领域。多载波信号在信号传输、测试测量等方面具有广泛的应用,比如,可以用来方便地配置发射机或接收机测试所需的宽带测试信号,多载波调制采用了多个载波信号,它将需要传输的数据信号分解为若干个子数据流,从而使子数据流具有低得多的传输比特速率,利用这些数据分别去调制若干个载波,也就是,将各载波信号进行不同或相同的频率偏移和相位偏移后叠加形成调制后的波形。现有的QPSK,BPSK等多种调制方式都是针对单一载波信号调制和解调的工作,使用FPGA来进行实现,不能实现在某一带宽内可以任意同时输出多个不同载波信号,不能对多个载波信号可以独立实现不同方式的调制工作。在干扰领域,存在一定的单一性和干扰性不够强,输出载波信号个数和调制方式不够灵活。

发明内容

本发明要解决的技术问题是如何克服现有多载波信号调制方式的单一性和抗干扰性上的问题,提供一种多载波调制装置及其相应的调制方法。

本多载波调制装置自载波输入至输出方向依次包括扰码器、比特映射器、载波映射器、多载波调制器、限幅器、合成载波调制器,其中

所述扰码器用于对输入的数据进行扰码,破坏相邻数据之间的相关性;所述比特映射器用于根据所选择的调制方式,对扰码后的序列进行截取并映射到星座图上的调制符号;所述载波映射器用于根据所设定的有用子载波序号,将映射后的调制符号映射到指定的子载波上;所述多载波调制器用于把经过子载波映射后的数据调制到其相对应的子载波上;所述限幅器用于对多载波调制信号的峰值进行限制,以减小输出信号的峰均比;所述合成载波调制器用于将经过多载波调制的信号调制到中频载波上;

所述多载波调制器包括运算放大器、A/D转换模块、存储器、处理器、时钟模块、晶振模块、FPGA芯片、D/A转换模块、低通滤波器,所述时钟模块的输入端分别与处理器和晶振模块连接,时钟模块的输出端分别与FPGA芯片和D/A转换电路连接;多载波信号依次通过运算放大器和A/D转换模块输入FPGA芯片,FPGA的输出端通过D/A转换电路与低通滤波电路连接,并由低通滤波电路进行信号输出。

进一步的,所述的FPGA芯片与处理器和存储器连接。

具体的,所述运算放大器采用AD823AR芯片,所述AD转换模块采用AD7476芯片,所述FPGA芯片型号为XC7K160T-2FFG676I,所述处理器型号为C8051F340,所述存储器型号为AT24C256,所述时钟模块采用AD9516芯片,所述晶振模块采用TDGAAN-40.00MH芯片,所述D/A转换模块采用AD9736z芯片

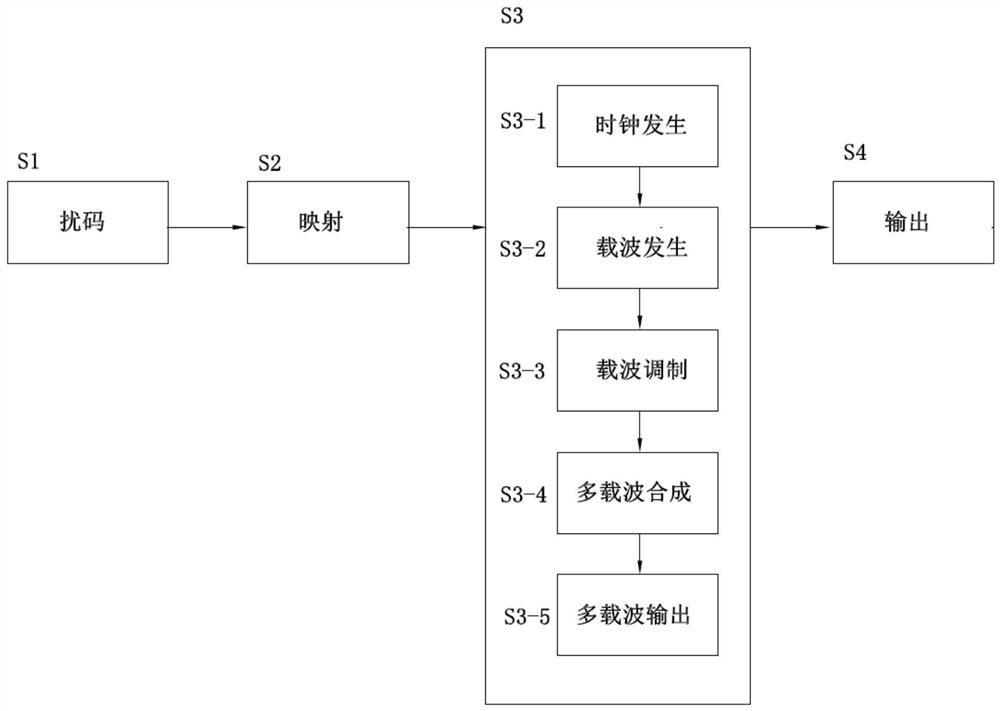

本多载波调制方法应用上述多载波调制装置,具体包括以下步骤,

S1扰码:对输入的数据进行扰码,破坏相邻数据之间的相关性;

S2映射:特映射器用于根据所选择的调制方式,对扰码后的序列进行截取并映射到星座图上的调制符号;设定的有用子载波序号,将映射后的调制符号映射到指定的子载波上;

S3调制:把经过子载波映射后的数据调制到其相对应的子载波上合成;将合成信号经D/A转换和低通滤波后输出给限幅器进行峰值限制,减小输出信号的峰均比;

S4输出:把经峰值限制的合成信号经D/A转换和低通滤波后输出给中频调制器输出。

进一步的,步骤S3所述调制包括以下步骤:

S3-1时钟发生:处理器由晶振模块和时钟模块产生高速时钟信号,输出给FPGA芯片和D/A转换模块;

S3-2载波发生:由FPGA芯片内部DCM将时钟信号提供给DDS,产生多个载波信号,输出给调制模块;调制信号通过运算放大器和A/D转换模块后,输出FPGA芯片;

S3-3载波调制:调制模块根据外部SPI命令的控制,对载波信号和输入的调制信号进行调制,得到调制后的载波信号;

S3-4多载波合成:FPGA芯片内部的数字合成模块在外部SPI命令的控制下,选择预设数量的调制后的载波信号进行合成,合成得到的信号;

S3-5多载波输出:合成信号经D/A转换和低通滤波后输出给下游限幅器。

本发明一种多载波调制装置及其调制方法,通过将可用频段划分成若干个子载波,在每个子载波上传输低速的数据流,能有效克服无线信道中多径造成的符号间干扰,同时能够获得较高的频谱效率;另外其具有合成输出的功能,调制合成过程在多载波调制器中完成,实现多个载波信号的同时产生输出和调制的同时,还使得每个载波信号的调制方式独立可控。

附图说明

下面结合附图对本发明一种多载波调制装置作进一步说明:

图1是本多载波调制装置的逻辑架构线框图;

图2是本多载波调制方法的调制流程图。

具体实施方式

以下用具体实施例对本发明技术方案做进一步描述,但本发明的保护范围不限制于下列实施例。

实施方式:本多载波调制装置自载波输入至输出方向依次包括扰码器、比特映射器、载波映射器、多载波调制器、限幅器、合成载波调制器,其中所述扰码器用于对输入的数据进行扰码,破坏相邻数据之间的相关性;所述比特映射器用于根据所选择的调制方式,对扰码后的序列进行截取并映射到星座图上的调制符号;所述载波映射器用于根据所设定的有用子载波序号,将映射后的调制符号映射到指定的子载波上;所述多载波调制器用于把经过子载波映射后的数据调制到其相对应的子载波上;所述限幅器用于对多载波调制信号的峰值进行限制,以减小输出信号的峰均比;所述合成载波调制器用于将经过多载波调制的信号调制到中频载波上;所述多载波调制器包括运算放大器、A/D转换模块、存储器、处理器、时钟模块、晶振模块、FPGA芯片、D/A转换模块、低通滤波器,所述时钟模块的输入端分别与处理器和晶振模块连接,时钟模块的输出端分别与FPGA芯片和D/A转换电路连接;多载波信号依次通过运算放大器和A/D转换模块输入FPGA芯片,FPGA的输出端通过D/A转换电路与低通滤波电路连接,并由低通滤波电路进行信号输出。

所述的FPGA芯片与处理器和存储器连接。所述运算放大器采用AD823AR芯片,所述AD转换模块采用AD7476芯片,所述FPGA芯片型号为XC7K160T-2FFG676I,所述处理器型号为C8051F340,所述存储器型号为AT24C256,所述时钟模块采用AD9516芯片,所述晶振模块采用TDGAAN-40.00MH芯片,所述D/A转换模块采用AD9736z芯片

实施例:本多载波调制方法应用上述多载波调制装置,具体包括以下步骤,S1扰码:对输入的数据进行扰码,破坏相邻数据之间的相关性;

S2映射:特映射器用于根据所选择的调制方式,对扰码后的序列进行截取并映射到星座图上的调制符号;设定的有用子载波序号,将映射后的调制符号映射到指定的子载波上;

S3调制:把经过子载波映射后的数据调制到其相对应的子载波上合成;将合成信号经D/A转换和低通滤波后输出给限幅器进行峰值限制,减小输出信号的峰均比;所述调制合成过程具体包括以下步骤:

S3-1时钟发生:处理器由晶振模块和时钟模块产生高速时钟信号,输出给FPGA芯片和D/A转换模块;

S3-2载波发生:由FPGA芯片内部DCM将时钟信号提供给DDS,产生多个载波信号,输出给调制模块;调制信号通过运算放大器和A/D转换模块后,输出FPGA芯片;

S3-3载波调制:调制模块根据外部SPI命令的控制,对载波信号和输入的调制信号进行调制,得到调制后的载波信号;

S3-4多载波合成:FPGA芯片内部的数字合成模块在外部SPI命令的控制下,选择预设数量的调制后的载波信号进行合成,合成得到的信号;

S3-5多载波输出:合成信号经D/A转换和低通滤波后输出给下游限幅器。

S4输出:把经峰值限制的合成信号经D/A转换和低通滤波后输出给中频调制器输出。

本发明一种多载波调制装置及其调制方法,通过将可用频段划分成若干个子载波,在每个子载波上传输低速的数据流,能有效克服无线信道中多径造成的符号间干扰,同时能够获得较高的频谱效率;另外其具有合成输出的功能,调制合成过程在多载波调制器中完成,实现多个载波信号的同时产生输出和调制的同时,还使得每个载波信号的调制方式独立可控。

以上描述显示了本发明的主要特征、基本原理,以及本发明的优点。对于本领域技术人员而言,显然本发明不限于上述示范性实施方式或者实施例的细节,且在不背离本发明的精神或者基本特征的情况下,能够以其他的具体形式实现本发明。因此应将上述实施方式或者实施例看作示范性的,且非限制性的。本发明的范围由所附权利要求而非上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

- 多载波数据接收方法、多载波调制装置及多载波调制系统

- 一种多载波调制装置及其调制方法