半导体装置和设备

文献发布时间:2023-06-19 11:17:41

技术领域

本发明涉及半导体装置和包括该半导体装置的设备。

背景技术

存在包括各自具有不同功能的多个堆叠的半导体层的半导体装置。日本专利特开No.2019-140237讨论了包括第一半导体层和第二半导体层的光电转换装置。多个光电转换部二维地布置在第一半导体层上。第二半导体层包括信号处理电路,该信号处理电路处理从多个光电转换部输出的信号。

根据日本专利特开No.2019-140237,半导体层包括p沟道金属氧化物半导体(PMOS)晶体管。本发明人研究了日本专利特开No.2019-140237中讨论的技术,并且发现存在PMOS晶体管不具有优异的特性的某些情况,并且存在改善半导体装置的性能的余地。

发明内容

本发明涉及表现出优异性能的半导体装置。

本发明的第一方面提供了一种半导体装置,该半导体装置包括:第一半导体层;与第一半导体层重叠的第二半导体层;以及布置在第一半导体层和第二半导体层之间的布线结构,其中第二半导体层设置有p型金属绝缘体半导体(p型MIS)晶体管,其中第一半导体层的晶体结构在沿着第一半导体层的主表面的方向上具有第一晶体取向和第二晶体取向,以及第一半导体层在沿着第一晶体取向的方向上的杨氏模量高于在第一半导体层在沿着第二晶体取向的方向上的杨氏模量,其中由第一晶体取向与p型MIS晶体管的源极和漏极被布置的方向形成的角度大于30度且小于60度,并且其中由第二晶体取向与p型MIS晶体管的源极和漏极被布置的方向形成的角度为0度以上且30度以下。

本发明的第二方面提供了一种设备,该设备包括:根据如上所述的半导体装置;以及以下中的至少一个:与半导体装置相对应的光学装置;控制半导体装置的控制装置;处理从半导体装置输出的信号的处理装置;显示从半导体装置获取的信息的显示装置;存储从半导体装置获取的信息的存储装置;以及基于从半导体装置获取的信息进行操作的机械装置。

通过以下参考附图对示例性实施例的描述,本发明的其它特征将变得清楚。

附图说明

图1A和图1B是示出半导体装置的示意图。

图2是示出半导体装置的示意图。

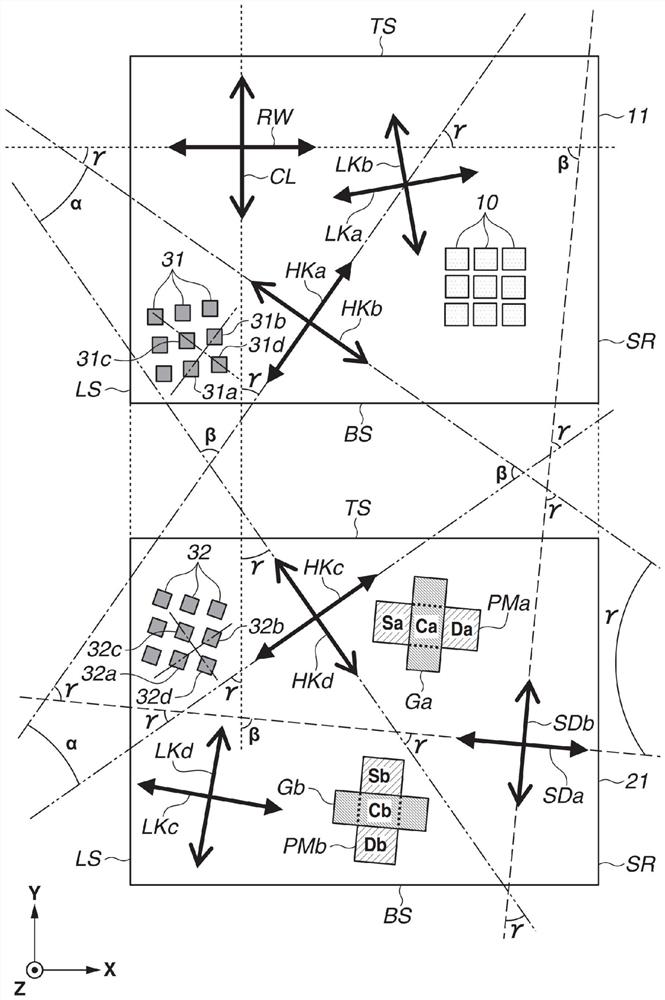

图3是示出半导体装置的示意图。

图4A和图4B是示出半导体装置的示意图。

图5A和图5B是示出半导体装置的示意图。

图6A和图6B是示出半导体装置的示意图。

具体实施方式

下面将参考附图描述本发明的各种示例性实施例。在以下描述和附图中,类似的配置在多个附图上被赋予相同的附图标记。因此,将参考多个附图描述配置,并且省略具有相同附图标记的配置的冗余描述。

<第一示例性实施例>

图1A示出了半导体装置APR。半导体装置APR整体或部分地是包括堆叠的芯片1和2的半导体器件集成电路(半导体器件IC)。根据本示例性实施例的半导体装置APR例如是可以用作图像传感器、自动聚焦(AF)传感器、测光传感器或测距传感器的光电转换装置。半导体装置APR包括堆叠的芯片1和2。芯片1包括以矩阵形式布置的多个电路10。芯片2包括多个电路20。

芯片1包括半导体层11和布线结构12。半导体层11包括多个电路10的多个半导体元件(未示出)。布线结构12包括多个电路10的M个布线层(未示出)。芯片2包括半导体层21和布线结构22。半导体层21包括多个电路20的多个半导体元件(未示出)。布线结构22包括多个电路20的N个布线层(未图示)。

半导体层21与半导体层11重叠。布线结构12和22布置在半导体层11和21之间。

布线结构12布置在半导体层11和21之间。布线结构22布置在布线结构12和半导体层21之间。

电路10可以是包括光电转换元件并且通常还包括放大元件的像素电路。其细节将在下面描述。电路20是驱动电路10并处理来自电路10的信号的电路。

本示例性实施例可应用于的半导体装置APR不限于光电转换装置。本示例性实施例还可应用于例如包括芯片1和2并且芯片1和2中的一个包括计算电路而另一个包括存储电路的半导体装置APR。此外,半导体装置APR的芯片1和2中的一个可以包括控制芯片1和2中的另一个的控制电路。此外,半导体装置APR的芯片1和2中的一个可以包括处理从芯片1和2中的另一个输出的信号的处理电路。

图1B示出了包括半导体装置APR的设备EQP。半导体器件IC包括像素区PX,在像素区PX中,包括电路10的像素PXC以矩阵形式布置。像素PXC除了电路10的光电转换元件之外还可以包括微透镜和/或滤色器。半导体器件IC可以包括在像素区PX周围的外围区PR。可以在外围区PR中布置除电路10以外的电路。半导体装置APR除了半导体器件IC之外还可以包括用于容纳半导体器件IC的封装体PKG。设备EQP可以进一步包括光学装置OPT、控制装置CTRL、处理装置PRCS、显示装置DSPL、存储装置MMRY和机械装置MCHN中的至少一个。设备EQP的细节将在下面描述。

图2是示出半导体装置APR的截面图。半导体层11包括前表面115、后表面116和侧表面。前表面115和后表面116是半导体层11的两个主表面并且是相对的表面。半导体层21包括前表面215、后表面216和侧表面。前表面215和后表面216是半导体层21的两个主表面并且是相对的表面。半导体层11的厚度是前表面115和后表面116之间的距离。半导体层21的厚度是前表面215和后表面216之间的距离。半导体层11的厚度小于半导体层21的厚度。半导体层11的厚度例如为1μm至10μm,例如为2μm至5μm。半导体层21的厚度例如为10μm至1000μm,例如为50μm至500μm或700μm至800μm。在使用200mm至300mm的晶片来制备半导体层21的情况下,如果将晶片处理为非常薄,则可能会损坏半导体层11和/或21。因此,半导体层21的厚度期望为700μm以上且800μm以下。在前表面115上设置有n型金属绝缘体半导体(n型MIS)晶体管的栅极电极111。尽管在本示例性实施例中在半导体层11上未设置p型金属绝缘体半导体(p型MIS)晶体管,但是可以在前表面115上设置p型MIS晶体管的栅极电极。在前表面215上设置有p型MIS晶体管的栅极电极212。尽管在本示例性实施例中在前表面215上设置有n型MIS晶体管的栅极电极211,但是半导体层21不一定包括n型MIS晶体管。本示例性实施例特别关注于p型MIS晶体管。由于MIS晶体管的栅极电极通常是氧化物,因此MIS晶体管也可以称为MOS晶体管。通常将使用n型MOS晶体管和p型MOS晶体管的电路称为互补金属氧化物半导体(CMOS)电路,但是CMOS电路的MIS晶体管的栅极绝缘膜不限于氧化物,并且可以是氮化物或碳化物。

覆盖栅极电极111的绝缘膜110设置在半导体层11与布线结构12之间。覆盖栅极电极211和212的绝缘膜210设置在半导体层21与布线结构22之间。

布线结构12包括多级布线层121、122和123,在布线层123上的电极焊盘31以及在布线层121、122和123以及电极焊盘31周围的绝缘体构件120。电极焊盘31在绝缘体构件120的凹陷(沟槽)中。具体地,电极焊盘31具有镶嵌结构。尽管在本示例性实施例中电极焊盘31具有双镶嵌结构,但是电极焊盘31可以具有单镶嵌结构。布线层121、122和123以及电极焊盘31的主要成分是铜。这里,“主要成分”是指以重量计的80%以上。

布线结构22包括多级布线层221、222、223和224,布线层224上的电极焊盘32以及在布线层221、222、223和224以及电极焊盘32周围的绝缘体构件220。电极焊盘32在绝缘体构件220的凹陷(沟槽)中。具体地,电极焊盘32具有镶嵌结构。尽管在本示例性实施例中电极焊盘32具有双镶嵌结构,但是电极焊盘32可以具有单镶嵌结构。布线层221、222和223以及电极焊盘32的主要成分是铜。布线层224的主要成分是铝。

在布线结构30中,布线结构12和22在结合表面33处结合在一起。在结合表面33处,布线结构12和22的绝缘体构件120和220共价键合。此外,在结合表面33处,布线结构12和22的电极焊盘31和32(金属焊盘)金属键合。如上所述在结合表面33处通过绝缘体的键合(共价键合)和导体的键合(金属键合)的组合进行的结合被称为“混合结合”。结合布线结构12和22的形式不限于混合结合。结合表面33可以仅包括绝缘体构件120和220,并且布线结构12和22可以通过绝缘体构件120和220的键合(共价键合)结合在一起。可替换地,布线结构12和22可以用粘合剂结合在一起。可替换地,可以在电极焊盘31和32之间使用凸块将布线结构12和22结合在一起,而无需直接结合布线结构12和22的绝缘体构件120和220。在使用凸块的情况下,底部填充树脂材料可以设置在布线结构12和22的绝缘体构件120和220之间。在混合结合和使用凸块的结合中,芯片1和2通过电极焊盘31和32电连接。在结合表面33仅包括绝缘体构件120和220的情况下,布线结构12和22的布线层经由穿过半导体层11或21的贯穿电极(贯穿硅通孔(TSV))连接。

光学结构40根据需要设置在半导体层11的后表面116上。光学结构40可以包括微透镜阵列、滤色器阵列、层内透镜阵列、诸如遮光壁或遮光膜之类的遮光构件以及电介质膜。滤色器阵列可以布置在微透镜阵列和半导体层11之间。层内透镜阵列可以布置在滤色器阵列和半导体层11之间。光学结构40的遮光壁可以布置在层内透镜阵列的层内透镜之间。光学结构40的遮光膜可以被设置为遮挡光接收区域免受光。光学结构40的电介质膜是包括抗反射层和电荷固定层的多层膜,并且可以包括金属氧化物层和/或硅化合物层。

下面将参考图2和图3描述在半导体层11是硅层的情况下硅的晶体结构与半导体层11之间的关系。图2示出了半导体层11的晶体结构中的晶体取向HKa和HKb以及晶体取向LKa和LKb。晶体取向HKa和HKb以及晶体取向LKa和LKb是但不限于平行于半导体层11的主表面(前表面115和后表面116)。在本示例性实施例中,半导体层11的主表面(前表面115和后表面116)平行于基于密勒指数的平面指数的(100)面。具有单晶结构的半导体层11由于以下原因而具有杨氏模量各向异性。具体地,可以将杨氏模量视为晶体对原子之间的距离变化的抵抗力,并且原子之间的距离取决于晶体取向。半导体层11在沿着晶体取向HKa和HKb的方向上的杨氏模量比在沿着晶体取向LKa和LKb的方向上的杨氏模量高。具体地,半导体层11在沿着晶体取向LKa和LKb的方向上比在沿着晶体取向HKa和HKb的方向上更易变形。

图3示出了在从垂直于前表面115和后表面116的方向观察半导体层11的情况下的晶体取向HKa和HKb以及晶体取向LKa和LKb。由晶体取向HKa和HKb形成的角度为60度以上且90度以下。由晶体取向LKa和LKb形成的角度为60度以上且90度以下。由晶体取向HKa和HKb与晶体取向LKa和LKb形成的角度大于30度且小于60度。例如,作为硅层的半导体层11中的晶体取向HKa和HKb为基于密勒指数的取向指数的<110>取向。作为硅层的半导体层11具有至少两个(例如,六个)<110>取向,并且两个<110>取向中的一个是晶体取向HKa且另一个是晶体取向HKb。两个<110>取向是正交的。具体地,由均可以是<110>取向的晶体取向HKa和HKb形成的角度为90度。

作为硅层的半导体层11具有至少两个(例如,六个)<100>取向,并且两个<100>取向中的一个是晶体取向LKa且另一个是晶体取向LKb。两个<100>取向是正交的。具体地,由晶体取向LKa和LKb形成的角度为90度。由可以分别是晶体取向LKa和LKb的两个<100>取向中的每一个与可以分别是晶体取向HKa和HKb的两个<110>取向中的每一个形成的角度为45度。

作为硅层的半导体层11在平行于<100>取向的方向上的杨氏模量约为130GPa(125GPa至135GPa)。作为硅层的半导体层11在平行于<110>取向的方向上的杨氏模量约为170GPa(165GPa至175GPa)。在<100>和<110>取向之间的方向上的杨氏模量是在平行于<100>取向的方向上的杨氏模量与在平行于<110>取向的方向上的杨氏模量之间的值(130GPa至170GPa)。具体地,在沿着半导体层11的主表面(前表面115和后表面116)的方向上,半导体层11在平行于晶体取向HKa和HKb的方向上的杨氏模量可以相对高。此外,在沿着半导体层11的主表面(前表面115和后表面116)的方向上,半导体层11在平行于晶体取向LKa和LKb的方向上的杨氏模量可以相对低。作为硅层的半导体层11具有至少两个(例如,六个)<111>取向,并且半导体层11在平行于<111>取向的方向上的杨氏模量约为185GPa(180GPa至190GPa)。

在作为硅层的半导体层11中发生解理的取向(解理取向(cleavageorientation))是<110>取向。在解理取向上发生解理的情况下,由解理形成的解理面是基于密勒指数的平面指数的(110)面。解理面垂直于解理取向。解理面垂直于(100)面,并且可以垂直于半导体层11的主表面。从以上描述可以理解,晶体取向HKa和HKb例如是<110>取向,因此可以是解理取向。更具体地,通过沿着作为解理取向的晶体取向HKa的解理形成的解理面垂直于作为解理取向的晶体取向HKb。通过沿着作为解理取向的晶体取向HKb的解理形成的解理面垂直于作为解理取向的晶体取向HKa。

图3示出了在从垂直于前表面215和后表面216的方向观察半导体层21的情况下的晶体取向HKc和HKd以及晶体取向LKc和LKd。由晶体取向HKc和HKd形成的角度为60度以上且90度以下。由晶体取向LKc和LKd形成的角度为60度以上且90度以下。由晶体取向HKc或HKd与晶体取向LKc或LKd形成的角度大于30度且小于60度。例如,作为硅层的半导体层21中的晶体取向HKc和HKd为基于密勒指数的取向指数的<110>取向。作为硅层的半导体层21具有至少两个(例如,六个)<110>取向,并且两个<110>取向中的一个是晶体取向HKc且另一个是晶体取向HKd。两个<110>取向是正交的。具体地,由均为<110>取向的晶体取向HKc和HKd形成的角度为90度。

作为硅层的半导体层21具有至少两个(例如,六个)<100>取向,并且两个<100>取向中的一个是晶体取向LKc且另一个是晶体取向LKd。两个<100>取向是正交的。具体地,由晶体取向LKc和LKd形成的角度为90度。由可以分别是晶体取向LKc和LKd的两个<100>取向中的每一个与可以分别是晶体取向HKc和HKd的两个<110>取向中的每一个形成的角度为45度。

作为硅层的半导体层21在平行于<100>取向的方向上的杨氏模量约为130GPa(125GPa至135GPa)。作为硅层的半导体层21在平行于<110>取向的方向上的杨氏模量约为170GPa(165GPa至175GPa)。在<100>和<110>取向之间的方向上的杨氏模量是在平行于<100>取向的方向上的杨氏模量与在平行于<110>取向的方向上的杨氏模量之间的值(130GPa至170GPa)。具体地,在沿着半导体层21的主表面(前表面215和后表面216)的方向上,半导体层21在平行于晶体取向HKc和HKd的方向上的杨氏模量可以相对高。此外,在沿着半导体层21的主表面(前表面215和后表面216)的方向上,半导体层21在平行于晶体取向LKc和LKd的方向上的杨氏模量可以相对低。作为硅层的半导体层21具有至少两个(例如,六个)<111>取向,并且半导体层21在平行于<111>取向的方向上的杨氏模量约为185GPa(180GPa至190GPa)。

在作为硅层的半导体层21中发生解理的取向(解理取向)是<110>取向。在解理取向上发生解理的情况下,由解理形成的解理面是基于密勒指数的平面指数的(110)面。解理面垂直于解理取向。解理面垂直于(100)面,并且可以垂直于半导体层21的主表面。从以上描述可以理解,晶体取向HKc和HKd例如是<110>取向,因此可以是解理取向。更具体地,通过沿着作为解理取向的晶体取向HKc的解理形成的解理面垂直于作为解理取向的晶体取向HKd。通过沿着作为解理取向的晶体取向HKd的解理形成的解理面垂直于作为解理取向的晶体取向HKc。

不仅对于硅层,而且对于各种晶体结构,都定义了杨氏模量相对高的取向和杨氏模量相对低的晶体取向。类似地,不仅对于硅层,而且对于各种晶体结构,都定义了解理取向。在晶体结构沿着晶体结构的主表面具有多个解理取向的情况下,由多个解理取向形成的角度可以为60度以上且90度以下。在晶体结构沿着晶体结构的主表面仅具有两个解理取向的情况下,由多个解理取向形成的角度可以为90度。在晶体结构沿着晶体结构的主表面仅具有三个解理取向的情况下,由多个解理取向形成的角度可以为60度。

图3示出了在从垂直于前表面115和后表面116的方向观察半导体层11的情况下,半导体层11的轮廓形状和作为单元的电路10的布置方向。半导体层11的轮廓基本为四边形。半导体层11的轮廓的四个边包括右边SRa、左边LSa、上边TSa和下边BSa。左边LSa基本平行于右边SRa,并且右边SRa和左边LSa沿着方向LR延伸。上边TSa基本平行于下边BSa,并且上边TSa和下边BSa沿着方向TB延伸。多个单元(电路10)以矩阵形式布置的单元阵列包括单元行和单元列。每个单元行包括在行方向RW上布置的两个或更多个单元(电路10),并且每个单元列包括在列方向CL上布置的两个或更多个单元(电路10)。多个单元行在列方向CL上布置,并且多个单元列在行方向RW上布置。

图3示出了在从垂直于前表面215和后表面216的方向观察半导体层21的情况下的半导体层21的轮廓形状。半导体层21的轮廓基本为四边形。半导体层21的轮廓的四个边包括右边SRb、左边LSb、上边TSb和下边BSb。左边LSb基本平行于右边SRb,并且右边SRb和左边LSb沿着方向LR延伸。上边TSb基本平行于下边BSb,并且上边TSb和下边BSb沿着方向TB延伸。

在本示例性实施例中,半导体层11和21的轮廓基本一致。上边TSa的长度基本等于上边TSb的长度。下边BSa的长度基本等于下边BSb的长度。左边LSa的长度基本等于左边LSb的长度。右边SRa的长度基本等于右边SRb的长度。如本文所使用的,短语“基本等于”是指两个对应边中的一边的长度是另一边的长度的90%以上且110%以下。

半导体层11的至少一个边的长度越长,则半导体层11的应力对半导体层21的影响越大。因此,本示例性实施例适合于半导体层11的至少一个边的长度为10mm以上的情况。对角线约为一英寸的格式的图像传感器的图像捕获区为13±1mm×9±1mm,因此半导体层11的至少一个边的长度需要为10mm以上。本示例性实施例更适合于半导体层11的至少一个边的长度为20mm以上的情况。C型高级照片系统(APS-C)格式的图像传感器的图像捕获区为23±1mm×15±1mm,因此半导体层11的至少一个边的长度需要为20mm以上。本示例性实施例甚至更适合于半导体层11的至少一个边的长度为30mm以上的情况。35mm格式的图像传感器的图像捕获区为36±1mm×24±1mm,因此半导体层11的至少一个边的长度需要为20mm以上。图3示出了从垂直于前表面215和后表面216的方向观察半导体层21的情况下的半导体层21的p型MIS晶体管PMa和PMb的布局。

p型MIS晶体管PMa包括源极Sa和漏极Da。p型MIS晶体管PMa包括在源极Sa和漏极Da之间的沟道Ca。p型MIS晶体管PMa的栅极电极Ga的至少一部分在沟道Ca上。p型MIS晶体管PMa的源极Sa和漏极Da被布置在方向SDa上。方向SDa对应于沟道Ca的沟道长度方向,即,栅极电极Ga的栅极长度方向。

p型MIS晶体管PMb包括源极Sb和漏极Db。p型MIS晶体管PMb包括在源极Sb和漏极Db之间的沟道Cb。p型MIS晶体管PMb的栅极电极Gb的至少一部分在沟道Cb上。p型MIS晶体管PMb的源极Sb和漏极Db被布置在方向SDb上。方向SDb对应于沟道Cb的沟道长度方向,即,栅极电极Gb的栅极长度方向。

方向SDa和SDb相交。具体地,由方向SDa和SDb形成的角度大于0度。由源极Sa和漏极Da被布置的方向SDa与源极Sb和漏极Db被布置的方向SDb形成的角度可以为60度以上且90度以下。由方向SDa和SDb形成的角度为80度以上且90度以下,并且在本示例性实施例中,该角度为90度。半导体层21可以设置有p型MIS晶体管PMa和PMb两者或之一。

在图3中,由各方向形成的每个角度由α、β或γ表示。角度α是0度以上且30度以下的范围内的角度,期望地是0度以上且10度以下的范围内的角度,典型地为0度。角度β是60度以上且90度以下的范围内的角度,期望是80度以上且90度以下的范围内的角度,典型地为90度。角度γ是大于30度且小于60度的角度,期望地在40度以上且50度以下的范围内的角度,典型地为45度。

在由两个方向形成的角度既不是0度也不是90度的情况下,该角度可以是锐角或钝角,但是本说明书始终关注锐角。具体地,由两个方向形成的角度被限定在0度以上且90度以下的范围内。

如图3中的“γ”所示的,由半导体层11的晶体结构的晶体取向HKa与p型MIS晶体管PMa的源极Sa和漏极Da被布置的方向SDa形成的角度大于30度且小于60度。类似地,如图3中的“γ”所示的,由半导体层11的晶体结构的晶体取向HKb与p型MIS晶体管PMa的源极Sa和漏极Da被布置的方向SDa形成的角度大于30度且小于60度。如图3中的“γ”所示的,由半导体层11的晶体结构的晶体取向HKa和HKb与p型MIS晶体管PMb的源极Sb和漏极Db被布置的方向SDb形成的角度大于30度且小于60度。

如图3中的“α”所示的,由半导体层11的晶体结构的晶体取向LKa与p型MIS晶体管PMa的源极Sa和漏极Da被布置的方向SDa形成的角度为0度以上且30度以下。类似地,如图3中的“α”所示的,由半导体层11的晶体结构的晶体取向LKb与p型MIS晶体管PMa的源极Sa和漏极Da被布置的方向SDa形成的角度为0度以上且30度以下。如图3中的“α”所示的,由半导体层11的晶体结构的晶体取向LKa和LKb与p型MIS晶体管PMb的源极Sb和漏极Db被布置的方向SDb形成的角度为0度以上且30度以下。

本示例性实施例集中于在半导体层11处产生的应力将应力施加到半导体层21的点。在半导体层11中具有较高杨氏模量的方向上,在半导体层11处产生的应力更大。施加到半导体层21且源自半导体层11的应力在平行于半导体层11中具有较高杨氏模量的方向的方向上比在其它方向上大。半导体层21处产生的应力导致p型MIS晶体管PMa和PMb的沟道Ca和Cb的晶体结构的畸变。p型MIS晶体管PMa和PMb的沟道Ca和Cb的晶体结构的畸变改变了p型MIS晶体管PMa和PMb的特性。因此,在半导体层11中具有高杨氏模量的方向HKa和HKb被布置为既不平行也不垂直于(角度γ)源极Sa和Sb以及漏极Da和Db被布置在半导体层21中的方向。此外,在半导体层11中具有较低杨氏模量的方向LKa和LKb被布置为基本平行(角度α)或基本垂直于(角度β)源极Sa和Sb以及漏极Da和Db被布置在半导体层21中的方向。因此,即使在半导体层11处产生应力,p型MIS晶体管PMa和PMb的特性也不太可能被改变。

如图3中的“α”所示的,由半导体层11的晶体取向HKa与半导体层21的晶体取向HKc形成的角度为0度以上且30度以下。如图3中的“α”所示的,由半导体层11的晶体取向HKb与半导体层21的晶体取向HKd形成的角度为0度以上且30度以下。如图3中的“β”所示的,由半导体层11的晶体取向HKb与半导体层21的晶体取向HKd形成的角度为60度以上且90度以下。如图3中的“β”所示的,由半导体层11的晶体取向HKb与半导体层21的晶体取向HKc形成的角度为60度以上且90度以下。

如上所述,在半导体层11中具有相对高的杨氏模量的方向基本平行于在半导体层21中具有相对高的杨氏模量的方向。此外,在半导体层11中具有相对低的杨氏模量的方向基本平行于在半导体层21中具有相对低的杨氏模量的方向。这减小了可能在半导体层11和21之间产生的应力的方向依赖性。因此,改善了半导体层11和/或半导体层21的晶体管特性。此外,减少了制备期间半导体层11和/或半导体层21的畸变,并且增加了成品率。减少了制备期间半导体层11和/或半导体层21的畸变,并且减少了例如混合结合中的电极焊盘31和32的未对准。这在增加成品率方面是有利的。此外,减少了包括微透镜阵列、滤色器阵列和层内透镜阵列的光学结构40与半导体层11的前表面115上的光电二极管的光轴偏移,这在增加成品率方面是有利的。

如图3中的“γ”所示的,由半导体层11的晶体取向HKa与半导体层11的四个边(右边SR、左边LS、上边TS、下边BS)形成的角度大于30度且小于60度。如图3中的“γ”所示的,由半导体层11的晶体取向HKb与半导体层11的四个边(右边SR、左边LS、上边TS、下边BS)形成的角度大于30度且小于60度。具体地,如图3中的“γ”所示的,由半导体层11的晶体取向HKb与半导体层11的四个边延伸的方向TB和LR形成的角度大于30度且小于60度。

如上所述,晶体取向HKa、HKb、HKc和HKd中的至少一个(在本示例性实施例中为所有晶体取向HKa、HKb、HKc和HKd)被布置为不平行于四个边中的至少一个边(在本示例性实施例中为所有四个边),从而防止了半导体层11和21的四个边碎裂和破裂。在将晶片切片成芯片时,期望使用激光(激光切片)。在用刀片进行切片(刀片切片)时,由于碎裂,四个边的形状经常变得不均匀。另一方面,在激光切片时,四个边的形状不太可能碎裂,从而减少了不均匀性。例如,在刀片切片时,沿着半导体层11和21的一边的在100μm范围内的不均匀的幅度可以是例如10μm或更大,但是在激光切片时,可以实现例如小于10μm。

在表1中的矩阵中,对由两个方向形成的角度进行分类。例如,在表1中的从顶部起的第四行(行HKa)中指定由半导体层11的晶体结构的晶体取向HKa与其它方向形成的角度,并且在不同的列中分别指定其它方向。例如,对于作为p型MIS晶体管PMa的源极Sa和漏极Da被布置的方向SDa的其它方向,在从右起的第二列(列SDa)中指定角度。在表1中的从顶部起的第四行(行HKa)与从右起的第二列(列SDa)的交点处指定的希腊字母指定了由两个方向形成的角度。在表1中,α表示0度以上且30度以下的角度,β表示60度以上且90度以下的角度,并且γ表示30度以上且60度以下的角度。

[表1]

如表1中的“α”所示的,由半导体层11的晶体取向LKa与半导体层21的晶体取向LKc形成的角度为0度以上且30度以下。如表1中的“α”所示的,由半导体层11的晶体取向LKb与半导体层21的晶体取向LKd形成的角度为0度以上且30度以下。如表1中的“β”所示的,由半导体层11的晶体取向LKa与半导体层21的晶体取向LKd形成的角度为60度以上且90度以下。如表1中的“β”所示的,由半导体层11的晶体取向LKb与半导体层21的晶体取向LKc形成的角度为60度以上且90度以下。

布线结构30可以包括其中布线结构12的电极焊盘31与布线结构22的电极焊盘32结合在一起的结合部分31a、31b、31c和31d。结合部分31a和31b相邻,并且没有结合部分以及电极焊盘31和32位于结合部分31a和31b之间。结合部分31c和31d相邻,并且没有结合部分以及电极焊盘31和32位于结合部分31c和31d之间。结合部分31a和31b沿着晶体取向HKa布置。结合部分31c和31d沿着解理取向HKb布置。连接结合部分31c和31d的线在结合部分31a和31b之间经过。结合部分31a、31b、31c和31d如上所述地相对于晶体取向HKa和HKb布置,使得结合部分31a、31b、31c和31d之间解理的可能性降低。因此,半导体装置APR的强度增加。

类似地,布线结构30可以包括其中布线结构12的电极焊盘31与布线结构22的电极焊盘32结合在一起的结合部分32a、32b、32c和32d。结合部分32a和32b相邻,并且没有结合部分以及电极焊盘31和32位于结合部分32a和32b之间。结合部分32c和32d相邻,并且没有结合部分以及电极焊盘31和32位于结合部分32c和32d之间。结合部分32a和32b沿着晶体取向HKc布置。结合部分32c和32d沿着晶体取向HKd布置。连接结合部分32c和32d的线在结合部分32a和32b之间经过。结合部分32a、32b、32c和32d如上所述地相对于晶体取向HKc和HKd布置,使得结合部分32a、32b、32c和32d之间解理的可能性降低。因此,半导体装置APR的强度增加。

主要有三种方法来制备包括芯片1和2的半导体装置APR。在第一种方法中,将包括芯片1的晶片和包括芯片2的晶片结合在一起,并且将结合的包括芯片1和2的晶片切片。在第二种方法中,将包括芯片1和2中的一个的晶片切片以生产芯片1和2中的这一个,并且将芯片1和2中的这一个与包括芯片1和2中的另一个的晶片结合。此后,将包括芯片1和2中的另一个的晶片切片。在第三种方法中,将包括芯片1的晶片切片以生产成芯片1,并且将包括芯片2的晶片切片以生产芯片2。此后,将芯片1和2结合在一起。在第一种方法中,半导体层11和21的轮廓基本一致。在第二和第三种方法中,可以将半导体层11和21的轮廓设计为基本一致,或者可以容易地将半导体层11和21的轮廓设计为不同。例如,可以将半导体层11的轮廓设计为小于半导体层21的轮廓。在包括芯片1的晶片和包括芯片2的晶片尺寸不同的情况下,第二和第三种方法是有利的。例如,包括芯片2的晶片的直径可以是200mm至300mm,并且包括芯片1的晶片的直径可以小于包括芯片2的晶片的直径,并且例如可以是50mm至200mm。显然,包括芯片1的晶片的直径可以为200mm,并且包括芯片2的晶片的直径可以为300mm。

<第二示例性实施例>

下面将描述可应用于第一示例性实施例的第二示例性实施例。省略了第二示例性实施例中与第一示例性实施例中类似的点的冗余描述。图4A更详细地示出了芯片1的结构。芯片1包括像素区域PX,在像素区域PX中布置了与单元(电场电路10)相对应的像素电路PXC。在像素区域PX的外部形成有用于将键合线与键合焊盘连接的焊盘开口19。在图4A中,示出了以上在第一示例性实施例中描述的晶体取向HKa和HKb(例如,<110>取向)。以上在第一示例性实施例中描述的晶体取向LKa(例如,<100>取向)平行于图4A中的X方向,并且以上在第一示例性实施例中描述的晶体取向LKb(例如,<100>取向)平行于图4中的Y方向。

图4B示出了半导体层11的前表面115上的布局。

在图4B中,将图4A中的半导体层11反转以互换右边和左边。图4B示出了两个像素电路(电路10),每个像素电路包括四个晶体管,这四个晶体管是转移晶体管、放大晶体管、复位晶体管和选择晶体管。可以采用其中多个像素共享像素电路的元件的像素共享结构。

半导体层11包括作为n型MIS晶体管的两个转移晶体管。两个转移晶体管分别包括栅极电极TXa和TXb。包括栅极电极TXa的转移晶体管的源极是光电二极管PDa,并且包括栅极电极TXa的转移晶体管的漏极是浮动扩散部FD。包括栅极电极TXb的转移晶体管的源极是光电二极管PDb,并且包括栅极电极TXb的转移晶体管的漏极是浮动扩散部FD。具体地,两个转移晶体管共享单个浮动扩散部FD。由光电二极管PDa和浮动扩散部FD被布置的方向与半导体层11的晶体取向HKa形成的角度为60度以上且90度以下(在本示例性实施例中为90度)。由光电二极管PDa和浮动扩散部FD被布置的方向与半导体层11的晶体取向HKb形成的角度为0度以上且30度以下(在本示例性实施例中为0度)。由光电二极管PDb和浮动扩散部FD被布置的方向与半导体层11的晶体取向HKa形成的角度为0度以上且30度以下(在本示例性实施例中为0度)。由光电二极管PDb和浮动扩散部FD被布置的方向与半导体层11的晶体取向HKb形成的角度为60度以上且90度以下(在本示例性实施例中为90度)。

半导体层11包括作为n型MIS晶体管的放大晶体管和复位晶体管。放大晶体管包括栅极电极SF,并且复位晶体管包括栅极电极RS。由包括栅极电极SF的放大晶体管的源极和漏极被布置的方向与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。由包括栅极电极RS的复位晶体管的源极和漏极被布置的方向与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。

半导体层11包括作为n型MIS晶体管的选择晶体管。选择晶体管包括栅极电极SL。由包括栅极电极SL的选择晶体管的源极和漏极被布置的方向与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。

由包括栅极电极SF的放大晶体管的源极和漏极被布置的方向(X方向)与包括栅极电极SL的选择晶体管的源极和漏极被布置的方向(Y方向)形成的角度为60度以上且90度以下(在本示例性实施例中为90度)。由包括栅极电极RS的复位晶体管的源极和漏极被布置的方向(X方向)与包括栅极电极SL的选择晶体管的源极和漏极被布置的方向(Y方向)形成的角度为60度以上且90度以下(在本示例性实施例中为90度)。由包括栅极电极SL的选择晶体管的源极和漏极被布置的方向与光电二极管PDb和浮动扩散部FD被布置的方向形成的角度大于30度且小于60度(在本示例性实施例中为45度)。

放大晶体管的栅极电极SF和复位晶体管的源极连接到浮动扩散部FD。电源电位被馈送到复位晶体管的源极和放大晶体管的漏极。放大晶体管的源极连接到选择晶体管的漏极,并且选择晶体管的源极连接到信号输出线。放大晶体管形成源极跟随器电路。

如图4B中所示,半导体层11中的n型MIS晶体管的源极和漏极的布置方向可以包括三个或更多个方向,因为与p型MIS晶体管相比,n型MIS晶体管不太可能受半导体层11的晶体取向HKa、HKb、LKa和LKb的影响。

半导体层11的元件区域由元件分离部分STI限定,该元件分离部分STI包括绝缘体,该绝缘体具有周期性重复的单位图案的图案。图4B示出了对应于两个单位图案及其附近的部分。由单位图案中的元件分离部分STI的轮廓的75%以上与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。在图4B中,由虚线包围的每个部分是元件分离部分STI的轮廓的一部分,并且相对于半导体层11的晶体取向HKa和HKb形成30度以下或60度以上的角度。在半导体层11中的晶体取向HKa和HKb上经常产生微小缺陷,并成为噪声源。因此,期望最小化(小于25%)相对于半导体层11中的晶体取向HKa和HKb形成30度以下或60度以上的角度的部分。

图5A更详细地示出了芯片2的结构。电路基本对称地(线对称或平移对称)布置在芯片2的左半部分和右半部分上。电路基本线对称地布置在芯片2的左半部分的上半部分和下半部分上。电路基本线对称地布置在芯片2的右半部分的上半部分和下半部分上。在图5A中,示出了以上在第一示例性实施例中描述的晶体取向HKc和HKd(例如,<110>取向)。以上在第一示例性实施例中描述的晶体取向LKc(例如,<100>取向)平行于图5A中的X方向,并且以上在第一示例性实施例中描述的晶体取向LKd(例如,<100>取向)平行于图5A中的Y方向。

芯片2包括多个模拟/数字(AD)转换区域(图5A中的“ADC阵列”)522,其中模拟/数字转换器(ADC)521布置在多行和多列中。具体地,AD转换区域522也布置在多行和多列中。对应于每个AD转换区域522设置缓冲存储器(图5A中的“缓冲存储器”)525。每个AD转换区域522的ADC 521经由图5A中的传输线(未示出)连接到对应的缓冲存储器525。此外,芯片2包括垂直扫描电路524(图5A中的“VSCAN”),该垂直扫描电路524逐行顺序地扫描芯片1的像素电路。

芯片2包括数字信号处理电路(图5A中的“DFE”)(以下称为“DFE”)528。每个DFE528对从缓冲存储器525输出的数字信号执行各种类型的处理(降噪处理,诸如增益校正和偏移校正之类的各种类型的校正)。芯片2包括多个DFE 528。一个DFE 528处理从多个缓冲存储器525输出的数字信号。ADC 521通过比较斜坡信号与基于光电转换部产生的信号的信号来执行斜坡信号比较型AD转换。芯片2包括产生斜坡信号的斜坡信号产生部535(图5A中的“斜坡发生器”)。芯片2包括定时发生器(图5A中的“TG”)(以下称为“TG”)530和计数器(图5A中的“计数器”)531。TG 530产生各种控制信号。计数器531产生用于斜坡信号比较型AD转换的格雷码计数信号。芯片2包括数据接口部(图5A中的“数据I/F”)(以下称为“IF部”)535,该数据接口部将由DFE 528处理的信号输出到图像捕获装置的外部。

图5B示出了芯片2的一部分中的半导体层21的前表面215上的布局的示例。半导体层21包括交替地布置的多个p型阱PW和多个n型阱NW。多个p型阱PW中的每一个包括多个n型MIS晶体管NM。多个n型阱NW中的每一个包括多个p型MIS晶体管PM。每个n型MIS晶体管NM包括n型源极101、漏极102和栅极电极103。每个p型MIS晶体管PM包括p型源极106、漏极107和栅极电极108。源极101和106经由导线104连接,漏极102和107经由导线105连接,并且栅极电极103和108经由导线109连接。这形成了CMOS开关电路,其中与导线109连接的节点是输入节点,并且与导线104/105连接的节点是输出节点。可替换地,可以采用以下电路配置:经由导线连接源极101和107,经由导线连接漏极102和106,以及经由导线109连接栅极电极103和108。

在图5B中,用Wn表示n型MIS晶体管NM的沟道宽度,并且用Ln表示n型MIS晶体管NM的沟道长度。此外,在图5B中,用Wp表示p型MIS晶体管PM的沟道宽度,并且用Lp表示p型MIS晶体管PM的沟道长度。如图5B中所示,由沟道长度Ln和Lp的方向(X方向)与晶体取向HKc和HKd形成的角度大于30度且小于60度(在本示例性实施例中为45度)。类似地,由沟道宽度Wn和Wp的方向(Y方向)与半导体层21的晶体取向HKc和HKd形成的角度大于30度且小于60度(在本示例性实施例中为45度)。如上所述,由沟道长度Ln和Lp的方向(X方向)与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。此外,由沟道宽度Wn和Wp的方向(Y方向)与半导体层11的晶体取向HKa和HKb形成的角度大于30度且小于60度(在本示例性实施例中为45度)。

p型MIS晶体管PM的沟道宽度Wp大于n型MIS晶体管NM的沟道宽度Wn。n型MIS晶体管NM的沟道宽度Wn大于n型MIS晶体管NM的沟道长度Ln。p型MIS晶体管PM的沟道宽度Wp大于p型MIS晶体管PM的沟道长度Lp。n型MIS晶体管NM的沟道长度Ln与p型MIS晶体管PM的沟道长度Lp之间的差小于n型MIS晶体管NM的沟道宽度Wn与p型MIS晶体管PM的沟道宽度Wp之间的差(|Ln-Lp|<|Wn-Wp|)。

半导体层21的主要成分可以是硅。包含硅作为主要成分的半导体层21的前表面215可以包括硅化钴区域和/或硅化镍区域。通过这样的硅化物区域,半导体层21的晶体管的接触电阻减小。此外,包含硅作为主要成分的半导体层21可以包括包含锗和/或铟的区域。通过这样的包含锗和/或铟的区域,可以调节晶体管特性。

<第三示例性实施例>

下面将描述可应用于第一示例性实施例和/或第二示例性实施例的第三示例性实施例。省略对第三示例性实施例的与第一示例性实施例和/或第二示例性实施例中类似的点的冗余描述。图6A和图6B是根据第三示例性实施例的示意图。芯片1与芯片2如图1A中那样重叠。芯片2的轮廓大于芯片1的轮廓。芯片1(半导体层11)的轮廓由与半导体层11的后表面116共用一侧的侧表面117限定。芯片2(半导体层21)的轮廓由与半导体层21的后表面216共用一侧的侧表面217限定。芯片1的侧表面117与作为芯片2的主表面的后表面216重叠。前述结构通过上述用于制备包括芯片1和2的半导体装置APR的第二或第三种方法来实现。

芯片1的半导体层11可以是化合物半导体层。化合物半导体层可以用作光接收层或光发射层。例如,作为芯片1的半导体层11的化合物半导体层可以是作为接收红外线的红外传感器的半导体装置APR的光接收层。在这种情况下,芯片2可以是用于从半导体层11读取信号的只读集成电路(ROIC)。例如,作为芯片1的半导体层11的化合物半导体层可以是在诸如激光光源或发光二极管(LED)之类的半导体装置APR中发射具有单个峰值波长的光的光发射层。在芯片1的半导体层11是化合物半导体层的情况下,芯片2的半导体层21不一定是化合物半导体层,并且可以由诸如硅或锗之类的IV族半导体构成,并且在本示例性实施例中,半导体层21可以是硅层。

作为化合物半导体层的半导体层11可以由例如III-V族半导体或II-VI族半导体构成,并且可以是二元混合晶体、三元混合晶体或四元混合晶体。晶体取向与杨氏模量之间的上述关系适用于诸如砷化镓(GaAs)之类的III-V族半导体。具体地,III-V族半导体在沿着<110>取向的方向上的杨氏模量高于III-V族半导体在沿着<100>取向的方向上的杨氏模量。III-V族半导体在沿着<111>取向的方向上的杨氏模量高于III-V族半导体在沿着<110>取向的方向上的杨氏模量。例如,砷化镓层在平行于<100>取向的方向上的杨氏模量约为85GPa(80GPa至90GPa)。砷化镓层在平行于<110>取向的方向上的杨氏模量约为122GPa(117GPa至127GPa)。砷化镓层在平行于<111>取向的方向上的杨氏模量约为142GPa(137GPa至147GPa)。在<100>和<110>取向之间的方向上的杨氏模量是在平行于<100>取向的方向上的杨氏模量与在平行于<110>取向的方向上的杨氏模量之间的值。在<110>和<111>取向之间的方向上的杨氏模量是在平行于<110>取向的方向上的杨氏模量与在平行于<111>取向的方向上的杨氏模量之间的值。

半导体层11可以包括多个半导体区域。半导体层11的多个半导体区域(例如,InGaAs区域和InP区域)可以形成量子阱结构。例如,半导体层11可以具有包括InGaAs区域和InP区域的量子阱结构。半导体层11可以具有包括InGaAs区域和GaAsSb区域的量子阱结构,或者可以具有包括GaInNAs区域和GaAsSb区域的量子阱结构。半导体层11可以具有包括InAs区域和GaSb区域的量子阱结构,或者可以具有包括InAsSb区域和InGaSb区域的量子阱结构。通过使用激光将晶片切片成芯片1,将诸如化合物半导体之类的难以切割的材料切片成芯片,而不会分层或碎裂。

芯片1和2通过在结合表面33处的混合结合而结合在一起。芯片1和2可以使用凸块结合在一起,但是混合结合非常牢固,并且芯片1和2之间的应力相互作用经常变得过多。因此,在采用混合结合的情况下,如上所述,期望设定半导体层11的晶体取向HKa、HKb、LKa和LKb。芯片1和2布置在基板9上。芯片2包括电极25,并且基板9包括电极8。电极25和8经由键合线6连接。用于控制芯片2的集成电路部件、用于处理从芯片2输出的信号的集成电路部件、诸如电容器和电阻器之类的无源部件以及诸如晶体管和二极管之类的有源部件可以布置在基板9上。为了防止半导体层11破裂,期望基板9不是柔性基板而是刚性基板。基板9可以是陶瓷基板或诸如环氧基板(玻璃环氧基板)或聚酰亚胺基板之类的树脂基板。

<第四示例性实施例>

下面将描述可应用于第一至第三示例性实施例的第四示例性实施例。省略对第四示例性实施例的与第一至第三示例性实施例中类似的点的冗余描述。下面将详细描述图1B中所示的设备EQP。半导体装置APR除了堆叠有芯片1和2的半导体器件IC之外还可以包括容纳半导体器件IC的封装体PKG。封装体PKG可以包括基材、诸如玻璃之类的盖以及诸如键合线和凸块之类的连接构件。半导体器件IC固定到基材。覆盖材料面对半导体器件IC。连接构件将基材上的端子连接到半导体器件IC上的端子。

设备EQP还可以包括光学装置OPT、控制装置CTRL、处理装置PRCS、显示装置DSPL和存储装置MMRY中的至少一个。光学装置OPT在用作光电转换装置的半导体装置APR上形成图像,并且例如是透镜、快门和反射镜。控制装置CTRL控制半导体装置APR,并且例如是诸如专用集成电路(ASIC)之类的半导体器件。处理装置PRCS处理从半导体装置APR输出的信号,并且形成模拟前端(AFE)或数字前端(DFE)。处理装置PRCS是诸如中央处理部(CPU)或ASIC之类的半导体器件。显示装置DSPL是显示由半导体装置APR获取的信息(图像)的电致发光(EL)显示装置或液晶显示装置。存储装置MMRY是存储由半导体装置APR获取的信息(图像)的诸如磁性器件之类的半导体器件。存储装置MMRY是诸如静态随机存取存储器(SRAM)或动态随机存取存储器(DRAM)之类的易失性存储器或者诸如闪速存储器或硬盘驱动器之类的非易失性存储器。机械装置MCHN包括诸如马达或引擎之类的移动部或驱动部。设备EQP在显示装置DSPL上显示从半导体装置APR输出的信号,并且经由设备EQP的通信装置(未示出)从外部传输信号。因此,设备EQP除了半导体装置APR的存储电路部和计算电路部之外还期望地包括存储装置MMRY和处理装置PRCS。

图1B中所示的设备EQP可以是具有成像功能的电子设备,诸如信息终端(例如,智能手机、可穿戴终端)或相机(例如,可互换镜头相机、紧凑型相机、视频相机、监控相机)。相机的机械装置MCHN驱动光学装置OPT的部件以进行变焦、聚焦和快门操作。此外,设备EQP可以是诸如车辆、轮船或飞机之类的运输设备(移动物体)。运输设备的机械装置MCHN用作移动装置。作为运输设备的设备EQP适合于运输半导体装置APR并利用成像功能来支持和/或自动驾驶(转向)。用于支持和/或自动驾驶(转向)的处理装置PRCS执行处理,以基于由半导体装置APR获取的信息,使机械装置MCHN作为移动装置进行操作。

根据本示例性实施例的半导体装置APR为其设计者、制造商、卖方、购买者和/或用户提供了巨大的价值。因此,如果将半导体装置APR安装在设备EQP上,则设备EQP的价值增加。因此,从在制造和销售设备EQP中增加设备EQP的价值的观点来看,将设备EQP安装在根据本示例性实施例的半导体装置APR上是有利的。

本发明不限于上述示例性实施例,并且各种修改是可能的。例如,将示例性实施例的配置的一部分添加到另一示例性实施例的修改以及将示例性实施例的配置的一部分替换为另一示例性实施例的一部分的修改也是本发明的示例性实施例。本说明书的公开不限于本说明书中描述的内容,并且涵盖可以从本说明书和所附于本说明书的附图中理解的所有要点。此外,本说明书的公开涵盖本说明书中描述的每个概念的补充。具体地,例如,如果本说明书包括描述“A大于B”,则应当理解,即使本说明书不包括描述“A不大于B”,本说明书也公开了“A不大于B”,因为描述“A大于B”的公开是基于假设考虑了“A不大于B”的情况。

尽管已经参考示例性实施例描述了本发明,但是应当理解,本发明不限于所公开的示例性实施例。所附权利要求的范围应被赋予最宽泛的解释,以涵盖所有这样的修改以及等同的结构和功能。

- 半导体封装件、半导体装置、半导体封装件搭载设备、以及半导体装置搭载设备

- 半导体装置、芯片状半导体元件、配备有半导体装置的电子设备以及制造半导体装置的方法