集成芯片及形成晶体管装置的方法

文献发布时间:2023-06-19 11:27:38

技术领域

本发明的实施例是有关于一种集成芯片及形成晶体管装置的方法。

背景技术

功率金属氧化物半导体场效晶体管(power metal-oxide-semiconductor field-effect transistors,MOSFETs)是被设计成应对高功率电平(例如,高电压和/或高电流)的MOSFETs。功率MOSFETs应用于显示器驱动器、功率转换器、电动机控制器、车辆功率装置等中。一种类型的功率MOSFET是侧向扩散式金属氧化物半导体(laterally-diffused metal-oxide semiconductor,LDMOS)晶体管。LDMOS晶体管在高频率下具有高增益、高功率输出及高效率,因此LDMOS晶体管通常与微波及射频(radio frequency,RF)功率放大器一起使用。

发明内容

本发明的实施例提供一种集成芯片,包括:栅极介电层,配置在衬底之上以及源极区与漏极区之间;栅极电极,配置在所述栅极介电层之上;场板介电层,配置在所述衬底之上以及所述栅极介电层与所述漏极区之间;以及场板,配置在所述场板介电层之上,其中所述场板介电层与所述栅极介电层间隔开。

本发明的实施例提供一种集成芯片,包括:栅极电极,配置在第一源极/漏极区与第二源极/漏极区之间的衬底之上;场板介电层,配置在所述衬底之上以及所述栅极电极与所述第二源极/漏极区之间;场板,配置在所述场板介电层的中心部分之上;以及间隔件结构,配置在所述场板介电层的外侧部分之上且环绕所述场板的外侧壁。

本发明的实施例提供一种形成晶体管装置的方法,包括:在衬底上或所述衬底内形成与漏极区隔开的源极区;在所述衬底之上形成连续的场板介电层;在所述连续的场板介电层之上形成连续的场板层;执行第一移除工艺,以移除所述连续的场板层的外侧部分来形成场板,并移除所述连续的场板介电层的外侧部分;在所述场板的外侧壁上及所述衬底之上形成间隔件结构;在所述衬底及所述场板之上形成连续的栅极介电层;在所述连续的栅极介电层之上形成连续的栅极电极层;以及执行第二移除工艺,以移除所述连续的栅极电极层的外侧部分及所述连续的栅极介电层的外侧部分,从而在与所述场板及所述连续的场板介电层间隔开的栅极介电层之上形成栅极电极。

附图说明

结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的尺寸。

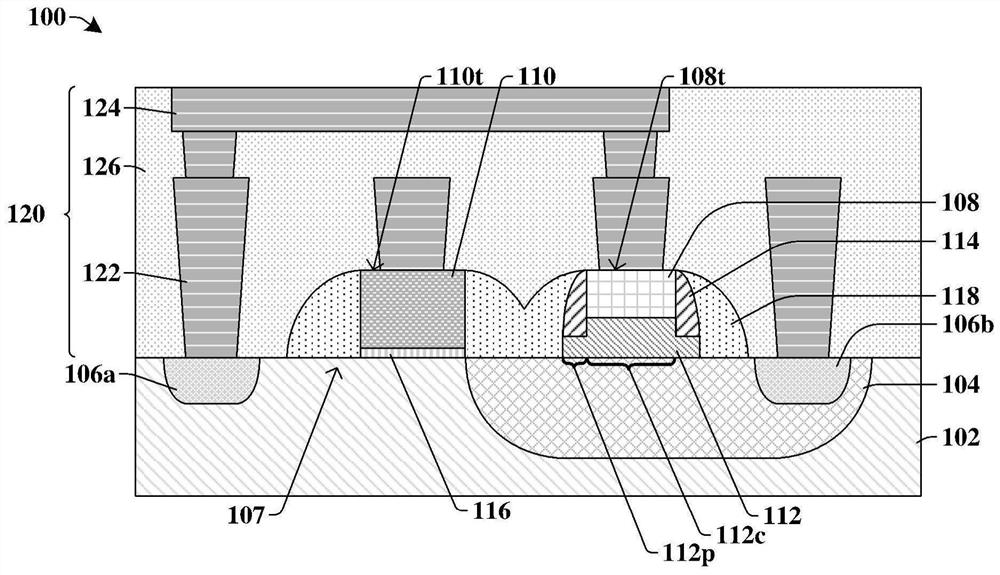

图1说明侧向扩散式金属氧化物半导体(LDMOS)晶体管的一些实施例的剖视图,所述LDMOS晶体管具有配置在场板介电层之上且在侧向上由间隔件结构环绕的场板。

图2说明图1所示LDMOS晶体管的一些替代实施例的剖视图,其中场板具有低于栅极电极的最顶表面的最顶表面。

图3说明LDMOS晶体管的另一些其他实施例的剖视图,所述LDMOS晶体管包括比栅极介电层厚且与栅极介电层隔开的场板介电层。

图4说明III/V族功率装置的一些实施例的剖视图,所述III/V族功率装置具有配置在场板介电层之上且在侧向上由间隔件结构环绕的场板。

图5到图21说明形成高功率装置的方法的一些实施例的剖视图,所述方法是先形成场板,再在侧向上在所述场板旁边形成栅极电极以减小场板与栅极电极之间的间隔。

图22说明与图5到图21中所说明的方法对应的形成高功率装置的方法的一些实施例的流程图。

[符号的说明]

100、200、300、400、500、600、700、800、900、1000、1100、1200、1300、1400、1500、1600、1700、1800、1900、2000、2100:剖视图

102:衬底

104:低掺杂漂移区

106a:第一源极/漏极区

106b:第二源极/漏极区

107:沟道区

108:场板

108t、110t:最顶表面

110:栅极电极

112:场板介电层

112c、902c:中心部分

112p、902p:外侧部分

114:间隔件结构

116:栅极介电层

118:介电间隔件层

120:内连线结构

122:内连线通孔

124:内连线配线

126:内连线介电结构

202:硅化物层

402:沟道层

404:有效层

406:隔离结构

408:钝化层

410a:第一源极/漏极触点

410b:第二源极/漏极触点

602:第一掩蔽结构

604:离子植入工艺

702:连续的场板介电层

704:连续的场板层

802:第二掩蔽结构

1002:连续的间隔件层

1302:连续的栅极介电层

1402:连续的栅极层

1404:第三掩蔽结构

1702:共形介电层

2200:方法

2202、2204、2206、2208、2210、2212、2214、2216:动作

d

d

d

d

d

d

d

具体实施方式

以下公开内容提供用于实施所提供主题的不同特征的许多不同的实施例或例子。以下阐述组件及配置的具体例子以简化本公开。当然,这些仅为例子而非旨在进行限制。举例来说,以下说明中将第一特征形成在第二特征之上或第二特征上可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成有附加特征从而使得所述第一特征与所述第二特征可不直接接触的实施例。另外,本公开可能在各种例子中重复使用参考编号和/或字母。这种重复使用是出于简洁及清晰的目的,而非自身指示所论述的各种实施例和/或配置之间的关系。

此外,为易于说明,本文中可能使用例如“在...下方(beneath)”、“在...下面(below)”、“下部的(lower)”、“在...上方(above)”、“上部的(upper)”等空间相对性用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的定向外还囊括装置在使用或操作中的不同定向。设备可具有其他定向(旋转90度或处于其他定向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

侧向扩散式金属氧化物半导体(LDMOS)晶体管是在放大器(例如,微波功率放大器、音频功率放大器及射频(RF)放大器)中常使用的高电压装置。举例来说,在一些RF放大器中,LDMOS晶体管被耦合成集成到RF放大器中以辅助进行包络跟踪(envelopetracking),其中连续地操控供应到RF放大器的功率以提高RF放大器的效率。在一些实例中,LDMOS晶体管具有场板,所述场板是配置在漂移区之上以通过操控栅极电极所产生的电场(例如,减小峰值电场)来增强装置性能的导电元件。通过操控由栅极电极产生的电场,LDMOS晶体管可实现较高的击穿电压(breakdown voltage)。

在一些实施例中,在LDMOS晶体管中场板配置在漏极区与栅极电极之间。为减小栅极电极与漏极区之间的电容,将场板与栅极电极间隔开,且场板可电耦合到源极区。通过减小栅极电极与漏极区之间的电容,能减小接通LDMOS晶体管的电阻,且因此减小LDMOS在接通与关断切换期间的功率损耗。

在一些实例中,为形成包括场板及栅极电极的LDMOS晶体管,在衬底之上形成栅极介电层及场板介电层。场板介电层的厚度可大于栅极介电层的厚度。然后,可通过以下方式同时形成场板及栅极电极:在栅极介电层及场板介电层之上沉积电极层,且移除电极层的一些部分以形成场板,所述场板配置在场板介电层之上且与配置在栅极介电层之上的栅极电极间隔开。然而,在这些实施例中,栅极介电层的宽度及场板介电层的宽度可以是大的,以提供较大的处理窗口,需要所述较大的处理窗口以确保场板直接形成在场板介电层之上且栅极电极直接形成在栅极介电层之上。

本公开的各种实施例涉及通过先形成场板再形成栅极电极来减小高功率装置(例如,LDMOS晶体管)中的场板与栅极电极之间的间隔。在一些实施例中,可在衬底之上形成连续的场板介电层,且然后,在所述场板介电层之上形成场板层。可使用间隔件结构将连续的场板介电层与场板层一起图案化以在场板介电层之上形成场板。在这些实施例中,由于不再需要将场板着落在场板介电层上的land on处理窗口,因此场板介电层的宽度减小。因此,高功率装置(例如,LDMOS装置)的总面积在衬底上可减小约15%到20%,从而在不牺牲高功率装置(例如,LDMOS装置)的可靠性的情况下增大装置密度。

图1说明LDMOS晶体管的一些实施例的剖视图100,LDMOS晶体管包括与栅极介电层完全间隔开的场板介电层。

图1的剖视图100包括配置在衬底102内的第一源极/漏极区106a及第二源极/漏极区106b。在一些其他实施例中,第一源极/漏极区106a及第二源极/漏极区106b可配置在衬底102之上。在一些实施例中,第一源极/漏极区106a及第二源极/漏极区106b可具有第一掺杂剂浓度的第一掺杂类型(例如,n型)。在一些实施例中,第二源极/漏极区106b也配置在衬底102的低掺杂漂移区(low doped drift region)104内。在这些实施例中,低掺杂漂移区104可以是衬底102的具有第二掺杂剂浓度的第一掺杂类型(例如,n型)的一部分,所述第二掺杂剂浓度小于所述第一掺杂剂浓度。在一些实施例中,第一源极/漏极区106a与低掺杂漂移区104间隔开,且沟道区107将第一源极/漏极区106a与低掺杂漂移区104隔开。在一些实施例中,第一源极/漏极区106a可对应于源极区,且第二源极/漏极区106b可对应于漏极区。在一些实施例中,衬底102未经掺杂,或者经过掺杂且具有与第一掺杂类型(例如,n型)不同的第二掺杂类型(例如,p型)。

此外,场板108及栅极电极110配置在衬底102之上。场板108与栅极电极110在侧向上隔开。在一些实施例中,场板108直接上覆在低掺杂漂移区104上,且栅极电极110直接上覆在沟道区107上。在一些实施例中,场板108直接配置在场板介电层112之上,且栅极电极110直接配置在栅极介电层116之上。在一些实施例中,栅极介电层116与场板介电层112间隔开且因此不接触场板介电层112。在一些实施例中,场板介电层112包括中心部分112c及环绕中心部分112c的外侧部分112p。在一些实施例中,场板介电层112的中心部分112c比场板介电层112的外侧部分112p厚。此外,在一些实施例中,场板108直接上覆在场板介电层112的中心部分112c上,且不直接上覆在场板介电层112的外侧部分112p上。在一些实施例中,间隔件结构114在侧向上环绕场板108且直接上覆在场板介电层112的外侧部分112p上。在这些实施例中,间隔件结构114可具有低于场板108的最底表面的最底表面。在一些实施例中,间隔件结构114用于在场板介电层112之上形成场板108期间保护场板108,且也用于当在形成场板108之后形成栅极电极110时保护场板108。在一些实施例中,栅极介电层116比场板介电层112的中心部分112c及外侧部分112p两者都薄。场板108将在第二源极/漏极区106b与沟道区107之间的电场分散(distribute)。在这些实施例中,由于场板介电层112具有比栅极介电层116高的击穿电压,因此场板介电层112可比栅极介电层116厚。

在一些实施例中,场板108的最顶表面108t与栅极电极110的最顶表面110t实质上共面。在一些实施例中,介电间隔件层118可环绕栅极电极110及场板108。在一些实施例中,间隔件结构114可直接配置在介电间隔件层118与场板108之间。在一些实施例中,介电间隔件层118可保护场板108的外侧壁及栅极电极110的外侧壁,且提供场板108与栅极电极110之间的电隔离。

在一些实施例中,在衬底102、场板108及栅极电极110之上形成有内连线结构120。在这些实施例中,内连线结构120包括嵌入在内连线介电结构126内的内连线通孔122及内连线配线124。在一些实施例中,为减小栅极电极110与第二源极/漏极区106b之间的电容,通过内连线通孔122及内连线配线124将场板108电耦合到第一源极/漏极区106a。

在一些实施例中,场板108是在栅极电极110之前形成,且场板108与场板介电层112同时被图案化。此外,在一些实施例中,栅极电极110与栅极介电层116同时形成。在这些实施例中,场板108与栅极电极110之间的间隔更为可控制的,且因此可减小场板108与栅极电极110之间的距离以在不牺牲电性性能的情况下增大LDMOS晶体管的装置密度。

图2说明LDMOS晶体管的一些替代实施例的剖视图200。

在一些实施例中,硅化物层202可直接形成在第一源极/漏极区106a、第二源极/漏极区106b、场板108和/或栅极电极110上。在一些实施例中,硅化物层202可包含例如硅化钴、硅化钛、硅化镍或一些其他适合的金属硅化物材料。在这些实施例中,硅化物层202可辅助将内连线通孔122耦合到第一源极/漏极区106a、第二源极/漏极区106b、场板108和/或栅极电极110。

此外,在一些实施例中,栅极电极110的最顶表面110t可配置在场板108的最顶表面108t上方。在这些实施例中,可在制造期间省略对栅极电极110和/或场板108进行的平坦化步骤以降低制造成本及改善时间效率,但当栅极电极110的最顶表面110t与场板108的最顶表面108t不实质上共面时,在场板108及栅极电极110上同时形成内连线通孔122可颇具挑战性。在一些实施例中,栅极电极110的厚度及场板108的厚度可各自处于例如近似100埃与近似2000埃之间的范围中。在一些实施例中,栅极介电层116及场板介电层112可各自具有处于例如近似10埃与近似1000埃之间的范围中的厚度。

在一些实施例中,场板介电层112的外侧部分112p具有等于第一距离d

图3说明LDMOS晶体管的另一些其他实施例的剖视图300,所述LDMOS晶体管包括配置在场板介电层之上且由间隔件结构环绕的场板。

在一些实施例中,场板介电层112横贯其宽度且具有实质上均匀的厚度。因此,在一些实施例中,场板介电层112可不具有外侧部分(图2所示112p)。在这些实施例中,间隔件结构114的底表面及场板介电层112的底表面可直接接触衬底102。

在一些实施例中,栅极介电层116与场板介电层112包含相同的材料,而在其他实施例中,栅极介电层116与场板介电层112可包含不同的材料。类似地,在一些实施例中,间隔件结构114包含与场板介电层112相同的材料,而在其他实施例中,间隔件结构114包含与场板介电层112不同的材料。在另一些其他实施例中,间隔件结构114可包括多个材料层。在一些实施例中,栅极介电层116、场板介电层112及间隔件结构114可例如包含以下材料中的一种或多种:氧化物(例如,二氧化硅)、氮氧化硅、氮化硅等。

此外,由于栅极电极110与场板108是分别形成的,因此在一些实施例中,栅极电极110与场板108可包含不同的材料。在一些其他实施例中,栅极电极110包含与场板108相同的材料。在一些实施例中,场板108及栅极电极110可包含以下材料中的一种或多种:半导体材料(例如,多晶硅(polysilicon)、非晶硅(amorphous silicon))、金属(例如,氮化钛、钛、氮化钽、钽、铝、钨)或一些其他适合的导电材料。

在一些实施例中,介电间隔件层118和/或内连线介电结构126可包含例如氮化物(例如,氮化硅、氮氧化硅)、碳化物(例如,碳化硅)、氧化物(例如,氧化硅)、硼硅酸盐玻璃(borosilicate glass,BSG)、磷硅酸盐玻璃(phosphoric silicate glass,PSG)、硼磷硅酸盐玻璃(borophosphosilicate glass,BPSG)、低介电常数氧化物(例如,掺杂碳的氧化物、SiCOH)等。此外,在一些实施例中,内连线通孔122及内连线配线124可包含导电材料,例如(举例来说)钛、钽、铝、钨、铜或一些其他适合的导电材料。

图4说明GaN或III/V族功率装置的一些实施例的剖视图400,所述GaN或III/V族功率装置具有配置在场板介电层之上且在侧向上由间隔件结构环绕的场板。

在一些实施例中,场板108及栅极电极110形成在III/V族半导体装置的有效层404之上。在这些实施例中,沟道层402可配置在衬底102上及衬底102与有效层404之间。在一些实施例中,沟道层402包含二元III/V族半导体(例如,第一III族氮化物材料,如氮化镓或砷化镓),且有效层404包含三元III/V族半导体(例如,第二III族氮化物材料,如氮化铝镓或砷化铝镓)。在一些实施例中,第一源极/漏极触点410a配置在有效层404之上,且第二源极/漏极触点410b配置在有效层404之上。在一些实施例中,第一源极/漏极触点410a及第二源极/漏极触点410b包含导电材料,例如钛、钽、铝等。在一些实施例中,第一源极/漏极触点410a、第二源极/漏极触点410b、栅极电极110及场板108在侧向上由钝化层408环绕。此外,在一些实施例中,隔离结构406可环绕有效层404的外侧壁及沟道层402的上部部分。

在III/V族功率装置的一些实施例中,场板108配置在场板介电层112之上且由间隔件结构114环绕,且栅极电极110配置在栅极介电层116之上且与场板108间隔开。应了解,配置在场板介电层112之上且由在栅极电极110之前形成的间隔件结构114环绕的场板108也可用于除III/V族功率装置或LDMOS晶体管之外的装置中,且此类其他实施例也处于本公开的范围内。

在III/V族功率装置的操作期间,在有效层404与沟道层402之间的界面处形成用作沟道区107的异质结。电流流过沟道区107,且可对场板108加以控制以操控沟道区107中的电场以减小III/V族功率装置的击穿电压。由于场板108是在栅极电极110之前形成且由于场板108与场板介电层112同时形成,因此可将场板108配置成更靠近栅极电极110及第二源极/漏极触点410b,从而在不牺牲总体III/V族功率装置的性能的情况下增大装置密度。

图5到图21说明在衬底之上形成高功率装置(例如,LDMOS晶体管)的方法的一些实施例的剖视图500到2100,其中先形成场板再形成栅极电极以减小高功率装置的大小。尽管图5到图21是关于方法加以阐述,但应了解,图5到图21中所公开的结构并不仅限于此方法,而是可作为独立于方法的结构单独存在。

如图5的剖视图500中所示,提供衬底102。在各种实施例中,衬底102可包括任何类型的半导体本体(例如,硅/互补金属氧化物半导体(complementary metal oxidesemiconductor,CMOS)块、锗化硅(SiGe)、绝缘体上硅(silicon on insulator,SOI)等),例如半导体晶片或位于晶片上的一个或多个管芯、以及任何其他类型的半导体和/或形成在半导体上和/或与半导体相关联的外延层。

如图6的剖视图600中所示,在一些实施例中,在衬底102之上形成第一掩蔽结构602,执行离子植入工艺604以对衬底102进行掺杂且在衬底102内形成低掺杂漂移区104。在一些实施例中,可使用光刻工艺及移除(例如,刻蚀)工艺形成第一掩蔽结构602。在一些实施例中,第一掩蔽结构602包含光刻胶或硬掩模材料。在一些实施例中,低掺杂漂移区104可具有第一掺杂类型(例如,n型)。此外,在一些实施例中,衬底102可未经掺杂,或具有与第一掺杂类型(例如,n型)不同的第二掺杂类型(例如,p型)。在其他实施例中,例如(举例来说)当将形成的装置是图4中所说明的III/V族功率装置时,可省略低掺杂漂移区104的形成。

如图7的剖视图700中所示,在一些实施例中,在衬底102之上形成连续的场板介电层702。此外,在一些实施例中,在所述连续的场板介电层702之上形成连续的场板层704。在一些实施例中,可通过热氧化工艺、原位蒸汽产生(in-situ steam generation,ISSG)氧化物工艺或一些其他沉积工艺(例如,物理气相沉积(physical vapor deposition,PVD)、化学气相沉积(chemical vapor deposition,CVD)、原子层沉积(atomic layer deposition,ALD)等)形成连续的场板介电层702。在一些实施例中,连续的场板介电层702可包含例如氧化物(例如,二氧化硅)、氮氧化硅、氮化硅等。在一些实施例中,连续的场板介电层702可具有处于例如近似10埃与近似1000埃之间的范围中的厚度。

在一些实施例中,连续的场板层704可包含例如半导体材料(例如,多晶硅、非晶硅)、金属(例如,氮化钛、钛、氮化钽、钽、铝、钨)或一些其他适合的导电材料。此外,在一些实施例中,连续的场板层704可通过沉积工艺(例如PVD、CVD、ALD、溅镀等)形成。在一些实施例中,连续的场板层704可具有处于例如近似100埃与近似2000埃之间的范围中的厚度。

如图8的剖视图800中所示,在一些实施例中,在连续的场板层704之上形成第二掩蔽结构802。在一些实施例中,第二掩蔽结构802直接上覆在低掺杂漂移区104上。在一些实施例中,第二掩蔽结构802可使用光刻工艺及移除(例如,刻蚀)工艺来形成,且包含光刻胶或硬掩模材料。在一些实施例中,第二掩蔽结构802可具有等于第六距离d

如图9的剖视图900中所示,在一些实施例中,执行移除工艺以根据第二掩蔽结构802移除连续的场板层(图7所示704)的外侧部分,以在衬底102之上形成场板108。在一些实施例中,在进行用于形成场板108的移除工艺之后,连续的场板介电层702包括比中心部分902c薄的外侧部分902p,其中连续的场板介电层702的中心部分902c直接且完全位于第二掩蔽结构802之下。在这些实施例中,移除工艺也移除连续的场板介电层702的未被第二掩蔽结构802覆盖的上部部分,但并不完全移除未被第二掩蔽结构802覆盖的连续的场板介电层702。因此,在进行用于形成场板108的移除工艺之后,连续的场板介电层702的外侧部分902p完全覆盖衬底102。举例来说,连续的场板介电层702的外侧部分902p可保护衬底102不受后续的处理步骤(例如,干式刻蚀/等离子体刻蚀)影响。

在一些其他实施例中,用于形成场板108的移除工艺可完全移除连续的场板介电层702的未被第二掩蔽结构802覆盖的部分。在此类其他实施例中,衬底102可被后续的处理步骤(例如(举例来说),干式刻蚀/等离子体刻蚀)损坏。

在一些实施例中,移除工艺可以是或包括干式刻蚀工艺。在一些实施例中,移除工艺可包括用于移除连续的场板层(图8所示704)的一些部分的第一干式刻蚀剂及用于移除连续的场板介电层702的一些部分的第二干式刻蚀剂。在一些实施例中,第二干式刻蚀剂不同于第一干式刻蚀剂,而在其他实施例中,将相同的干式刻蚀剂用于移除工艺。在一些实施例中,第一干式刻蚀剂可以是或包括例如CF

如图10的剖视图1000中所示,在一些实施例中,在衬底102之上形成连续的间隔件层1002。在一些实施例中,在形成连续的间隔件层1002之前,可通过例如湿式化学刻蚀剂移除第二掩蔽结构(图9所示802)。在其他实施例中,第二掩蔽结构(图9所示802)可保留在场板108上,且可在第二掩蔽结构(图9所示802)之上形成连续的间隔件层1002。然而,在一些实施例中,可在连续的场板介电层702之上及在场板108之上形成连续的间隔件层1002。

在一些实施例中,可通过热氧化工艺和/或沉积工艺(例如PVD、CVD、ALD、溅镀等)形成连续的间隔件层1002。在一些实施例中,连续的间隔件层1002可包含例如氧化物(例如,二氧化硅)、氮氧化硅、氮化硅等。在一些实施例中,连续的间隔件层1002可包括前述材料的多个层。在一些实施例中,连续的间隔件层1002可具有处于例如近似5纳米与近似15纳米之间的范围中的厚度。

如图11的剖视图1100中所示,在一些实施例中,执行移除工艺以移除连续的间隔件层(图10所示1002)的实质上水平部分以形成环绕场板108的间隔件结构114。在一些实施例中,间隔件结构114配置在连续的场板介电层702的外侧部分902p上,且与场板108配置在距衬底102相同的高度处。在一些实施例中,间隔件结构114具有实质上弯曲的外侧壁,而在其他实施例中,间隔件结构114可具有平坦/笔直的侧壁、锯齿状/粗糙的侧壁或其组合。在一些实施例中,间隔件结构114不覆盖场板108的最顶表面108t。在一些实施例中,移除工艺可以是在实质上垂直的方向上进行的干式刻蚀工艺。在这些实施例中,形成间隔件结构114可不需要掩蔽结构。在一些实施例中,图11的移除工艺可包括干式刻蚀剂,例如(举例来说)CF

在一些实施例中,间隔件结构114与连续的场板介电层702包含相同的材料。在这些实施例中,可基于连续的间隔件层(图10所示1002)的厚度通过预定的刻蚀时间来控制图11的移除工艺。举例来说,在一些实施例中,可在所述预定的刻蚀时间进行图11的移除工艺,以移除连续的间隔件层(图10所示1002)的实质上水平部分,但不移除连续的场板介电层702。在一些其他实施例中,图11的移除工艺可移除连续的场板介电层702中的一些,以使得连续的场板介电层702的厚度减小;然而,在图11的移除工艺之后,连续的场板介电层702仍完全覆盖衬底102以保护衬底102不被图11的移除工艺损坏。

在另一些其他实施例中,可不执行图11的移除工艺达足以完全移除连续的间隔件层(图10所示1002)的实质上水平部分的时长。在此类其他实施例中,在图11的移除工艺之后,连续的间隔件层(图10所示1002)的薄层可仍保留在连续的场板介电层702上。在此类其他实施例中,可例如通过图12的移除工艺移除连续的间隔件层(图10所示1002)的薄层(未示出)。

如图12的剖视图1200中所示,在一些实施例中,执行移除工艺以移除连续的场板介电层(图11所示702)的未被间隔件结构114覆盖的外侧部分(图11所示902p),从而形成配置在场板108及间隔件结构114下面的场板介电层112。在一些其他实施例中,图12的移除工艺也可移除直接配置在连续的场板介电层(图11所示702)的外侧部分(图11所示902p)上的连续的间隔件层(图10所示1002)的任何剩余部分(未示出)。此外,在一些实施例中,如果场板介电层112与间隔件结构114包含相同的材料,则图12的移除工艺可减小间隔件结构114的大小。然而,在这些实施例中,在图12的移除工艺之后,可仍存在间隔件结构114以界定由图12的移除工艺形成的场板介电层112。

在一些实施例中,场板介电层112包括直接配置在间隔件结构114下面的外侧部分112p及由外侧部分112p环绕且直接配置在场板108下面的中心部分112c。在一些实施例中,场板介电层112的中心部分112c比场板介电层112的外侧部分112p厚。在一些实施例中,场板介电层112的外侧部分112p具有等于第一距离d

在一些实施例中,用于形成场板介电层112的移除工艺可以是或包括湿式刻蚀。在一些实施例中,湿式刻蚀可在不损坏衬底102的情况下移除连续的场板介电层(图11所示702)的外侧部分(902p)。在一些实施例中,执行用于形成场板介电层112的移除工艺不需要掩蔽结构。在一些其他实施例中,图12的移除工艺可包括干式刻蚀剂,例如(举例来说)CF

由于场板介电层112是根据场板108及间隔件结构114形成,因此场板介电层112可被视为在自对准工艺中与场板108一起形成。如此,场板介电层112及场板108可具有较小的宽度,从而减小总体LDMOS晶体管的装置密度。

如图13的剖视图1300中所示,在一些实施例中,可在衬底102之上形成连续的栅极介电层1302。在一些实施例中,可通过热氧化工艺和/或沉积工艺(例如PVD、CVD、ALD、溅镀等)形成连续的栅极介电层1302。在一些实施例中,连续的栅极介电层1302可包含例如氧化物(例如,二氧化硅)、氮氧化硅、氮化硅等。在一些实施例中,连续的栅极介电层1302可具有处于例如近似10埃与近似1000埃之间的范围中的厚度。在一些实施例中,连续的栅极介电层1302的厚度可小于场板介电层112的外侧部分112p及中心部分112c的厚度。

如图14的剖视图1400中所示,在一些实施例中,在连续的栅极介电层1302之上形成连续的栅极层1402。在一些实施例中,连续的栅极层1402包含与场板108相同的材料,而在其他实施例中,连续的栅极层1402包含与场板108不同的材料。在一些实施例中,连续的栅极层1402可包含例如半导体材料(例如,多晶硅、非晶硅)、金属(例如,氮化钛、钛、氮化钽、钽、铝、钨)或一些其他适合的导电材料。此外,在一些实施例中,可通过沉积工艺(例如PVD、CVD、ALD、溅镀等)形成连续的栅极层1402。在一些实施例中,连续的栅极层1402可具有处于例如近似100埃与近似2000埃之间的范围中的厚度。

此外,在一些实施例中,在连续的栅极层1402之上形成第三掩蔽结构1404。在一些实施例中,第三掩蔽结构1404可使用光刻工艺及移除(例如,刻蚀)工艺形成且包含光刻胶或硬掩模材料。在一些实施例中,第三掩蔽结构1404可具有等于第七距离d

如图15的剖视图1500中所示,在一些实施例中,执行移除工艺以根据第三掩蔽结构(图14所示1404)移除连续的栅极介电层(图14所示1302)的外侧部分及连续的栅极层(图14所示1402)的外侧部分,以在栅极介电层116之上形成栅极电极110。在一些实施例中,所述移除工艺可以是或包括干式刻蚀工艺。在一些实施例中,图15的移除工艺可包括用于移除连续的栅极层(图14所示1402)的一些部分的第一干式刻蚀剂及用于移除连续的栅极介电层(图14所示1302)的一些部分的第二干式刻蚀剂。在一些实施例中,第二干式刻蚀剂不同于第一干式刻蚀剂,而在其他实施例中,将相同的干式刻蚀剂用于移除工艺。在一些实施例中,第一干式刻蚀剂可以是或包括例如CF

在一些实施例中,栅极电极110可具有位于场板108的最顶表面108t上方、位于场板108的最顶表面108t下面或与场板108的最顶表面108t位于衬底102上方的约相同高度处的最顶表面110t。此外,在一些实施例中,栅极介电层116与场板介电层112完全隔开。在一些实施例中,栅极介电层116配置在距场板介电层112第四距离d

在一些实施例中,移除工艺可以是或包括干式刻蚀工艺。在一些实施例中,移除工艺可包括用于移除连续的场板层(图8所示704)的一些部分的第一干式刻蚀剂及用于移除连续的场板介电层702的一些部分的第二干式刻蚀剂。在一些实施例中,第二干式刻蚀剂不同于第一干式刻蚀剂,而在其他实施例中,将相同的干式刻蚀剂用于移除工艺。在一些实施例中,第一干式刻蚀剂可以是或包括例如CF

在一些实施例中,由于场板108可能经受比栅极电极110高的电压偏压(voltagebias),因此场板介电层112比栅极介电层116厚以增大场板108的击穿电压。

如图16的剖视图1600中所示,在一些实施例中,可执行平坦化工艺(例如,化学机械平坦化(chemical mechanical planarization,CMP))以使得栅极电极110的最顶表面110t与场板108的最顶表面108t实质上共面。平坦化工艺可移除栅极电极110的上部部分、场板108的上部部分和/或间隔件结构114的上部部分。在一些实施例中,由于栅极介电层116比场板介电层112薄,因此尽管栅极电极的最顶表面110t与场板108的最顶表面108t实质上共面,但栅极电极110比场板108厚。当栅极电极110的最顶表面110t与场板108的最顶表面108t实质上共面时,形成内连线通孔(例如,图21所示122)可更可控。然而,在一些实施例中,可省略图16的平坦化工艺。

如图17的剖视图1700中所示,在一些实施例中,可在栅极电极110及场板108之上形成共形介电层1702。在一些实施例中,可通过热氧化工艺和/或沉积工艺(例如PVD、CVD、ALD、溅镀等)形成共形介电层1702。在一些实施例中,共形介电层1702可包含例如氮化物(例如,氮化硅、氮氧化硅)、碳化物(例如,碳化硅)、氧化物(例如,氧化硅)、硼硅酸盐玻璃(BSG)、磷硅酸盐玻璃(PSG)、硼磷硅酸盐玻璃(BPSG)、低介电常数氧化物(例如,掺杂碳的氧化物、SiCOH)等。此外,在一些实施例中,共形介电层1702可包括前述材料的多个层。

如图18的剖视图1800中所示,在一些实施例中,执行移除工艺以移除共形介电层(图17所示1702)的实质上水平部分,以形成在侧向上环绕栅极电极110及间隔件结构114的介电间隔件层118。在一些实施例中,介电间隔件层118为栅极电极110及场板108提供结构保护且提供栅极电极110与场板108之间的电隔离。在一些实施例中,在图18的移除工艺之后,介电间隔件层118可具有实质上弯曲的外侧壁及上表面,而在其他实施例中,举例来说,介电间隔件层118的外侧壁及上表面可为平坦的/倾斜的、锯齿状的/粗糙的或其组合。

在一些实施例中,图18的移除工艺可以是在实质上垂直的方向上进行的干式刻蚀工艺。在这些实施例中,形成介电间隔件层118不需要掩蔽结构。在一些实施例中,图18的移除工艺可包括干式刻蚀剂,例如(举例来说)CF

如图19的剖视图1900中所示,在一些实施例中,执行离子植入工艺以对衬底102的区进行掺杂,以在衬底102中形成第一源极/漏极区106a及第二源极/漏极区106b。在一些其他实施例中,第一源极/漏极区106a及第二源极/漏极区106b可形成在衬底102之上。在一些实施例中,第一源极/漏极区106a及第二源极/漏极区106b可具有第一掺杂类型(例如,n型)且可具有比低掺杂漂移区104的掺杂浓度大的掺杂浓度。在一些实施例中,可在离子植入工艺期间使用掩蔽结构(未示出),以使得在衬底102上的所期望区域中形成第一源极/漏极区106a及第二源极/漏极区106b。在一些实施例中,栅极电极110及场板108配置在第一源极/漏极区106a与第二源极/漏极区106b之间。在一些实施例中,由于第一源极/漏极区106a被配置成相较于距场板108而更靠近栅极电极110,因此第一源极/漏极区106a是源极区;且由于第二源极/漏极区106b被配置成相较于距栅极电极110而更靠近场板108,因此第二源极/漏极区106b是漏极区。

如图20的剖视图2000中所示,在一些实施例中,在第一源极/漏极区106a、第二源极/漏极区106b、场板108和/或栅极电极110之上形成硅化物层202。在一些实施例中,可通过以下方式形成硅化物层202:沉积覆盖第一源极/漏极区106a、第二源极/漏极区106b、场板108和/或栅极电极110的过渡金属层,且随后对过渡金属层进行加热以使其与第一源极/漏极区106a、第二源极/漏极区106b、场板108和/或栅极电极110的半导体材料发生反应。因此,在一些实施例中,硅化物层202可包含硅化镍、硅化钛、硅化钴、硅化铂、硅化钨或一些其他金属半导体材料。在一些其他实施例中,如果栅极电极110和/或场板108包含金属而不包含半导体材料,则不在栅极电极110和/或场板108上形成硅化物层。

如图21的剖视图2100中所示,在一些实施例中,在衬底102之上形成内连线结构120。在一些实施例中,内连线结构120包括耦合到第一源极/漏极区106a、第二源极/漏极区106b、栅极电极110和/或场板108的内连线通孔122及内连线配线124的网络(network)。在一些实施例中,内连线通孔122及内连线配线124嵌入在内连线介电结构126内。在一些实施例中,通过沉积工艺(例如PVD、CVD、ALD、溅镀等)、移除工艺(例如,湿式刻蚀、干式刻蚀、CMP)和/或图案化工艺(例如,光刻/刻蚀)的各种步骤形成内连线结构120。举例来说,在一些实施例中,内连线结构120是通过单镶嵌工艺和/或双镶嵌工艺形成。在一些实施例中,内连线介电结构126包含例如氮化物(例如,氮化硅、氮氧化硅)、碳化物(例如,碳化硅)、氧化物(例如,氧化硅)、硼硅酸盐玻璃(BSG)、磷硅酸盐玻璃(PSG)、硼磷硅酸盐玻璃(BPSG)、低介电常数氧化物(例如,掺杂碳的氧化物、SiCOH)等。此外,在一些实施例中,内连线通孔122及内连线配线124可包含导电材料,例如(举例来说)钛、钽、铝、钨、铜或一些其他适合的导电材料。

在一些实施例中,场板108可耦合到第一源极/漏极区106a以减小栅极电极110与第二源极/漏极区106b之间的电容。此外,在一些实施例中,为减小栅极电极110与第二源极/漏极区106b之间的电容,将场板108与栅极电极110完全间隔开。

为减小栅极电极与漏极区之间的电容,将场板与栅极电极间隔开,且可将场板电耦合到源极区。通过减小栅极电极与漏极区之间的电容,接通LDMOS晶体管的电阻得以减小,且因此在接通与关断切换期间LDMOS的功率损耗得以减小。然而,通过先在场板介电层112之上形成场板108再在栅极介电层116之上形成栅极电极110,能在维持LDMOS晶体管的可靠性的同时增大总体LDMOS晶体管的装置密度。

图22说明分别与图5到图21的剖视图500到2100对应的方法2200的一些实施例的流程图。

虽然方法2200在下文被说明且阐述为一系列动作或事件,但应了解,此类动作或事件的所说明排序不应被解释为具有限制意义。举例来说,一些动作可以不同的次序发生和/或与除本文中所说明和/或所述的动作或事件之外的其他动作或事件同时发生。另外,可能并非所有所说明的动作均是实施本文中说明的一个或多个方面或实施例所必需的。此外,本文中所绘示的动作中的一者或多者可在一个或多个单独的动作和/或阶段中施行。

在动作2202处,在衬底内形成低掺杂漂移区。图5说明对应于动作2202的一些实施例的剖视图500。

在动作2204处,在位于衬底上的连续的场板介电层之上形成连续的场板层。图6说明对应于动作2204的一些实施例的剖视图600。

在动作2206处,执行第一移除工艺以移除连续的场板层的外侧部分,以在连续的场板介电层之上及在低掺杂漂移区之上形成场板。图8说明对应于动作2206的一些实施例的剖视图800。

在动作2208处,在场板的外侧壁上及在衬底之上形成间隔件结构。图10说明对应于动作2208的一些实施例的剖视图1000。

在动作2210处,在衬底及场板之上形成连续的栅极介电层。图12说明对应于动作2210的一些实施例的剖视图1200。

在动作2212处,在连续的栅极介电层之上形成栅极电极层。图13说明对应于动作2212的一些实施例的剖视图1300。

在动作2214处,执行第二移除工艺以移除栅极电极层的外侧部分及连续的栅极介电层的外侧部分,以在栅极介电层之上形成栅极电极。图14说明对应于动作2214的一些实施例的剖视图1400。

在动作2216处,在衬底内形成第一源极/漏极区及第二源极/漏极区,其中场板及栅极电极位于第一源极/漏极区与第二源极/漏极区之间。图18说明对应于动作2216的一些实施例的剖视图1800。

因此,本公开涉及形成具有配置在场板介电层之上的场板的高功率装置,所述场板是在位于栅极介电层之上的栅极电极之前形成以减小场板与栅极电极之间的间隔,从而增大总体高功率装置的装置密度。

因此,在一些实施例中,本公开涉及一种集成芯片,所述集成芯片包括:栅极介电层,配置在衬底之上及源极区与漏极区之间;栅极电极,配置在所述栅极介电层之上;场板介电层,配置在所述衬底之上及所述栅极介电层与所述漏极区之间;以及场板,配置在所述场板介电层之上,其中所述场板介电层与所述栅极介电层间隔开。

在一些其他实施例中,在所述的集成芯片中,还包括:间隔件结构,环绕所述场板的外侧壁且直接配置在所述场板介电层之上。

在一些其他实施例中,在所述的集成芯片中,其中所述间隔件结构直接配置在所述场板介电层的外侧部分之上,其中所述场板直接配置在所述场板介电层的中心部分之上,且其中所述场板介电层的所述中心部分比所述场板介电层的所述外侧部分厚。

在一些其他实施例中,在所述的集成芯片中,其中所述场板具有配置在所述衬底的最顶表面上方第一高度处的最顶表面,其中所述栅极电极具有配置在所述衬底的所述最顶表面上方第二高度处的最顶表面,且其中所述第一高度约等于所述第二高度。

在一些其他实施例中,在所述的集成芯片中,其中所述场板电耦合到所述源极区。

在一些其他实施例中,在所述的集成芯片中,其中所述场板包含与所述栅极电极不同的材料。

在一些其他实施例中,在所述的集成芯片中,其中所述场板直接上覆在所述衬底的低掺杂漂移区上,且其中所述低掺杂漂移区具有比所述漏极区低的掺杂浓度。

在其他实施例中,本公开涉及一种集成芯片,所述集成芯片包括:栅极电极,配置在第一源极/漏极区与第二源极/漏极区之间的衬底之上;场板介电层,配置在所述衬底之上及所述栅极电极与所述第二源极/漏极区之间;场板,配置在所述场板介电层的中心部分之上;以及间隔件结构,配置在所述场板介电层的外侧部分之上且环绕所述场板的外侧壁。

在一些其他实施例中,在所述的集成芯片中,其中所述场板介电层的所述中心部分比所述场板介电层的所述外侧部分厚。

在一些其他实施例中,在所述的集成芯片中,其中所述衬底包含氮化镓。

在一些其他实施例中,在所述的集成芯片中,其中所述间隔件结构具有与所述场板在所述衬底的最顶表面上方处于相同高度处的最顶表面。

在一些其他实施例中,在所述的集成芯片中,还包括:栅极介电层,直接配置在所述栅极电极与所述衬底之间,其中所述栅极介电层具有与所述栅极电极的宽度相等的宽度。

在一些其他实施例中,在所述的集成芯片中,其中所述栅极介电层具有第一厚度,其中所述场板介电层的所述外侧部分具有比所述第一厚度大的第二厚度,且其中所述场板介电层的所述中心部分具有比所述第二厚度大的第三厚度。

在一些其他实施例中,在所述的集成芯片中,其中所述栅极电极比所述场板厚。

在一些其他实施例中,在所述的集成芯片中,其中所述场板的上表面与所述栅极电极的上表面实质上共面。

在另一些其他实施例中,本公开涉及一种形成高电压晶体管装置的方法,所述方法包括:在衬底上或所述衬底内形成与漏极区隔开的源极区;在所述衬底之上形成连续的场板介电层;在所述连续的场板介电层之上形成连续的场板层;执行第一移除工艺,以移除所述连续的场板层的外侧部分来形成场板,并移除所述连续的场板介电层的外侧部分;在所述场板的外侧壁上及所述衬底之上形成间隔件结构;在所述衬底及所述场板之上形成连续的栅极介电层;在所述连续的栅极介电层之上形成连续的栅极电极层;以及执行第二移除工艺,以移除所述连续的栅极电极层的外侧部分及所述连续的栅极介电层的外侧部分,从而在与所述场板及所述场板介电层间隔开的栅极介电层之上形成栅极电极。

在一些其他实施例中,在所述的方法中,还包括:在所述形成所述间隔件结构之后执行第三移除工艺,以进一步移除所述连续的场板介电层的未被所述间隔件结构或所述场板覆盖的外侧部分,从而在所述间隔件结构及所述场板下方形成场板介电层。

在一些其他实施例中,在所述的方法中,还包括:执行平坦化工艺,以移除所述场板的上部部分和/或所述栅极电极的上部部分,其中在所述平坦化工艺之后,所述场板的最顶表面与所述栅极电极的最顶表面实质上共面。

在一些其他实施例中,在所述的方法中,还包括:在所述场板及所述栅极电极之上形成内连线结构,所述内连线结构包括位于内连介电层内的内连线配线及内连线通孔,其中所述内连线结构将所述场板电耦合到所述源极区。

在一些其他实施例中,在所述的方法中,其中所述第一移除工艺及所述第二移除工艺包括干式刻蚀。

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下在本文中作出各种改变、代替及变更。

- 集成芯片及形成晶体管装置的方法

- 集成芯片及用于形成高压晶体管器件的方法