一种存储器的信息区数据上电自检方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及集成电路设计技术领域,具体涉及一种存储器的信息区数据上电自检方法。

背景技术

微控制单元(MCU),又称微型计算机或者单片机,是把中央处理器的频率与规格做适当缩减,并将内存、计数器、USB、A/D转换、UART、PLC、DMA等周边接口,甚至LCD驱动电路都整合在单一芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。目前MCU芯片在上电后需要先初始化硬件环境,即先初始化内核时钟、主时钟和各个外设的时钟,然后关闭看门狗、建立中断向量表和初始化堆栈寄存器,然后初始化软件环境,即MCU芯片的运行系统自动加载存储器的信息区的数据来配置MCU的具体参数或者可选功能,然而在信息区的数据加载过程中如果存在干扰或者原来存储数据异常,会导致配置信息错误,进而导致MCU芯片的功能异常或者出行死机等问题。

发明内容

鉴于背景技术的不足,本发明提供了一种存储器信息区数据上电自检方法,所要解决的技术问题是目前MCU芯片的运行系统在加载存储器的信息区的数据来配置功能时可能会因为数据异常造成配置信息错误,进而导致MCU芯片功能异常或者出行死机等问题。

为解决以上技术问题,本发明提供了如下技术方案:一种存储器的信息区数据上电自检方法,包括以下步骤:

S1:在存储器的信息区中选取M个存储单元,M为正整数,在M个存储单元中分别设置译码位;

S2:在向存储器的信息区配置数据时,分别向M个存储单元的译码位写入一位二进制的校验数据;

S3:MCU芯片上电;

S4:MCU芯片的运行系统先自动加载存储器的信息区的配置数据,接着提取所述M个存储单元的译码位的校验数据进行译码,如果译码成功则MCU芯片的运行系统继续运行,否则重新执行步骤S4,直至译码成功。

作为进一步的技术方案,M个存储单元连续分布,M不大于存储单元的位数,M个存储单元的译码位的位置互不相同。

作为进一步的技术方案,步骤S4中的译码成功是指M个存储单元的译码位的校验数据在译码后的数据和预设值相同。

更进一步地,步骤S2中,将M个存储单元的译码位的校验数据按照存储地址增加的顺序依次存入到存储器的信息区的存储单元A的M位bit中,译码成功是指MCU芯片的运行系统提取到的M个存储单元的译码位的校验数据和存储单元A的M位bit中的数据相同。

本发明与现有技术相比所具有的有益效果是:通过本发明方法可以在上电后对存储器的信息区的数据进行自检,在存储器的信息区的数据出现异常或者错误后使MCU芯片的运行系统重新加载存储器的信息区的数据进行自检,直至译码成功,避免MCU芯片将存储器内的错误数据来配置功能参数,以及确保MCU芯片在运行时不会因为配置参数错误而出现功能异常或者死机等问题。

附图说明

本发明有如下附图:

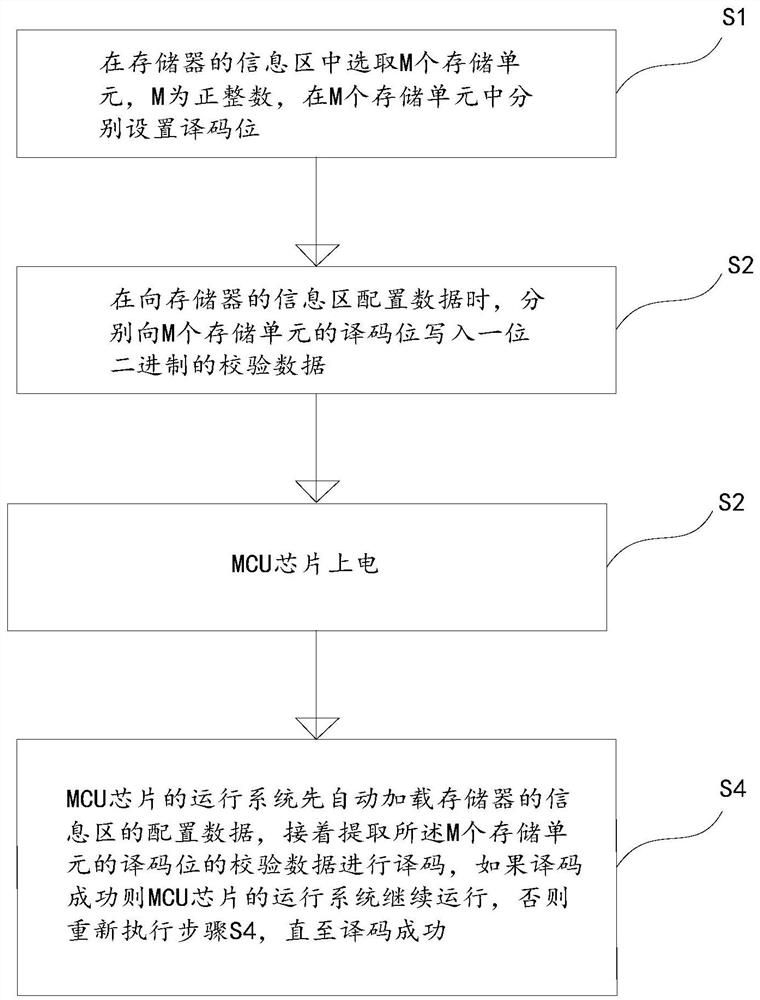

图1本发明进行自检的流程图;

图2为实施例中的存储器的结构示意图;

图3为实施例中的第一种译码电路的电路示意图;

图4为实施例中的第二种译码电路的电路示意图;

图5为实施例中向存储器的信息区的前八个存储单元的译码位写入校验数据后的存储示意图。

具体实施方式

现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

如图1所示,一种存储器的信息区数据上电自检方法,包括以下步骤:

S1:在存储器的信息区中选取M个存储单元,M为正整数,在M个存储单元中分别设置译码位;

S2:在向存储器的信息区配置数据时,分别向M个存储单元的译码位写入一位二进制的校验数据;

S3:MCU芯片上电;

S4:MCU芯片的运行系统先自动加载存储器的信息区的配置数据,接着提取所述M个存储单元的译码位的校验数据进行译码,如果译码成功则MCU芯片的运行系统继续运行,否则重新执行步骤S4,直至译码成功。

如图2所示,存储器可以划分为程序区和信息区,程序区用来存储MCU芯片的运行程序,信息区用来存储MCU芯片的配置信息。信息区的存储单元的地址从上往下是依次增加的,其中,信息区的存储单元地址为0X00~0X0F,每一个地址存储一组数据,在每一组数据中任意选取一位作为译码数据使用,则译码数据位可以设置为0~16位。

作为进一步的技术方案,M个存储单元连续分布,M不大于存储单元的位数,M个存储单元的译码位的位置互不相同。本实施例中,选取信息区的前八个存储单元即M等于8,八个存储单元的地址分别为0X00~0X07。在步骤S2中,在配置存储器信息区的时候,烧录器写入01011010到八个存储单元预留的译码位中,具体如图5所示。MCU芯片在上电后,MCU芯片的运行系统会自动加载存储器信息区的数据,读取每一个存储单元的数据内容,提取前八个存储单元的译码位的校验数据到如图3所示的译码电路进行识别译码,在译码时钟CLK到来后通过D触发器将译码结果传递给后级复位电路和时钟控制电路,系统复位信号高电平且时钟切换为系统时钟,程序继续运行,否则MCU的运行系统重新加载存储器信息区的数据进行译码,直至译码成功,因此本实施例中的译码成功是指图3所示的译码电路在输入存储器信息区前八个存储单元预留的译码位的数据后输出高电平的复位信号。

在某种实施方式中,为了提高译码的灵活性,在步骤S2中配置存储器信息区数据时,把0X00~0X07地址的校验数据同时存储到0X08 bit<7:0>中。MCU芯片上电后,MCU芯片的运行系统自动加载存储器信息区数据,然后再通过如图4所示的译码电路对比存储地址为0X00~0X07的存储单元中的译码数据和存储地址为0X08的存储单元的bit<7:0>数据是否一致,如果一致则存储器信息区的数据无误,如果不一致则存储器信息区的数据出现异常,此方法仍可以验证MCU芯片在上电自动加载存储器信息区数据时的准确性,另外该方法可以在每次配置信息区时调整校验数据,不再依赖硬件电路。

在以上方法的基础上还可通过增加烧录器和软件,实现芯片加密功能,保证存储器数据不被读出,具体如下:烧录软件根据固定的用户ID自动生成随机8位秘钥,烧录器将8位随机秘钥烧录在存储器信息区的存储地址为0X00~0X07的存储单元的译码位中和存储地址为0X08的存储单元的bit<7:0>中。MCU芯片上电时先自动加载信息区数据,然后通过硬件译码电路识别、对比译码数据。软件设置读取芯片存储程序时需验证信息区译码数据,由于译码数据的随机性,选择加密芯片后就很难读出存储程序,既保证了加载信息区数据的可靠性,也能保证芯片数据的私密性。

上述依据本发明为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求范围来确定其技术性范围。

- 一种存储器的信息区数据上电自检方法

- 建筑信息模型数据库的自检方法及自检系统