优化CIS传感器多晶硅刻蚀缺陷的方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及半导体技术领域,尤其是涉及一种优化CIS传感器多晶硅刻蚀缺陷的方法。

背景技术

CIS(CMOS Image Sensor)传感器是一种光电转换器件,它采用一列内置的LED发光二极管照明,因该部件体积小,重量轻,被广泛用于含摄像功能的智能手机等移动设备中。

实际生产中,使CIS传感器的生产维持在一个稳定的良率是一个工艺成熟稳定的标志,其中形成CIS传感器的步骤中,刻蚀多晶硅形成浮栅这一步骤作为前段刻蚀工艺中最重要的一环,对CIS传感器的电学特性表现和良率都起着极其重要的决定性作用。在CIS传感器的多晶硅刻蚀工艺中,各种因素都可能会造成多晶硅的刻蚀出现缺陷。

现有技术中,刻蚀形成CIS器件的机台包括:承载台、位于承载台上用于限位晶圆的边缘环、包围承载台的腔体以及位于腔体顶壁用于通入气体的管道。其中,腔体包括:侧壁和顶壁,顶壁由石英盘组成。由于现有腔体的设计TCP处于承载台的上方,电感耦合产生等离子体与产生等离子体的线圈半径分布一致,使得石英盘处于强等离子体处,导致在使用SIN膜作为多晶硅刻蚀的硬质膜时,在多晶硅刻蚀的过程中会形成类似于环形的刻蚀缺陷,留下小块的多晶硅残留,从而影响CIS传感器的质量。

发明内容

本发明的目的在于提供一种优化CIS传感器多晶硅刻蚀缺陷的方法,在刻蚀CIS传感器之前,可以清洗刻蚀机台的腔体的顶壁的毛刺,使得在刻蚀形成CIS传感器时能减少刻蚀的缺陷,提高CIS传感器的质量。

为了达到上述目的,本发明提供了一种优化CIS传感器多晶硅刻蚀缺陷的方法,用于在CIS传感器刻蚀前清洗刻蚀机台的腔体,刻蚀机台包括:承载台、位于所述承载台上用于限位待刻蚀的半导体基底的边缘环、包围所述承载台的腔体以及位于所述腔体的顶壁并用于通入气体的管道。其中,所述腔体包括:侧壁和顶壁,优化CIS传感器多晶硅刻蚀缺陷的方法包括:

S11:提供半导体基底,所述半导体基底包括Si-O薄膜;

S12:刻蚀所述半导体基底,以产生Si-O聚合物,所述Si-O聚合物对所述腔体的顶壁和侧壁进行填充;

S13:清洗所述腔体的侧壁,以去除所述侧壁的Si-O聚合物;

S14:多次重复步骤S12~S13,使得所述腔体的顶壁填充满Si-O聚合物。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,所述半导体基底包括晶圆和位于所述晶圆上的二氧化硅层。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,所述二氧化硅层的厚度大于或等于1000埃。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,每次刻蚀所述半导体基底的时间大于或等于10分钟。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,刻蚀所述半导体基底的方法包括刻蚀二氧化硅层。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,采用NF

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,清洗所述腔体的侧壁的时间大于或等于60s。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,每进行一次步骤S12之后进行一次步骤S13。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,并且重复次数大于或等于50次。

可选的,在所述的优化CIS传感器多晶硅刻蚀缺陷的方法中,所述顶壁由石英盘组成。

在本发明提供的优化CIS传感器多晶硅刻蚀缺陷的方法中,包括:S11:提供半导体基底,所述半导体基底包括Si-O薄膜;S12:刻蚀所述半导体基底,以产生Si-O聚合物,所述Si-O聚合物对所述腔体的顶壁和侧壁进行填充;S13:清洗所述腔体的侧壁,以去除所述侧壁的Si-O聚合物;S14:多次重复S12步骤和S13步骤,使得所述腔体的顶壁填充满Si-O聚合物。本发明在刻蚀CIS传感器之前,可以清洗刻蚀机台的腔体的顶壁的毛刺,使得在刻蚀形成CIS传感器时能减少刻蚀的缺陷,提高CIS传感器的质量。

附图说明

图1是本发明实施例的刻蚀机台的结构示意图;

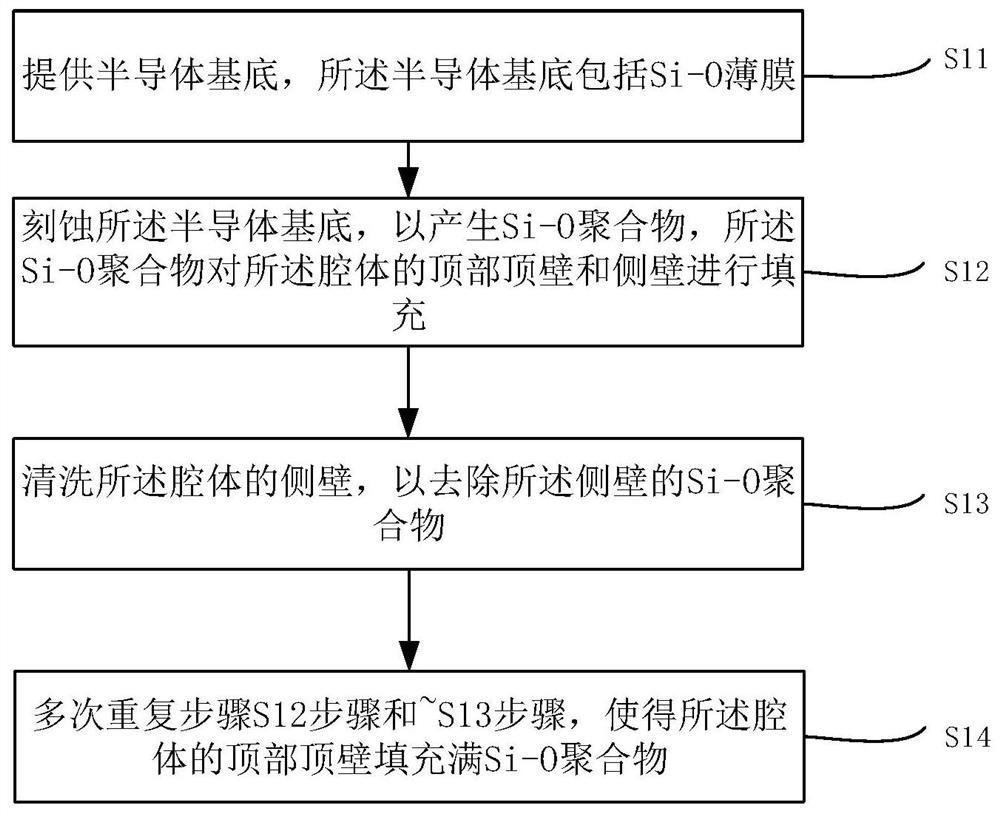

图2是本发明实施例的优化CIS传感器多晶硅刻蚀缺陷的方法的流程图;

图3至图4是本发明实施例的优化CIS传感器多晶硅刻蚀缺陷的方法的示意图;

图中:110-承载台、120-边缘环、130-侧壁、140-顶壁、150-通道、160-SI-O聚合物。

具体实施方式

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

在下文中,术语“第一”“第二”等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换。类似的,如果本文所述的方法包括一系列步骤,且本文所呈现的这些步骤的顺序并非必须是可执行这些步骤的唯一顺序,且一些所述的步骤可被省略和/或一些本文未描述的其他步骤可被添加到该方法。

CIS传感器的形成方法为现有技术,在此,只对其中的主要步骤进行阐述,形成CIS传感器的主要步骤一般是,提供晶圆,在晶圆上形成栅氧化层和浮栅,之后再形成控制栅。形成浮栅和控制栅均是先形成多晶硅层,再刻蚀多晶硅层形成浮栅或控制栅。因此,刻蚀多晶硅这一步骤非常重要,并且要求高。刻蚀多晶硅主要采用刻蚀机台刻蚀。请参照图1,刻蚀机台一般包括:承载台110,用于放置待刻蚀的半导体基底、位于所述承载台110上用于限位待刻蚀的半导体基底的边缘环120、包围所述承载台110的腔体以及位于所述腔体的顶壁并用于通入气体的管道150。其中,所述腔体包括:侧壁130和顶壁140,顶壁140由石英盘组成,很容易得知,侧壁130与承载台110连接,侧壁130位于承载台110的四周,顶壁140与侧壁130连接,顶壁140将侧壁130形成的腔体密封。刻蚀时,管道150通入刻蚀气体对承载台110上待刻蚀的半导体基底进行刻蚀,刻蚀气体在腔体内受到磁场的作用到达承载台110上的半导体基底表面,对半导体基底进行刻蚀。因此,腔体内有磁场力的存在,此时,如果顶壁的石英盘表面具有毛刺或者石英盘表面具有粗糙部位,在磁场力的作用下,容易达到半导体基底的表面。导致在刻蚀多晶硅时,在多晶硅上形成刻蚀缺陷,例如,多晶硅表面有类似环形颗粒的缺陷,影响CIS传感器的质量。因此,在衬底刻蚀形成CIS传感器前,对刻蚀腔体进行处理,以减少刻蚀时出现的缺陷。

请参照图2,本发明提供了一种优化CIS传感器多晶硅刻蚀缺陷的方法,用于在CIS传感器刻蚀前清洗刻蚀机台的腔体,其中,腔体包括侧壁和顶壁,优化CIS传感器多晶硅刻蚀缺陷的方法包括:

S11:提供半导体基底,所述半导体基底包括Si-O薄膜;

S12:刻蚀所述半导体基底,以产生Si-O聚合物,所述Si-O聚合物对所述腔体的顶壁和侧壁进行填充;

S13:清洗所述腔体的侧壁,以去除所述侧壁的Si-O聚合物;

S14:多次重复步骤S12~S13,使得所述腔体的顶壁填充满Si-O聚合物。

接着,请参照图3和图4,首先,提供含有Si-O薄膜的半导体基底,用于刻蚀产生Si-O聚合物,以对所述腔体的顶壁140和侧壁130进行填充。本发明实施例中,所述半导体基底包括晶圆和位于所述晶圆上的二氧化硅层,二氧化硅层为二氧化硅,二氧化硅含有Si-O化合物,在本发明的其他实施例中,也可以是除了二氧化硅的其他含Si-O的物质。形成半导体基底的方法为:提供一衬底,例如,是一晶圆,在衬底上形成一层二氧化硅层,形成二氧化硅层的方法可以是沉积二氧化硅形成。而形成的所述二氧化硅层的厚度大于或等于1000埃。

接着,对半导体基底进行刻蚀,刻蚀所述半导体基底的方法包括刻蚀二氧化硅层,即,主要刻蚀的是半导体基底上的二氧化硅层以产生Si-O聚合物160,Si-O聚合物160在磁场的作用下达到腔体的顶壁140和侧壁130,最终聚积在顶壁140和侧壁130。其中,每次刻蚀半导体基底即刻蚀二氧化硅层的时间大于或等于10分钟。

接着,由于顶壁140和侧壁130都聚积有Si-O聚合物,因此,需要刻蚀掉腔体的侧壁130的Si-O聚合物160,本发明实施例中采用NF3和O2的混合气体清洗所述腔体的侧壁130,NF

发明人发现,只进行一次步骤S12和步骤S13,Si-O聚合物160可能仍然没有填充满腔体的顶壁140,因此,在多次实验之后,需要不断重复步骤S12和步骤S13,不断Si-O聚合物160,自然地,因为侧壁的Si-O聚合物160不符合需求,因此每进行一次步骤S12的Si-O聚合物160填充,之后就进行一次步骤S13的侧壁Si-O聚合物160刻蚀。最终,经过数据计算和对顶壁140的Si-O聚合物160填充状况的观察,得出不断重复步骤S12和步骤S13的重复次数大于或等于50次。

综上,在本发明实施例提供的提供的优化CIS传感器多晶硅刻蚀缺陷的方法中,包括:S11:提供半导体基底,所述半导体基底包括Si-O薄膜;S12:刻蚀所述半导体基底,以产生Si-O聚合物,所述Si-O聚合物对所述腔体的顶壁和侧壁进行填充;S13:清洗所述腔体的侧壁,以去除所述侧壁的Si-O聚合物;S14:多次重复S12步骤和S13步骤,使得所述腔体的顶壁填充满Si-O聚合物。本发明在刻蚀CIS传感器之前,可以清洗刻蚀机台的腔体顶壁的毛刺,使得在刻蚀形成CIS传感器时能减少刻蚀的缺陷,提高CIS传感器的质量。

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

- 优化CIS传感器多晶硅刻蚀缺陷的方法

- 一种改善多晶硅刻蚀腔体聚合物缺陷的方法