数据加密方法、数据解密方法及存储介质

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及数据加解密技术领域,尤其涉及一种数据加密方法、数据解密方法及存储介质。

背景技术

高级加密标准(AES,Advanced Encryption Standard)为常见的对称加密算法,具有安全性高,速度快等特点,在信息安全领域中扮演重要的角色,现有技术中许多场景都采用协处理器对AES加解密算法进行加速,但是,传统的协处理器属于固定电路,只能进行特定等级的加解密,导致无法在同一个协处理器中实现不同等级的加解密算法。

发明内容

本申请实施例通过提供一种数据加密方法、数据解密方法及存储介质,旨在解决无法在同一个协处理器中实现不同等级的加解密算法的问题。

本申请实施例提供了一种数据加密方法,所述数据加密方法,包括:

在接收到明文数据后,将所述明文数据拆分为预设数量的明文字符串;

采用预设的加密密钥序列分别对每个所述明文字符串进行预设次数的循环加密,以得到每个所述明文字符串对应的密文字符串;

将所述密文字符串进行合并,以得到密文数据。

在一实施例中,所述采用预设的加密密钥序列分别对每个所述明文字符串进行预设次数的循环加密的步骤包括:

依次提取缓存中的各个所述明文字符串,其中,将拆分得到的所述明文字符串按照拆分顺序依次存储至所述缓存中;

在提取到每个所述明文字符串后,提取加密密钥序列中的首个加密密钥;

采用首个加密密钥对所述明文字符串进行加密得到密文字符串;

将所述首个加密密钥作为当前加密密钥;

获取加密密钥序列中所述当前加密密钥的下一加密密钥,并采用所述下一加密密钥对所述密文字符串进行加密,并采用加密结果更新所述密文字符串;

将所述下一加密密钥作为当前加密密钥;

返回执行所述获取加密密钥序列中所述当前加密密钥的下一加密密钥的步骤,直至所述加密密钥序列中的加密密钥均被提取或者所述明文字符串的加密次数达到预设次数,将当前的加密结果作为所述明文字符串对应的所述密文字符串。

在一实施例中,所述采用首个加密密钥对所述明文字符串进行加密得到密文字符串的步骤包括:采用首个加密密钥对所述明文字符串依次执行轮密钥加运算、字节替换查表运算、行位移运算以及列混合运算后,得到密文字符串。

在一实施例中,所述将所述密文字符串进行合并,以得到密文数据的步骤包括:将各个所述密文字符串对应的加密结果根据加密顺序进行合并,以得到密文数据。

此外,为实现上述目的,本发明还提供了一种数据解密方法,所述数据解密方法包括:

在接收到密文数据后,缓存所述密文数据,所述密文数据中包括预设数量的密文字符串;

采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串;

将所述明文字符串进行合并,以得到明文数据。

在一实施例中,所述采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串的步骤包括:

依次提取缓存中的各个所述密文字符串;

在提取到每个所述密文字符串后,提取解密密钥序列中的首个解密密钥;

采用首个解密密钥对所述密文字符串进行解密得到明文字符串;

将所述首个解密密钥作为当前解密密钥;

获取解密密钥序列中所述当前解密密钥的下一解密密钥,并采用所述下一解密密钥对所述密文字符串进行解密,并采用解密结果更新所述明文字符串;

将所述下一解密密钥作为当前解密密钥;

返回执行所述获取解密密钥序列中所述当前解密密钥的下一解密密钥的步骤,直至所述解密密钥序列中的解密密钥均被提取或者所述密文字符串的解密次数达到预设次数,将当前的解密结果作为所述密文字符串对应的所述明文字符串。

在一实施例中,所述采用首个解密密钥对所述密文字符串进行解密得到明文字符串的步骤包括:

采用首个解密密钥对所述密文字符串依次执行轮密钥加运算、字节逆替换查表运算、逆行位移运算以及逆列混合运算后,得到明文字符串。

在一实施例中,所述在接收到密文数据后,缓存所述密文数据,所述密文数据中包括预设数量的密文字符串的步骤之后还包括:

获取协处理器的工作模式;

根据所述工作模式确定每次从缓存中提取密文字符串的数量;

所述采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串的步骤包括:

采用预设的解密密钥序列分别对所述数量的密文字符串进行预设次数的并行循环解密,以得到所述数量的密文字符串对应的明文字符串。

在一实施例中,所述将所述明文字符串进行合并,以得到明文数据的步骤包括:将各个所述明文字符串对应的解密结果根据解密顺序进行合并,以得到明文数据。

此外,为实现上述目的,本发明还提供了一种存储介质,所述存储介质有数据加密程序以及数据解密程序,所述数据加密程序被处理器执行时实现上述的数据加密方法的各个步骤,所述数据解密程序被处理器执行时实现上述的数据解密方法的各个步骤。

本申请实施例中提供的一种数据加密方法、数据解密方法及存储介质的技术方案,至少具有如下技术效果或优点:

由于采用了在接收到明文数据后,将所述明文数据拆分为预设数量的明文字符串;采用预设的加密密钥序列分别对每个所述明文字符串进行预设次数的循环加密,以得到每个所述明文字符串对应的密文字符串;将所述密文字符串进行合并,以得到密文数据的技术方案,解决了现有技术中在同一个协处理器中执行不同等级的加密算法的问题,使协处理器实现在不同场景下功耗与性能的平衡。

由于采用了在接收到密文数据后,缓存所述密文数据,所述密文数据中包括预设数量的密文字符串;采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串;将所述明文字符串进行合并,以得到明文数据的技术方案,解决了现有技术中在同一个协处理器中执行不同等级的解密算法的问题,使协处理器实现在不同场景下功耗与性能的平衡。

附图说明

图1为本发明数据加密方法及数据解密方法的硬件运行环境结构示意图;

图2为本发明数据加密以及数据解密的分组示意图;

图3为本发明协处理器的内部结构示意图;

图4为本发明数据加密以及数据解密的流程示意图;

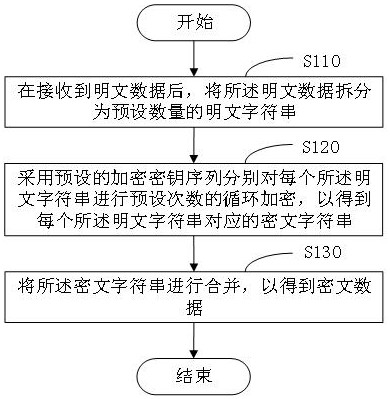

图5为本发明数据加密方法第一实施例的流程示意图;

图6为本发明数据加密方法第二实施例的流程示意图;

图7为本发明数据解密方法第五实施例的流程示意图;

图8为本发明数据解密方法第六实施例的流程示意图;

图9为本发明数据解密方法第八实施例的流程示意图;

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

为了更好的理解上述技术方案,下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

如图1所示,图1为本发明实施例方案涉及的硬件运行环境的结构示意图。

需要说明的是,图1即可为数据加密方法及数据解密方法的硬件运行环境的结构示意图,如图1所示,协处理器的总线接口挂载在系统总线上,同时,系统总线与外部缓存连接,协处理器的扩展指令接口与RISCV主处理器的扩展指令接口连接,接收主处理器发送的RISCV-AES加/解密扩展指令,并根据所述RISCV-AES加/解密扩展指令进行相应的配置,通过总线接口从外部缓存中读取明文数据或者密文数据,在协处理器中完成加密处理或者解密处理后,将加密生成的密文数据,以及解密生成的明文数据写入外部缓存中,当将密文数据以及所述明文数据全部写入外部缓存中时,生成中断信号,将所述终端信号发送至RISCV主处理器,通知RISCV主处理已完成一次AES加密或者解密操作。

本领域技术人员可以理解,图1中的数据加密方法及数据解密方法的硬件运行环境的结构并不构成对数据加密设备限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

本发明实施例提供了数据加密方法以及数据解密方法的实施例,需要说明的是,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤,该数据加密方法以及数据解密方法应用于协处理器中。

在本发明实施例中,AES(Advanced Encryption )是美国联邦政府采用的一种区块加密标准,属于对称加密;AES算法明文字符串以及密文字符串长度固定为128bit,不管是加密密钥还是解密密钥,都支持128bit、192bit和256bit三种长度,根据密钥长度的不同,AES加密算法又分为AES-128,AES-192,AES-256三种;协处理器支持的工作模式:1组数据串行加/解密模式,2组数据并行加/解密模式,3组数据并行加/解密模式,4组数据并行加/解密模式,每种工作模式下均支持AES-128,AES-192,AES-256三种密钥长度的加/解密算法。

如图5所示,在本申请的第一实施例中,本申请的数据加密方法,包括以下步骤:

步骤S110,在接收到明文数据后,将所述明文数据拆分为预设数量的明文字符串;

步骤S120,采用预设的加密密钥序列分别对每个所述明文字符串进行预设次数的循环加密,以得到每个所述明文字符串对应的密文字符串;

步骤S130,将所述密文字符串进行合并,以得到密文数据。

在本实施例中,为了解决在同一个协处理器中不能进行不同等级的加解密算法,本申请设计了一种数据加解密方法,该数据加解密方法应用在一种基于RISCV扩展指令集的AES加解密协处理器,利用定制的RISCV-AES加解密协扩展指令集,可以使指令集在指令集层面的AES算法调度与实现,通过可编程、可配置的方式让协处理器可以灵活执行不同等级的AES算法,如AES-128,AES-192,AES-256等,也可以针对明文或者密文长度的大小,灵活调度和配置明文字符串,例如,在高性能使用场景下,可以调用更多的协处理器硬件资源,实现多段明文/密文并行加/解密,从而实现对高速数据流的快速加解密,在低功耗使用场景下,可以只开启协处理其中特定的硬件资源,其余硬件资源进入低功耗状态,从而减少协处理器芯片的功耗。

在本实施例中,如图2所示,图2为数据加密以及数据解密的分组示意图,图2中的明文分组即为明文字符串,每个明文字符串的长度固定为128bit,图2中的虚线的箭头指向代表加密的过程,实线的箭头指向代表解密的过程,在加密时,明文数据被拆分为多个128bit的明文字符串,每个明文字符串均通过AES加密算法进行加密,得到对应长度的128bit的密文字符串,将密文字符串合并得到最终密文数据输出。

在本实施例中,在得到所述明文数据之后,将所述明文数据拆分为多个明文字符串并存储在外部缓存中,因为每个明文字符串的长度固定为128bit,因此,根据明文数据的长度以及所述明文字符串的长度可确定明文字符串的预设数量;所述循环加密的预设次数可根据协处理器的工作模式进行确定,在确定协处理器的工作模式之后,即可确定循环加密的预设次数,采用预设的加密密钥序列分别对每个明文字符串进行预设次数的循环加密,以得到每个明文字符串对应的密文字符串,最后将所有的密文字符串进行合并,得到密文数据。

在本实施例中,协处理器的内部结构示意图如图3所示,RISCV主处理器通过扩展指令端口向协处理器发送RISCV-AES加密扩展指令,协处理器的译码模块对RISCV-AES加密扩展指令进行译码,获得明文数据的源地址、明文数据长度、目的地址、初始密钥、加密密钥长度、协处理器工作模式等配置信息;本实施例以一次AES-128,1组明文字符串串行加密模式为例,明文数据加密得到密文数据的流程如图4所示,首先,协处理器的扩展密钥生成模块对初始密钥进行扩展,生成加密密钥序列;接着,DMA模块根据明文数据的源地址从图1中的外部缓存中搬运1组明文字符串,写入到协处理器内部的存储器1中,控制模块启动AES加密运算;接着,轮密钥加模块从加密密钥生成模块的加密密钥序列中获取首轮加密密钥,控制模块串行从存储器1中读出1组明文字符串;然后,将该明文字符串输入加密运算单元的轮密钥加模块0,经过字节替换查找表、行移位0、列混合模块0后完成第一轮加密,输出数据流重新输入轮密钥加密模块0,进行第二轮加密;以此类推,到第十轮加密时,控制模块控制数据流跳过列混合模块0直接输入到轮密钥加模块0中,产生1组密文字符串输出,将所述密文字符串写入存储器2中,由DMA模块读出并搬运到目的地址,完成1组明文字符串加密;DMA接着从源地址中获取1组明文字符串,重复此过程,直到所有明文字符串加密完毕,协处理器向RISCV主处理器发送中断,完成一次AES-128加密,将每一次加密得到的密文字符串合并,以得到密文数据,在这个过程中,只开启协处理其中特定的硬件资源,其余硬件资源进入低功耗状态,从而减少芯片功耗。

在本实施例中,以一次AES-128,4组明文字符串并行加密模式,与1组明文字符串串行加密模式类似,区别在于,每一次从源地址获取的明文字符串的数量不同,具体的,DMA模块根据明文数据的源地址从外部缓存中搬运4组明文字符串,写入到协处理器内部的存储器1中,控制模块启动AES加密运算;轮密钥加模块首先从加密密钥生成模块的加密密钥序列中获取首轮密钥,控制模块并行从存储器1中读出4组明文字符串,4组明文字符串分别输入加密运算单元中的轮密钥加模块0-轮密钥加模块3中,分别对应经过字节替换查找表模块、行移位模块0-行移位模块3、列混合模块0-列混合模块3运算后完成第一轮加密,输出数据流重新输入轮密钥加密模块,进行第二轮加密;以此类推,到第十轮加密时,控制模块控制数据流跳过列混合模块0-列混合模块3直接输入到轮密钥加模块0-轮密钥加模块3中,产生4组密文字符串输出,将密文字符串写入存储器2中,由DMA模块读出并搬运到目的地址,完成4组明文字符串并行加密;DMA接着从源地址中获取4组明文字符串,重复此过程,直到所有明文字符串加密完毕,协处理器向RISCV主处理器发送中断,完成一次AES-128加密,在这个过程中,可以调用更多的协处理器硬件资源,实现多组明文字符串并行加密,从而实现对高速数据流的快速加解密。

本实施例根据上述技术方案,由于采用了在接收到明文数据后,将所述明文数据拆分为预设数量的明文字符串,采用预设的加密密钥序列分别对每个明文字符串进行预设次数的循环加密,以得到每个明文字符串对应的密文字符串,将各个密文字符串进行合并,以得到密文数据的技术手段,实现了数据加密。

如图6所示,图6为本申请的第二实施例,基于第一实施例,本申请的数据加密方法,包括以下步骤:

步骤S121,依次提取缓存中的各个所述明文字符串,其中,将拆分得到的所述明文字符串按照拆分顺序依次存储至所述缓存中;

步骤S122,在提取到每个所述明文字符串后,提取加密密钥序列中的首个加密密钥;

步骤S123,采用首个加密密钥对所述明文字符串进行加密得到密文字符串;

步骤S124,将所述首个加密密钥作为当前加密密钥;

步骤S125,获取加密密钥序列中所述当前加密密钥的下一加密密钥,并采用所述下一加密密钥对所述密文字符串进行加密,并采用加密结果更新所述密文字符串;

步骤S126,将所述下一加密密钥作为当前加密密钥;

步骤S127,返回执行所述获取加密密钥序列中所述当前加密密钥的下一加密密钥的步骤,直至所述加密密钥序列中的加密密钥均被提取或者所述明文字符串的加密次数达到预设次数,将当前的加密结果作为所述明文字符串对应的所述密文字符串。

在本实施例中,在接收到明文数据之后,根据明文数据的长度以及所述明文字符串的固定长度可确定拆分得到的明文字符串的预设数量,将明文字符串按照拆分顺序依次存储在外部缓存中,当控制模块启动AES加密运算时,轮密钥加模块从扩展密钥生成模块中的加密密钥序列中获取首个加密密钥,控制模块串行从存储器1中读出明文字符串,采用首个加密密钥对所述明文字符串进行加密得到密文字符串,具体的,将该明文字符串输入加密运算单元的轮密钥加模块0,经过字节替换查找表、行移位0、列混合模块0后完成第一轮加密,输出数据流重新输入轮密钥加密模块0;接着,将所述首个加密密钥作为当前加密密钥,获取加密密钥序列中当前加密密钥的下一加密密钥,采用所述下一加密密钥对所述明文字符串进行第二轮加密;将所述下一加密密钥作为当前加密密钥,返回执行所述获取加密密钥序列中所述当前加密密钥的下一加密密钥的步骤,直至所述加密密钥序列中的加密密钥均被提取或者所述明文字符串的加密次数达到预设次数,将当前的加密结果作为所述明文字符串对应的所述密文字符串;到第十轮加密时,控制模块控制数据流跳过列混合模块0直接输入到轮密钥加模块0中,产生密文字符串输出,将所述密文字符串写入存储器2中,由DMA模块读出并搬运到目的地址,完成明文字符串加密,在这个过程中,不断对每一轮的加密结果更新,直到最终产生密文字符串输出。

在本实施例中,不断从源地址中获取明文字符串,重复此过程,直至加密密钥序列中的加密密钥均被提取或者所述明文字符串的加密次数达到预设次数,协处理器向RISCV主处理器发送中断信号,完成加密,将当前的加密结果作为所述明文字符串对应的所述密文字符串,同时,将每一次加密得到的密文字符串合并,以得到密文数据,在这个过程中,只开启协处理其中特定的硬件资源,其余硬件资源进入低功耗状态,从而减少芯片功耗。

本实施例根据上述技术方案,由于采用了对从外部缓存中提取的各个明文字符串并采用加密密钥进行循环加密的技术手段,实现了数据加密的效果。

,基于第二实施例,本申请第三实施例的数据加密方法,包括以下步骤:

步骤S1231,采用首个加密密钥对所述明文字符串依次执行轮密钥加运算、字节替换查表运算、行位移运算以及列混合运算后,得到密文字符串。

在本实施例中,在采用加密密钥对明文字符串进行加密得到密文字符串的过程,包括预设次数的循环加密,例如,在首次加密的过程中,采用首个加密密钥对所述明文字符串依次执行输入加密运算单元的轮密钥加模块0,字节替换查找表模块、行移位模块0以及列混合模块0后完成第一轮加密,输出数据流重新输入轮密钥加密模块0,进行第二轮加密。以此类推,到第十轮加密时,控制模块控制数据流跳过列混合模块0直接输入到轮密钥加模块0中,产生密文字符串输出。

在本实施例中,由于采用加密密钥对明文字符串执行轮密钥加运算、字节替换查表运算、行位移运算以及列混合运算后,从而实现对明文字符串的加密。

基于第二实施例,本申请第四实施例的数据加密方法,还包括以下步骤:

步骤S131,将各个所述密文字符串对应的加密结果根据加密顺序进行合并,以得到密文数据。

在本实施例中,将每个明文字符串进行预设次数的循环加密,并对循环加密结果更新,得到更新后的加密结果以及对应的密文字符串,将每个密文字符串对应的加密结果根据加密顺序进行合并,以得到密文数据,具体的,加密后的每个密文字符串对应的加密结果都会根据加密顺序依次存储在外部缓存对应的目的地址中,将目的地址中的各个加密结果根据所述加密顺序进行连接以合并,最终得到密文数据。

在本实施例的技术方案中,通过将各个密文字符串对应的加密结果根据加密顺序进行合并,从而明文数据对应的密文数据。

如图7所示,图7为本申请的第五实施例,第五实施例的数据解密方法包括以下步骤:

步骤S210,在接收到密文数据后,缓存所述密文数据,所述密文数据中包括预设数量的密文字符串;

步骤S220,采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串;

步骤S230,将所述明文字符串进行合并,以得到明文数据。

在本实施例中,如图2所示,图2为数据加密以及数据解密的分组示意图,图2中的密文分组即为密文字符串,每个密文字符串的长度固定为128bit,图2中的虚线的箭头指向代表加密的过程,实线的箭头指向代表解密的过程,在解密时,密文数据被拆分为多个128bit的密文字符串,每个密文字符串均通过AES解密算法进行解密,得到对应长度为128bit的明文字符串,将明文字符串合并得到最终明文数据输出。

在本实施例中,在得到所述密文数据之后,将所述密文数据拆分为多个密文字符串并存储在外部缓存中,因为每个密文字符串的长度固定为128bit,因此,根据密文数据的长度以及所述密文字符串的长度可确定密文字符串的预设数量;所述循环解密的预设次数根据协处理器的工作模式进行确定,在确定协处理器的工作模式之后,即可确定循环解密的预设次数,采用预设的解密密钥序列分别对每个密文字符串进行预设次数的循环解密,以得到每个密文字符串对应的明文字符串,最后将所有的明文字符串进行合并,得到明文数据。

在本实施例中,协处理器的内部结构示意图如图3所示,协处理器的译码模块对RISCV-AES解密扩展指令进行译码,获得密文源地址、密文数据长度、目的地址、初始密钥、密钥长度、协处理器工作模式等配置信息;本实施例以一次AES-192串行数据解密操作为例,明文数据加密得到密文数据的流程如图4所示,首先,处理器通过扩展指令接口向协处理器发送扩展RISCV-AES解密指令;协处理器的扩展密钥生成模块对初始密钥进行扩展,生成解密密钥序列;DMA模块根据密文的源地址和密文数据长度,从外部缓存中将获取1组128bit密文字符串写入协处理器内部的存储器1中,控制模块启动AES解密运算;轮密钥加模块首先从扩展密钥生成模块的解密密钥序列中获取首轮解密密钥,控制模块从存储器1中读取1组密文字符串,输入解密运算单元的轮密钥加模块0,经字节逆替换查找表模块、逆行位移模块0、逆列混合模块0运算后完成第一轮解密,接着,进行第二轮解密。以此类推,到第十二轮解密时,数据从逆行位移模块0输出后跳过逆列混合模块0直接进入轮密钥加模块0,产生1组明文字符串输出,明文字符串写入存储器2中,由DMA模块读出并搬运到目的地址;DMA模块接着从源地址读取下一组密文字符串,重复上述过程,直到所有密文字符串被解密完毕,协处理器向RISCV主处理器发出中断,完成一次AES-192解密操作。在串行模式下,只开启协处理其中特定的硬件资源,其余硬件资源进入低功耗状态,从而减少芯片功耗。在本实施例中,还可以配置为其他的协处理器密文数据并行工作模式,具体解密过程与串行数据解密操作类似,在此不再赘述。

本实施例根据上述技术方案,由于采用了在接收到密文数据后,缓存所述密文数据,所述密文数据中包括预设数量的密文字符串;采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串;将所述明文字符串进行合并,以得到明文数据的技术手段,实现了密文数据进行解密。

如图8所示,在本申请的第六实施例中,基于第五实施例,本申请的数据解密方法,包括以下步骤:

步骤S221,依次提取缓存中的各个所述密文字符串;

步骤S222,在提取到每个所述密文字符串后,提取解密密钥序列中的首个解密密钥;

步骤S223,采用首个解密密钥对所述密文字符串进行解密得到明文字符串;

步骤S224,将所述首个解密密钥作为当前解密密钥;

步骤S225,获取解密密钥序列中所述当前解密密钥的下一解密密钥,并采用所述下一解密密钥对所述密文字符串进行解密,并采用解密结果更新所述明文字符串;

步骤S226,将所述下一解密密钥作为当前解密密钥;

步骤S227,返回执行所述获取解密密钥序列中所述当前解密密钥的下一解密密钥的步骤,直至所述解密密钥序列中的解密密钥均被提取或者所述密文字符串的解密次数达到预设次数,将当前的解密结果作为所述密文字符串对应的所述明文字符串。

在本实施例中,在接收到密文数据之后,根据密文数据的长度以及所述密文字符串的固定长度可确定拆分得到的密文字符串的预设数量,将密文字符串按照拆分顺序依次存储在外部缓存中,当控制模块启动AES解密运算时,轮密钥加模块从扩展密钥生成模块中的解密密钥序列中获取首个解密密钥,控制模块串行从存储器1中读出密文字符串,采用首个解密密钥对所述密文字符串进行解密得到明文字符串,具体的,将该密文字符串输入解密运算单元的轮密钥加模块0,经过字节逆替换查找表模块、逆行移位模块0以及逆列混合模块0运算后完成第一轮加密,输出数据流重新输入轮密钥加密模块0;接着,将所述首个解密密钥作为当前解密密钥,获取解密密钥序列中当前解密密钥的下一个解密密钥,采用所述下一个解密密钥对所述密文字符串进行第二轮解密;将所述下一解密密钥作为当前解密密钥,返回执行所述获取解密密钥序列中所述当前解密密钥的下一解密密钥的步骤,直至所述解密密钥序列中的解密密钥均被提取或者所述密文字符串的解密次数达到预设次数,将当前的解密结果作为所述密文字符串对应的所述明文字符串;到第十轮解密时,控制模块控制数据流跳过逆列混合模块0直接输入到轮密钥加模块0中,产生明文字符串输出,将所述明文字符串写入存储器2中,由DMA模块读出并搬运到目的地址,完成密文字符串解密,在这个过程中,不断对每一轮的解密结果更新,直到最终产生明文字符串输出。

在本实施例中,不断从源地址中获取密文字符串,重复此过程,直至解密密钥序列中的解密密钥均被提取或者所述密文字符串的加密次数达到预设次数,协处理器向RISCV主处理器发送中断信号,完成解密,将当前的解密结果作为所述密文字符串对应的所述明文字符串,同时,将每一次解密得到的明文字符串合并,以得到明文数据,在这个过程中,只开启协处理其中特定的硬件资源,其余硬件资源进入低功耗状态,从而减少芯片功耗。

本实施例根据上述技术方案,由于采用了对从外部缓存中提取的各个密文字符串并采用解密密钥进行循环解密的技术手段,实现了数据解密的效果。

基于第六实施例,在本申请第七实施例的数据解密方法,包括以下步骤:

步骤S2231,采用首个解密密钥对所述密文字符串依次执行轮密钥加运算、字节逆替换查表运算、逆行位移运算以及逆列混合运算后,得到明文字符串。

在本实施例中,在采用解密密钥对密文字符串进行解密得到明文字符串的过程,包括预设次数的循环解密,例如,在首次解密的过程中,采用首个解密密钥对所述密文字符串依次执行输入解密运算单元的轮密钥加模块0,字节逆替换查找表模块、逆行移位模块0以及逆列混合模块0运算后完成第一轮解密,输出数据流重新输入轮密钥加密模块0,进行第二轮解密。以此类推,到第十轮解密时,控制模块控制数据流跳过逆列混合模块0直接输入到轮密钥加模块0中,产生明文字符串输出。

在本实施例中,由于采用解密密钥对密文字符串执行轮密钥加运算、字节逆替换查表运算、逆行位移运算以及逆列混合运算后,从而实现对密文字符串的解密。

如图9所示,图9为本申请的第八实施例,基于第六实施例,本申请第八实施例中的数据解密方法,包括以下步骤:

步骤S310,获取协处理器的工作模式;

步骤S320,根据所述工作模式确定每次从缓存中提取密文字符串的数量;

所述采用预设的解密密钥序列分别对每个所述密文字符串进行预设次数的循环解密,以得到每个所述密文字符串对应的明文字符串的步骤包括:

步骤S330,采用预设的解密密钥序列分别对所述数量的密文字符串进行预设次数的并行循环解密,以得到所述数量的密文字符串对应的明文字符串。

在本实施例中,所述协处理器的工作模式包括:1组数据串行解密模式,2组数据并行解密模式,3组数据并行解密模式,4组数据并行解密模式,根据所述工作模式确定每次从缓存中提取密文字符串的数量,例如,当所述协处理器的工作模式为4组数据并行解密模式时,从外部缓存中提取4组密文字符串,并采用预设的解密密钥序列分别对所述4组密文字符串进行预设次数的并行循环解密,以得到所述4组密文字符串对应的4组明文字符串,从而提高解密的处理速度。

本实施例根据上述技术方案,由于采用了获取协处理器的工作模式,根据所述工作模式确定每次从缓存中提取密文字符串的数量,采用预设的解密密钥序列分别对所述数量的密文字符串进行预设次数的并行循环解密,以得到所述数量的密文字符串对应的明文字符串的技术手段,采用并行的解密工作模式,提高解密速度。

基于第六实施例,本申请第九实施例中的数据解密方法,包括以下步骤:

步骤S231,将各个所述明文字符串对应的解密结果根据解密顺序进行合并,以得到明文数据。

在本实施例中,将每个密文字符串进行预设次数的循环解密,并对循环解密结果更新,得到更新后的解密结果以及对应的明文字符串,将每个明文字符串对应的解密结果根据解密顺序进行合并,以得到明文数据,具体的,解密后的每个明文字符串以及对应的解密结果都会根据解密顺序依次存储在外部缓存对应的目的地址中,将目的地址中的各个解密结果根据所述解密顺序进行连接以合并,最终得到明文数据。

在本实施例的技术方案中,通过将各个明文字符串对应的解密结果根据解密顺序进行合并,从而密文数据对应的明文数据。

基于同一发明构思,本申请实施例还提供了一种存储介质,所述存储介质存储有数据加密以及数据解密程序,所述数据加密程序被处理器执行时实现如上所述的数据加密方法的各个步骤,所述数据解密程序被处理器执行时实现如上所述的数据解密方法的各个步骤,且能达到相同的技术效果,为避免重复,这里不再赘述。

由于本申请实施例提供的存储介质,为实施本申请实施例的方法所采用的存储介质,故而基于本申请实施例所介绍的方法,本领域所属人员能够了解该存储介质的具体结构及变形,故而在此不再赘述。凡是本申请实施例的方法所采用的计算机存储介质都属于本申请所欲保护的范围。

本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机程序产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。

本发明是参照根据本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

应当注意的是,在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。单词“包含”不排除存在未列在权利要求中的部件或步骤。位于部件之前的单词“一”或“一个”不排除存在多个这样的部件。本发明可以借助于包括有若干不同部件的硬件以及借助于适当编程的计算机来实现。在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。单词第一、第二、以及第三等的使用不表示任何顺序。可将这些单词解释为名称。

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 数据加密方法、数据解密方法及存储介质

- 数据加密方法、数据解密方法、终端及存储介质