串行数据处理装置与数据偏移修正方法

文献发布时间:2023-06-19 12:05:39

技术领域

本案是关于串行数据处理装置,更明确地说,是关于可修正数据偏移的串行数据处理装置与其修正方法。

背景技术

串行通讯接口常见于计算机总线或是集成电路与集成电路之间的数据信道。在实际应用(尤其是同步传输应用)中,经由串行通讯接口传输的数据可能会受到传递延迟、信号反射、输入输出电路的驱动能力等等因素的影响,造成接收端装置收到的数据产生偏移。如此,将导致接收端装置接收到错误的数据。

发明内容

在一些实施例中,串行数据处理装置包含偏移侦测电路以及偏移校正电路。偏移侦测电路用以储存多个符记,并从主机装置接收第一数据信号,并根据这些符记侦测接收到的该第一数据信号的偏移以产生修正信号,其中这些符记中每一者都包含至少一默认逻辑值,且这些符记每一者的该至少一默认逻辑值的个数彼此不同。偏移校正电路用以根据该修正信号修正接收到的该第一数据信号,以产生第二数据信号。

在一些实施例中,数据偏移修正方法包含下列操作:从主机装置接收第一数据信号;根据多个符记侦测接收到的该第一数据信号的偏移以产生修正信号,其中这些符记中每一者都包含至少一默认逻辑值,且这些符记中每一者的该至少一默认逻辑值的个数彼此不同;以及根据该修正信号修正该第一数据信号,以产生第二数据信号。

有关本案的特征、实施与效果,将结合附图作详细说明如下。

附图说明

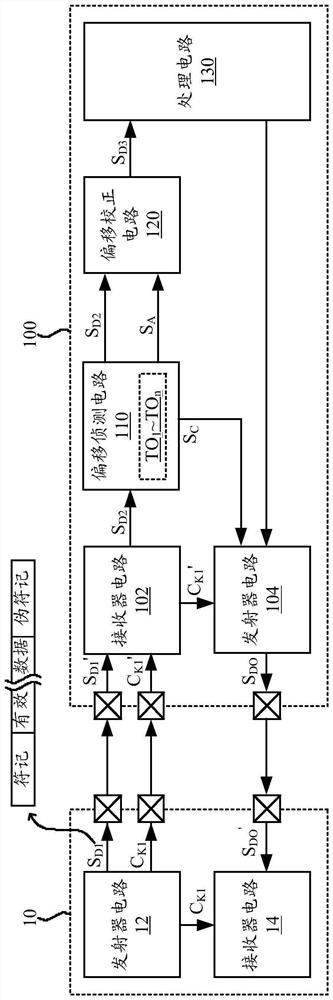

图1为根据本案一些实施例示出一种串行数据处理装置的示意图;

图2A为根据本案一些实施例示出图1的数据信号出现右偏移的波形示意图;

图2B为根据本案一些实施例示出图1的数据信号出现左偏移的波形示意图;

图3为根据本案一些实施例示出图1的数据信号的波形图;

图4为根据本案一些实施例示出一种串行数据处理装置的示意图;

图5A为根据本案一些实施例示出一种串行数据处理装置的示意图;

图5B为根据本案一些实施例示出一种串行数据处理装置的示意图;以及

图6为根据本案一些实施例示出一种数据偏移修正方法的流程图。

具体实施方式

本文所使用的所有词汇具有其通常的含义。上述的词汇在普遍常用字典中的定义,在本案的内容中包含任一于此讨论的词汇的使用例子仅为示例,不应限制到本案的范围与含义。同样地,本案也不仅以在此说明书所示出的各种实施例为限。

关于本文中所使用的“耦接”或“连接”,均可指两个或更多个组件相互直接作实体或电性接触,或是相互间接作实体或电性接触,也可指两个或更多个组件相互操作或动作。如本文所用,用语“电路”可为由至少一个晶体管与/或至少一个主被动组件按一定方式连接以处理信号的装置。

如本文所用,用语“与/或”包含了列出的关联项目中的一个或多个的任何组合。在本文中,使用第一、第二与第三等等之词汇,是用于描述并辨别各个组件。因此,在本文中的第一组件也可被称为第二组件,而不脱离本案的本意。为易于理解,在各附图中的类似组件将被指定为相同标号。

图1为根据本案一些实施例示出一种串行数据处理装置100的示意图。在一些实施例中,串行数据处理装置100从主机(host)装置10接收数据信号S

主机装置10包含发射器电路12与接收器电路14。串行数据处理装置100包含接收器电路102、发射器电路104、偏移侦测电路110、偏移校正电路120以及处理电路130。发射器电路12传输频率信号C

在一些实施例中,发射器电路104可根据频率信号C

处理电路130可从偏移校正电路120接收数据信号S

图2A为根据本案一些实施例示出图1的数据信号S

或者,若频率信号C

图2B为根据本案一些实施例示出图1的数据信号SD1'出现左偏移的波形示意图。于此例中,发射器电路12响应于频率信号CK1的上升沿传输数据信号SD1至接收器电路102。接收器电路102根据频率信号CK1'的上升沿对数据信号SD1'取样以产生数据信号SD2(未绘示)。若线路延迟的影响不大(即第一情形),频率信号C

或者,若线路延迟的影响过大(即第二情形),频率信号C

继续参照图1。在一些实施例中,偏移侦测电路110可包含缓存器(未绘示),其用以储存这些符记TO

TO

TO

TO

TO

TO

TO

在此例中,n设置为6,且每一个TO

如图1所示,数据信号S

在联机初始阶段,主机装置10与串行数据处理装置100可事先约定使用多个符记TO

举例来说,主机装置10使用包含符记TO

例如,若数据信号S

或者,若数据信号S

响应于修正信号S

在一些实施例中,偏移侦测电路110可包含缓存器电路、比较器电路(例如可为异或门电路)、计数器电路与/或其他数字逻辑电路,以实施储存多个符记TO

图3为根据本案一些实施例示出图1的数据信号S

在本案一些实施例中,当偏移侦测电路110侦测到数据信号S

图4为根据本案一些实施例示出一种串行数据处理装置100的示意图。相较于图1,如下表所示,多个符记TO

默认指令

TO

TO

TO

TO

TO

TO

在此例中,偏移侦测电路110还根据数据信号S

在一些应用中,处理电路130的操作为平行运算。在这些应用中,串行数据处理装置100可设定为输出并列数据。图5A为根据本案一些实施例示出串行数据处理装置100的示意图。在此例中,串行数据处理装置100还包含串行转并列(serial-to-parallel)电路510。串行转并列电路510耦接于偏移侦测电路110与偏移校正电路120之间,并用以根据数据信号S

图5B为根据本案一些实施例示出串行数据处理装置100的示意图。相较于图5A,串行转并列电路510耦接于偏移校正电路120与处理电路130之间。串行转并列电路510根据数据信号S

图6为根据本案一些实施例示出一种数据偏移修正方法600的流程图。在一些实施例中,数据偏移修正方法600可由(但不限于)串行数据处理装置100执行。

在操作S610,从主机装置接收第一数据信号。

在操作S620,根据多个符记侦测接收到的第一数据信号的偏移以产生修正信号,其中这些符记中每一者都包含至少一默认逻辑值,且这些符记中每一者的该至少一默认逻辑值的个数彼此不同。

在操作S630,根据修正信号修正接收到的第一数据信号,以产生第二数据信号。

上述操作S610、S620以及S630的说明可参照前述各个实施例,故不重复赘述。上述数据偏移修正方法600的多个操作仅为示例,并非限定需依照此示例中的顺序执行。在不违背本案的各实施例的操作方式与范围下,在数据偏移修正方法600下的各种操作当可适当地增加、替换、省略或以不同顺序执行。

上述关于符记的设置方式以及位数量用于示例,且本案各实施例并不以上述例子为限。

综上所述,本案一些实施例所提供的串行数据处理装置与数据偏移修正方法可利用预先设定好的多种符记修正数据偏移。在进一步的实施例中,这些符记还可用于传输默认指令。

虽然本案的实施例如上所述,然而这些实施例并非用来限定本案,本技术领域具有通常知识者可依据本案的明示或隐含的内容对本案的技术特征施以变化,凡此种变化均可能属于本案所寻求的专利保护范畴,换言之,本案的专利保护范围须视本说明书的申请专利范围所界定者为准。

【符号说明】

10:主机装置

12:发射器电路

14:接收器电路

100:串行数据处理装置

102:接收器电路

104:发射器电路

110:偏移侦测电路

120:偏移校正电路

130:处理电路

C

S

S

S

TO

S

510:串行转并列电路

600:数据偏移修正方法

S610,S620,S630:操作

- 串行数据处理装置与数据偏移修正方法

- 一种高速串行数据转并行数据的处理装置和方法