实施堆叠芯片高动态范围图像传感器的方法及系统

文献发布时间:2023-06-19 12:16:29

本申请为发明名称为“实施堆叠芯片高动态范围图像传感器的方法及系统”、申请号为201610344265.2、申请日为2016年5月23日的中国发明专利申请的分案申请。

技术领域

本发明的实例大体上涉及图像传感器。更特定来说,本发明的实例涉及实施堆叠芯片高动态范围图像传感器的方法及系统。

背景技术

在不同领域(其包含汽车领域、机器视觉领域及专业视频拍摄领域)中的许多应用中已广泛使用高速图像传感器。用于制造图像传感器(且尤其是互补金属氧化物半导体(COMS)图像传感器)的技术已持续以迅猛的速度进步。举例来说,对更高帧频及更低功耗的需求已促进这些图像传感器的进一步微型化及集成化。

增加COMS图像传感器的帧频的一种途径可为增加并行操作的读出电路的数目。在常规图像传感器中,像素阵列中的一列像素可共享一个读出电路。在常规技术中的其它实例中,像素阵列中的一列像素单元可共享多个读出电路。这些解决方案提供更高帧频,但需要更多硅面积,这并不有助于硅图像传感器的微型化。

此外,许多应用需要高动态范围(HDR)以捕获从10

发明内容

一方面,本发明提供一种在图像传感器中实施堆叠芯片高动态范围(HDR)算法的方法,其包括:由像素阵列捕获具有第一曝光时间的第一帧及具有第二曝光时间的第二帧,其中所述第一曝光时间与所述第二曝光时间相比更长或更短,其中所述像素阵列安置于第一半导体裸片中,其中所述像素阵列被划分成多个像素子阵列,其中所述多个像素子阵列中的每一者布置成多个像素群组,且其中所述多个像素群组中的每一者布置成p x q阵列的像素单元;由多个读出电路获取所述第一帧的图像数据及所述第二帧的图像数据,其中所述多个读出电路包含于安置于第二半导体裸片中的读出电路中,其中所述多个像素子阵列中的每一者通过多个导体中的对应一者耦合到所述多个读出电路中的对应一者;由包含于所述读出电路中的多个ADC电路分别将所述第一帧的所述图像数据从模拟转换成数字以获得第一ADC输出且将所述第二帧的所述图像数据从模拟转换成数字以获得第二ADC输出;以及由功能逻辑将所述第一ADC输出及所述第二ADC输出加总以产生最终ADC输出,其中所述功能逻辑安置于所述第二半导体裸片中。

另一方面,本发明提供一种堆叠芯片高动态范围(HDR)成像系统,其包括:像素阵列,其安置于第一半导体裸片中,其中所述像素阵列被划分成多个像素子阵列,其中所述多个像素子阵列中的每一者布置成多个像素群组,且其中所述多个像素群组中的每一者布置成p x q阵列的像素单元,其中所述像素阵列捕获具有第一曝光时间的第一帧及具有第二曝光时间的第二帧,其中所述第一曝光时间与所述第二曝光时间相比更长或更短;多个读出电路,其包含于安置于第二半导体裸片中的读出电路中,其中所述多个像素子阵列中的每一者通过多个导体中的对应一者耦合到所述多个读出电路中的对应一者,其中所述多个读出电路获取所述第一帧的图像数据及所述第二帧的图像数据,其中所述多个读出电路分别包含将所述第一帧的所述图像数据从模拟转换成数字以获得第一ADC输出且将所述第二帧的所述图像数据从模拟转换成数字以获得第二ADC输出的模/数(ADC)电路;以及功能逻辑,其耦合到所述读出电路以将所述第一ADC输出与所述第二ADC输出加总以产生最终ADC输出,其中所述功能逻辑安置于所述第二半导体裸片中。

另一方面,本发明提供一种在图像传感器中实施堆叠芯片高动态范围(HDR)算法的方法,其包括:由像素阵列捕获具有第一曝光时间的第一帧,其中所述像素阵列安置于第一半导体裸片中,其中所述像素阵列被划分成多个像素子阵列,其中所述多个像素子阵列中的每一者布置成多个像素群组,且其中所述多个像素群组中的每一者布置成p x q阵列的像素单元;由包含于读出电路中的多个ADC电路分别将所述第一帧的图像数据从模拟转换成数字以获得第一ADC输出,其中所述多个读出电路包含于安置于第二半导体裸片中的读出电路中,其中所述多个像素子阵列中的每一者通过多个导体中的对应一者耦合到所述多个读出电路中的对应一者;存储所述第一ADC输出;由所述像素阵列捕获具有第二曝光时间的第二帧,其中所述第一曝光时间与所述第二曝光时间相比更长或更短;由所述ADC电路将所述第二帧的图像数据从模拟转换成数字以获得第二ADC输出;读出所述第二ADC输出且由功能逻辑将所述第二ADC输出与所述存储的第一ADC输出加总以产生最终ADC输出,其中所述功能逻辑安置于所述第二半导体裸片中;将最终ADC输出存储于包含于所述功能逻辑中的帧缓冲器中;以及由外部主机执行HDR组合及线性化。

附图说明

在附图的图式中,以实例方式而非以限制方式说明本发明的实施例,其中相似元件符号贯穿各种视图指示类似元件,除非另有规定。应注意,在此揭示内容中参考本发明的“一”或“一个”实施例未必参考同一实施例,且其意味着至少一个实施例。在图中:

图1为说明根据本发明的一个实施例的包含具有像素阵列的图像传感器的实例成像系统的框图,所述像素阵列带有以用于堆叠CMOS图像传感器方案中的高动态范围(HDR)的像素架构布置于像素子阵列中的多个像素。

图2为根据本发明的教示的包含包含于像素阵列中的实例像素子阵列的图像传感器的部分的示意图。

图3为说明根据本发明的一个实施例的图1中的读出电路的细节的框图。

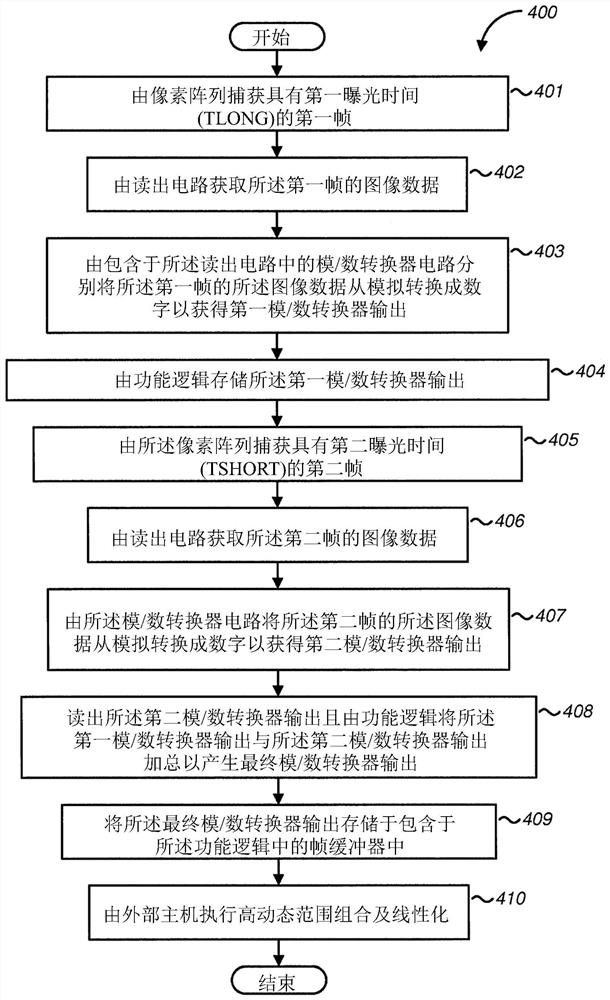

图4为展示根据本发明的一个实施例的读出被划分成像素子阵列的像素阵列的实例过程的流程图。

图5(a)及5(b)为说明根据本发明的一个实施例的相对于针对较长时间的曝光(Tlong)及较短时间的曝光(Tshort)的最低有效位(LSB)输出的光照水平的图表。

对应参考字符贯穿图式的若干视图指示对应组件。所属领域的技术人员应了解,图中的元件出于简单及清楚的目的而说明,且未必是按比例绘制。举例来说,图中一些元件的尺寸相对于其它元件可被夸大以帮助提高对本发明的各种实施例的理解。此外,为了促进对本发明的这些各种实施例的较不受阻碍的理解,通常不描绘在商业上可行的实施例中有用的或必要的常见但众所周知的元件。

具体实施方式

在以下描述中,阐述众多特定细节以便提供对本发明的透彻理解。然而,应理解,可在不具有这些特定细节的情况下实践本发明的实施例。在其它情况下,未展示众所周知的电路、结构及技术以避免混淆对此描述的理解。

贯穿本说明书的对“一个实施例”或“一实施例”的参考意指结合所述实施例所描述的特定特征、结构或特性包含于本发明的至少一个实施例中。因此,贯穿本说明书的各种地方的短语“在一个实施例中”或“在实施例中”的出现未必皆是指同一实施例。此外,在一或多个实施例中,可以任何合适方式组合特定特征、结构或特性。特定特征、结构或特性可包含于集成电路、电子电路、组合逻辑电路或提供所描述的功能的其它合适组件中。

如将在各种实例中揭示,一种用于读出具有高动态范围(HDR)的像素阵列有效方法,所述方法利用布置于堆叠CMOS芯片解决方案中的像素子阵列,在堆叠CMOS芯片解决方案中像素单元包含于第一半导体裸片中,且其中读出电路包含于第二半导体裸片中。例如,在一个实例中,所述第一半导体裸片可为像素裸片,且所述第二半导体裸片可为专用集成电路(ASIC)裸片。在一个实例中,像素子阵列可由n x m像素群组的集群组成。在实例中,根据本发明的教示,n x m像素群组内部的像素单元的放大器输出节点耦合在一起,使得n xm像素群组中的每一者共享包含于读出电路中的单个读出电路。在实例中,根据本发明的教示,以高速及/或用低功率并行读出像素子阵列。在一个实例中,具有其中像素单元的集群共享读出电路的共享像素架构的堆叠芯片图像传感器的HDR增加。

图1为说明根据本发明的一个实施例的包含具有像素阵列的图像传感器的实例成像系统的框图,所述像素阵列带有以用于堆叠CMOS图像传感器方案中的高动态范围(HDR)的像素架构布置于像素子阵列中的多个像素。如图1中所说明,根据本发明的教示,成像系统100包含具有像素阵列105的图像传感器,像素阵列105被划分成包含用于堆叠图像传感器方案中的HDR的像素架构的多个像素子阵列。在所说明的实例中,用堆叠CMOS芯片实现成像系统100,所述堆叠CMOS芯片包含与ASIC裸片180堆叠在一起且耦合到ASIC裸片180的像素裸片170。例如,在一个实例中,像素裸片170包含像素阵列105,且ASIC裸片180包含控制电路120、读出电路130及功能逻辑140。在所描绘的实例中,控制电路120经耦合以控制像素阵列105的操作,像素阵列105经耦合以由读出电路130通过位线160读出。

特定来说,在图1中所描绘的实例中,像素阵列105为被划分成多个像素子阵列110的二维(2D)阵列,如所展示。在一个实例中,每一像素子阵列110包含多个像素群组,所述多个像素群组中的每一者包含多个像素单元(图1中未展示)。在实例中,像素子阵列中的多个像素群组中的每一者经耦合以利用位线160的同一位线,且共享读出电路130中的同一读出电路,其更多细节将在下文结合图2进行描述。

控制电路120耦合到像素阵列105以控制像素阵列105的操作特性。在一个实例中,控制电路120经耦合以产生用于控制每一像素单元的图像获取的全局快门信号。在实例中,全局快门信号同时启用像素阵列105的所有像素子阵列110内的特定像素单元以在单个获取窗口期间同时转移来自其相应光电检测器的图像电荷。在一个实施例中,控制电路120控制像素阵列以致使像素阵列105捕获具有第一曝光时间的第一帧及具有第二曝光时间的第二帧。第一曝光时间(“Tlong”)与第二曝光时间(“Tshort”)相比可更长。在其它实施例中,第一曝光时间(“Tshort”)与第二曝光时间(“Tlong”)相比可更短。在一个实施例中,自动曝光控制逻辑包含于功能逻辑140中且确定第一曝光时间与第二曝光时间的比率。所述自动曝光控制逻辑因此计算适当曝光值(例如第一及第二曝光时间),所述曝光值被传输到控制电路120以在像素阵列105的捕获及读出期间实施所述曝光值。在此实施例中,通过第一曝光时间与第二曝光时间的比率确定增益系数。所述增益系数可由控制电路120或功能逻辑140确定。

在一个实例中,在像素子阵列110中的像素单元中的每一者已获取或捕获其图像数据或图像电荷之后,由读出电路130通过位线160的位线读出所述图像数据。在一个实施例中,逻辑电路(未展示)可控制读出电路130且将图像数据输出到功能逻辑140。功能逻辑140可仅存储图像数据或甚至通过应用后图像效果(例如,裁剪、旋转、移除红眼、调整亮度、调整对比度或以其它方式)操纵图像数据。

图2为根据本发明的教示的包含像素子阵列210(其可为包含于像素阵列(例如(举例来说)图1的实例像素阵列105)中的多个像素子阵列中的一者)的图像传感器的部分的一个实例的示意图。在图2中所描绘的实例中,像素子阵列210包含布置成n=2列且m=2行的多个像素群组220、221、222及223。组成图2中所描绘的实例中的像素子阵列210的四个像素群组220、221、222及223中的每一者包含布置成p=2列且q=2行的四个像素单元230、231、232及233,以及由每一像素群组220、221、222及223的所有四个像素单元230、231、232及233共享的像素支持电路240。

所述像素单元为图1的像素阵列105的最小重复单元,且在图2中所说明的实例中所展示的像素单元230、231、232及233中的每一者包含光电检测器251及转移晶体管252,其经耦合以由转移信号TG控制。布置于像素阵列105中的同一行且在相应像素群组内的相同位置中的转移晶体管可由相同转移信号控制。举例来说,布置于像素群组220的左上角中的像素单元230的转移晶体管252由转移信号TG1(i-1)控制,且布置在与像素群组220中的像素单元230相同的行中的像素群组221中的对应像素单元也包含由转移信号TG1(i-1)控制的转移晶体管,如所展示。

特定像素群组(例如像素群组220)的像素单元230、231、232及233中的四个转移晶体管252中的每一者共享单个浮动扩散节点241。在所说明的实例中所展示的像素支持电路240中的每一者耦合到每一特定像素群组的像素单元230、231、232及233中的四个转移晶体管252且由所述四个转移晶体管252共享,且包含复位晶体管242及放大器晶体管243(其在所说明的实例中为耦合源极跟随器(SF)的晶体管243)、行选择晶体管244及电容器245(其耦合到电容器线270)。浮动扩散节点241经耦合以经由电源RFD通过复位晶体管242复位到浮动扩散复位电压。复位晶体管242经耦合以响应于复位信号RST而受控制。在实例中,布置于同一行中的像素群组由相同复位信号控制。例如,像素群组220及221由复位信号RST(i-1)控制,而像素群组222及223由复位信号RST(i)控制。

浮动扩散节点241还经耦合以控制放大器晶体管的端子,所述放大器晶体管在图2中为使其栅极端子耦合到浮动扩散节点241且使其漏极端子耦合到电源VDD的源极跟随器晶体管243。在所描绘的实例中,行选择晶体管244由行选择信号控制。在实例中,布置于同一行中的像素群组由相同行选择信号RS控制。例如,像素群组220及221由行选择信号RS(i-1)控制,而像素群组222及223由行选择信号RS(i)控制。在一个实例中,行选择晶体管224耦合于位线260与源极跟随器晶体管243的漏极端子之间。源极跟随器晶体管243的源极端子耦合到位线260。同一像素子阵列中的像素单元耦合到同一位线。

电容器245耦合于浮动扩散区241与电容器线270之间。在所描绘的实例中,耦合到像素群组220及222的电容器线270经耦合以接收信号cap_line(j)。电容器245可响应于cap_line(j)而增加浮动扩散节点241的电容以增大像素单元的动态范围。在所说明的实例中,每一像素群组220、221、222及223的电容器245可用于在特定像素群组被读取时停用其它像素群组。例如,可通过响应于cap_line(j)而将低电压施加到电容器线270以在像素群组221及223的读出期间停用像素群组220及222。类似地,可通过经由cap_line(j+1)施加低电压而在像素群组220及222的读出期间停用像素群组221及223。

在其它实例中,应了解,可省略电容器245及电容器线270,可通过将低电压施加到RFD来停用含有未被读出的像素单元的像素群组。在其它实例中,可通过将下拉晶体管耦合在浮动扩散区241与低电压(例如接地)之间且启用所述下拉晶体管以将所述低电压提供给浮动扩散区241来停用含有未被读出的像素单元的像素群组。

如上文所概括,应注意,在图2中所描绘的实例中,像素子阵列210包含布置成n xm阵列的多个像素群组,其中n=2且m=2。另外,应注意,每一像素群组包含布置成p x q阵列的多个像素单元,其中p=2且q=2,且其中每一像素群组中的像素单元皆共享同一像素支持电路240。当然应了解,出于解释目的,所说明的实例利用n=2、m=2、p=2及q=2,且在其它实例中,其它值可用于n、m、p及q,其中n>1、m>1、p>1且q>1,且其中n、m、p及q为整数。

如所描绘的实例中所说明,像素子阵列210的所有像素单元形成于像素裸片270上且共享同一位线260。在一个实例中,位线260可将像素子阵列210的所有像素单元耦合到单个读出电路285,其可被包含作为包含于形成于与像素裸片270堆叠在一起且耦合到像素裸片270的ASIC裸片280上的读出电路283中的多个读出电路中的一者。在一个实例中,包含于读出电路283中的多个读出电路的每一单个读出电路285通过单个位线260耦合到所述多个像素子阵列中的单个者。在一个实例中,互连层290安置于像素裸片270与ASIC裸片280之间。在一个实例中,互连层290可包含多个导体。在实例中,可利用所述多个导体中的每一者将读出电路283耦合到包含于像素裸片270中的电路。

例如,在图2中所描绘的实例中,使用包含于互连层290中的多个导体中的一者来实现位线260。换句话说,在一个实例中,像素裸片270中的多个像素子阵列(例如像素子阵列210)中的每一单个者可通过包含于互连层290中的多个导体(例如位线260)中的对应单个者耦合到包含于ASIC裸片280中的读出电路283中的多个读出电路(例如读出电路285)中的对应单个者。因而,在一个实例中,根据本发明的教示,可由所述多个读出电路中的对应单个者通过所述多个导体中的对应单个者(或单个位线)并行读出所述多个像素子阵列中的每一单个者。

在一个实例中,互连层290可包含通孔,例如微穿硅通孔(μTSVs)或穿硅通孔(TSVs)。在其它实例中,一个像素子阵列210可耦合到形成于ASIC裸片280上的一个以上读出电路285。在其它实例中,两个或两个以上像素子阵列210可共享形成于ASIC裸片280上的一个读出电路285。在一个实例中,多个读出电路285中的每一者可包含形成于ASIC裸片280上的模/数转换器(ADC)电路、加法器及存储器(例如静态随机存取存储器(SRAM)或动态随机存取存储器(DRAM))。在其它实例中,多个读出电路285中的每一者可包含形成于ASIC裸片280上的ADC电路及加法器,其中存储器(例如SRAM及DRAM)形成于存储器裸片上,所述存储器裸片可通过互连层耦合到ASIC裸片280。

参考图3,其为说明根据本发明的一个实施例的图1中的读出电路130中的多个读出电路中的一者的细节的框图。如图3中所展示,读出电路130可包含扫描电路310及ADC电路320。扫描电路310还可包含放大电路、选择电路(例如多路复用器)等等以沿读出位线160一次读出一行图像数据或可使用各种其它技术读出图像数据,例如串行读出或同时完全并行读出所有像素。在一个实施例中,读出电路130从像素阵列105读出图像数据,其包含从具有设置曝光时间的两个帧读出图像数据。第一帧可具有与第二帧的曝光时间(“Tshort”)相比更长的曝光时间(“Tlong”)。在其它实施例中,第一帧可具有与第二帧的曝光时间(“Tlong”)相比更短的曝光时间(“Tshort”)。扫描电路130获取第一帧的图像数据及第二帧的图像数据。在一个实施例中,第一帧的图像数据可存储于功能逻辑140中。在由像素阵列捕获具有更短或更长曝光时间的第二帧之前,可执行第一帧的图像数据的存储。ADC电路320可将来自扫描电路310的图像数据中的每一者从模拟转换成数字。举例来说,包含于读出电路中的ADC电路320可分别将第一帧的图像数据从模拟转换成数字以获得第一ADC输出且将第二帧的图像数据从模拟转换成数字以获得第二ADC输出。返回参考图1,功能逻辑140可将第一ADC输出与第二ADC输出加总以产生最终ADC输出。外部主机可接着执行HDR组合及线性化。按像素、按像素集群或按子阵列执行HDR组合及线性化。相应地,曝光比率可按像素、按像素集群或按子阵列而改变。举例来说,每一集群(或子阵列)可动态地确定(例如,使用先前帧)较长曝光时间(Tlong)与短曝光时间(Tshort)的比率。

在一个实施例中,像素阵列105可捕获具有长曝光时间的第一帧。读出电路130或功能逻辑140可存储ADC电路320的输出。像素阵列105可接着捕获具有较短曝光时间的第二帧。读出针对第二帧的ADC输出且将其与第一帧的ADC输出加总。在此实施例中,ADC电路320在大小上为9位。针对第一帧及第二帧的ADC输出的加总结果存储于帧缓冲器中。在一个实施例中,加总结果为10位数据且所述帧缓冲器在大小上为10位。外部主机(芯片外)可接着执行加总结果的HDR组合及线性化。

此外,本发明的以下实施例可被描述为过程,其通常被描述为流程图(flowchart或flow diagram)、结构图或框图。尽管流程图可将操作描述为循序过程,但可并行或同时执行许多操作。另外,可重新布置操作的顺序。过程在其操作完成时终止。过程可对应于方法、程序等等。

图4为展示根据本发明的一个实施例的读出被划分成像素子阵列的像素阵列的实例过程的流程图。在所描绘的实例中,应了解,过程可应用于(例如)如上文关于图1及/或图2所描述的像素子阵列。例如,如上文所描述,每一像素子阵列包含多个像素群组,所述多个像素群组中的每一者包含多个像素单元,如上文关于图1及/或图2所详细论述。方法400在框410处以使用像素阵列捕获具有第一曝光时间的第一帧开始。在一个实施例中,像素阵列安置于第一半导体裸片中。在框402处,多个读出电路获取第一帧的图像数据。读出电路包含于安置于第二半导体裸片中的读出电路中。多个像素子阵列中的每一者通过多个导体中的对应一者耦合到多个读出电路中的对应一者。在框403处,包含于读出电路中的多个ADC电路分别将第一帧的图像数据从模拟转换成数字以获得第一ADC输出。在框404处,功能逻辑存储第一ADC输出。功能逻辑可安置于第二半导体裸片中。在一个实施例中,包含于功能逻辑中的帧缓冲器存储第一ADC输出。在框405处,像素阵列捕获具有第二曝光时间的第二帧。第一曝光时间与第二曝光时间相比可更长。在其它实施例中,第一曝光时间与第二曝光时间相比可更短。在框406处,读出电路获取第二帧的图像数据。在框407处,ADC电路将第二帧的图像数据从模拟转换成数字以获得第二ADC输出。在框408处,读出第二ADC输出且功能逻辑将第一ADC输出与第二ADC输出加总以产生最终ADC输出。在框409处,将最终ADC输出存储于包含于功能逻辑中的帧缓冲器中。在框410处,外部主机执行HDR组合及线性化。

在另一实施例中,不同于在框404处功能逻辑存储第一ADC输出,ADC电路包含存储第一ADC输出的帧缓冲器。在此实施例中,ADC电路还包含用于在框408处将第一ADC输出与第二ADC输出加总以产生在框409处存储于ADC电路的帧缓冲器中的最终ADC输出的逻辑栅极。在另一实施例中,在框409处,最终ADC输出也可存储于包含于功能逻辑中的帧缓冲器中。

上文所解释的过程是在计算机软件及硬件方面进行描述的。所描述的技术可构成在机器(例如,计算机)可读存储媒体内体现的机器可执行指令,所述机器可执行指令在由机器执行时将致使所述机器执行所描述的操作。另外,所述过程可在硬件内体现,例如,专用集成电路(“ASIC”)或类似物。

图5(a)及5(b)为说明根据本发明的一个实施例的相对于对应于具有较长曝光时间(Tlong)的帧及具有较短曝光时间(Tshort)的帧的最低有效位(LSB)输出的光照水平的图表。特定来说,图5(a)及5(b)展示对应于较长曝光时间(Tlong)的第一帧及具有较短曝光时间(Tshort)的第二帧的可能的9位ADC输出(例如第一ADC输出及第二ADC输出),以及为第一ADC输出与第二ADC输出的加总结果的10位最终ADC输出。在其它实施例中,第一帧可具有较短曝光时间(“Tshort”)且第二帧可具有较长曝光时间(“Tlong”)。图5(b)进一步说明可由外部主机芯片外执行的HDR组合及线性化的结果。

借助于根据本发明的一个实施例的包含具有像素阵列(其带有以用于堆叠CMOS图像传感器方案中的高动态范围(HDR)的像素架构布置于像素子阵列中的多个像素)的图像传感器的成像系统,可在不增大输出数据速率的情况下增大动态范围。通常,除非在芯片上执行HDR组合,否则必须输出两个或两个以上帧捕获,这增加了复杂性及成本。此外,本文所描述的成像系统及读出方法在不增大ADC电路320的分辨率的情况下增大图像传感器的动态范围。最后,根据本发明的实施例的成像系统及读出方法提供自适应曝光时间及跨越像素阵列的动态范围,且特定来说,提供像素阵列的集群水平控制而非在帧水平上的控制。

不希望本发明的所说明的实例的以上描述(包含摘要中所描述的内容)为穷尽性或限于所揭示的精确形式。尽管本文出于说明性目的描述本发明的特定实施例及本发明的实例,但在不脱离本发明的更广精神及范围的情况下的各种等效修改是可能的。

依据以上详细描述可对本发明的实例做出这些修改。所附权利要求书中使用的术语不应解释为将本发明限于本说明书和权利要求书中所揭示的特定实施例。而是,本发明的范围全部应由所附权利要求书确定,所附权利要求书应根据权利要求解释的既定规则来解释。本说明书及图应相应地被视为说明性的而非限制性的。

- 实施堆叠芯片高动态范围图像传感器的方法及系统

- 包括堆叠的半导体芯片的CMOS图像传感器和包括超晶格的读出电路系统及相关方法