一种复位时间可调的复位电路及设备

文献发布时间:2023-06-19 12:24:27

技术领域

本发明属于集成电路设计技术领域,尤其涉及一种复位时间可调的复位电路及设备。

背景技术

在集成电路设计中,为了保证整个电路状态的确定性,需要对内部电路进行复位。因此,复位电路是集成电路设计中不可缺少的组成部分。

目前,现有的复位电路一般通过一个PMOS管对电容器进行充电,利用电容器的两端电压不能突变的原理,上电时电容器的电压为零,电源通过PMOS管对电容器充电的时间就是复位时间,或者直接使用集成复位IC。

但是,上述复位电路无法解决复位时间可调的问题。

发明内容

有鉴于此,本发明实施例提供了一种复位时间可调的复位电路及设备,以解决现有技术中的复位电路的复位时间不可调的问题。

本发明实施例的第一方面提供了一种复位时间可调的复位电路,包括:

在复位引脚低电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻、第五电阻、第六电阻、第一NPN型三极管、CPU和电源;所述RC回路包括:开关按键、第一电阻、第二电阻、第三电阻和电容;所述电源的正极分别连接所述第四电阻的一端、所述第二电阻的一端和所述开关按键的一端,所述第四电阻的另一端分别连接所述CPU的复位引脚和所述第一NPN型三极管的集电极,所述第二电阻的另一端分别连接所述第三电阻的一端和所述比较器的负极输入端,所述开关按键的另一端连接所述第一电阻的一端,所述第一电阻的另一端分别连接所述电容的一端和所述比较器的正极输入端,所述电容的另一端、所述第三电阻的另一端、所述第六电阻的一端和所述第一NPN型三极管的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻的一端,所述第五电阻的另一端连接所述第六电阻的另一端和所述第一NPN型三极管的基极;

或,

在复位引脚低电平有效的情况下,所述复位电路包括:RC回路、PNP型三极管、第四电阻、第五电阻、第六电阻、第一NPN型三极管、CPU和电源;所述RC回路包括:开关按键、第一电阻、第二电阻、第三电阻和电容;所述电源的正极分别连接所述第四电阻的一端、所述第二电阻的一端、所述第六电阻的一端和所述开关按键的一端,所述第四电阻的另一端分别连接所述CPU的复位引脚和所述PNP型三极管的集电极,所述第二电阻的另一端连接所述第一NPN型三极管的集电极,所述开关按键的另一端连接所述第一电阻的一端,所述第一电阻的另一端分别连接所述电容的一端和所述第一NPN型三极管的基极,所述第三电阻的一端连接所述第一NPN型三极管的基极,所述电容的另一端、所述第三电阻的另一端、所述第一NPN型三极管的发射极和所述PNP型三极管的发射极均接所述电源的负极,所述PNP型三极管的基极连接所述第五电阻的一端,所述第五电阻的另一端连接所述第一NPN型三极管的集电极和所述第六电阻的另一端;

在复位引脚高电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻、第五电阻、第六电阻、PNP型三极管、CPU和电源;所述RC回路包括:开关按键、第一电阻、第二电阻、第三电阻和电容;所述电源的正极分别连接所述第四电阻的一端、所述第二电阻的一端和所述开关按键的一端,所述第四电阻的另一端分别连接所述CPU的复位引脚和所述PNP型三极管的集电极,所述第二电阻的另一端分别连接所述第三电阻的一端和所述比较器的负极输入端,所述开关按键的另一端连接所述第一电阻的一端,所述第一电阻的另一端分别连接所述电容的一端和所述比较器的正极输入端,所述电容的另一端、所述第三电阻的另一端、所述第六电阻的一端和所述PNP型三极管的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻的一端,所述第五电阻的另一端连接所述第六电阻的另一端和所述PNP型三极管的基极;

或,

在复位引脚高电平有效的情况下,所述复位电路包括:RC回路、比较器、非门、第四电阻、第五电阻、第六电阻、第一NPN型三极管、CPU和电源;所述RC回路包括:开关按键、第一电阻、第二电阻、第三电阻和电容;所述电源的正极分别连接所述第四电阻的一端、所述第二电阻的一端和所述开关按键的一端,所述第四电阻的另一端分别连接所述CPU的复位引脚和所述第一NPN型三极管的集电极,所述第二电阻的另一端分别连接所述第三电阻的一端和所述比较器的负极输入端,所述开关按键的另一端连接所述第一电阻的一端,所述第一电阻的另一端分别连接所述电容的一端和所述比较器的正极输入端,所述电容的另一端、所述第三电阻的另一端、所述第六电阻的一端和所述第一NPN型三极管的发射极均接所述电源的负极,所述比较器的输出端连接所述非门的输入端,所述非门的输出端连接所述第五电阻的一端,所述第五电阻的另一端连接所述第六电阻的另一端和所述第一NPN型三极管的基极。

本发明实施例的第二方面提供了一种设备,包括本发明实施例的第一方面所述的复位时间可调的复位电路。

本发明实施例与现有技术相比存在的有益效果是:

本发明实施例的一种复位时间可调的复位电路,包括:在复位引脚低电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻、第五电阻、第六电阻、第一NPN型三极管、CPU和电源;所述RC回路包括:开关按键、第一电阻、第二电阻、第三电阻和电容;所述电源的正极分别连接所述第四电阻的一端、所述第二电阻的一端和所述开关按键的一端,所述第四电阻的另一端分别连接所述CPU的复位引脚和所述第一NPN型三极管的集电极,所述第二电阻的另一端分别连接所述第三电阻的一端和所述比较器的负极输入端,所述开关按键的另一端连接所述第一电阻的一端,所述第一电阻的另一端分别连接所述电容的一端和所述比较器的正极输入端,所述电容的另一端、所述第三电阻的另一端、所述第六电阻的一端和所述第一NPN型三极管的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻的一端,所述第五电阻的另一端连接所述第六电阻的另一端和所述第一NPN型三极管的基极。本发明通过比较器、LC回路和MOS管的结合,有效提高了复位电路的可靠性以及抗ESD能力强。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

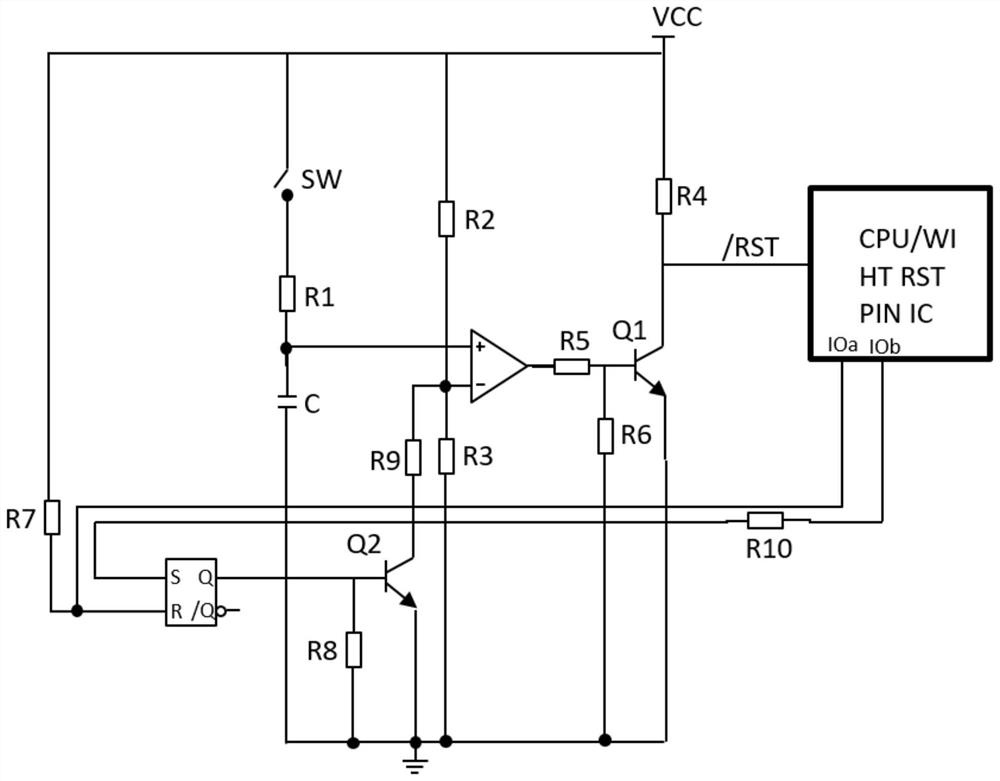

图1是本发明一实施例提供的一种复位时间可调的复位电路示意图;

图2是本发明另一实施例提供的一种复位时间可调的复位电路示意图;

图3是本发明另一实施例提供的一种复位时间可调的复位电路示意图;

图4是本发明另一实施例提供的一种复位时间可调的复位电路示意图。

具体实施方式

以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

为了说明本发明所述的技术方案,下面通过具体实施例来进行说明。

本发明一实施例提供一种复位时间可调的复位电路。该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST低电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q1、CPU和电源;所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述第一NPN型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻R6的一端和所述第一NPN型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻R6的另一端和所述第一NPN型三极管Q1的基极。

具体地,所述在复位引脚RST低电平有效的情况下,长按开关按键SW,所述RC回路给所述电容C充电;

在所述电容C的电压大于所述比较器的负极输入端的电压的情况下,所述比较器的输出端输出高电平,所述第一NPN型三极管Q1导通,所述复位引脚RST为低电平,所述CPU实现复位。

本发明另一实施例提供一种复位时间可调的复位电路。该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST低电平有效的情况下,所述复位电路包括:RC回路、PNP型三极管Q1、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q3、CPU和电源;所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端、第六电阻的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚和所述PNP型三极管Q1的集电极,所述第二电阻R2的另一端连接所述第一NPN型三极管Q3的集电极,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述第一NPN型三极管Q3的基极,所述第三电阻R3的一端连接所述第一NPN型三极管Q3的基极,所述电容C的另一端、所述第三电阻R3的另一端、所述第一NPN型三极管Q3的发射极和所述PNP型三极管Q1的发射极均接所述电源的负极,所述PNP型三极管Q1的基极连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第一NPN型三极管Q3的集电极和所述第六电阻的另一端。

具体地,所述在复位引脚RST低电平有效的情况下,长按开关按键SW,所述RC回路给所述电容C充电;

在所述电容C的电压大于所述PNP型三极管Q1的发射极的电压的情况下,所述PNP型三极管Q1的基极为高电平,所述第一NPN型三极管Q3导通,所述复位引脚RST为低电平,所述CPU实现复位。

本发明另一实施例提供一种复位时间可调的复位电路。该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST高电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻R4、第五电阻R5、第六电阻R6、PNP型三极管Q1、CPU和电源;所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述PNP型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻的一端和所述PNP型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻的另一端和所述PNP型三极管Q1的基极。

具体地,所述在复位引脚RST高电平有效的情况下,长按开关按键SW,所述RC回路给所述电容C充电;

在所述电容C的电压大于所述比较器的负极输入端的电压的情况下,所述比较器的输出端输出高电平,所述高电平经所述非门后变为低电平,所述PNP型三极管Q1截止,所述复位引脚RST为高电平,所述CPU实现复位。

本发明另一实施例提供一种复位时间可调的复位电路。该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST高电平有效的情况下,所述复位电路包括:RC回路、比较器、非门、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q1、CPU和电源;所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述第一NPN型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电R1阻的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻的一端和所述第一NPN型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述非门的输入端,所述非门的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻的另一端和所述第一NPN型三极管Q1的基极。

具体地,所述在复位引脚RST高电平有效的情况下,长按开关按键SW,所述RC回路给所述电容C充电;

在所述电容C的电压大于所述比较器的负极输入端的电压的情况下,所述比较器的输出端输出高电平,所述第一NPN型三极管Q1截止,所述复位引脚RST为高电平,所述CPU实现复位。

上述实施例中的复位电路的复位时间可通过硬件进行调整,即通过调整R1、C、R2和R3的值来调整复位的时间,下面提供一种复位时间通过软件进行调整的复位电路。

图1是本发明一实施例提供一种复位时间可调的复位电路。结合图1所示,该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST低电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q1、CPU、SR触发器、第七电阻R7、第八电阻R8、第九电阻R9、第十电阻R10、第二NPN型三极管Q2和电源;

所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述第一NPN型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻R6的一端和所述第一NPN型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻R6的另一端和所述第一NPN型三极管Q1的基极;

所述CPU的第一IO引脚IOa分别连接所述第七电阻R7的另一端和所述SR触发器的R端,所述第七电阻R7的一端连接所述电源的正极,所述SR触发器的S端连接所述第十电阻R10的一端,所述第十电阻R10的另一端连接所述CPU的第二IO引脚IOb,所述SR触发器的Q端连接所述第二NPN型三极管Q2的基极,所述第二NPN型三极管Q2的基极还连接所述第八电阻R8的一端,所述第八电阻R8的另一端和所述第二NPN型三极管Q2的发射极均接所述电源的负极,所述第二NPN型三极管Q2的集电极连接所述第九电阻R9的一端,所述第九电阻R9的另一端连接所述第三电阻R3的一端。

具体地,开关按键SW未按下时,比较器输出低电平,NPN型三极管截止,复位引脚RST输出高电平,CPU正常工作;开关按键SW短按时,电容C充电时间较短,正向电压小于负向电压,比较器输出低电平,NPN型三极管截止,复位引脚RST输出高电平,系统正常工作。

在一实施例中,在所述SR触发器中的R=0,S=1的情况下,SR触发器的Q端输出低电平,所述第二NPN型三极管Q2截止,所述比较器的负极输入端的电压为第一电压;

在所述SR触发器中的R=1,S=0的情况下,SR触发器的Q端输出高电平,所述第二NPN型三极管Q2导通,所述比较器的负极输入端的电压为第二电压,其中,所述第二电压小于所述第一电压。

具体地,在所述CPU发生意外崩溃的情况下,SR触发器的Q端的输出电压不变,以保证所述CPU正常工作。或,在所述CPU发生意外崩溃的情况下,按开关按键强制复位,以保证所述CPU正常工作。

图2是本发明另一实施例提供一种复位时间可调的复位电路。结合图2所示,该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST低电平有效的情况下,所述复位电路包括:RC回路、PNP型三极管Q1、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q3、CPU、电源、SR触发器、第七电阻R7、第八电阻R8、第九电阻R9、第十电阻R10和第二NPN型三极管Q2;

所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端、第六电阻的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚和所述PNP型三极管Q1的集电极,所述第二电阻R2的另一端连接所述第一NPN型三极管Q3的集电极,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述第一NPN型三极管Q3的基极,所述第三电阻R3的一端连接所述第一NPN型三极管Q3的基极,所述电容C的另一端、所述第三电阻R3的另一端、所述第一NPN型三极管Q3的发射极和所述PNP型三极管Q1的发射极均接所述电源的负极,所述PNP型三极管Q1的基极连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第一NPN型三极管Q3的集电极和所述第六电阻的另一端;

所述CPU的第一IO引脚IOa分别连接所述第七电阻R7的另一端和所述SR触发器的R端,所述第七电阻R7的一端和所述第二NPN型三极管Q2的集电极均连接所述电源的正极,所述SR触发器的S端连接所述第十电阻R10的一端,所述第十电阻R10的另一端连接所述CPU的第二IO引脚IOb,所述SR触发器的Q端分别连接所述第二NPN型三极管Q2的基极和所述第八电阻R8的一端,所述第八电阻R8的另一端连接所述电源的负极,所述第二NPN型三极管Q2的发射极连接所述第九电阻R9的一端,所述第九电阻R9的另一端连接所述第三电阻R3的一端。

在一实施例中,在所述SR触发器中的R=0,S=1的情况下,SR触发器的Q端输出低电平,所述第二NPN型三极管Q2截止,所述第一NPN型三极管Q3的基极达到高电平的时间为第一时间;

在所述SR触发器中的R=1,S=0的情况下,SR触发器的Q端输出高电平,所述第二NPN型三极管Q2导通,所述第一NPN型三极管Q3的基极达到高电平的时间为第二时间,所述第二时间小于所述第一时间。

具体地,在所述CPU发生意外崩溃的情况下,SR触发器的Q端的输出电压不变,以保证所述CPU正常工作。或,在所述CPU发生意外崩溃的情况下,按开关按键强制复位,以保证所述CPU正常工作。

图3是本发明一实施例提供一种复位时间可调的复位电路。结合图3所示,该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST高电平有效的情况下,所述复位电路包括:RC回路、比较器、第四电阻R4、第五电阻R5、第六电阻R6、PNP型三极管Q1、CPU和电源、SR触发器、第七电阻R7、第八电阻R8、第九电阻R9、第十电阻R10和第二NPN型三极管Q2;

所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述PNP型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电阻R1的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻的一端和所述PNP型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻的另一端和所述PNP型三极管Q1的基极;

所述CPU的第一IO引脚IOa分别连接所述第七电阻R7的另一端和所述SR触发器的R端,所述第七电阻R7的一端连接所述电源的正极,所述SR触发器的S端连接所述第十电阻R10的一端,所述第十电阻R10的另一端连接所述CPU的第二IO引脚IOb,所述SR触发器的Q端连接所述第二NPN型三极管Q2的基极,所述第二NPN型三极管Q2的基极还连接所述第八电阻R8的一端,所述第八电阻R8的另一端和所述第二NPN型三极管Q2的发射极均接所述电源的负极,所述第二NPN型三极管Q2的集电极连接所述第九电阻R9的一端,所述第九电阻R9的另一端连接所述第三电阻R3的一端。

在一实施例中,在所述SR触发器中的R=0,S=1的情况下,SR触发器的Q端输出低电平,所述第二NPN型三极管Q2截止,所述比较器的负极输入端的电压为第一电压;

在所述SR触发器中的R=1,S=0的情况下,SR触发器的Q端输出高电平,所述第二NPN型三极管Q2导通,所述比较器的负极输入端的电压为第二电压,其中,所述第二电压小于所述第一电压。

具体地,在所述CPU发生意外崩溃的情况下,SR触发器的Q端的输出电压不变,以保证所述CPU正常工作。或,在所述CPU发生意外崩溃的情况下,按开关按键强制复位,以保证所述CPU正常工作。

图4是本发明一实施例提供一种复位时间可调的复位电路。结合图4所示,该实施例的一种复位时间可调的复位电路包括:

在复位引脚RST高电平有效的情况下,所述复位电路包括:RC回路、比较器、非门、第四电阻R4、第五电阻R5、第六电阻R6、第一NPN型三极管Q1、CPU、电源、SR触发器、第七电阻R7、第八电阻R8、第九电阻R9、第十电阻R10和第二NPN型三极管Q2;

所述RC回路包括:开关按键SW、第一电阻R1、第二电阻R2、第三电阻R3和电容C;所述电源的正极分别连接所述第四电阻R4的一端、所述第二电阻R2的一端和所述开关按键SW的一端,所述第四电阻R4的另一端分别连接所述CPU的复位引脚RST和所述第一NPN型三极管Q1的集电极,所述第二电阻R2的另一端分别连接所述第三电阻R3的一端和所述比较器的负极输入端,所述开关按键SW的另一端连接所述第一电R1阻的一端,所述第一电阻R1的另一端分别连接所述电容C的一端和所述比较器的正极输入端,所述电容C的另一端、所述第三电阻R3的另一端、所述第六电阻的一端和所述第一NPN型三极管Q1的发射极均接所述电源的负极,所述比较器的输出端连接所述非门的输入端,所述非门的输出端连接所述第五电阻R5的一端,所述第五电阻R5的另一端连接所述第六电阻的另一端和所述第一NPN型三极管Q1的基极;

所述CPU的第一IO引脚IOa分别连接所述第七电阻R7的另一端和所述SR触发器的R端,所述第七电阻R7的一端连接所述电源的正极,所述SR触发器的S端连接所述第十电阻R10的一端,所述第十电阻R10的另一端连接所述CPU的第二IO引脚IOb,所述SR触发器的Q端连接所述第二NPN型三极管Q2的基极,所述第二NPN型三极管Q2的基极还连接所述第八电阻R8的一端,所述第八电阻R8的另一端和所述第二NPN型三极管Q2的发射极均接所述电源的负极,所述第二NPN型三极管Q2的集电极连接所述第九电阻R9的一端,所述第九电阻R9的另一端连接所述第三电阻R3的一端。

在一实施例中,在所述SR触发器中的R=0,S=1的情况下,SR触发器的Q端输出低电平,所述第二NPN型三极管Q2截止,所述比较器的负极输入端的电压为第一电压;

在所述SR触发器中的R=1,S=0的情况下,SR触发器的Q端输出高电平,所述第二NPN型三极管Q2导通,所述比较器的负极输入端的电压为第二电压,其中,所述第二电压小于所述第一电压。

具体地,在所述CPU发生意外崩溃的情况下,SR触发器的Q端的输出电压不变,以保证所述CPU正常工作。或,在所述CPU发生意外崩溃的情况下,按开关按键强制复位,以保证所述CPU正常工作。

本发明一实施例还提供了一种设备,所述设备包括上述任一所述的复位时间可调的复位电路。

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

- 一种复位时间可调的复位电路及设备

- 一种复位时间可调的复位电路