半导体装置及其制造方法

文献发布时间:2023-06-19 19:14:59

技术领域

本公开的示例性实施方式涉及包括重分布焊盘的半导体装置以及制造该半导体装置的方法。

背景技术

随着半导体装置尺寸的减小,用于电连接的接合焊盘的数量增加,并且接合焊盘之间的间隙减小。

发明内容

根据本公开的实施方式,一种半导体装置包括:芯片主体;钝化层,其位于芯片主体上;下介电层,其位于钝化层上;第一重分布焊盘,其位于下介电层上;上介电层,其位于下介电层上,上介电层具有暴露出第一重分布焊盘的上表面的凹槽;以及第二重分布焊盘,其位于上介电层上。第二重分布焊盘的上表面比第一重分布焊盘的上表面定位在更高的高度(level)处。

根据本公开的实施方式,一种半导体装置包括:芯片主体,其具有第一金属焊盘及第二金属焊盘;钝化层,其位于芯片主体上;下介电层,其位于钝化层上;第一重分布焊盘,其位于下介电层上;上介电层,其位于下介电层上,上介电层具有暴露出第一重分布焊盘的上表面的凹槽;以及第二重分布焊盘,其位于上介电层上。第一重分布焊盘包括:第一通孔部分,其竖直贯穿下介电层和钝化层,以与第一金属焊盘联接;以及第一延伸部分,其从第一通孔部分沿第一水平方向延伸。第二重分布焊盘包括:第二通孔部分,其竖直贯穿上介电层、下介电层和钝化层,以与第二金属焊盘联接;以及第二延伸部分,其从第二通孔部分沿第一水平方向延伸。

根据本公开的实施方式,一种半导体装置包括:下介电层,其被设置在芯片主体上;多个第一重分布焊盘,其被设置在下介电层上;上介电层,其被设置在下介电层上,上介电层具有暴露出第一重分布焊盘的凹槽;以及多个第二重分布焊盘,其被设置在上介电层上。第一重分布焊盘和第二重分布焊盘沿第一水平方向平行延伸。第一重分布焊盘和第二重分布焊盘在第二水平方向上交替地设置。第一水平方向与第二水平方向彼此垂直。

根据本公开的又一实施方式,一种制造半导体装置的方法包括以下步骤:制备具有第一金属焊盘和第二金属焊盘的芯片主体;在芯片主体上形成钝化层;在钝化层上形成下介电层;在下介电层上形成第一重分布焊盘;在下介电层上形成上介电层,上介电层具有暴露出第一重分布焊盘的上表面的凹槽;以及在上介电层上形成第二重分布焊盘。

附图说明

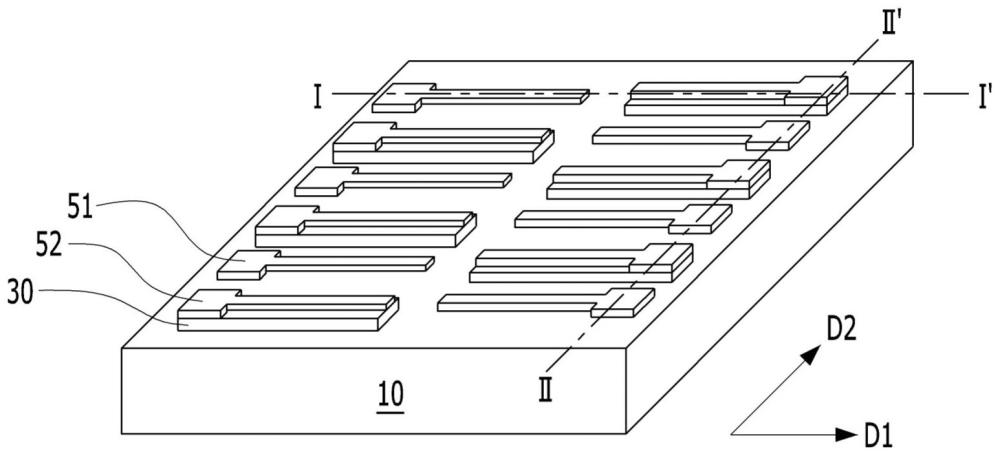

图1A是例示了根据本公开实施方式的半导体装置的立体图。

图1B是沿图1A所示的线I-I′截取的半导体装置的纵向截面图。

图1C是沿图1A所示的线II-II′截取的半导体装置的纵向截面图。

图2A是例示了引线接合在电路板上的半导体装置的示意性立体图。

图2B是例示了上面形成有芯片引线基座的重分布焊盘的侧面图。

图3A是沿图1A所示的线I-I′截取的根据本公开的实施方式的半导体装置的纵向截面图。

图3B是沿图1A所示的线I-I′截取的根据本公开的实施方式的半导体装置的纵向截面图。

图4A至图4L、图5A至图5H和图6A至图6F是例示了根据本公开的不同实施方式的制造半导体装置的方法的纵向截面图。

具体实施方式

下面将参照附图更详细地描述本公开的示例性实施方式。然而,本公开可以以不同形式来体现并且不应被解释为限于在此阐述的实施方式。相反,提供这些实施方式是为了使本公开更加透彻和完整,并将本公开的范围完整地传达给本领域的技术人员。本发明的精神和范围如权利要求中所定义。

本公开的实施方式提供了包括设置在不同高度的重分布焊盘的半导体装置。

本公开的实施方式提供了制造包括设置在不同高度的重分布焊盘的半导体装置的方法。

图1A是例示了根据本公开实施方式的半导体装置的立体图。参照图1A,半导体装置可以包括设置在芯片主体10上的多个提升层(lift-up layer)30、多个第一重分布焊盘51和多个第二重分布焊盘52。提升层30可以包括介电材料,并且第一重分布焊盘51和第二重分布焊盘52可以包括导电材料。第二重分布焊盘52可以设置在提升层30上。因此,第二重分布焊盘52可以设置在比第一重分布焊盘51高的高度。第一重分布焊盘51和第二重分布焊盘52中的每一个可以从芯片主体10的中央沿第一水平方向D1朝向边缘延伸。第一重分布焊盘51和第二重分布焊盘52可以在第二水平方向D2上交替地设置成彼此相邻。第一水平方向D1和第二水平方向D2可以彼此垂直。

图1B是沿图1A所示的线I-I′截取的半导体装置的纵向截面图。图1C是沿图1A所示的线II-II′截取的半导体装置的纵向截面图。参照图1B和图1C,根据本公开的示例性实施方式的半导体装置可以包括芯片主体10、设置在第一区域R1中的第一重分布焊盘51以及设置在第二区域R2中的第二重分布焊盘52。芯片主体10可以包括硅基板、硅基板上的晶体管、金属互连层和层间介电层。芯片主体10可以包括在第一区域R1中的第一金属焊盘15a和在第二区域R2中的第二金属焊盘15b。第一金属焊盘15a和第二金属焊盘15b可以设置在芯片主体10的中央附近。第一金属焊盘15a和第二金属焊盘15b可以对应于芯片主体10中的金属互连层当中的顶部金属互连层。例如,第一金属焊盘15a和第二金属焊盘15b可以包括输入/输出焊盘。第一金属焊盘15a和第二金属焊盘15b可以包括诸如铝(Al)、镍(Ni)、铜(Cu)或钨(W)之类的金属、诸如钛铝(TiAl)之类的金属合金、或者诸如氮化钛(TiN)之类的金属化合物当中的至少一种。第一重分布焊盘51和第二重分布焊盘52可以包括具有高导电性的金属,诸如金(Au)、银(Ag)或铜(Cu)。

半导体装置还可以包括形成在芯片主体10上的钝化层20、形成在钝化层20上的下介电层31、以及形成在下介电层31上的上介电层33。钝化层20可以暴露出第一金属焊盘15a的上表面和第二金属焊盘15b的上表面。上介电层33可以对应于图1的提升层30。钝化层20、下介电层31和上介电层33中的每一个可以包括诸如氧化硅(SiO

第一重分布焊盘51可以包括竖直贯穿下介电层31以与第一金属焊盘15a联接的第一通孔部分51v、设置在下介电层31上以从第一通孔部分51v水平延伸的第一延伸部分51e、以及对应于第一延伸部分51e的端部的第一焊盘部分51p。第一通孔部分51v、第一延伸部分51e和第一焊盘部分51p的上表面可以是共面的。例如,第一通孔部分51v可以设置在芯片主体10的中央附近,并且第一焊盘部分51p可以设置在芯片主体10的边缘附近。第二重分布焊盘52可以包括竖直贯穿上介电层33和下介电层31以与第二金属焊盘15b联接的第二通孔部分52v、设置在上介电层33上以从第二通孔部分52v水平延伸的第二延伸部分52e、以及对应于第二延伸部分52e的端部的第二焊盘部分52p。第二通孔部分52v、第二延伸部分52e和第二焊盘部分52p的上表面可以是共面的。例如,第二通孔部分52v可以设置在芯片主体10的中央附近,并且第二焊盘部分52p可以设置在芯片主体10的边缘附近。

第一重分布焊盘51的第一延伸部分51e和第一焊盘部分51p可以设置在下介电层31上。下介电层31可以围绕第一重分布焊盘51的第一通孔部分51v的所有侧表面的下部部分和第二重分布焊盘52的第二通孔部分52v的侧表面的下部部分。上介电层33可以覆盖第一重分布焊盘51的侧表面。例如,上介电层33可以与第一重分布焊盘51的第一焊盘部分51p和第一延伸部分51e的侧表面接触。上介电层33可以与第一重分布焊盘51的第一通孔部分51v的侧表面的上部部分接触。上介电层33可以具有暴露出第一重分布焊盘51的上表面的凹槽G。上介电层33可以围绕第二重分布焊盘52的第二通孔部分52v的侧表面的上部部分。第二重分布焊盘52的第二延伸部分52e和第二焊盘部分52p可以设置在上介电层33上。因此,第二重分布焊盘52的第二延伸部分52e和第二焊盘部分52p可以定位在比第一重分布焊盘51的第一延伸部分51e和第一焊盘部分51p高的高度处。第二重分布焊盘52的上表面可以定位在比第一重分布焊盘51的上表面高的高度处。第二重分布焊盘52的第二通孔部分52v可以比第一重分布焊盘51的第一通孔部分51v大(更高或更长)。

下金属衬件41可以共形地形成在第一重分布焊盘51的下表面上,并且上金属衬件42可以共形地形成在第二重分布焊盘52的下表面上。下金属衬件41和上金属衬件42可以包括单个金属层或多个金属层。例如,下金属衬件41和上金属衬件42可以包括Ti层和Ti合金层。下金属衬件41和上金属衬件42可以用作阻挡金属层和种子金属层。

图2A是例示了引线接合在电路板70上的半导体装置的示意性立体图。图2B是例示了上面形成有芯片引线基座(chip wire base)71b、72b的重分布焊盘51和52的侧面图。参照图2A,根据本公开的实施方式的半导体装置可以通过使用第一引线71a和第二引线72a电接合并且物理接合到电路板70。第一基板接合焊盘73和第二基板接合焊盘74可以设置在电路板70上。第一基板引线基座71c可以形成在第一基板接合焊盘73上,并且第二基板引线基座72c可以形成在第二基板接合焊盘74上。第一芯片引线基座71b可以形成在第一重分布焊盘51的第一焊盘部分51p上,并且第二芯片引线基座72b可以形成在第二重分布焊盘52的第二焊盘部分52p上。第一引线71a可以将第一基板引线基座71c联接至第一芯片引线基座71b。第二引线72a可以将第二基板引线基座72c联接至第二芯片引线基座72b。引线基座71b、71c、72b和72c可以是引线材料熔融的结果。引线基座71b、71c、72b和72c可以使焊盘51、52、73和74以及引线71a和72a具有低电阻并且彼此稳定地接合。引线基座71b、71c、72b和72c可以具有半球形形状。为了稳定连接,可能希望引线基座71b、71c、72b和72c具有足够的体积,并且还可能希望引线基座71b、71c、72b和72c与相邻的第一重分布焊盘51和第二重分布焊盘52以及相邻的第一芯片引线基座71b和第二芯片引线基座72b间隔开,以便不会电短路,并且也不造成电干扰。

图3A是沿图1A所示的线I-I′截取的根据本公开的实施方式的半导体装置的纵向截面图。参照图3A,与图1所示的半导体装置相比,半导体装置还可以包括具有第一连接孔81和第二连接孔82的保护介电层35。第一连接孔81可以暴露出第一重分布焊盘51的第一焊盘部分51p。第二连接孔82可以暴露出第二重分布焊盘52的第二焊盘部分52p。保护介电层35可以包括可以形成上介电层33的材料中的一种。第一连接孔81和第二连接孔82可以界定第一芯片引线基座71b和第二芯片引线基座72b(如图2A和图2B所示)。因此,可以防止第一芯片引线基座71b与第二芯片引线基座72b之间的电短路和电干扰。

图3B是沿图1A所示的线I-I′截取的根据本公开的实施方式的半导体装置的纵向截面图。参照图3B,与图3A所示的半导体装置相比,半导体装置还可以包括第一柱91和第二柱92。第一柱91可以包括第一支柱91a和第一接合部分91b,并且第二柱92可以包括第二支柱92a和第二接合部分92b。第一支柱91a可以形成在第一连接孔81中以联接到第一重分布焊盘51,并且第二支柱92a可以形成在第二连接孔82中以联接到第二重分布焊盘52。第一柱91的上端和第二柱92的上端可以定位在同一高度处。例如,第一柱91可以比第二柱92大(更高或更长)。第一接合部分91b可以形成在第一支柱91a上,以提供化学稳定性和物理接合稳定性,并且第二接合部分92b可以形成在第二支柱92a上,以提供化学稳定性和物理接合稳定性。第一柱91和第二柱92可以提供用于倒装芯片接合(flip chip bonding)的结构。第一支柱91a和第二支柱92a可以包括诸如铜(Cu)之类的金属。第一接合部分91b和第二接合部分92b可以包括诸如锡(Sn)之类的焊料材料。

图4A至图4L是例示了根据本公开的实施方式的制造半导体装置的方法的纵向截面图。参照图4A,制造半导体装置的方法可以包括:提供具有形成在第一区域R1中的第一金属焊盘15a和形成在第二区域R2中的第二金属焊盘15b的芯片主体10,以及在芯片主体10的形成有第一金属焊盘15a和第二金属焊盘15b的上表面上形成具有第一开口O1和第二开口O2的钝化层20。形成钝化层20的步骤可以包括执行沉积工艺或涂覆工艺,以形成无机介电材料或聚合物有机介电材料。形成第一开口O1和第二开口O2的步骤可以包括执行光刻工艺以选择性地去除钝化层20,以暴露出第一金属焊盘15a和第二金属焊盘15b。

参照图4B,该方法还可以包括在钝化层20上形成具有第一下孔H1a和第二下孔H1b的下介电层31。形成下介电层31的步骤可以包括:执行沉积工艺或涂覆工艺以形成无机介电材料层或有机介电材料层,以及执行图案化工艺以形成分别暴露出第一金属焊盘15a和第二金属焊盘15b的第一下孔H1a和第二下孔H1b。第一下孔H1a可以与第一开口O1交叠并且暴露出第一金属焊盘15a。第二下孔H1b可以与第二开口O2交叠并且暴露出第二金属焊盘15b。

参照图4C,该方法还可以包括形成下金属衬件41。形成下金属衬件41的步骤可以包括通过执行诸如溅射之类的物理气相沉积(PVD)工艺来形成包括钛(Ti)的金属层。下金属衬件41可以共形地形成在第一金属焊盘15a和第二金属焊盘15b的上表面、第一下孔H1a和第二下孔H1b的侧壁以及下介电层31的上表面上。钝化层20和下介电层31的侧表面可以暴露在第一下孔H1a和第二下孔H1b中。形成下金属衬件41的步骤可以包括形成Ti层以及在Ti层上形成TiW层。

参照图4D,该方法还可以包括形成具有第一沟槽T1的第一掩模图案M1。第一沟槽T1可以在第一区域R1中暴露出下金属衬件41。形成第一掩模图案M1的步骤可以包括完全涂覆诸如光刻胶之类的有机材料,以及执行光刻工艺以形成第一沟槽T1。

参照图4E,该方法还可以包括在第一沟槽T1中形成第一重分布焊盘51。形成第一重分布焊盘51的步骤可以包括执行镀覆工艺。第一重分布焊盘51可以包括诸如金(Au)、银(Ag)或铜(Cu)之类的金属。

参照图4F,该方法还可以包括去除第一掩模图案M1。去除第一掩模图案M1的步骤可以包括通过使用氧等离子体来执行灰化工艺。第一掩模图案M1可以被去除以暴露出下金属衬件41。

参照图4G,该方法还可以包括去除暴露出的下金属衬件41。下金属衬件41可以仅保留在第一重分布焊盘51的下部部分中。去除下金属衬件41的步骤可以包括执行湿法蚀刻工艺或湿法清洁工艺。

参照图4H,该方法还可以包括形成具有凹槽G和上孔H2的上介电层33。形成上介电层33的步骤可以包括:执行沉积工艺或涂覆工艺以形成无机介电材料层或有机介电材料层,以及执行图案化工艺以形成凹槽G和上孔H2。凹槽G可以暴露出第一重分布焊盘51。上孔H2可以与第二下孔H1b交叠以暴露出第二金属焊盘15b的表面。

参照图4I,该方法还可以包括在整个表面上形成上金属衬件42。形成上金属衬件42的工艺可以与形成下金属衬件41的工艺相同。上金属衬件42可以共形地形成在第一重分布焊盘51的在凹槽G中暴露出的上表面、凹槽G的侧表面、第二金属焊盘15b的上表面、第一下孔H1b和上孔H2的侧壁以及上介电层33的上表面上。钝化层20、下介电层31和上介电层33的侧表面可以暴露在第二下孔H1b和上孔H2中。

参照图4J,该方法还可以包括形成具有第二沟槽T2的第二掩模图案M2。第二沟槽T2可以在第二区域R2中暴露出上金属衬件42。形成第二掩模图案M2的步骤可以包括:在整个上金属衬件42上涂覆有机材料(诸如光刻胶),以及执行光刻工艺以形成第二沟槽T2。第二掩模图案M2可以填充凹槽G。第二下孔H1b和上孔H2可以暴露在第二沟槽T2中。

参照图4K,该方法还可以包括在上孔H2、第二下孔H1b和第二沟槽T2中形成第二重分布焊盘52。形成第二重分布焊盘52的步骤可以包括执行镀覆工艺。第二重分布焊盘52可以包括诸如金(Au)、银(Ag)或铜(Cu)之类的金属。

参照图4L,该方法还可以包括去除第二掩模图案M2。上金属衬件42可以被暴露出来。

随后,参照图1B,该方法还可以包括去除暴露出的上金属衬件42。上金属衬件42可以仅保留在第二重分布焊盘52的下部部分中。

图5A至图5H是例示了根据本公开的实施方式的制造半导体装置的方法的纵向截面图。参照图5A,制造半导体装置的方法可以包括:制备具有形成在第一区域R1中的第一金属焊盘15a和形成在第二区域R2中的第二金属焊盘15b的芯片主体10,以及在芯片主体10的形成有第一金属焊盘15a和第二金属焊盘15b的上表面上形成具有第一开口O1的钝化层20,该第一开口O1暴露出第一金属焊盘15a的上表面。与图4A相比,可以不形成第二开口O2。

参照图5B,该方法还可以包括在钝化层20上形成具有第一下孔H1a的下介电层31。与图4B相比,可以不形成第二下孔H1b。

参照图5C,该方法可以包括在第一金属焊盘15a的上表面、第一下孔H1a的侧壁和下介电层31的上表面上共形地形成下金属衬件41。

参照图5D,该方法还可以包括形成具有第一沟槽T1的第一掩模图案M1。第一沟槽T1可以在第一区域R1中暴露出下金属衬件41。

参照图5E,该方法还可以包括在第一沟槽T1中形成第一重分布焊盘51。

参照图5F,该方法还可以包括去除第一掩模图案M1。第一掩模图案M1可以被去除以暴露出下金属衬件41。

参照图5G,该方法还可以包括去除暴露出的下金属衬件41以形成第一重分布焊盘51。

参照图5H,该方法可以包括形成具有上孔H2和凹槽G的上介电层。上孔H2可以暴露出第二金属焊盘15b的上表面,并且凹槽G可以暴露出第一重分布焊盘51的上表面。

随后,该方法还可以包括执行参照图4I至图4L描述的工艺,以形成如图1A至图1C所示的半导体装置。

图6A至图6F是例示了根据本公开的实施方式的制造半导体装置的方法的纵向截面图。参照图6A,制造半导体装置的方法可以包括:执行参照图5A至图5G描述的工艺,以及在第一重分布焊盘51和下介电层31上形成具有上孔H2的上介电层33。与图5H相比,可以不形成凹槽G。

参照图6B,该方法还可以包括在第二金属焊盘15b的上表面、上孔H2的内壁和上介电层33的上表面上共形地形成上金属衬件42。

参照图6C,该方法还可以包括形成具有第二沟槽T2的第二掩模图案M2。第二沟槽T2可以在第二区域R2中暴露出上金属衬件42。上孔H2可以暴露在第二沟槽T2中。

参照图6D,该方法还可以包括在上孔H2和第二沟槽T2中形成第二重分布焊盘52。

参照图6E,该方法还可以包括去除第二掩模图案M2以及去除暴露出的上金属衬件42。

参照图6F,该方法还可以包括形成第三掩模图案M3,以及执行蚀刻工艺以选择性地去除上介电层33以形成暴露出第一重分布焊盘51的凹槽G。

随后,该方法还可以包括去除第三掩模图案M3以形成如图1A至图1C所示的半导体装置。

根据本公开的实施方式,由于半导体装置具有设置在不同高度的重分布焊盘,因此芯片引线基座可以彼此充分地间隔开。换言之,根据本公开的实施方式的半导体装置可以防止输入/输出信号之间的电短路并且使干扰最小化。

虽然已经关于具体实施方式描述了本公开,但是对于本领域技术人员显而易见的是,在不脱离如所附权利要求限定的本发明的精神和范围的情况下可以进行各种改变和修改。

相关申请的交叉引用

本申请要求于2021年8月20日提交的韩国专利申请No.10-2021-0110069的优先权,通过引用将其全部内容并入本文中。

- 半导体装置、半导体装置的制造方法以及半导体封装的制造方法

- 金属互连,制造金属互连的方法,半导体装置和制造半导体装置的方法

- 等离子体处理装置、半导体制造装置及半导体装置的制造方法

- 树脂组合物、树脂膜、半导体层叠体、半导体层叠体的制造方法及半导体装置的制造方法

- 树脂组合物、树脂膜、半导体层叠体、半导体层叠体的制造方法及半导体装置的制造方法

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 氮化物半导体层叠物、半导体装置、氮化物半导体层叠物的制造方法、氮化物半导体自支撑基板的制造方法以及半导体装置的制造方法