一种抗干扰磁性编码器

文献发布时间:2023-06-19 19:14:59

技术领域

本发明属于编码器领域,更具体地,涉及一种抗干扰磁性编码器。

背景技术

编码器是将信号(如比特流)或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。编码器从原理上来讲,拥有如下类别:光电编码器、磁编码器、电容编码器、电感编码器等。磁编码器作为新兴技术在市场上应用的越来越多,市场上电机位置传感的数据接口分为:ABZ接口、PWM接口、I2C接口、SPI接口等,不同接口下的传感器输出的位置精度又不一样,相对而言,SPI接口的磁编码器位置输出精度最高,无论哪种接口的传感器,在电机通电后,都会受到电磁干扰,其中SPI和I2C接口的传感器对电磁干扰最敏感。现有技术下,基本都采用屏蔽系统来解决磁编码器受到电磁干扰的问题。其中方案一为采用定制的屏蔽线,然而此方法存在屏蔽线更换不方便的问题。另方案二为采用M12接口,然后此方案会存在接口较大的问题。

发明内容

本发明的目的在于解决现有磁编码器SPI高速数据传输过程中,为尽可能屏蔽电磁干扰而存在屏蔽线更换不方便以及接口较大的问题

为了实现上述目的,本发明提供一种抗干扰磁性编码器。

根据本发明提供了一种抗干扰磁性编码器,所述磁性编码器包括磁性传感器主体和用于实现所述磁性传感器主体与远端的控制器电性连接的数据线;

所述磁性传感器主体包括PCB板、设置在所述PCB板上的磁性传感器芯片和第一Type-C母座,以及罩设在所述PCB板上的屏蔽外壳;

所述第一Type-C母座与所述磁性传感器芯片之间遵循SPI通信协议,所述第一Type-C母座的VBUS引脚与所述磁性传感器芯片的VDD引脚相连,所述磁性传感器芯片的GND引脚和所述Type-C母座的GND引脚接入同一电源地;

所述数据线包括第一Type-C公头单元、第二Type-C公头单元以及连接二者的数据线主体,所述第一Type-C公头单元用于与所述第一Type-C母座相连,所述第二Type-C公头单元用于与所述控制器的预先配置的第二Type-C母座相连以及对所述控制器的收发数据进行隔离及转发;

所述磁性传感器主体还包括RC滤波电路,所述RC滤波电路串接在所述第一Type-C母座的VBUS引脚与所述磁性传感器芯片的VDD引脚之间。

作为可选的是,所述第一Type-C公头单元包括第一PCB转接板和设置在所述第一PCB转接板上的第一Type-C公头,所述数据线主体的第一端通过所述第一PCB转接板与所述第一Type-C公头电性连接。

作为可选的是,所述第一Type-C公头配置有第一屏蔽壳。

作为可选的是,所述第二Type-C公头单元包括第二PCB转接板和设置在所述第二PCB转接板上的第二Type-C公头,所述数据线主体的第二端通过所述第二PCB转接板与所述第二Type-C公头电性连接;

所述第二Type-C公头单元还包括设置在所述第二PCB转接板上的数字隔离芯片,所述数字隔离芯片用于对所述第二Type-C公头与所述数据线主体之间的SPI通信进行隔离。

作为可选的是,所述第二Type-C公头配置有第二屏蔽壳。

作为可选的是,所述数据线主体为五芯屏蔽线,分别为电源线、数据发送线、数据接收线、片选线和时钟线。

本发明的有益效果在于:

本发明的一种抗干扰磁性编码器,与现有的磁编码器相比,采用四通道数字隔离芯片和屏蔽结构以提高抗干扰能力,磁性传感器主体通过本方案数据线与控制器连接,实现SPI高速数据传输,大大降低磁编码器输出信号的干扰,解决市面上目前屏蔽方案中屏蔽线更换不便和接口大小的问题。

根据以上内容可知,本发明的抗干扰磁性编码器能够有效地解决现有磁编码器SPI高速数据传输过程中,为尽可能屏蔽电磁干扰而存在屏蔽线更换不方便以及接口较大的问题。

本发明的其他特征和优点将在随后具体实施方式部分予以详细说明。

附图说明

本发明可以通过参考下文中结合附图所做出的描述而得到更好的理解,其中在所有附图中使用了相同或相似的附图标记来表示相同或者相似的部件。

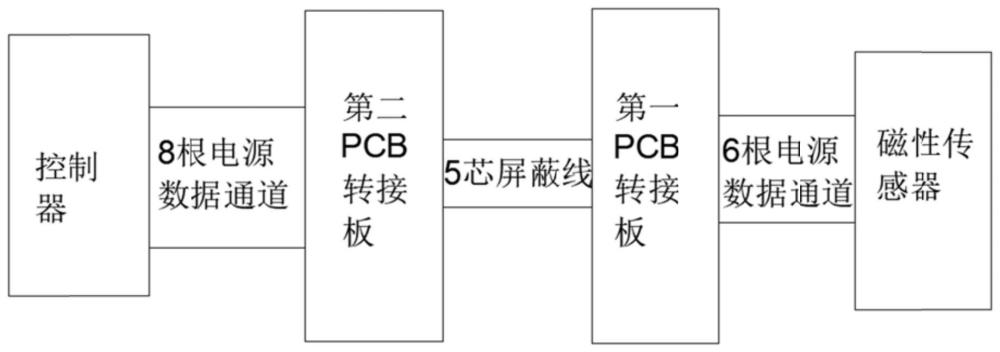

图1示出了本发明的实施例的抗干扰磁性编码器原理框图。

图2示出了本发明的实施例的磁性传感器芯片中相关电源滤波电容和电阻之间的电连接关系图。

具体实施方式

为了使所属技术领域的技术人员能够更充分地理解本发明的技术方案,在下文中将结合附图对本发明的示例性的实施方式进行更为全面且详细的描述。显然地,以下描述的本发明的一个或者多个实施方式仅仅是能够实现本发明的技术方案的具体方式中的一种或者多种,并非穷举。应当理解的是,可以采用属于一个总的发明构思的其他方式来实现本发明的技术方案,而不应当被示例性描述的实施方式所限制。基于本发明的一个或多个实施方式,本领域的普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施方式,都应当属于本发明保护的范围。

实施例:图1示出了本发明的实施例的抗干扰磁性编码器原理框图。参照图1,本发明实施例的抗干扰磁性编码器,磁性编码器包括磁性传感器主体和用于实现磁性传感器主体与远端的控制器电性连接的数据线;

磁性传感器主体包括PCB板、设置在PCB板上的磁性传感器芯片和第一Type-C母座,以及罩设在PCB板上的屏蔽外壳;

第一Type-C母座与磁性传感器芯片之间遵循SPI通信协议,第一Type-C母座的VBUS引脚与磁性传感器芯片的VDD引脚相连,磁性传感器芯片的GND引脚和Type-C母座的GND引脚接入同一电源地;

数据线包括第一Type-C公头单元、第二Type-C公头单元以及连接二者的数据线主体,第一Type-C公头单元用于与第一Type-C母座相连,第二Type-C公头单元用于与控制器的预先配置的第二Type-C母座相连以及对控制器的收发数据进行隔离及转发;

磁性传感器主体还包括RC滤波电路,RC滤波电路串接在第一Type-C母座的VBUS引脚与磁性传感器芯片的VDD引脚之间。

具体地,本发明实施例中,参照图2,RC滤波电路包括电阻和电容;电阻的第一端与第一Type-C母座的VBUS引脚相连,电阻的第二端与电容的第一端的公共端与磁性传感器芯片的VDD引脚相连,电容的第二端接入电源地,通过RC滤波器尽可能减少电源的输入纹波,其中,In连接的电源的输入端具体引脚是可以变动的,OUT连接的传感器芯片的电源输入脚。具体芯片引脚存在不同编号。

进一步地,本发明实施例中,第一Type-C公头单元包括第一PCB转接板和设置在第一PCB转接板上的第一Type-C公头,数据线主体的第一端通过第一PCB转接板与第一Type-C公头电性连接。第一PCB转接板设置有六根电源数据通道分别为5伏电源线、5伏接地线、数据接收线、数据发送线、片选线和时钟线。

再进一步地,本发明实施例中,第一Type-C公头配置有第一屏蔽壳。

再进一步地,本发明实施例中,第二Type-C公头单元包括第二PCB转接板和设置在第二PCB转接板上的第二Type-C公头,数据线主体的第二端通过第二PCB转接板与第二Type-C公头电性连接;

第二Type-C公头单元还包括设置在第二PCB转接板上的数字隔离芯片,数字隔离芯片用于对第二Type-C公头与数据线主体之间的SPI通信进行隔离。第二PCB转接板设置有八根电源数据通道分别为5伏电源线、3.3伏电源线、5伏接地线、3.3伏接地线、数据接收线、数据发送线、片选线和时钟线。数字隔离芯片包含四路数字隔离通道,分别为数据接收线、数据发送线、片选线和时钟线。

再进一步地,本发明实施例中,第二Type-C公头配置有第二屏蔽壳。

再进一步地,本发明实施例中,数据线主体为五芯屏蔽线,分别为电源线、数据发送线、数据接收线、片选线和时钟线。

具体地,本发明实施例中,在磁性传感器的PCB板上设置有支持SPI接口的同轴磁旋转位置传感器芯片AS5047P,供电端加滤波电容和电阻,PCB板上还设置有作为对外接口的第一TYPE-C母座且与传感器芯片AS5047P之间遵循SPI通信协议,同轴磁旋转位置传感器芯片AS5047P配合径向磁铁实现电机位置检测,磁铁的选择是开放的,保证是径向磁铁就可以。磁铁的固定位置在电机的转子上,并且需要径向磁铁的磁场旋转中心在传感器芯片的表贴端面中心。

数据线包括第一TYPE-C公头单元、第二TYPE-C公头单元以及连接二者的数据线主体,数据线主体为5芯屏蔽线分别为电源线VCC、数据发送线MOSI、数据接收线MISO、片选线CSN和时钟线CLK,实现SPI高速数据通信,屏蔽层作第6根线,并定为地线,整个数据线包含总外屏蔽结构。第一TYPE-C公头单元包括第一PCB转接板和设置在第一PCB转接板上的第一TYPE-C公头,第一PCB转接板设置有6根电源数据通道分别为5伏电源线、5伏接地线、数据接收线、数据发送线、片选线和时钟线,第一PCB转接板通过第一TYPE-C公头与第一TYPE-C母座相连,实现SPI高速数据通信。值得提出的是,第一TYPE-C公头及第一TYPE-C母座的安装位置亦可互换,本实施例提出的为最优方案,第一TYPE-C公头设置在第一PCB转接板目的是减小第一PCB转接板体积。第二TYPE-C公头单元包括第二PCB转接板和设置在第二PCB转接板上的第二TYPE-C公头,第二PCB转接板设置有8根电源数据通道分别为5伏电源线、3.3伏电源线、5伏接地线、3.3接地线、数据接收线、数据发送线、片选线和时钟线,第二PCB转接板通过第二TYPE-C公头与预先设置在控制器上的第二TYPE-C母座相连,实现SPI高速数据通信,值得提出的是,第二TYPE-C公头及第二TYPE-C母座的安装位置亦可互换,本实施例提出的为最优方案,第二TYPE-C公头设置在第二PCB转接板上目的是减小第二PCB转接板体积。

第二PCB转接板上还设置有数字隔离芯片ISO7241CDW,数字隔离芯片ISO7241CDW包含4路数字隔离通道分别为数据发送线MOSI、数据接收线MISO、片选线CSN和时钟线CLK。连接磁编码器端采用5VDC、5VGND,连接控制器端采用3.3VDC、3.3VGND。数字隔离芯片用于对第二Type-C公头与数据线主体之间的SPI通信进行隔离。采用四通道数字隔离芯片和屏蔽结构以提高抗干扰能力。

虽然以上对本发明的一个或者多个实施方式进行了描述,但是本领域的普通技术人员应当知晓,本发明能够在不偏离其主旨与范围的基础上通过任意的其他的形式得以实施。因此,以上描述的实施方式属于示意性的而非限制性的,在不脱离如所附各权利要求所定义的本发明精神及范围的情况下,对于本技术领域的普通技术人员而言许多修改和替换均具有显而易见性。

- 一种分体式磁性编码器及使用该磁性编码器的电机

- 一种编码器门控抗干扰电路及编码器