一种基于脉宽扩展单元的n倍脉宽扩展电路及其锁相环

文献发布时间:2023-06-19 09:24:30

技术领域

本发明涉及模拟电路技术领域,具体涉及一种基于脉宽扩展单元的n倍脉宽扩展电路及其锁相环。

背景技术

目前较常见的锁相环主要由鉴频鉴相器、电荷泵、低通滤波器、压控振荡器和分频器构成,锁相环主要通过鉴频鉴相器比较输入参考信号和分频器输出的反馈信号的频率和相位,输出相应控制信号,控制电荷泵对低通滤波器进行电流流入和流出的控制,从而调节低通滤波器的输出电压,通过低通滤波器的输出电压对压控振荡器进行调节,从而改变压控振荡器的输出频率,通过分频器对压控振荡器的输出信号进行分频,并反馈到鉴频鉴相器,从而调整鉴频鉴相器的输出控制信号,如此循环往复直至锁相稳定,锁相稳定时参考信号频率和输出信号频率相等或呈倍数n的关系。传统锁相环系统内部的分频器模块输出的反馈信号占空比较小,导致虽然反馈信号频率较低,但鉴频鉴相器处理信号的速度常常不能满足需求,当压控振荡器输出时钟信号FVCO的频率较高时,对鉴频鉴相器的速度要求更高,因此传统锁相环在系统输出频率较高时稳定性较差,一旦发生鉴频鉴相器的速度不够,可能导致电路产生错误锁定工作在最高频率的情况,且现有的脉冲宽度扩展电路的电路结构较为复杂,增加脉冲宽度扩展电路的生产成本,降低脉宽扩展效率。

发明内容

为解决上述问题,本发明提供了一种基于脉宽扩展单元的n倍脉宽扩展电路,简化脉宽扩展电路的电路结构,通过扩展反馈信号的高电平宽度降低对鉴频鉴相器的速度要求,大大提高了锁相环系统适应性和稳定性。本发明的具体技术方案如下:

一种基于脉宽扩展单元的n倍脉宽扩展电路,所述基于脉宽扩展单元的n倍脉宽扩展电路包括:脉宽传递序列、脉宽扩展组、或逻辑组和输出整形单元;具体地,脉宽传递序列,包括n-1个级联的D触发器;脉宽扩展组,包括n-1个脉宽扩展单元,每一个脉宽扩展单元包括一个双输入端的或逻辑单元和一个延时单元,延时单元的信号输入端和延时单元的信号输出端分别与双输入端的或逻辑单元的信号输入端连接;或逻辑组,包括一个多输入端的或逻辑单元;输出整形单元,包括一个D触发器D_0;其中,参考时钟信号Clk从脉宽传递序列的第n-1级D触发器D_n-1的时钟信号输入端输入,脉宽传递序列的n-1个级联的D触发器的信号输入端与脉宽扩展组的n-1个脉宽扩展单元的信号输入端对应连接,脉宽扩展组的信号输出端与或逻辑组的信号输入端连接,或逻辑组的信号输出端与输出整形单元的信号输入端连接;n是大于或等于2的整数。所述基于脉宽扩展单元的n倍脉宽扩展电路,可根据用户实际需求调配出不同倍数脉宽的脉冲信号,实现预期展宽效果,相较于现有脉宽扩展电路简化了电路结构,降低脉宽扩展电路的生产成本,有利于消除传统逻辑电路中存在的信号波动,提高电路脉宽扩展效率和可靠性。

进一步地,所述脉宽传递序列包括n-1个级联的D触发器,第n-1级D触发器D_n-1的信号输出端与第n-2级D触发器D_n-2的信号输入端连接;其中,级数最高的D触发器的信号输入端用于输入待扩展信号Fbk_t,第1级D触发器的信号输出端与所述或逻辑组的多输入端的或逻辑单元的相应信号输入端连接。待扩展信号通过输入D触发器输入所述脉宽传递序列中,所述脉宽传递序列对待扩展信号起移位寄存的作用,n-1个D触发器输出进行相应脉宽传递后的待扩展信号。

进一步地,所述脉宽传递序列的n-1个级联的D触发器的信号输入端与脉宽扩展组的n-1个脉宽扩展单元的信号输入端对应连接是指所述脉宽传递序列的n-1个级联的D触发器的信号输入端与n-1个脉宽扩展单元的延时单元的信号输入端对应连接。n-1个D触发器输出进行相应脉宽传递后的待扩展信号通过脉宽扩展单元的延时单元的信号输入端输入脉宽扩展组,所述脉宽扩展单元基于延时单元对待扩展信号起延时Δt的作用,每个脉宽扩展单元对信号进行Δt的延时,以达到多个信号出现部分信号重叠的目的,避免因延迟问题引起反馈信号fbk抖动等问题导致产生错误信号。

进一步地,所述或逻辑组包括一个多输入端的或逻辑单元,所述脉宽扩展组的信号输出端与或逻辑组的信号输入端连接是指n-1个脉宽扩展组的双输入端的或逻辑单元的信号输出端与或逻辑组的多输入端的或逻辑单元的信号输入端对应连接。所述或逻辑组对输入的待扩展信号进行或逻辑运算,使得输入的多个信号通过信号重叠部分消除传统逻辑电路可能产生的信号波动,再进行信号脉宽扩展,避免产生错误信号。

进一步地,所述输出整形单元包括一个D触发器D_0,所述D触发器D_0的时钟信号输入端与所述脉宽传递序列的n-1个D触发器的时钟信号输入端连接。所述输出整形单元的D触发器的时钟信号输入端输入参考时钟信号。

进一步地,所述或逻辑组的信号输出端与输出整形单元的信号输入端连接是指所述或逻辑组的多输入端的或逻辑单元的信号输出端与所述输出整形单元的D触发器D_0的信号输入端连接。该技术方案中待扩展信号经过所述或逻辑组的多级逻辑运算后,存在产生一定延迟的可能性,通过所述输出整形单元进行整形输出,可输出满足n倍脉宽扩展的脉冲信号。

本发明还公开一种脉宽扩展电路,所述脉宽扩展电路由m个n值相同或不同的如权利要求1至7任一项所述的基于脉宽扩展单元的n倍脉宽扩展电路串联组成,使得所述脉宽扩展电路的脉冲扩展倍数是这m个如权利要求1至7任一项所述的基于脉宽扩展单元的n倍脉宽扩展电路的脉宽扩展倍数和值减m加一。该技术方案可应用于用户所需脉宽扩展倍数较大时,通过串联多个脉宽扩展电路实现大倍数的脉宽扩展需求。

本发明还公开一种应用基于脉宽扩展单元的n倍脉宽扩展电路的锁相环,所述脉宽扩展的锁相环包括:鉴频鉴相器PFD、电荷泵模块CP、低通滤波器LPF、压控振荡器VCO、分频器N divider和如权利要求1至7所述的n倍脉宽扩展电路模块fbk_pwe;其中,鉴频鉴相器PFD的信号输出端与电荷泵模块CP的信号输入端连接,电荷泵模块CP的信号输出端与低通滤波器LPF的信号输入端连接,低通滤波器LPF的信号输出端与压控振荡器VCO的信号输入端连接,压控振荡器VCO的信号输出端与分频器N divider的信号输入端连接,分频器Ndivider的信号输出端与脉宽扩展电路模块fbk_pwe的信号输入端连接,脉宽扩展电路模块fbk_pwe的信号输出端与鉴频鉴相器PFD的反馈信号输入端连接。该技术方案公开的应用基于脉宽扩展单元的n倍脉宽扩展电路的锁相环,基于n倍脉宽扩展电路将反馈信号fbk_t转变为脉冲宽度为原脉宽n倍的反馈信号fbk_nt,所述锁相环可根据实际脉宽倍数需求灵活调节脉宽扩展倍数,保证锁相环工作的稳定性,提高锁相环中鉴频鉴相器PFD工作的稳定性和可靠性。

附图说明

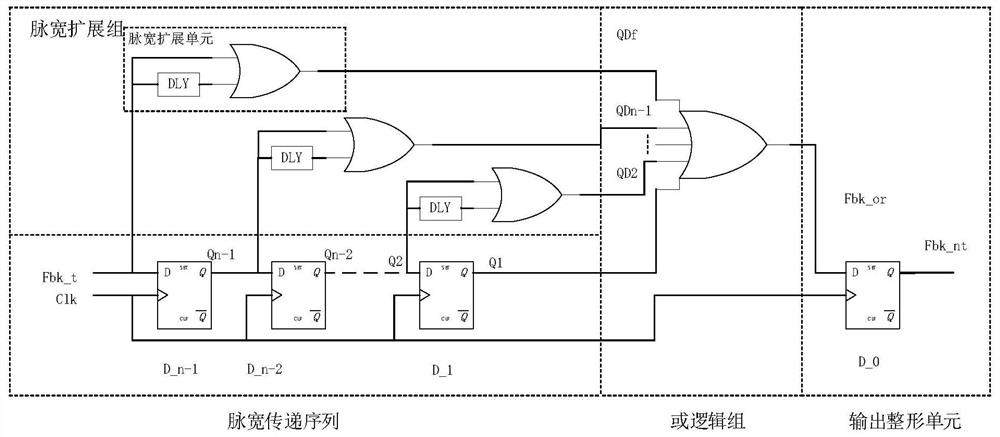

图1为本发明一种实施例所述基于脉宽扩展单元的n倍脉宽扩展电路的结构示意图。

图2为本发明一种实施例所述基于脉宽扩展单元的2倍脉宽扩展电路的结构示意图。

图3为本发明一种实施例所述基于脉宽扩展单元的3倍脉宽扩展电路的结构示意图。

图4为图3所示实施例的所述基于脉宽扩展单元的3倍脉宽扩展电路的各节点信号的波形图。

图5为本发明一种实施例所述基于脉宽扩展单元的4倍脉宽扩展单元的结构示意图。

图6为本发明一种实施例所述应用基于脉宽扩展单元的n倍脉宽扩展电路的锁相环的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行详细描述。应当理解,下面所描述的具体实施例仅用于解释本发明,并不用于限定本发明。

本发明一种实施例中提供一种基于脉宽扩展单元的n倍脉宽扩展电路,参阅图1所示,所述基于脉宽扩展单元的n倍脉宽扩展电路由脉宽传递序列、脉宽扩展组、或逻辑组和输出整形单元四个部分组成。所述基于脉宽扩展单元的n倍脉宽扩展电路可应用于如图6所示的锁相环中。需要说明的是,n是大于或等于2的整数。

具体地,所述基于脉宽扩展单元的n倍脉宽扩展电路中的脉宽传递序列包括n-1个级联的D触发器,待扩展信号Fbk_t和参考时钟信号Clk分别从级数最高的D触发器的信号输入端及其时钟信号输入端输入所述脉宽传递序列,第n-1级D触发器D_n-1的信号输出端与第n-2级D触发器D_n-2的信号输入端连接,所述脉宽扩展组包括n-1个信号输入端和n-1个信号输出端,所述脉宽传递序列的n-1个级联的D触发器的信号输入端分别与脉宽扩展组相匹配的信号输入端连接。

具体地,所述脉宽扩展组中存在n-1个信号输入端和对应的n-1个信号输出端之间连接有一个脉宽扩展单元,以构成n-1个脉宽扩展单元,所述脉宽扩展单元包括一个延时单元和一个双输入端的或逻辑单元,所述延时单元的信号输入端和信号输出端分别与所述双输入端的或逻辑单元对应的两个信号输入端连接,所述脉宽扩展组的n-1个信号输入端对应为n-1个延时单元的信号输入端,所述脉宽扩展组的n-1个信号输出端对应为n-1个双输入端的或逻辑单元的信号输出端,所述脉宽传递序列的第n-1级D触发器D_n-1的信号输入端与对应的一个脉宽扩展单元的信号输入端连接,即所述脉宽传递序列的第n-1级D触发器D_n-1的信号输入端与对应的一个脉宽扩展单元的延时单元的信号输入端连接。

具体地,所述或逻辑组包括一个多输入端的或逻辑单元,所述多输入端的或逻辑单元的输入端数量由所述基于脉宽扩展单元的n脉宽扩展电路的脉宽扩展倍数数值决定,所述或逻辑单元的信号输入端与对应的所述脉宽扩展组中的n-1个脉宽扩展单元的信号输出端连接,即所述或逻辑单元的信号输入端与n-1个对应的所述脉宽扩展单元的双输入端的或逻辑单元的信号输出端连接,以实现所述脉宽扩展组的n-1个信号输出端分别与或逻辑组相匹配的信号输入端对应连接,所述或逻辑组的信号输出端与输出整形单元的信号输入端连接。

具体地,所述输出整形单元包括一个D触发器D_0,所述或逻辑组的多输入端的或逻辑单元的信号输出端与所述D触发器D_0的信号输入端连接,以实现所述或逻辑组的信号输出端与所述输出整形单元信号输入端连接,所述D触发器D_0的时钟信号输入端与所述脉宽传递序列的n-1个D触发器的时钟信号输入端连接。

具体地,参考时钟信号Clk通过脉宽传递序列的第n-1级D触发器的时钟信号输入端输入所述基于脉宽传递单元的n倍脉宽扩展电路,所述脉宽传递序列的第n-1级D触发器的时钟信号输入端与所述脉宽传递序列的每一级D触发器的时钟信号输入端和所述输出整形单元的D触发器D_0的时钟信号输入端连接,待扩展信号Fbk_t通过脉宽传递序列的第n-1级D触发器的信号输入端输入所述基于脉宽传递单元的n倍脉宽扩展电路,同时待扩展信号Fbk_t输入至脉宽扩展组的相应脉宽扩展单元,并通过延时单元的延时处理和双输入端的或逻辑单元的或逻辑运算处理后,由双输入端的或逻辑单元的信号输出端输出信号QDf至或逻辑组的多输入端的或逻辑单元的对应信号输入端,第n-1级D触发器D_n-1输出脉宽传递后的信号Qn-1至脉宽扩展组的相应脉宽扩展单元,并通过延时单元的延时处理和双输入端的或逻辑单元的或逻辑运算处理后,由双输入端的或逻辑单元的信号输出端输出信号QDn-1至或逻辑组的多输入端的或逻辑单元的对应信号输入端,以此类推,脉宽传递序列的n-1个D触发器的信号输出端分别输出脉宽传递后的信号Qn-1、Qn-2...Q2和Q1,信号Qn-1、Qn-2...Q2分别输入至相匹配的脉宽扩展单元,并通过延时单元的延时处理和双输入端的或逻辑单元的或逻辑运算处理后,由双输入端的或逻辑单元的信号输出端输出信号QDn-1、QDn-2...QD2至或逻辑组的多输入端的或逻辑单元的对应信号输入端,特别地,第1级D触发器D_1可以直接输出信号Q1至或逻辑组的多输入端的或逻辑单元的对应信号输入端,也可以与第n-1级D触发器D_n-1一样输出信号Q1至脉宽扩展单元的信号输入端,多输入端的或逻辑单元对信号QDn-1、QDn-2...QD2和Q1进行或逻辑运算并输出信号Fbk_or至输出整形单元,输出整形单元对信号Fbk_or进行输出整形处理并输出n倍脉宽扩展后的信号Fbk_nt。

具体地,或逻辑组模块是对多个输入信号执行或逻辑运算并输出一个结果信号,当所述n倍脉宽扩展电路的n值较大时,一个多输入端的或逻辑单元难以快速完成n-1个信号的或逻辑运算,此时可适应性增加或逻辑单元的数量,通过多个或逻辑单元的组合使用,以实现对所有输入信号执行或逻辑运算并输出一个结果信号的功能。

本发明的一种实施例中提供一种脉宽扩展电路,所述脉宽扩展电路由m个n值相同或不同的如图1所示的基于脉宽扩展单元的n倍脉宽扩展电路串联而成,所述脉宽扩展电路的脉宽扩展倍数为以上基于脉宽扩展单元的n倍脉宽扩展电路的脉宽扩展倍数和值减m加一。

本发明的一种实施例中提供一种基于脉宽扩展单元的2倍脉宽扩展电路,参阅图2所示,所述基于脉宽扩展单元的2倍脉宽扩展电路由脉宽传递序列、脉宽扩展组、或逻辑组和输出整形单元四个部分组成,所述脉宽传递序列由一个D触发器D_1组成,所述脉宽扩展组由一个脉宽扩展单元组成,所述脉宽扩展单元包括一个延时单元和一个双输入端的或逻辑单元H1,所述延时单元的信号输入端和信号输出端分别与双输入端的或逻辑单元H1相对应的两个信号输入端连接,所述或逻辑组包括一个双输入端的或逻辑单元H2,所述输出整形单元包括一个D触发器D_0。所述基于脉宽扩展单元的2倍脉宽扩展电路可应用于如图6所示的锁相环中。

具体地,参考时钟信号Clk由脉宽传递序列的D触发器D_1的时钟信号输入端输入所述基于脉宽扩展单元的2倍脉宽扩展电路,脉宽传递序列的D触发模块D_1的时钟信号输入端与输出整形单元的D触发器D_0的时钟信号输入端连接,待扩展信号Fbk_t由脉宽传递序列模块的D触发器D_1的信号输入端和脉宽扩展单元的信号输入端输入所述2倍脉宽扩展电路,双输入端的或逻辑单元H2接收D触发器D_1输出的信号Q1和双输入端的或逻辑单元H1输出的信号QDf并进行或逻辑运算处理,双输入端的或逻辑单元H2输出或逻辑运算处理后的信号Fbk_or,输出整形单元的D触发器对信号Fbk_or进行整形处理后输出2倍脉宽扩展后信号Fbk_2t。

本发明的一种实施例提供一种基于脉宽扩展单元的3倍脉宽扩展电路,参阅图3所示,所述基于脉宽扩展单元的3倍脉宽扩展电路由脉宽传递序列、脉宽扩展组、或逻辑组和输出整形单元四个部分组成;其中,所述脉宽传递序列包括两个D触发器D_1和D_2,所述脉宽扩展组包括两个脉宽扩展单元,所述脉宽扩展单元包括一个延时单元和一个双输入端的或逻辑单元H1,所述或逻辑组包括一个三输入端的或逻辑单元,所述输出整形单元包括一个D触发器D_0。

所述基于脉宽扩展单元的3倍脉宽扩展电路可应用于如图6所示的锁相环中。具体地,所述锁相环PLL工作时,压控振荡器VCO产生一个时钟输出信号fout,所述时钟输出信号fout经过分频器N divider的分频产生一个反馈信号fbk,所述反馈信号fbk即为待扩展信号Fbk_t,待扩展信号经过n倍脉宽扩展电路后产生脉冲宽度为3倍的信号Fbk_3t,脉冲扩展后信号Fbk_3t作为新的反馈信号输入鉴频鉴相器PPL,鉴频鉴相器PPL将反馈信号Fbk_3t和输入的参考信号fre进行相位比较并输出具有相位信息的控制信号至电荷泵CP,电荷泵CP接收的控制信号转化电流,控制调节低通滤波器LPF的电压,并调节压控振荡器VCO的输出时钟频率,开始下一个循环调制,直到反馈信号Fbk_3t和参考信号Fref达到同频同相,整个锁相环路处于稳定状态,压控振荡器VCO输出时钟信号fout频率稳定,锁相环基于应用基于脉宽扩展单元的3倍脉宽扩展电路获取n倍时钟信号频率输出,实现锁相环稳定。

具体地,所述反馈信号Fbk_t输入所述基于脉宽扩展单元的3倍脉宽扩展电路时各节点信号的波形可参阅图4所示,当锁相环PLL中分频器N完成一次分频后,反馈信号fbk输出一个高电平,所述反馈信号fbk即为待扩展信号Fbk_t;参考时钟信号Clk第一个上升沿来临时,待扩展信号Fbk_t由低电平状态变为高电平,但仍处于低电平,第2级D触发器D_2输出的脉宽传递后的待扩展信号Q2为低电平,同理,当参考时钟信号第一个上升沿来临时,第1级D触发器D_1输出的脉宽传递后的待扩展信号Q1为低电平;参考信号Clk第二个上升沿来临时,待扩展信号Fbk_t由高电平变为低电平,但仍处于高电平,所以当参考时钟信号Clk的第二个上升沿来临时,第2级D触发器D_2输出的脉宽传递后的待扩展信号Q2由低电平变为高电平,但仍处于低电平,此时第1级D触发器D_1输出的脉宽传递后的待扩展信号Q1仍为低电平;当参考时钟信号Clk的第三个上升沿来临时,待扩展信号Fbk_t仍为为低电平,第2级D触发器D_2输出的脉宽传递后的待扩展信号Q2由高电平变为低电平,但仍处于高电平,第1级D触发器D_1输出的脉宽传递后的待扩展信号Q1由低电平变为高电平;当参考时钟信号Clk的第四个上升沿来临时,待扩展信号Fbk_t仍为低电平,第2级D触发器D_2输出的脉宽传递后的待扩展信号Q2仍为低电平,第1级D触发器D_1输出的脉宽传递后的待扩展信号Q1由高电平变为低电平。待扩展信号Fbk_t经过脉宽扩展组的一个脉宽扩展单元后产生了经过延时Δt的信号b的或逻辑输出信号QDf,信号QDf相较于信号Fbk_t上升沿一致,信号QDf的下降沿比信号Fbk_t延时Δt,第2级D触发器D_2输出信号Q2经过脉宽扩展组的一个脉宽扩展单元后产生经过延时Δt的信号a的或逻辑输出信号QD2,信号QD2相较于信号Q2上升沿一致,信号QD2的下降沿比信号Q2延时Δt;第1级D触发器D_1输出的脉宽传递后的待扩展信号Q1、或逻辑处理b信号后输出的信号QDf和或逻辑处理a信号后输出的信号QD2分别输入三输入端的或逻辑单元的相应信号输入端,三输入端的或逻辑单元对输入信号Q1、QDf和QD2进行或逻辑运算处理,通过三个信号Q1、QDf和QD2的信号存在部分重叠,避免组合逻辑产生错误信号,三输入端或逻辑单元输出或逻辑运算后的信号Fbk_or;经过多级或逻辑运算后,信号存在产生延迟的可能性,信号Fbk_or通过输出整形单元进行整形输出,获取3倍脉宽扩展信号Fbk_3t。

本实施例中出现的“第一”、“第二”、“第三”、“第n-1”等术语,是为了便于相关特征次序先后的区分,并不能理解为指示或暗示其相对重要性或者技术特征的数量。

本发明一种实施例中提供一种基于脉宽扩展单元的4倍脉宽扩展电路,参阅图5所示,所述基于脉宽扩展单元的4倍脉宽扩展电路由脉宽传递序列、脉宽扩展组、或逻辑组和输出整形单元四个部分构成;所述脉宽传递序列包括3个D触发器,第3级D触发器D_3的信号输出端与第2级D触发器D_2的信号输入端连接,第2级D触发器D_2的信号输出端与第1级D触发器D_1的信号输入端连接;所述脉宽扩展组包括三个脉宽扩展单元,所述脉宽扩展单元包括一个延时单元和一个双输入端的或逻辑单元,所述延时单元的信号输入端和信号输出端分别与同一脉宽扩展单元中的双输入端的或逻辑单元的相应的两个信号输入端连接,所述脉宽传递序列的D触发器的信号输入端与所述脉宽扩展组的相匹配的脉宽扩展单元的延时单元的信号输入端连接;所述或逻辑组包括一个四输入端的或逻辑单元,所述脉宽扩展组的三个脉宽扩展单元的双输入端的或逻辑单元的信号输出端与相匹配的所述四输入端的或逻辑单元的信号输入端连接,特别地,所述脉宽传递序列的第1级D触发器D_1的信号输出端与相匹配的所述四输入端的或逻辑单元的信号输入端连接;所述输出整形单元包括一个D触发器D_0,所述或逻辑组的四输入端的或逻辑单元的信号输出端与所述D触发器D_0的信号输入端连接,所述D触发器D_0的时钟信号输入端与所述脉宽传递序列的3个D触发器的时钟信号输入端连接。所述基于脉宽扩展单元的4倍脉宽扩展电路可应用于如图6所示的锁相环中。

本发明的一种实施例中提供一种应用基于脉宽扩展单元的n倍脉宽扩展电路的锁相环,所述应用基于脉宽扩展单元的n倍脉宽扩展电路的锁相环PLL包括鉴频鉴相器PFD、电荷泵CP、低通滤波器LPF、压控振荡器VCO、分频器N divider和基于脉宽扩展单元的n倍脉宽扩展电路fbk_pwe。所述锁相环PLL工作时,压控振荡器VCO产生一个时钟输出信号fout,所述时钟输出信号fout经过分频器N divider的分频产生一个反馈信号fbk,所述反馈信号fbk即为待扩展信号Fbk_t,待扩展信号经过n倍脉宽扩展电路后产生脉冲宽度为n倍的信号Fbk_nt,脉冲扩展后信号Fbk_nt作为新的反馈信号输入鉴频鉴相器PPL,鉴频鉴相器PPL将反馈信号Fbk_nt和输入的参考信号fre进行相位比较并输出具有相位信息的控制信号至电荷泵CP,电荷泵CP接收的控制信号转化电流,控制调节低通滤波器LPF的电压,并调节压控振荡器VCO的输出时钟频率,开始下一个循环调制,直到反馈信号Fbk_nt和参考信号Fref达到同频同相,整个锁相环路处于稳定状态,压控振荡器VCO输出时钟信号fout频率稳定,基于n倍脉宽扩展电路实现锁相环获取n倍时钟信号频率输出。

最后应当说明,以上所述实施例仅为本发明的优选实施例,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,可以作出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。