一种DBBC的同步采集时延控制方法

文献发布时间:2023-06-19 09:26:02

技术领域

本发明涉及射电天文技术领域,具体涉及一种DBBC的同步采集时延控制方法。

背景技术

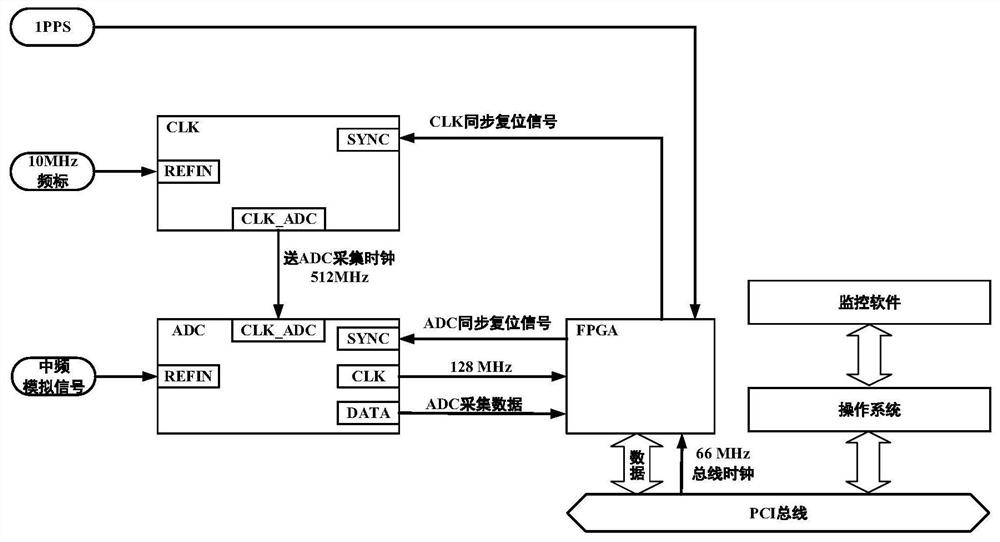

由干涉测量技术原理(干涉测量系统结构框图如图1所示)可知,DBBC(DigitalBase Band Converter,基带转换与记录系统)的系统时延作为VLBI(Very Long BaselineInterferometer,甚长基线干涉测量,VLBI系统组成及测量原理如图2所示)几何时延测量误差的一部分,需要在观测时进行标校消除。在工作环境和温度不变的情况下,可从时延是否变化的角度,将DBBC系统时延分为固定时延和同步采集时延两部分:①固定时延是指每次进行数据采集时固定不变的时延,包括电缆时延和信号处理时延等;②同步采集时延指每次进行数据采集时,与秒脉冲(1Pulse Per Second,1PPS)信号之间的同步关系发生变化的时延,包括时钟同步时延、模数转换器(Analog-to-Digital Converter,ADC)同步时延和现场可编程门阵列(Field Programmable Gate Array,FPGA)数据处理同步时延,其示意图如图3所示。在DBBC系统中10MHz频标信号输入CLK芯片,CLK芯片输出ADC采样时钟;ADC按ADC采样时钟采集中频模拟信号获得数字信号并发送到FPGA,FPGA进行数字信号处理,其中,1PPS秒脉冲信号和10MHz频标信号由时标设备产生,中频模拟信号由观测天线接收。同步采集时延误差主要由以下三部分组成:

1、两个观测站ADC采样时钟的时延差τ

2、两个观测站ADC从开始采集模拟信号到输出数字信号给FPGA之间的时延差τ

3、两个观测站FPGA进行DBBC数字信号处理算法产生的时延差τ

作为一个高精度测量系统,在工作环境和温度不变的情况下,DBBC设备应当具有稳定的系统时延,否则DBBC系统时延将作为VLBI几何时延测量误差的一部分,需要在每次观测前对系统时延进行标校。VLBI观测时延τ

τ

式中:

τ

τ

τ

τ

可见,要实现几何时延τ

1、DBBC每次开机,都必须利用射电源等手段进行时延校准,如果遇到没有合适的射电源用于观测时,同步采集误差无法完全消除;

2.DBBC时延经过校准后,如果遇到断电,死机等异常情况,开机后还需重新标校,将占用宝贵的观测时间;

3.不利于发现异常的时延变化问题。

由此可见,国内外同类设备仅考虑了一次开机后同步采集时延一致性的问题,没有考虑不同次开机的时延一致性问题,导致每次开机后,都需要重新进行标校,降低了VLBI观测效率,无法实现同步采集时延的高稳定度控制。

发明内容

有鉴于此,本发明提供了一种DBBC的同步采集时延控制方法,考虑了不同次开机的时延一致性问题,能够实现同步采集时延的高稳定度控制,每次开机后,不需要重新进行标校,解决了设备重开机时延零值不确定的难题。

本发明是通过以下技术方案来实现的:

本发明的一种DBBC的同步采集时延控制方法,在DBBC中,时统设备产生1PPS秒脉冲信号和10MHz频标信号,10MHz频标信号发送到CLK芯片,CLK芯片输出ADC采集时钟;ADC采集中频模拟信号获得数字信号并发送到FPGA,FPGA进行数字信号处理,所述控制方法包括如下步骤:

步骤1,将CLK芯片配置为零延时操作模式;

在FPGA工作时钟的驱动下,在两个1PPS秒脉冲信号之间启动同步使能信号;1PPS秒脉冲信号到来后,将同步使能信号延迟一个时钟周期,再将同步使能信号由高电平变为低电平;对1PPS秒脉冲信号取反,并与同步使能脉冲相与,产生下降沿与1PPS秒脉冲信号的上升沿同步的CLK同步复位脉冲信号;

在每次时钟状态改变时,所述CLK同步复位脉冲信号对CLK芯片进行同步复位,使得同步复位后的CLK芯片输出的ADC采样时钟与1PPS秒脉冲上升沿保持固定的相位关系;

步骤2,采用与CLK同步复位脉冲信号相同的产生方式,产生下降沿与1PPS秒脉冲信号的上升沿同步的ADC同步复位脉冲信号;

在每次时钟状态改变时,所述ADC同步复位脉冲信号对ADC进行同步复位,使得同步复位后的ADC输出数字信号始终与输入模拟信号之间有固定的时间延迟;

步骤3,利用时统设备进行时间校准,用户根据任务需求设定任务启动时刻;

在任务启动时刻对应的1PPS秒脉冲信号到来之前0.2秒~0.7秒,采用与CLK同步复位脉冲信号相同的产生方式,产生下降沿与1PPS秒脉冲信号的上升沿同步的FPGA同步复位脉冲信号;

在每次时钟状态改变时,所述FPGA同步复位脉冲信号对DBBC的各个单元模块进行同步复位;

当FPGA同步复位脉冲有效后,将ADC采集数据写入异步FIFO中;

当FIFO数据容量达到半满条件后,将FIFO读使能信号置为高,FIFO输出ADC采集数据,送给后续的DBBC信号处理单元。

其中,在CLK芯片中,利用R分频器将10MHz频标信号分频,得到2MHz信号,然后再倍频得到ADC采集时钟。

其中,CLK芯片中,VCO、VCO分频器、通道0分频器以及N分频器都在锁相环的环路中;

鉴相器通过调整VCO频率,保证N分频器输出的2MHz时钟信号与R分频器输出的2MHz时钟信号保持同相。

其中,在CLK芯片中,利用R分频器将10MHz频标信号分频,得到1MHz信号,然后再倍频得到ADC采集时钟。

其中,所述ADC采集时钟为256MHz、512MHz或1024MHz。

有益效果:

本发明通过对CLK、ADC和FPGA数据处理的同步使能机制进行设计,采用基于1PPS的同步触发控制策略,保证τ

附图说明

图1为干涉测量系统结构框图。

图2为VLBI系统组成及测量原理示意图。

图3为DBBC同步采集时延示意图。

图4为国内外典型基带转换器的同步设计结构框图。

图5为本发明采用的同步采集时延控制系统设计结构框图。

图6为本发明采用的AD9522芯片的详细结构框图。

图7为本发明时钟分频产生的时钟相位模糊示意图。

图8为本发明同步复位信号产生时序图。

图9为本发明同步后的2MHz输出时钟产生时序图。

图10为本发明CLK芯片时钟产生结构框图。

图11为本发明采用的CLK芯片配置为普通模式结构框图。

图12为本发明采用的CLK芯片配置为零延时模式结构框图。

图13为本发明采用的ADC同步复位原理示意图。

图14为本发明采用的FPGA实现结构框图。

图15为本发明采用的FPGA处理同步使能示意图。

图16为本发明采用的基于相时延的开机同步测试系统框图。

图17为本发明采用的基于相时延的开机同步测试结果。

图17(a)为多次开关机信号相位变换情况;图17(b)为多次开关机之间相时延差。

图18为本发明基于群时延的开机同步测试系统框图。

图19为本发明基于群时延的开机同步测试结果。

图19(a)为多次开关机被测系统的群时延值;图19(b)为多次开关机之间群时延差。

具体实施方式

下面结合附图并举实施例,对本发明进行详细描述。

本实施例提供了一种DBBC的同步采集时延控制方法,首先详细阐述本发明的方法原理和实施步骤,最后搭建实验系统,通过实测数据,对所提方法的同步采集时延稳定性能进行测试。

本实施例提出的同步采集时延控制方法采用具有高稳定性的同步采集时延控制系统,系统的实现结构框图如图5所示。在VLBI观测站内,1PPS秒脉冲信号和10MHz频标信号是由站内氢原子钟和GPS共视接收机(时统设备)产生的,两者之间的时延差在观测期间保持一致并且是可测的。中频模拟信号为观测天线接收信号。DBBC同步采集时延控制方法的实施步骤为:

步骤1,设备开机,监控软件启动初始化程序,检测信号采集与处理板工作正常后,开始对同步采集时延进行控制;

步骤2,监控软件通过PCI总线配置板卡寄存器,首先在某一1PPS秒脉冲的触发逻辑控制下,同步复位CLK芯片,使之输出的512MHz采样时钟始终与1PPS秒脉冲有固定的相位关系;

步骤3,监控软件通过PCI总线配置板卡寄存器,在某一1PPS秒脉冲的触发逻辑控制下,同步复位ADC,使之输出数字信号始终与输入模拟信号之间有固定的时间延迟;

步骤4,监控软件通过PCI总线配置板卡寄存器,在某一1PPS秒脉冲的触发逻辑控制下,同步复位DBBC的各个单元模块,包括FIR滤波器、NCO、子带AGC、FIFO等,使各单元处于等待状态。在同步复位后,将AD采样数据流标记为有效状态,则接收ADC数据FIFO写使能信号有效,DBBC即刻开始工作。

通过以上同步使能机制,实现了DBBC每次开机时,同步采集时延的高稳定度控制,从而实现了DBBC在工作环境和温度不变的情况下,具有稳定一致的设备时延。

具体地,对CLK、ADC和FPGA的同步方法如下:

(1)基于1PPS的采样时钟CLK同步方法

在DBBC的实现过程中,为了提高可靠性,ADC实际工作在交替采样模式下,即进行上下边沿采样,所需采样时钟降为512MHz。如图5所示,ADC的512MHz采样时钟由频率综合器CLK对10MHz频标进行锁相产生。因此,为了保证ADC的512MHz采样时钟的开机同步,需要确保ADC的512MHz采样时钟与1PPS秒脉冲上升沿保持固定的相位关系。

图6给出了AD9522芯片的详细结构框图,由图6可知,512MHz时钟无法由10MHz参考频标直接倍频产生,必须先利用R分频模块将10MHz分频至2MHz,然后再倍频至512MHz。需要注意的是,对时钟进行倍频,不会产生时钟延时模糊,但是对时钟进行分频时,如果不加控制,会导致时钟相位模糊。图7给出了时钟分频产生的时钟相位模糊的示意图,如图7所示,以基准频率为参考,假设设备任意时刻开始工作,即输出时钟的上升沿将随机与基准频率时钟的某个上升沿对齐,若进行倍频(图7中以2倍频为例),则倍频后时钟与基准频率时钟的相位关系是固定的,不会产生时钟延时模糊;若进行分频(图7中以2分频为例),则分频后时钟与基准频率时钟的相位关系有两种可能情况,即相对于1PPS信号,存在时钟延时模糊。N分频会有N个不同的延迟输出,即有N个时钟延时模糊存在。时钟延时模糊会导致在设备每次开机后,存在N种可能延迟。也就是说,时钟延时模糊会导致时钟延迟会随机变化,开机延迟不一致。

为了解决分频产生的时钟延时模糊问题,本发明以1PPS秒脉冲信号为参考,产生一个与1PPS秒脉冲上升沿同步的复位信号。在每次时钟状态改变时(如重新开机、时钟重新锁定、程序重新加载等),对时钟进行同步复位,保证每次都是由参考时钟的同一个上升沿进行分频,消除时钟相位模糊。同步复位信号产生模块设计如下:

在FPGA内部利用状态机实现同步复位信号的产生逻辑功能,其产生时序如图8所示。首先,在FPGA工作时钟(板上PCI总线时钟,频率为66MHz,注意,不可以用CLK频综芯片的128MHz时钟,因为在进行时钟同步复位的过程中,CLK芯片不输出时钟)的驱动下,在两个1PPS信号之间启动同步使能信号(变为高)。状态机检测到1PPS到来后,将同步使能信号延迟一个时钟周期,再将使能信号由高电平变为低电平。由于同步使能脉冲的上升沿提前于1PPS信号,而1PPS的持续时间通常远大于一个FPGA工作时钟周期,因此,同步使能信号的下降沿将介于1PPS信号上升沿与下降沿之间。对1PPS信号取反,并与同步使能脉冲相与,即可产生同步复位脉冲信号。以上“取反”和“相与”操作由FPGA的组合逻辑实现,从而保证了同步复位脉冲下降沿与1PPS信号上升沿的同步。

FPGA将产生的同步复位脉冲信号输出给CLK芯片的SYNC管脚,如图5所示,来同步复位R分频模块,从而得到同步后无时钟延迟模糊的2MHz时钟,其产生时序图如图9所示。

另外,对于时钟频率综合器设计如下:

综合考虑各种需求,本实施例采用了ADI公司的AD9522-3可编程时钟芯片。该芯片可通过SPI串行接口编程来定制用户需求的功能。图10给出了CLK芯片时钟产生的结构框图。通过同步复位R分频器,可以保证10MHz与2MHz同步。鉴相器通过调整VCO频率,保证N分频器输出的2MHz时钟信号与R分频器输出的2MHz时钟信号保持同相。

此外,在设计中,为了使512MHz时钟与1PPS同步,需要将CLK芯片配置成内部零延迟操作模式。为说明这一点,下面将CLK芯片配置为普通模式和零延时操作模式的结构框图进行对比,分别如图11和图12所示。

如图11所示,当CLK芯片配置为普通模式时,VCO输出频率为2MHz的倍频因而没有时钟延时模糊,但是,各通道输出时钟必须由VCO经VCO分频器和通道分频器分频得到。因为CLK芯片的SYNC信号只能同步复位R分频器和N分频器,而不能同步复位各通道分频器,导致各通道分频器即使经过SYNC复位,仍然存在时延模糊。综上可知,若将CLK芯片配置为普通模式,必然存在时钟延时模糊。

如图12所示,当CLK芯片配置为零延时操作模式时,VCO、VCO分频器、通道0分频器以及N分频器都在锁相环的环路中。由锁相环特性可知,环路中的时钟必然是同步的,因此,N分频器输出2MHz、通道0分频器输出16MHz以及VCO分频器输出512MHz和VCO输出2048MHz保持同步。将通道1分频器置为旁路,因此通道1输出时钟为512MHz,该时钟必然与2MHz保持同步,自然也与10MHz频标和1PPS信号同步,从而可以作为ADC同步采样时钟。

综上所述,通过将CLK芯片配置为零延时操作模式,并利用基于1PPS同步复位机制,即可实现512MHz采样时钟的开机同步。

(2)基于1PPS的ADC同步方法

ADC芯片选择美国国家半导体公司推出的ADC08D1020。在本实施例中,ADC工作在交替采集模式下,采样速率为1024Msps,而采样时钟只需512MHz。在数字输出端,ADC芯片采用串并转换方式,输出4路256MHz,8bit数据流,ADC采集数据随路时钟为128MHz,为双边沿采样。在这个过程中,128MHz时钟由512MHz时钟分频得到,所以存在时钟相位模糊问题。因此,ADC芯片同样需要进行同步复位,使ADC输出的128MHz与1PPS同步,保证输出数字信号始终与输入模拟信号之间有固定的时间延迟。ADC同步复位信号产生原理与时钟频率综合器的同步复位信号产生原理一样(见图8),这里不再赘述。ADC复位的时序图如图13所示,只要同步复位信号下降沿与1PPS秒脉冲上升沿保持同步,即可实现ADC数据采集的开机同步。

(3)基于1PPS的FPGA处理同步方法

在VLBI观测任务中,数据采集均在监控软件的控制下,以某个整秒时刻开始。在整秒启动时刻,FPGA开始接收ADC的数据流,完成DBBC信号处理功能,主要包括FIR滤波器、NCO、子带AGC、FIFO等功能模块。图14给出了FPGA实现结构框图。监控软件启动后,按照初始化流程,通过PCI总线配置FPGA寄存器,先后产生CLK同步使能脉冲、ADC同步使能脉冲和FPGA同步启动脉冲,分别产生CLK、ADC和FPGA的同步复位脉冲信号。

对于FPGA的同步使能机制,图15给出了FPGA同步使能机制的时序图,当与启动时刻对应的1PPS信号到来前,FPGA内各功能模块均处于复位状态。在启动时刻前0.5s,FPGA在软件的配置下,发送FPGA同步使能脉冲信号,产生与1PPS信号上升沿同步的FPGA同步复位脉冲(实现原理见图8)。当FPGA同步复位脉冲有效后(为低电平),在ADC随路128MHz时钟的时序逻辑触发下,将异步FIFO写使能信号置为高,即置为有效状态,则ADC采集数据开始写入异步FIFO中。当FIFO数据容量达到半满条件后,FIFO读使能信号置为高,FIFO输出ADC采集数据,送给后续的DBBC信号处理单元。

从上述过程可以看出,ADC随路128MHz时钟与1PPS、FPGA同步复位脉冲信号都是同步的,因此异步FIFO写使能也与1PPS同步,从而保证了FPGA同步时延是固定的,实现了FPGA的同步使能。

另外,在CLK芯片中,也可以利用R分频器将10MHz频标信号分频得到1MHz信号,然后再倍频得到ADC采集时钟,不是必须分频到2MHz。

所述ADC采集时钟也可以为按需求设定的其他值,常见的有256MHz或1024MHz以及本实施例的512MHz。

实验验证:为了验证DBBC同步采集时延控制方法的时延稳定性能,分别从相时延和群时延两个方面,对同步采集时延稳定性能进行测试。其中,相时延用于求取精确的同步采集误差,群时延用于确定同步采集误差的模糊度。

(1)基于相时延的同步采集时延误差测试:

基于相时延的同步采集时延稳定性测试的原理为:使用DBBC对同源的单点频信号进行多次重启记录,分析各次记录信号相位的一致性。若同步设计良好,则每次采集记录信号的相位应当相同。由相时延的定义可知:

式中,

式中,

利用Symmetricom Datum X72铷原子钟作为信号源及参考时钟。该原子钟能够产生同源的1PPS信号、10MHz频标和60MHz TTL信号。60MHz TTL信号具有丰富的谐波,对其300MHz处的5次谐波进行采集记录。提取不同次记录信号的相位,计算DBBC的同步采集指标。测试系统框图如图16所示。DBBC参数具体设置为:信号带宽为1MHz、中心频率为299.75MHz、量化位数16bit、复信号输出。分别对测试系统进行三次开关机采集记录,得到各次采集记录信号的相位如图17(a)所示。根据各次采集记录信号相位,求取多次采集信号之间的相时延差,如图17(b)所示。△21表示第二次和第一次开关机测量之间的相时延差,△31表示第三次和第一次开关机测量之间的相时延差,△32表示第三次和第二次开关机测量之间的相时延差。由测试结果可知,系统时延控制精度优于0.01ns。

基于相时延的测量结果具有测量精度高的优点,但是可能存在时延模糊。对于300MHz信号而言,其时延模糊约为3.33ns。为了判断同步采集误差是否存在相时延模糊,采用群时延的测量方法,再次对系统同步采集特性进行测试。

(2)基于群时延的同步采集时延误差测试:

相比于相时延,群时延的测量精度较低,但其时延测量无模糊范围大,从而能够正确求取待测系统的时延值。基于群时延的同步采集测试原理与相时延相同,即求取多次开关机测量结果之间的群时延差。系统测试框图如图18所示。采用频率间隔为100kHz的PCAL信号作为测试信号,原子钟仍采用Symmetricom Datum X72铷钟,利用信号源产生100MHz的同源频标。分别对PCAL信号进行三次开关机采集记录,DBBC参数设置为:信号带宽为4MHz、中心频率为300MHz、量化位数8bit、复信号输出。提取各次记录PCAL信号的相位,根据带内各频点的相频特性,求取每次开机后被测系统的群时延以及多次测量结果之间的群时延差,如图19所示。由图19(b)可知,基于群时延测量的开机同步误差约为0.5ns。结合相时延的测量结果可知,0.5ns小于300MHz的周期(3.33ns)。因此,基于相时延的同步采集误差测量结果不存在模糊,0.01ns的开机同步误差即为真实的开机同步采集时延稳定性能。

其中,CLK、ADC和FPGA芯片还可以有其它选项,本发明也在CLK芯片AD9520、ADC芯片EV10AQ190和FPGA芯片kintex7实现过,可以得到同样的性能。

综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。