一种声纳信号模拟器延时控制的声纳信号模拟方法及装置

文献发布时间:2023-06-19 09:27:35

技术领域

本发明属于水声信号处理、电子技术领域,涉及一种声纳信号模拟器延时控制的声纳信号模拟方法及装置。

背景技术

在研制和交付声纳装备时,需要进行大量的(湖)海试验,对装备的声系统及总体性能进行有效的评估和检验。试验需要消耗大量人力、物力和财力,并且试验周期长,收海况、气候等因素影响较多,试验次数也有限,而路上半实物仿真系统相对于湖试或海试不但能够节省大量的人力和物力,而且能够提供科研、生产和使用过程中的系统测试。

在声纳信号处理领域,现有的声纳信号模拟器延时控制方法大部分采用了DSP实现,这些方法均为串行的工作方式,即使多核并行,往往运算控制机制也不够完善,工作效率不及并行运算的FPGA。在使用FPGA实现的方法中,《CN104022782B[中文]一种数字式多通道模拟信号发生方法》在数字信号方面提出通过使用随机寄存器循环读址的方法实现时延与串并转换,然而该方法在信号时延与资源占用方面仍有改进的可能。

发明内容

要解决的技术问题

为了避免现有技术的不足之处,本发明提出一种声纳信号模拟器延时控制的声纳信号模拟方法及装置,克服目前在FPGA中实现声纳信号模拟占用资源巨大的问题,本发明的方法以一种小型化的声纳信号模拟系统实现,同时采用一种占用资源较少的信号延时控制方法。

技术方案

一种声纳信号模拟器延时控制的声纳信号模拟方法,其特征在于:数组梯级组合型移位寄存器组成的多抽头移位寄存器,通过异相位时钟分别控制移位寄存器的数据读入与读出,步骤如下:

步骤1:通过Matlab产生所需单周期信号数据,并存入FPGA芯片的ROM中;采用DDS的方法将ROM中的单周期信号数据生成声纳信号存入FIFO;

步骤2:读入逻辑由时钟触发,触发后判断FIFO的EMPTY信号是否为低电平,若EMPTY为低电平则读入数据,移位寄存器读入该数据进行移位操作;

步骤3:每读入一次数据读入计数加1,当读入计数累加至移位寄存器最大值后,且读出逻辑由与读入逻辑时钟相比延迟90°的异相位时钟触发,触发后各个通道根据不同的地址读取移位寄存器中的数据;

第i个通道的读出数据的地址ADDR

ADDR

addr为声纳阵列模型计算的时延地址差值;

步骤4:对不同的地址读取移位寄存器中的数据进行D/A数模转换得到模拟信号,再进行加噪滤波放大得到模拟的水声输出信号。

以AMP

所述AMP

所述声纳阵列模型计算的时延地址差值addr的获得:

输出信号的频率

计算多普勒频率f

计算频率控制字

时延地址差值addr=f

所述水中声速c取1500m/s。

一种实现所述声纳信号模拟器延时控制的声纳信号模拟方法的装置,其特征在于包括处理器模块、数字可编程逻辑阵列模块、数模转换模块和低通滤波器;处理器模块输入端与上位机相连接,输出端与数字可编程逻辑阵列模块连接,数字可编程逻辑阵列模块形成多个通道与相应的数模转换模块连接;数模转换模块分别依次与相对应的低通滤波器连接,各个低通滤波器与对应的水声换能器连接,组成一路水声信号发生通道。

所述处理器模块为集成于数字可编程逻辑阵列模块上的ARM处理器。

所述数字可编程逻辑阵列模块采用FPGA。

有益效果

本发明提出的一种声纳信号模拟器延时控制的声纳信号模拟方法及装置,通过FPGA使用DDS的方式生成信号,充分的利用了FPGA上的运算资源,ARM只需要根据声纳信号模型计算频率控制字和相位控制字交由FPGA完成DDS。

本发明将信号时延模块与串并转换模块结合,通过调整可变长度移位寄存器长度以调整时延大小,同时使用梯级组合型移位寄存器有效的降低了移位寄存器触发链组合逻辑所需要的资源。

本发明通过FPGA的并行处理能力同步的产生多路不同时延的并行信号,避免了采用循环读取地址的方式导致系统效率降低。

附图说明

图1:声纳信号模拟系统组成框图;

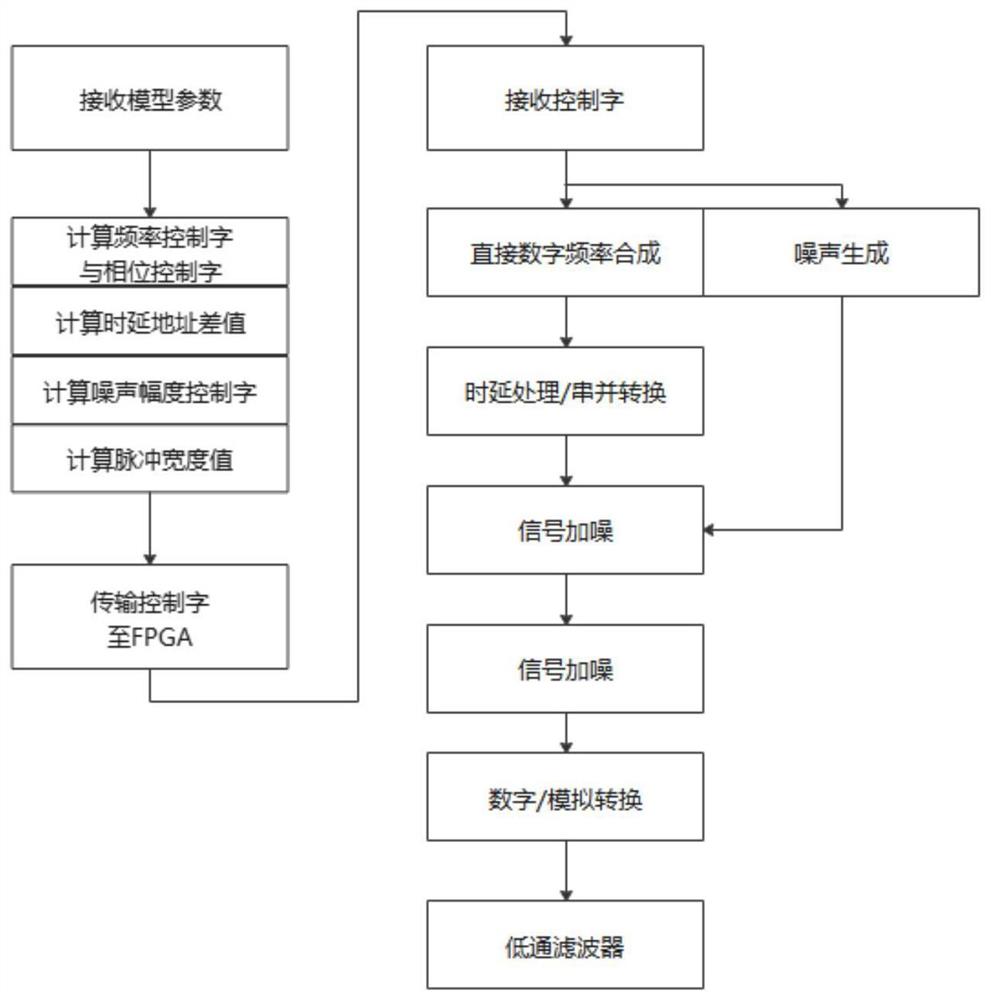

图2:系统工作流程图;

图3:时延模块示意图;

具体实施方式

现结合实施例、附图对本发明作进一步描述:

如图1所示,声纳信号模拟系统的主要组成框架如下:包括处理器模块、数字可编程逻辑阵列模块、数模转换模块、低通滤波器,所述处理器模块与上位机相连接,与所述数字可编程逻辑阵列模块连接;所述数字可编程逻辑阵列模块形成多个通道与相应的数模转换模块连接;所述数模转换模块分别依次与相对应的低通滤波器连接;所述各个低通滤波器与对应的水声换能器连接,可组成一路水声信号发生通道。

所述处理器模块与上位机连接,所述上位机将目标模型的参数发送至处理器模块;系统的输出为经过数模转换、低通滤波以及放大后生成的电信号,可以以此驱动水声换能器。

所述处理器模块为集成于数字可编程逻辑阵列模块上的ARM处理器,所述处理器模块通过亮点模型,根据从上位机输入的参数计算信号生成所需参数,并输出至数字可编程逻辑阵列模块,其中参数包括频率控制字、相位控制字、时延地址差值、噪声幅度控制字、信号脉宽值。

所述数字可编程逻辑阵列模块由FPGA实现,其特征在于所述FPGA中包括DDS模块,噪声生成模块,串并转换时延模块,信号加噪模块以及数模转换接口模块;所述直接数字频率合成器模块与串并转换时延模块连接;所述串并转换时延模块生成多路时延信号,并与对应的信号加噪模块通道连接;所述噪声生成模块连接生成多路噪声并与信号加噪模块连接;所述信号加噪模块各个通道与对应的数模转换接口模块连接。

所述的直接数字频率合成器模块,其特征在于通过Matlab产生所需单周期信号数据,并存入FPGA芯片的ROM中;所述直接数字频率合成器模块通过从处理器模块接收的相位控制字与频率控制字,其中相位控制字可调整输出正弦波的相位,频率控制字可以调整输出信号的频率,直接数字频率合成器模块输出进入FIFO,等待串并转换时延模块读取。

所述串并转换时延模块,其特征在于数组梯级组合型移位寄存器组成的多抽头移位寄存器,通过异相位时钟分别控制移位寄存器的数据读入与读出,其运行逻辑如下:

(1)读入逻辑由时钟触发,触发后判断FIFO的EMPTY信号是否为低电平,若EMPTY为低电平则读入数据,读入后数据进行移位操作;

(2)每读入一次数据读入计数加1,当读入计数累加至移位寄存器最大值后读出使能;

(3)读出逻辑由与读入逻辑时钟相比延迟90°的异相位时钟触发,触发后各个通道根据不同的地址读取移位寄存器中的数据;

(4)第i个通道的读出数据的地址ADDR

ADDR

其中n为从处理机模块输入的时延地址差值,由亮点目标模型计算出。

上位机可通过以太网向系统发送模型参数,其中包括信号频率f、信噪比SNR、信号脉宽T、目标方位角θ、目标径向速度v、阵元数N、阵元间距d;经由处理器模块计算后,得到频率控制字、相位控制字、时延地址差值、信号幅度控制字、噪声幅度控制字、信号脉宽值并将这些参数发送至数字可编程逻辑阵列模块;数字可编程逻辑阵列模块中,根据处理器模块传输的数据实现以下功能:

(1)根据频率控制字、相位控制字以及信号脉宽值实现直接数字频率合成;

(2)根据时延地址差值实现时延以及串并转换功能;

(3)根据噪声幅度控制字实现信号加噪功能;

然后通过数模装换接口向数模转换模块发送数据;信号经数模转换成为模拟信号后经过低通滤波器,得到模拟声纳信号。

进一步地,如图2中所示,频率控制字的计算与生成信号频率以及FPGA芯片ROM的深度有关,输出信号的频率f

其中,f

(1)计算多普勒频率f

f

其中c为水中声速,通常取1500m/s。

(2)计算频率控制字FCW

进一步的,相位控制字用于控制也可以对影响DDS地址查找,通常情况下相位控制字为0。

进一步的,时延地址差值addr的值由阵元间距、目标方位角以及DDS生成信号采样频率f

addr=f

其中f

进一步的,噪声幅度控制字AMP

(1)计算信号幅度与噪声幅度的比值S/N

S/N=exp(SNR/20)

(2)将S/N的倒数量化为8bit数据AMP

DDS:进一步的,信号脉宽值N

FPGA中需要实现功能模块有DDS模块,噪声生成模块,串并转换时延模块,信号加噪模块以及数模转换接口模块,其具体框架及流程如图1。

所述DDS模块接收频率控制字与相位控制字,配合相位累加寄存器生成查询表地址,然后通过地址查询的方式生成数据,该DDS的频率步进精度Δf与相位步进精度Δp计算公式如下:

Δp=(2π/2

其中,2

所述噪声生成模块同样基于读取试先存储在ROM中数据的方法生成噪声。具体实现方法为,使用MATLAB生成服从一定均值和方差的噪声信号。然后将数据存在FPGA中进行回放,以此来产生高斯白噪声。

如图3,所述的串并转换时延模块使用基于RAM的多抽头移位寄存器,这里以1bit数据为例,通过约束让其形成梯级组合型移位寄存器,同时也通过约束让其输出逻辑综合为单独的寄存器,具体操作如下:

(1)首先需要评估工程需要的最大延时τ

M>τ

M=2

其中n为梯级数;

(2)创建梯级组合型移位寄存器,梯级组合型移位寄存器的特点每一个梯级由一个2:1多路复用器控制,每个复用器都有单独的控制位,共n个,二者呈指数关系;且是由不同长度的移位寄存器组成的梯级,第0级由20=1个触发器组成,第1级由2

(3)由于梯级组合型移位寄存器的长度可调,发明中通过将N-1个梯级组合型移位寄存器串联的方式,可以得到第i个阵元的输出信号为第i-1组梯级组合型移位寄存器的输出。

(4)如果使用触发器搭建此移位寄存器会消耗大量的触发器资源,而使用基于RAM的移位寄存器可以有效地回避这个问题,同时也应注意到基于RAM的移位寄存器限制了最小长度为3,本示例中采用触发器组成梯级组合型移位寄存器的第0级与第1级;在延时精度要求不高的情况下可以忽略第0级与第1级。

进一步的,在对移位寄存器进行操作时我们采用异相位的时钟分别进行读写操作,具体逻辑如下:

(1)读入逻辑由时钟触发,触发后判断FIFO的EMPTY信号是否为低电平,若EMPTY为低电平则读入数据,读入后数据进行移位操作;

(2)每读入一次数据读入计数加1,当读入计数累加至移位寄存器最大值后读出使能;

(3)读出逻辑由与读入逻辑时钟相比延迟90°的异相位时钟触发,触发后各个通道根据不同的地址读取移位寄存器中的数据;

(4)第i个通道的读出数据的地址ADDR

ADDR

其中n为从处理机模块输入的时延地址差值,由亮点目标模型计算出。实际上,读出地址用于控制可变长度移位寄存器的长度。

所述的信号加噪模块对每一路通道的信号进行加噪,由于信号的加噪处理有可能导致进位,这里的处理方法是进行加噪后对数据进行一次左移并舍弃掉最后一位,以保证数据不会溢出。

所述的低通滤波器应保证通带带宽足够大,因为经数字模拟转换后的信号中包含需要的白噪声,这也对数字模拟转换模块的噪声控制提出一定的有要求,需要保证数模装换产生的噪声不会对信噪比产生影响。

本应用示例中,所述声纳信号模拟系统基于SOC FPGA实现,当前,不少FPGA集成了强大的ARM处理器以及大量的FPGA资源,在ARM的控制下,FPGA可以解放出大量用于计算的资源,同时由于单板就可以完成从接收参数到生成多路数字信号的功能。