一种级联半带插值滤波器结构

文献发布时间:2023-06-19 09:27:35

技术领域

本发明涉及大规模数字集成电路技术领域,特别涉及一种级联半带插值滤波器结构。

背景技术

DUC(Digital Up Converter,数字上变频器)是软件无线电中发射机的核心部分,它的基本功能将基带信号其上变频到载波频率上,再经过发射天线发射出去。

目前使用较多的方法是半带插值滤波器,其最大的特点是通过半带滤波器有一半的系数为0,可以减少一半的计算量;半带插值滤波器进行采样率的变换是数字上变频的关键技术之一。此外,对低采样率的基带信号直接模拟采样会带来较大的量化误差,因此运用半带插值滤波器的方法可以降低模拟滤波器设计的难度,此外,运用级联半带插值的方法将低速的基带信号转换为高速的数字数据流,便于实现且成本较低,在雷达发射系统中有着举足轻重的地位。

发明内容

本发明的目的在于提供一种级联半带插值滤波器结构,为高速DUC中插值滤波器的设计提供一种高速高精度且面积相对较小的解决方案。

为解决上述技术问题,本发明提供了一种级联半带插值滤波器结构,包括:

串并转换模块,根据输入和输出数据的关系进行串并行转换;

时钟分频模块,由基准时钟通过分频的方法得到多个时钟,为级联结构中的各个环节提供不同频率的时钟;

半带插值滤波器模块,将输入数据进行数字信号处理后输出。

可选的,所述串并转换模块对输入的2路数据串并转换后得到4路输出。

可选的,所述时钟分频模块由一个基准时钟通过数字分频的方法得到2、4、8和16分频的时钟。

可选的,所述半带插值滤波器模块包括延迟模块和数字信号处理模块,输入数据依次经过所述延迟模块和所述数字信号处理模块进行处理,得到4路输出数据。

可选的,所述延迟模块按照时钟顺序将输入数据延迟若干个时钟,包括:

将序列X(n)延迟k拍得到序列X(n-k);当设计级联半带插值滤波器结构为2路输入,4路输出时,两路输入为X0和X1;

先在每相邻两项输入的数据间插入0值形成新的数值序列;该数值序列经过延迟模块之后可得到新的序列,即X(n-0)、X(n-1)、X(n-2)、X(n-3)、X(n-4)…,其中,所有奇数项(X(n-2*k-1),k=0,1,2…)均为插值0项,而一路输入X0经过延迟得到X(n-0)、X(n-4)、X(n-8)…X(n-4*k),另一路输入X1经过延迟得到X(n-2)、X(n-6)、X(n-10)…X(n-4*k+2),k=1,2…。

可选的,所述数字信号处理模块包括加法器、乘法器、求和运算模块和溢出处理模块。

可选的,当滤波器所有参数共为N(N=4*i+3,i=0,1,2…)个时,根据半带插值滤波系数的关系可知,所有系数关于中间系数对称,因此所述加法器将系数相同的两相进行加法计算,即add

可选的,所述乘法器根据所述加法器计算的结果,再与半带插值滤波器的系数C

可选的,所述求和运算模块是根据所述乘法器所计算的结果,对所有项进行求和计算得到半带插值滤波后的结果,即sum=mul

可选的,所述数据溢出处理模块对数据计算、截位过程中存在的数据溢出进行处理,当定义输入输出bits为M位的数据[M-1:0]时,经过数字信号处理模块进行有符号数计算后得到bits为(M+1)位的数据[M:0],需要对数据进行溢出处理,处理方法为:针对最高位符号位和次最高位符号位将数据分为四种情况:

当[M:M-1]=2‘b10时,数据发生了负溢出,从负的满量程反转到正数,出现错误,因此需处理为负的最大值;

当[M:M-1]=2’b01时,数据发生了正溢出,从正的满量程反转到负数,出现错误,因此需处理为正的最大值;

当[M:M-1]=2’b00或2’b11时,输出数据的两位符号位相同即并未发生溢出,因此只需对其进行截取[M-1:0]位即可。

在本发明提供的级联半带插值滤波器结构中,包括串并转换模块、时钟分频模块和半带插值滤波器模块。串并转换模块根据输入和输出数据的关系进行串并行转换;时钟分频模块由基准时钟通过分频的方法得到多个时钟,为级联结构中的各个环节提供不同频率的时钟;半带插值滤波器模块将输入数据进行数字信号处理后输出。本发明能够有效提高原信号的频率,当为2倍半带插值滤波器时,信号频率扩展到2倍,4倍半带插值滤波器和8倍半带插值滤波器同理可得到相应4倍和8倍的扩频。

附图说明

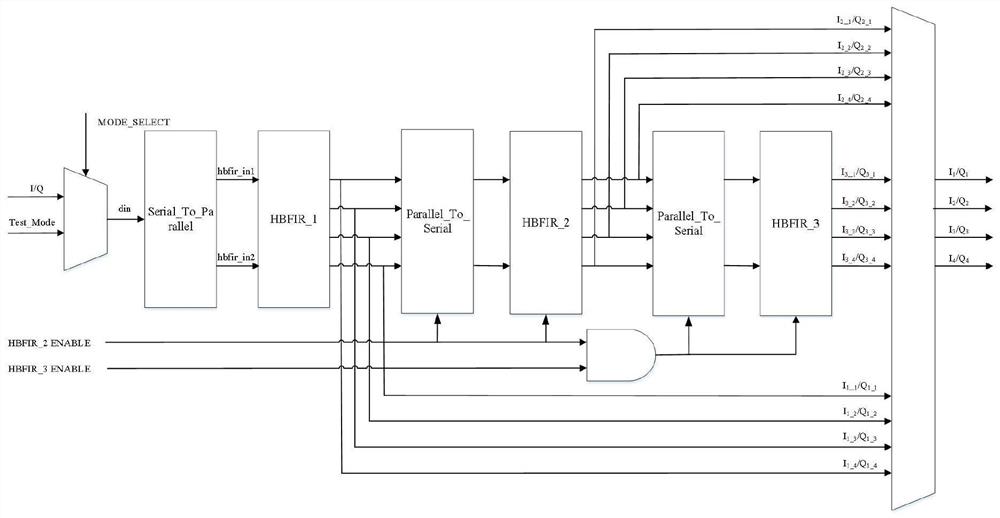

图1是本发明提供的级联半带插值滤波器结构示意图;

图2是半带滤波器插值图解;

图3是第一级半带滤波器数字信号处理结构示意图;

图4是4路并行输入转换为2路并行输出实现原理图;

图5是1路串行输入转换为2路并行输出实现原理图。

具体实施方式

以下结合附图和具体实施例对本发明提出的一种级联半带插值滤波器结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

实施例一

本发明提供了一种级联半带插值滤波器结构,其设计框图如图1所示,包括串并转换模块(Serial_To_Parallel)、时钟分频模块(Clock Divider)和半带插值滤波器设计模块(HalfBandFiliter)。所述串并转换模块主要完成顶层输入和级联半带滤波器间数据的串并转换;所述时钟分频模块主要对级联半带插值滤波器的各个环节提供不同频率的时钟,从而正确的对数据进行传输和转换;所述半带插值滤波器模块主要完成插值滤波的功能,即在每相邻两项数据间插入0值,如图2所示,将所得到的新序列进行数字信号处理后输出。

具体的,所述串并转换模块主要是对输入输出数据进行串并行转换的功能,如图5所示,即当2路输入信号,经过串并转换后得到4路输出,图5中只画出1路的转换过程,另一路同理可得出;当为多个半带插值滤波器级联时,级联半带插值滤波器间的数据转换如图4所示,即将4路并行输入转换为2路并行输出。

所述时钟分频模块主要是对级联半带插值滤波器的各个环节提供不同的时钟,进而使数据能够正确的进行传输和转换,避免重复和丢失的情况,时钟分频负责在不同的配置下为半带插值滤波器模块和串并转换模块提供2、4、8和16分频的时钟,设半带插值滤波器模块的4路并行输出的总时钟频率为CLK_Frequency,则整个级联半带滤波器设计各个部分的时钟频率与CLK_Frequency的比值关系如下表所示,表格中的分频比例在图1中均可找到相应模块:

所述半带插值滤波器模块主要包括延迟模块(Delay)、数字信号处理模块(Digital Signal Processor),如图3所示,其中:

所述延迟模块的作用:按照时钟顺序将输入数据进行延迟若干个时钟,然后进行数字滤波处理,当为4路输出时,每路延迟序列X(n)延迟k拍可得到序列X(n-4*k);当设计级联半带插值滤波器结构为2路输入,4路输出时,两路输入为X0和X1,根据半带滤波器的特点即先在每相邻两项输入的数据间插入0值形成新的数值序列;该序列经过延迟模块之后可得到新的序列,即X(n-0)、X(n-1)、X(n-2)、X(n-3)、X(n-4)…等,其中,所有奇数项(X(n-2*k-1),k=0,1,2…)均为插值0项,而一路输入X0经过延迟得到X(n-0)、X(n-4)、X(n-8)…X(n-4*k),另一路输入X1经过延迟得到X(n-2)、X(n-6)、X(n-10)…X(n-4*k+2),k=1,2…。

数字信号处理模块(Digital Signal Processor):根据半带插值滤波器的公式和性质可知,数字插值滤波主要包含、加法器(Add)、乘法器(Multiply)、求和运算模块(Sum)和溢出处理模块(Overflow);

第1路:Y(n-0)=C

=C

第2路:Y(n-1)=C

=C

第3路:Y(n-2)=C

=C

第4路:Y(n-3)=C

=C

加法器(Add):当滤波器长度为55时,根据半带插值滤波系数的关系可知,所有系数关于中间系数对称,因此将系数相同的两项进行加法计算,即add

乘法器(Multiply):根据上述加法器计算的结果,再与半带插值滤波器的系数C

求和运算模块(Sum):根据上述乘法器所计算的结果,对所有项进行求和计算得到半带插值滤波后的结果,即sum=mul

数据溢出处理模块(Overflow):在数据计算、截位等过程中会存在数据溢出现象,因此需要对正负满量程最大值进行溢出处理,当定义输入输出bits为16位的数据[15:0]时,经过数字信号处理模块进行有符号数计算后得到bits为16位的数据[16:0],因此需要对数据进行溢出处理,处理方法为:针对最高位符号位和次最高位符号位将数据分为四种情况,即当[16:15]=2’b10时,数据发生了负溢出,从负的满量程反转到正数,出现错误,因此需处理为负的最大值;当[16:15]=2’b01时,数据发生了正溢出,从正的满量程反转到负数,出现错误,因此需处理为正的最大值;当[16:15]=2’b00或2’b11时,输出数据的两位符号位相同即并未发生溢出,因此只需对其进行截取[15:0]位即可。

如图3所示,当为4路输出时,通过滤波器系数的相关性质可知第2、4路是通过延迟移位得到,不需要做相关计算;第1、3路是通过半带插值滤波器进行计算得到,因此需要对输出数据进行时序一致性处理,处理方法为:上述半带插值滤波器计算由数据处理模块(加法器、乘法器、求和计算模块和数据溢出处理模块)所进行延迟的拍数为8,因此可知最终的第2和第4相输出为X(n-60)和X(n-62),而第1和第3相则计算完直接输出即可。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。