FPGA芯片内的时钟生成单元

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及FPGA(现场可编程逻辑门阵列)芯片领域,尤其涉及一种FPGA芯片内的时钟生成单元。

背景技术

随着半导体技术的不断发展,FPGA芯片已逐渐在人工智能、大数据分析、云计算、网络通信、图像处理、机器人、芯片验证等诸多领域得到广泛的引用。在少数领域中,FPGA芯片甚至正在取代CPU、GPU或DSP的地位,成为主导芯片。然而,FPGA芯片的使用从硬件电路到逻辑设计都需要非常专业的技术,稍不小心就会产生致命性错误,导致整个系统无法正常工作。在诸多致使FPGA芯片无法工作的因素中,因硬件设计缺陷导致FPGA内部没有一个有效的时钟是最常见的问题。因此,如何在现有硬件的基础上为FPGA提供一个合适的参考时钟成为了亟待解决的问题。

针对现有硬件FPGA缺少参考时钟的问题,目前主要有三种解决方案。

第一种解决方案为硬件改版方案。硬件改版方案通过重新设计制造FPGA硬件来给FPGA提供参考时钟。由于此方案需要重新设计并重新制造硬件,因此方案实施时间长、成本高,而且在重新制造过程中可能会引入其他风险。

第二种解决方案为硬件维修方案。硬件维修方案通过飞线等方式给FPGA提供参考时钟,因此需要投入一定的硬件维修成本。飞线方式需要硬件板卡自身具备相应的参考时钟源,并且FPGA专用时钟引脚需要具备飞线引入点,两者缺一不可。此外,在飞线过程中容易造成硬件的二次损坏,无法保证通过飞线维修引入的时钟的可靠性。

第三种解决方案利用其它与FPGA通信的接口模拟时钟信号为FPGA提供时钟。此方案不仅要求FPGA外部具有与FPGA通信的接口,而且要求通信接口可以模拟时钟,与此同时模拟时钟的引脚必须连接在FPGA时钟专用引脚上。第三种解决方案对硬件环境的要求较高,一般无法满足。另外,该方案也同样无法保障时钟的可靠性。

因此,需要提供一种经济且可靠的解决方案,以便为FPGA芯片提供参考时钟。

发明内容

有鉴于此,本发明提出了一种FPGA芯片内的时钟生成单元,其能够解决以上技术问题。

本发明的技术方案如下:

一种FPGA芯片内的时钟生成单元,包括:

输入选择器,其包括时钟使能端、输入选择器输入端和输入选择器输出端;

查找表,其包括查找表输入端和查找表输出端,所述查找表被配置为:当所述查找表输入端为低电平时,所述查找表输出端输出高电平,当所述查找表输入端为高电平时,所述查找表输出端输出低电平;

延时链,其包括延时链输入端和延时链输出端,所述延时链输出端相对于所述延时链输入端具有延时链延时D

其中,所述输入选择器输入端与所述延时链输出端连接,所述输入选择器输出端与所述查找表输入端连接,所述查找表输出端与所述延时链输入端连接,所述输入选择器被配置为:当所述时钟使能端为低电平时,所述输入选择器输出端为低电平,当所述时钟使能端为高电平时,所述输入选择器输出端输出所述输入选择器输入端的电平。

根据本发明一优选实施例,所述查找表输出端还与时钟输出端连接。

根据本发明一优选实施例,所述查找表输出端与所述时钟输出端之间连接有时钟缓冲器。

根据本发明一优选实施例,所述输入选择器输出端相对于所述输入选择器输入端具有输入选择器延时D

根据本发明一优选实施例,所述时钟信号的频率为f=1/(2(D

根据本发明一优选实施例,所述延时链包括串联的n个延时单元,每个延时单元产生延时t,所述延时链延时D

一种FPGA芯片,该FPGA芯片实现以上描述的时钟生成单元。

由以上技术方案可以看出,本发明的FPGA芯片内的时钟生成单元利用FPGA芯片内的输入选择器、查找表和延时链,得到稳定的时钟输出。本发明的时钟生成单元无需在硬件上对FPGA做任何更改或维修,不仅可以省去因硬件改版或硬件维修带来的成本,而且可以避免因硬件改版或维修带来的风险,是一种经济又可靠的解决方案。

附图说明

参照附图,本发明的公开内容将变得更易理解。本领域技术人员容易理解的是,这些附图仅仅用于举例说明本发明的技术方案,而并非意在对本发明的保护范围构成限定。图中:

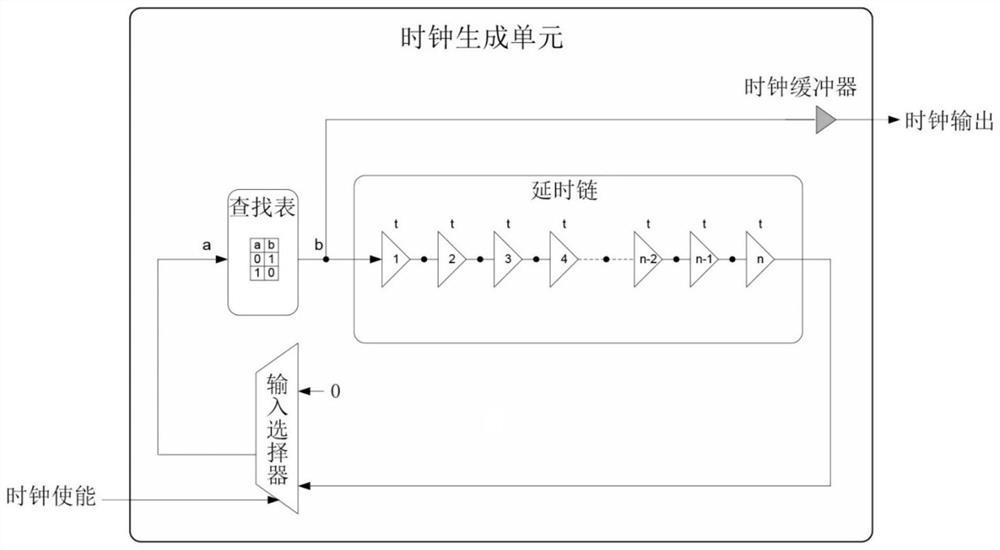

图1为根据本发明实施例的FPGA内的时钟生成单元的结构示意图。

具体实施方式

为了使本发明的目的、技术方案和优点更加清楚,下面结合附图和具体实施例对本发明进行详细描述。

图1为根据本发明实施例的FPGA内的时钟生成单元的结构示意图。如图1所示,时钟生成单元包括输入选择器、查找表和延时链。

在本实施例中,输入选择器包括使能端、输入选择器输入端和输入选择器输出端。信号从选择器输入端到选择器输出端会产生选择器延时D

在本实施例中,查找表包括查找表输入端和查找表输出端。信号从查找表输入端到查找表输出端会产生查找表延时D

在本实施例中,延时链包括延时链输入端和延时链输出端。延时链输出端相对于延时链输入端具有延时链延时D

以下将结合图1动态地介绍根据本发明的时钟生成单元生成时钟信号的具体步骤。在以下描述中,二进制数0代表逻辑“0”(即低电平),二进制数1代表逻辑“1”(即高电平)。

1)当时钟使能端为0(即时钟使能关闭)时,选择器输出常值0。此时,查找表输入端a为常值0,查找表输出端b为常值1。

2)当时钟使能端变为1(即时钟使能开启)时,输入选择器输出端为1,查找表输入端a为1,查找表输出端b为0。

3)随后,查找表输出端b的0值经过延时链延时n个t(即n×t)后到达输入选择器输入端。由于此时使能端为1,因此输入选择器输出端输出输入选择器输入端的值0。

4)由于查找表输入端a与输入选择器输出端连接,因此查找表输入端a变为0,查找表输出端b变为1。

5)随后,查找表输出端的值1经过延时链延时n个t(即n×t)后到达输入选择器输入端。由于此时使能端为1,因此输入选择器输出端输出输入选择器输入端的值1。

6)由于查找表输入端a与输入选择器输出端连接,因此查找表输入端a变为1,查找表输出端b变为0。

7)重复步骤3至6,在查找表输出端b输出稳定的时钟信号。

通过以上步骤根据本实施例的时钟生成单元生成1(高电平)和0(低电平)交替的方波时钟信号。当需要停止产生时钟信号时,可以将时钟使能端设为0(低电平)。此时查找表输入端为低电平,查找表输出端恒定为1,因此不再产生1和0交替的时钟信号。

从以上步骤可以看出,查找表输出端b从值1开始,需要经过延时链、输入选择器,再经查找表反相之后变成0,这个过程的经过的时间为延时链延时D

在本实施例中,由于时钟输出端与查找表输出端连接,因此时钟信号是从查找表输出端产生的。需要理解的是,在其他实施例中,时钟输出端也可以与例如查找表输入端或延时链输出端连接,这两种连接方式都可以产生稳定的时钟输出,时钟信号的周期和频率与查找表输出端输出的时钟信号相同。

在现有硬件FPGA缺少参考时钟的情况下,可以通过软件编程的方式在FPGA中实现以上描述的时钟生成单元,从而为FPGA提供稳定且可靠的时钟。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。