应用于复数域滤波器的高GWB高输出摆幅运放

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及集成电路技术领域,特别涉及一种应用于复数域滤波器的高GWB高输出摆幅运放。

背景技术

运算放大器是许多模拟系统和混合信号系统中的一个完整部分,大量的具有突通复杂程度的运放被用来实现各种功能:从直流偏置的产生到高速放大或滤波。伴随着每一代CMOS工艺,由于电源电压和晶体管沟道长度的减小,为运放的设计不断提出复杂的课题,多数运放都被设计成通用的模块,适用于各种不同应用的要求。设计者企图制造一种理想运放,例如,具有非常高的电压增益,非常高的输入阻抗以及非常低的输出阻抗,但是却以牺牲其它性能为代价,例如速度、输出摆幅和功耗等。现有的运放设计认识到各参数间的折衷关系,这种折衷最终要求在整体设计中进行多方面的综合考虑,因而我们必须知道满足每一个参数的适当的数值。例如,如果对速度要求高,而对增益误差要求不高,则电路的结构选择应偏向前者,可能会牺牲后者。

发明内容

本发明提供了一种应用于复数域滤波器的高GWB高输出摆幅运放,其目的是为了传统的运放输出阻抗高且输出摆幅会受到限制的问题。

为了达到上述目的,本发明的实施例提供了一种应用于复数域滤波器的高GWB高输出摆幅运放,包括:

主运算放大器,所述主运算放大器的第一端与Inp端电连接,所述主运算放大器的第二端与Inn端电连接,所述主运算放大器的第三端与OUTp端电连接,所述主运算放大器的第四端与OUTn端电连接,负载电容的第一端与所述主运算放大器的第三端电连接,所述负载电容的第二端与所述主运算放大器的第四端电连接;

比较放大电路,所述比较放大电路的第一端与所述主运算放大器的第五端电连接;

共模电平检测电路,所述共模电平检测电路的第一端与所述主运算放大器的第三端电连接,所述共模电平检测电路的第二端与所述主运算放大器的第四端电连接,所述共模电平检测电路的第三端与所述比较放大电路的第二端电连接;

使能电路,所述使能电路的第一端输入EN信号,所述使能电路的第二端输入ENb信号,所述使能电路的第三端输入参考电压Vref,所述使能电路的第三端与所述比较放大电路的第三端电连接;

电流镜电路,所述电流镜电路的第一端与所述主运算放大器的第六端电连接,所述电流镜电路的第二端与所述比较放大电路的第四端电连接,所述电流镜电路的第三端与所述比较放大电路的第五端电连接,所述电流镜电路的第四端与所述使能电路的第四端电连接,所述电流镜电路的第五端与所述使能电路的第五端电连接,所述电流镜电路的第六端与所述使能电路的第六端电连接。

其中,所述主运算放大器包括:

第一PMOS管,所述第一PMOS管的栅极端与Inp端电连接;

第二PMOS管,所述第二PMOS管的源极端与所述第一PMOS管的源极端电连接,所述第二PMOS管的栅极端与Inn端电连接;

第三PMOS管,所述第三PMOS管的漏极端与所述第一PMOS管的源极端电连接;

第一NMOS管,所述第一NMOS管的漏极端与所述第一PMOS管的漏极端电连接;

第二NMOS管,所述第二NMOS管的漏极端与所述第二PMOS管的漏极端电连接,所述第二NMOS管的栅极端与所述第一NMOS管的栅极端电连接,所述第二NMOS管的源极端与所述第一NMOS管的源极端电连接;

第三NMOS管,所述第三NMOS管的栅极端与所述第二NMOS管的漏极端电连接,所述第三NMOS管的源极端与所述第二NMOS管的源极端电连接;

第四NMOS管,所述第四NMOS管的栅极端与所述第一NMOS管的漏极端电连接,所述第四NMOS管的源极端与所述第三NMOS管的源极端电连接;

第四PMOS管,所述第四PMOS管的漏极端分别与所述第三NMOS管的漏极端和OUTp端电连接;

第五PMOS管,所述第五PMOS管的源极端与所述第四PMOS管的源极端电连接,所述第五PMOS管的栅极端与所述第四PMOS管的栅极端电连接,所述第五PMOS管的漏极端分别与所述第四NMOS管的漏极端和OUTn端电连接。

其中,所述比较放大电路包括:

第六PMOS管;

第七PMOS管,所述第七PMOS管的源极端与所述第六PMOS管的漏极端电连接,所述第七PMOS管的栅极端与所述第三PMOS管的栅极端电连接;

第八PMOS管,所述第八PMOS管的源极端与所述第七PMOS管的漏极端电连接,所述第八PMOS管的栅极端与所述第二PMOS管的栅极端电连接;

第九PMOS管,所述第九PMOS管的源极端与所述第八PMOS管的源极端电连接,所述第九PMOS管的栅极端与所述第一PMOS管的栅极端电连接,所述第九PMOS管的漏极端与所述第八PMOS管的漏极端电连接;

第五NMOS管,所述第五NMOS管的漏极端分别与所述第九PMOS管的漏极端和所述第一NMOS管的栅极端电连接,所述第五NMOS管的栅极端与所述第五NMOS管的漏极端电连接,所述第五NMOS管的源极端与所述第一NMOS管的源极端电连接。

其中,所述共模电平检测电路包括:

第十PMOS管,所述第十PMOS管的源极端与所述第六PMOS管的源极端电连接,所述第十PMOS管的栅极端与所述第四PMOS管的漏极端电连接;

第十一PMOS管,所述第十一PMOS管的源极端分别与所述第十PMOS管的源极端和所述第四PMOS管的源极端电连接,所述第十一PMOS管的栅极端与所述第五PMOS管的漏极端电连接,所述第十一PMOS管的漏极端分别与所述第十PMOS管的漏极端和所述第三PMOS管的源极端电连接。

其中,所述使能电路包括:

第六NMOS管,所述第六NMOS管的栅极端输入EN信号;

第十二PMOS管,所述第十二PMOS管的源极端与所述第六PMOS管的栅极端电连接,所述第十二PMOS管的栅极端输入ENb信号,所述第十二PMOS管的漏极端输入参考电压Vref。

其中,所述电流镜电路包括:

第四PMOS管;

第五PMOS管;

第六PMOS管;

第十三PMOS管,所述第十三PMOS管的栅极端与所述第十三PMOS管的漏极端电连接;

第十四PMOS管,所述第十四PMOS管的源极端与所述第十三PMOS管的源极端电连接,所述第十四PMOS管的栅极端与所述第十三PMOS管的栅极端电连接;

第七NMOS管,所述第七NMOS管的漏极端与所述第十四PMOS管的漏极端电连接,所述第七NMOS管的栅极端与所述第七NMOS管的漏极端电连接,所述第七NMOS管的源极端与所述第六NMOS管的源极端电连接;

第八NMOS管,所述第八NMOS管的栅极端与所述第七NMOS管的栅极端电连接,所述第八NMOS管的源极端分别与所述第七NMOS管的源极端和所述第五NMOS管的源极端电连接;

第十五PMOS管,所述第十五PMOS管的源极端分别与所述第十四PMOS管的源极端和所述第六PMOS管的源极端电连接,所述第十五PMOS管的栅极端与所述第十二PMOS管的源极端电连接。

其中,还包括:

第十六PMOS管,所述第十六PMOS管的源极端与所述第十五PMOS管的漏极端电连接,所述第十六PMOS管的栅极端与所述第十六PMOS管的漏极电连接,所述第十六PMOS管的漏极端与所述第八NMOS管的漏极端电连接。

其中,还包括:

电阻,所述电阻的第一端与所述第十三PMOS管的漏极端电连接,所述电阻的第二端与所述第六NMOS管的漏极端电连接。

其中,还包括:

当所述第十PMOS管和所述第十一PMOS管工作在线性区时,所述第十PMOS管和所述第十一PMOS管的跨导用下式计算:

gm10=gm11=μnCox(W/L)V

其中,gm10表示第十PMOS管的跨导,gm11表示第十一PMOS管的跨导,μn表示载流子迁移率,Cox表示单位面积的栅氧化层电容,W/L表示第十PMOS管和第十一PMOS管的宽长比,V

其中,还包括:

主运算运算放大器的增益带宽积,用下式计算:

GBW=gm/C

其中,GBW表示增益带宽积,gm表示MOS管跨导,C

本发明的上述方案有如下的有益效果:

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,能够提供较大的GBW,输出阻抗低,输出摆幅大,功耗低,具备一定的驱动能力,能够用于对GBW和输出摆幅要求高的应用。

附图说明

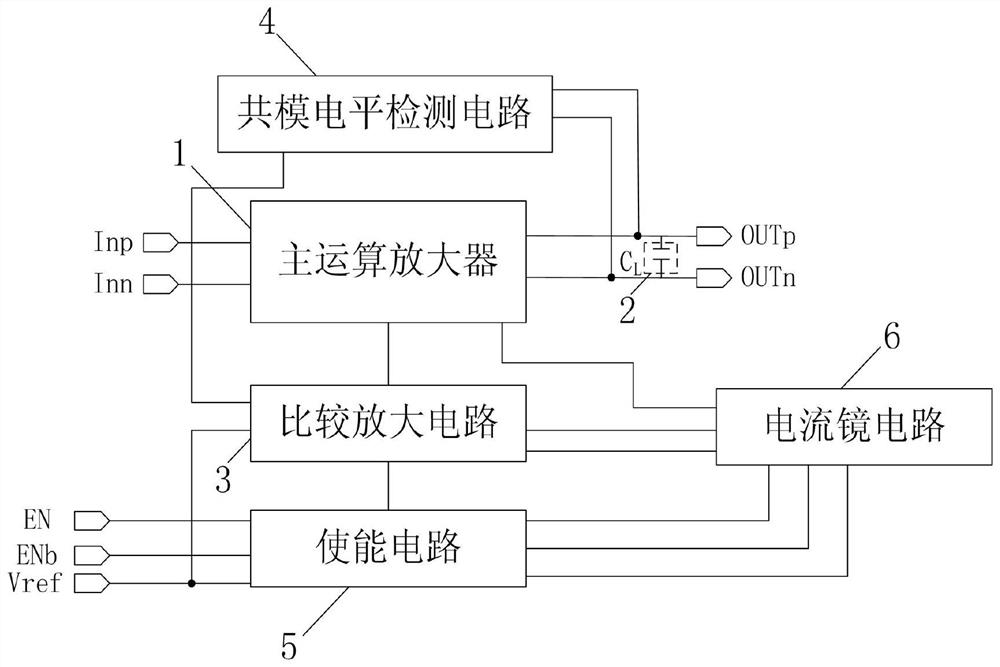

图1为本发明的总体结构示意图;

图2为本发明的具体结构示意图;

图3为本发明的开环幅频特性曲线示意图;

图4为本发明的各个性能参数的PVT仿真示意图;

图5为本发明的各个性能参数的MonteCarlo仿真示意图。

【附图标记说明】

1-主运算放大器;2-负载电容;3-比较放大电路;4-共模电平检测电路;5-使能电路;6-电流镜电路;7-第一PMOS管;8-第二PMOS管;9-第三PMOS管;10-第一NMOS管;11-第二NMOS管;12-第三NMOS管;13-第四NMOS管;14-第四PMOS管;15-第五PMOS管;16-第六PMOS管;17-第七PMOS管;18-第八PMOS管;19-第九PMOS管;20-第五NMOS管;21-第十PMOS管;22-第十一PMOS管;23-第六NMOS管;24-第十二PMOS管;25-第十三PMOS管;26-第十四PMOS管;27-第七NMOS管;28-第八NMOS管;29-第十五PMOS管;30-第十六PMOS管;31-电阻。

具体实施方式

为使本发明要解决的技术问题、技术方案和优点更加清楚,下面将结合附图及具体实施例进行详细描述。

本发明针对现有的运放输出阻抗高且输出摆幅会受到限制的问题,提供了一种应用于复数域滤波器的高GWB高输出摆幅运放。

如图1至图5所示,本发明的实施例提供了一种应用于复数域滤波器的高GWB高输出摆幅运放,包括:主运算放大器1,所述主运算放大器1的第一端与Inp端电连接,所述主运算放大器1的第二端与Inn端电连接,所述主运算放大器1的第三端与OUTp端电连接,所述主运算放大器1的第四端与OUTn端电连接,负载电容2的第一端与所述主运算放大器1的第三端电连接,所述负载电容2的第二端与所述主运算放大器1的第四端电连接;比较放大电路3,所述比较放大电路3的第一端与所述主运算放大器1的第五端电连接;共模电平检测电路4,所述共模电平检测电路4的第一端与所述主运算放大器1的第三端电连接,所述共模电平检测电路4的第二端与所述主运算放大器1的第四端电连接,所述共模电平检测电路4的第三端与所述比较放大电路3的第二端电连接;使能电路5,所述使能电路5的第一端输入EN信号,所述使能电路5的第二端输入ENb信号,所述使能电路5的第三端输入参考电压Vref,所述使能电路5的第三端与所述比较放大电路3的第三端电连接;电流镜电路6,所述电流镜电路6的第一端与所述主运算放大器1的第六端电连接,所述电流镜电路6的第二端与所述比较放大电路3的第四端电连接,所述电流镜电路6的第三端与所述比较放大电路3的第五端电连接,所述电流镜电路6的第四端与所述使能电路5的第四端电连接,所述电流镜电路6的第五端与所述使能电路5的第五端电连接,所述电流镜电路6的第六端与所述使能电路5的第六端电连接。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,包括:所述主运算放大器1、所述比较放大电路3、所述共模电平检测电路4、所述使能电路5和所述电流镜电路6;所述主运算放大器1提取输出端OUTp和OUTn端的共模电平,将共模电平与一个参考电平比较得到共模误差电平,将共模误差电平放大或者直接反馈到Inp端和Inn端,所述主运算放大器1的输出接所述共模电平检测电路4的输入,所述共模电平检测电路4的输出端接所述比较放大电路3的输入,所述比较放大电路3的输出端通过放大反馈到所述主运算放大器1中形成反馈环路,所述使能电路5的使能端控制所述应用于复数域滤波器的高GWB高输出摆幅运放的偏置电流,该偏置电流被其它支路复制或放大。

其中,所述主运算放大器1包括:第一PMOS管7,所述第一PMOS管7的栅极端与Inp端电连接;第二PMOS管8,所述第二PMOS管8的源极端与所述第一PMOS管7的源极端电连接,所述第二PMOS管8的栅极端与Inn端电连接;第三PMOS管9,所述第三PMOS管9的漏极端与所述第一PMOS管7的源极端电连接;第一NMOS管10,所述第一NMOS管10的漏极端与所述第一PMOS管7的漏极端电连接;第二NMOS管11,所述第二NMOS管11的漏极端与所述第二PMOS管8的漏极端电连接,所述第二NMOS管11的栅极端与所述第一NMOS管10的栅极端电连接,所述第二NMOS管11的源极端与所述第一NMOS管10的源极端电连接;第三NMOS管12,所述第三NMOS管12的栅极端与所述第二NMOS管11的漏极端电连接,所述第三NMOS管12的源极端与所述第二NMOS管11的源极端电连接;第四NMOS管13,所述第四NMOS管13的栅极端与所述第一NMOS管10的漏极端电连接,所述第四NMOS管13的源极端与所述第三NMOS管12的源极端电连接;第四PMOS管14,所述第四PMOS管14的漏极端分别与所述第三NMOS管12的漏极端和OUTp端电连接;第五PMOS管15,所述第五PMOS管15的源极端与所述第四PMOS管14的源极端电连接,所述第五PMOS管15的栅极端与所述第四PMOS管14的栅极端电连接,所述第五PMOS管15的漏极端分别与所述第四NMOS管13的漏极端和OUTn端电连接。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,所述主运算放大器1包括第一级增益放大级和第二级缓冲级,第一级增益放大级由所述第一PMOS管7、所述第二PMOS管8、所述第三PMOS管9、所述第一NMOS管10和所述第二NMOS管11组成;第二级缓冲级由所述第三NMOS管12、所述第四NMOS管13、所述第四PMOS管14和所述第五PMOS管15组成,第二级缓冲级为源跟随器结构,因此具备较低的输出阻抗,具备一定的驱动能力,适用于复数域滤波器中的应用;所述主运算放大器1的输出摆幅为Vod到VDD-Vod,其中,Vod为所述第三NMOS管12、所述第四NMOS管13、所述第四PMOS管14和所述第五PMOS管15的过驱动电压,VDD为电源电压,图2中的VB1和VB2为偏置电压,VB3为参考电压。

其中,所述比较放大电路3包括:第六PMOS管16;第七PMOS管17,所述第七PMOS管17的源极端与所述第六PMOS管16的漏极端电连接,所述第七PMOS管17的栅极端与所述第三PMOS管9的栅极端电连接;第八PMOS管18,所述第八PMOS管18的源极端与所述第七PMOS管17的漏极端电连接,所述第八PMOS管18的栅极端与所述第二PMOS管8的栅极端电连接;第九PMOS管19,所述第九PMOS管19的源极端与所述第八PMOS管18的源极端电连接,所述第九PMOS管19的栅极端与所述第一PMOS管7的栅极端电连接,所述第九PMOS管19的漏极端与所述第八PMOS管18的漏极端电连接;第五NMOS管20,所述第五NMOS管20的漏极端分别与所述第九PMOS管19的漏极端和所述第一NMOS管10的栅极端电连接,所述第五NMOS管20的栅极端与所述第五NMOS管20的漏极端电连接,所述第五NMOS管20的源极端与所述第一NMOS管10的源极端电连接。

其中,所述共模电平检测电路4包括:第十PMOS管21,所述第十PMOS管21的源极端与所述第六PMOS管16的源极端电连接,所述第十PMOS管21的栅极端与所述第四PMOS管14的漏极端电连接;第十一PMOS管22,所述第十一PMOS管22的源极端分别与所述第十PMOS管21的源极端和所述第四PMOS管14的源极端电连接,所述第十一PMOS管22的栅极端与所述第五PMOS管15的漏极端电连接,所述第十一PMOS管22的漏极端分别与所述第十PMOS管21的漏极端和所述第三PMOS管9的源极端电连接。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,所述共模电平检测电路4由所述第十PMOS管21和所述第十一PMOS管22组成,通过调节工作在线性区所述第十PMOS管21、所述第十一PMOS管22和所述电阻31大小实现反馈的功能。

其中,所述使能电路5包括:第六NMOS管23,所述第六NMOS管23的栅极端输入EN信号;第十二PMOS管24,所述第十二PMOS管24的源极端与所述第六PMOS管16的栅极端电连接,所述第十二PMOS管24的栅极端输入ENb信号,所述第十二PMOS管24的漏极端输入参考电压Vref。

其中,所述电流镜电路6包括:第四PMOS管14;第五PMOS管15;第六PMOS管16;第十三PMOS管25,所述第十三PMOS管25的栅极端与所述第十三PMOS管25的漏极端电连接;第十四PMOS管27,所述第十四PMOS管27的源极端与所述第十三PMOS管25的源极端电连接,所述第十四PMOS管27的栅极端与所述第十三PMOS管25的栅极端电连接;第七NMOS管27,所述第七NMOS管27的漏极端与所述第十四PMOS管27的漏极端电连接,所述第七NMOS管27的栅极端与所述第七NMOS管27的漏极端电连接,所述第七NMOS管27的源极端与所述第六NMOS管23的源极端电连接;第八NMOS管28,所述第八NMOS管28的栅极端与所述第七NMOS管27的栅极端电连接,所述第八NMOS管28的源极端分别与所述第七NMOS管27的源极端和所述第五NMOS管20的源极端电连接;第十五PMOS管29,所述第十五PMOS管29的源极端分别与所述第十四PMOS管27的源极端和所述第六PMOS管16的源极端电连接,所述第十五PMOS管29的栅极端与所述第十二PMOS管24的源极端电连接。

其中,还包括:第十六PMOS管30第十六PMOS管30,所述第十六PMOS管30第十六PMOS管30的源极端与所述第十五PMOS管29的漏极端电连接,所述第十六PMOS管30第十六PMOS管30的栅极端与所述第十六PMOS管30第十六PMOS管30的漏极电连接,所述第十六PMOS管30第十六PMOS管30的漏极端与所述第八NMOS管28的漏极端电连接。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,所述第十六PMOS管30用于调节所述第十五PMOS管29漏极端的电压。

其中,还包括:电阻31,所述电阻31的第一端与所述第十三PMOS管25的漏极端电连接,所述电阻31的第二端与所述第六NMOS管23的漏极端电连接。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,所述电阻31用于控制和调节偏置电流的大小。

其中,还包括:当所述第十PMOS管21和所述第十一PMOS管22工作在线性区时,所述第十PMOS管21和所述第十一PMOS管22的跨导用下式计算:

gm10=gm11=μnCox(W/L)V

其中,gm10表示第十PMOS管21的跨导,gm11表示第十一PMOS管22的跨导,μn表示载流子迁移率,Cox表示单位面积的栅氧化层电容,W/L表示第十PMOS管21和第十一PMOS管22的宽长比,V

其中,还包括:主运算运算放大器的增益带宽积,用下式计算:

GBW=gm/C

其中,GBW表示增益带宽积,gm表示MOS管跨导,C

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,EN信号为所述应用于复数域滤波器的高GWB高输出摆幅运放的使能信号,ENb信号为EN信号的反向信号,当EN=0时,关闭偏置电流,当EN=1时,所述应用于复数域滤波器的高GWB高输出摆幅运放工作,所述共模电平检测电路4检测并提取出所述主运算放大器1输出端的共模电平将提取出的共模电平与参考电平进行比较放大得到误差信号,将误差信号反馈回所述主运算放大器1并调节所述主运算放大器1的共模点,整个环路形成一个负反馈环路,从而达到稳定所述主运算放大器1输出端共模电平的作用。

本发明的上述实施例所述的应用于复数域滤波器的高GWB高输出摆幅运放,输出阻抗低,输出摆幅大,功耗低,具有较大的输出摆幅,且具备一定的驱动能力,能够用于对GBW以及输出摆幅要求高的应用。

以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明所述原理的前提下,还可以作出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。