应用于多速率的高线性度的相位插值器及采用其的电路

文献发布时间:2023-06-19 09:30:39

技术领域

本发明涉及集成电路领域,特别涉及到一种用于多速率高速数据传输系统中高线性度的相位插值器电路。

背景技术

时钟数据恢复电路(CDR,clock and data recovery)是高速串行接口电路中接收器(RX,receiver)的关键部分。一般有两种结构:一种是基于锁相环(PLL,phase lockedloop)的CDR,这种结构的电路依靠压控振荡器(VCO,voltage controlled oscillator)来产生数据采样时钟;一种是基于数字锁相环(DPLL,digital phase locked loop)的CDR,依靠数字积分器(DI,digital integrator)和相位插值器(PI,phase interpolator)来代替VCO提供采样时钟。

由于一个完整的高速串行接口电路中包含锁相环、发送器(TX,transmitter)和接收器,使基于DPLL的CDR可以节省掉一个VCO所占的面积和功耗。同时,DPLL中包含的数字滤波器(DLF,digital loop filter)使这种CDR电路的抗PVT(process,voltage andtemperature)变化能力更强,电路鲁棒性更好。所以,这种CDR电路相比较基于模拟锁相环的CDR更加流行。

基于DPLL的CDR电路的性能依赖于PI的线性度,更高的PI线性度意味着更稳定的CDR负反馈环路和更好的频率容差。对于无论是传统的电流模逻辑(CML,current modelogic)PI还是传统的电压模逻辑(VML,voltage mode logic)PI,为了实现高线性度,输入的时钟信号的斜率和幅度必须控制在合理范围内,所以传统结构的PI只适用于单速率数据信号传输。

因此,亟需一种可以用于多速率的高线性度的相位插值器。

发明内容

有鉴于此,本发明的主要目的在于提供一种应用于多速率的高线性度的相位插值器,以期部分地解决上述技术问题中的至少之一。

为了实现上述目的,作为本发明的一方面,提供了一种相位插值器,包括电流可控的尾电流管、时钟边沿斜率与幅度控制单元和插值相位产生单元,其中,

电流可控的尾电流管,用于产生随锁相环时钟频率变化趋势相同的电流并提供给所述时钟的边沿斜率与幅度控制单元;

时钟边沿斜率与幅度控制单元,用于根据偏置电流值动态调整时钟信号的边沿斜率和幅度;

插值相位产生单元,输入信号来源于所述时钟边沿斜率与幅度控制单元,用于产生并输出最终的插值相位。

其中,所述相位插值器为模拟相位插值器。

其中,所述时钟边沿斜率与幅度控制单元包括两组电流模逻辑电路,所述两组电流模逻辑的偏置电流由所述电流可控的尾电流管提供。

其中,所述时钟边沿斜率与幅度控制单元的输入为相位相差90°的两对差分时钟信号。

其中,所述插值相位产生单元采用电流模逻辑的结构,两组偏置电流由数字码控制,四个输入信号由时钟边沿斜率与幅度控制单元的四个输出信号提供。

作为本发明的另一方面,还提供了一种包括如上所述的相位插值器的时钟数据恢复电路,其中,还包括锁相环,其中,所述锁相环包括环形压控振荡器,用于为相位插值器的尾电流管提供电流偏置。

其中,所述环形压控振荡器包括压控电流镜和流控振荡器,其中,所述压控电流镜的电流会随着控制电压的升高而增大,所述流控振荡器的振荡频率会随流入电流的增大而提高,从而实现压控振荡器的频率随控制电压升高而提高的功能。

基于上述技术方案可知,本发明的应用于多速率的高线性度的相位插值器相对于现有技术至少具有如下有益效果之一或其中的一部分:

本发明提供了一种应用于多速率的高线性度的相位插值器,通过将低速时钟的陡峭时钟边沿转化得平缓,同时可将高速时钟的平缓时钟边沿转化得陡峭,从而实现多速率的高线性度的相位插值功能。

附图说明

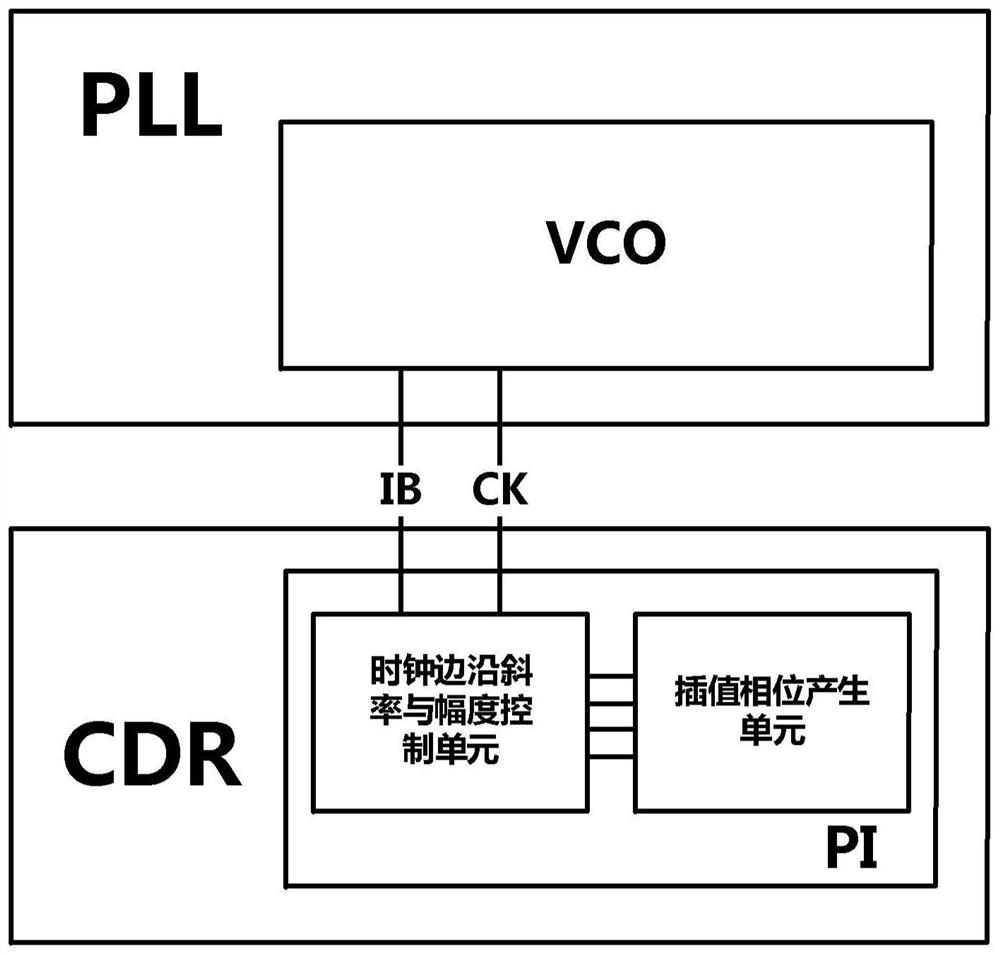

图1为本发明实施例提供的包含相位插值器的电路结构的结构框图;

图2为本发明实施例提供的电流可控的尾电流管;

图3为本发明实施例提供的时钟边沿斜率与幅度控制单元;

图4为本发明实施例提供的插值相位产生单元;

图5为本发明实施例提供的相位插值器在灌入450uA尾电流值时,分别工作在2.5GHz和5GHz时钟速率下对应的差分非线性的仿真结果对比;

图6为本发明实施例提供的相位插值器在灌入850uA尾电流值时,分别工作在2.5GHz和5GHz时钟速率下对应的差分非线性的仿真结果对比;

图7为本发明实施例提供的相位插值器分别工作在2.5GHz和5GHz时钟速率下与灌入不同尾电流的相位插值器的线性度对比。

具体实施方式

本发明公开了一种应用于多速率的高线性度相位插值器,其包括:电流可控的尾电流管、时钟的边沿斜率与幅度控制单元和插值相位产生单元。电流可控的尾电流管可产生随锁相环时钟频率变化趋势相同的电流并提供给时钟的边沿斜率与幅度控制单元。控制单元会对较低频率的差分信号产生较小的增益将低频时钟的边沿变得平缓;同时,也会对高频率的差分信号产生较高的增益将高频时钟的边沿变得陡峭。即可在宽时钟频率范围产生合适边沿斜率的信号并在插值相位产生单元中实现高线性度相位插值。

具体的,本发明公开了一种相位插值器,包括电流可控的尾电流管、时钟边沿斜率与幅度控制单元和插值相位产生单元,其中,

电流可控的尾电流管,用于产生随锁相环时钟频率变化趋势相同的电流并提供给所述时钟的边沿斜率与幅度控制单元;

时钟边沿斜率与幅度控制单元,用于根据偏置电流值动态调整时钟信号的边沿斜率和幅度;

插值相位产生单元,输入信号来源于所述时钟边沿斜率与幅度控制单元,用于产生并输出最终的插值相位。

其中,所述相位插值器为模拟相位插值器。所述时钟边沿斜率与幅度控制单元包括两组电流模逻辑电路,所述两组电流模逻辑的偏置电流由所述电流可控的尾电流管提供。所述时钟边沿斜率与幅度控制单元的输入为相位相差90°的两对差分时钟信号。所述插值相位产生单元采用电流模逻辑的结构,两组偏置电流由数字码控制,四个输入信号由时钟边沿斜率与幅度控制单元的四个输出信号提供。

本发明还公开了一种包括如上所述的相位插值器的时钟数据恢复电路,其中,还包括锁相环,其中,所述锁相环包括环形压控振荡器,用于为相位插值器的尾电流管提供电流偏置。

其中,所述环形压控振荡器包括压控电流镜和流控振荡器,所述压控电流镜的电流会随着控制电压的升高而增大,所述流控振荡器的振荡频率会随流入电流的增大而提高,从而实现压控振荡器的频率随控制电压升高而提高的功能。

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明作进一步的详细说明。

如图1所示,是本发明的结构框图。相位插值器的尾电流由锁相环中环形VCO偏置出的电流提供。

如图2所示,是锁相环中环形VCO的基本结构图。pMOS晶体管1、2、3的栅电压都由pMOS晶体管5偏置产生,所以1、2、3同时受控于VCTRL电压,并且这三个晶体管电流变化相同。对于环形VCO,CCO输出频率受控于pMOS晶体管3的输出电流,更大晶体管电流意味着更的输出频率。所以,pMOS晶体管1、2产生了与VCO输出频率变化趋势相同的电流。

如图3所示,是时钟边沿斜率与幅度控制单元,由两组CML结构的电路组成。尾电流由图1中pMOS晶体管1、2提供。四组输入时钟信号CK0、CK180、CK90、CK270由图1中环形VCO产生,CK0和CK180构成一组差分信号输入一个CML电路,同时,CK90和CK270构成另一组差分信号输入另一个CML电路,这两组差分信号的相位差为900。此单元将两组差分时钟信号进行斜率和幅度调整并输出四组信号C0、C180、C90、C270。如上所述,pMOS晶体管1、2产生了与VCO输出频率变化趋势相同的电流,所以CML电路的增益会根据输入时钟频率的不同发生相应的变化。

如图4所示,是插值相位产生单元,该电路同样采用CML结构。尾电流受控于数字码,两路尾电流ID1与ID2之和为定值,如公式(1)所示:

ID=ID1+ID2 (1)

电流ID1和ID2相对的比例即为输入的两组差分信号C0、C180与C90、C270所占权重。数字控制码越小,ID1越大,输出的差分信号VOUTP、VOUTN的相位更接近差分信号CK0、CK180的相位;数字控制码越大,ID2越大,输出的差分信号VOUTP、VOUTN的相位更接近差分信号CK90、CK270的相位。

如上描述了本发明的相位插值器的基本工作原理。下面继续针对本发明中多速率高线性度的特点进行进一步说明。

对于较低速率时钟,其时钟周期较长,其时钟边沿相对较陡峭;而对于较高速率时钟,其时钟周期较短,时钟边沿相对较平缓。由于本发明中图2所示的pMOS晶体管1、2产生的电流与时钟频率变化趋势相同。那么图3中的控制单元会对较低频率的差分信号产生较小的增益将低频时钟的边沿变得平缓;同时,也会对高频率的差分信号产生较高的增益将高频时钟的边沿变得陡峭。即无论是低频时钟还是高频时钟,在将时钟信号送入图4的插值相位产生单元之前,都能先在图3的时钟的斜率、幅度控制单元产生合适边沿斜率的信号,从而使得本发明提出的相位插值器可以在较宽时钟速率范围内实现高线性度。

也就是说本发明的关键在于,为了在不同时钟频率下实现相位插值器的高线性度,pMOS晶体管1、2产生的尾电流值需要随时钟频率进行调整。经过上述说明可以确定,相位插值器为了实现更好的线性度,较低频率需要较小的尾电流值,较高的频率需要较大的尾电流值。

为了证明以上说明,对电路进行仿真,观察灌入相同尾电流的情况下不同速率时钟表现的线性度。如图5所示是灌入450uA的尾电流时相位插值器分别工作在2.5GHz和5GHz时钟频率下,对应的差分非线性(DNL,differential non-linearity)的仿真结果对比。如图6所示是灌入850uA的尾电流时相位插值器分别工作在2.5GHz和5GHz时钟频率下,对应的差分非线性的仿真结果对比。可以发现,尾电流值为450uA时,电路工作在2.5GHz时钟频率下可以实现比5GHz更好的线性度;尾电流值为850uA时,电路工作在5GHz时钟频率下可以实现比2.5GHz更好的线性度。即图5和图6的仿真结果表明,为了实现不同时钟频率下的高线性度,相位插值器的尾电流需要随时钟频率进行调整,并且较低频率需要较小的尾电流值,较高的频率需要较大的尾电流值。

如图7所示是本发明分别工作在2.5GHz和5GHz时钟速率下与灌入不同尾电流的相位插值器的线性度对比。本次对比的是不同电路的DNL的标准差,标准差更小表示更好的线性度。可以发现,相位插值器电路工作在2.5GHz时,当灌入450uA尾电流时,电路表现出最好的线性度;相位插值器电路工作在5GHz时,当灌入850uA尾电流时,电路表现出最好的线性度。同时,本公开在2.5GHz和5GHz的时钟速率下都表现出接近对应速率最好的线性度,即本公开实现了多速率的高线性度。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。