用于管理锁相环的启动的方法及对应的集成电路

文献发布时间:2023-06-19 09:32:16

本申请要求于2019年07月09日提交的法国申请号1907661的优先权,其内容在法律允许的最大范围内通过引用以其整体并入于此。

技术领域

实施方式和实施例涉及集成电路,并且具体地涉及本领域技术人员通常已知的锁相环,并且更具体地涉及管理锁相环的启动。

背景技术

锁相环通常被用在例如可编程核或微处理器的数字系统中,其要求例如大约几百兆赫兹的高内部操作频率。

因此,锁相环的作用具体地是将具有高操作频率的内部时钟信号递送到这些数字系统。

然而,由于用于稳定锁相环所需的反馈环路和电容性网络的存在,因此启动时间(即为了使环路稳定所需的持续时间(即,其中基准信号和振荡器的输出信号接近相互同步))可能非常长,通常大于100μs。

此外,在该启动阶段期间,环路的振荡器的输出信号相对于其最终标称值存在频率过冲。该频率过冲也可能达到最终标称值的25%。

在启动时的这种频率过冲意味着PLL的数字电路必须被设计成能够承受这种较高的频率。因此,必须提高该电路的速度,从而特别地引起泄漏电流和/或动态消耗的增加。

因此,需要限制锁相环的启动时间以及该频率过冲的幅度。

发明内容

根据一个方面,提出了一种用于管理锁相环的操作的方法。

锁相环的操作包括启动阶段或步骤,涉及:将具有50%的占空比的基准信号递送到环路的相位比较器;在基准信号的第一类型的每个信号沿处(例如在每个上升信号沿处),将环路的电压控制振荡器的输出信号的第一分频器复位;以及经由接收基准信号和来自第一分频器的反馈信号的相位比较器递送控制脉冲,在该控制脉冲期间,振荡器的控制电压在基准信号的第二类型的每个信号沿处(例如在每个下降信号沿处)增加。

结合这些特征,特别是提供具有50%的占空比的基准信号,以及在基准信号的(例如)每个上升信号沿处将环路的分频器复位,允许环路的启动时间和频率过冲的显著减少。

因此,以指示的方式,对于基准信号的等于2MHz、4MHz、8MHz或16MHz的频率,以及振荡器的输出信号的等于832MHz的标称频率,与针对常规的锁相环的70微秒到100微秒以上的启动时间相比,实现了大约三十微秒左右的启动时间。

类似地,与针对常规的锁相环的高达25%的频率过冲相比,在振荡器的输出信号上实现了大约百分之几(例如,大约2%)的频率过冲。

在存在不具有50%的占空比的初始基准信号的情况下,则基准信号的递送有利地包括将该初始基准信号二分频,以便获得具有50%的占空比的基准信号,并且在该情况下,反馈信号不是直接来自环路的第一分频器的输出信号,而是经二分频的第一分频器的输出信号。

这使得可以使用任何初始基准信号,而不管其占空比如何。

尽管可以将由相位比较器递送的控制脉冲用在电荷泵电路中,但在启动阶段期间将该电荷泵电路“短路”,以直接向连接到振荡器的输入的电阻性电容性滤波器施加预充电电流特别有利。

换句话说,根据这种实施方式,在启动阶段期间,增加振荡器的控制电压包括向连接到振荡器的输入的电阻性电容性滤波器施加预充电电流。

这进一步有助于减少环路的启动时间,并且使该启动时间更少地依赖于电荷泵的电流约束,该约束与环路的稳定性链接。

根据一种实施方式,电阻性电容性滤波器包括:第一支路,连接在振荡器的上述输入与接地之间,并且包含与具有第一电容的第一电容器串联连接的电阻性网络,上述电阻性网络包含:第一电阻器,连接在振荡器的上述输入与中间节点之间,并且具有第一电阻;以及第二电阻器,连接在中间节点与第一电容器之间,并且具有第二电阻;以及第二支路,连接在振荡器的上述输入与地之间并且包含具有第二电容的第二电容器。

那么第一电容有利地等于第二电容的A倍,而第一电阻等于第二电阻的A倍。

然后将预充电电流有利地施加到上述中间节点。

实现了跨两个电容器的端子的两个电容性电压的均匀增加,并因此实现了在振荡器输入处递送的电容性电压的稳定增加。

根据一种实施方式,当控制脉冲的持续时间小于振荡器的输出信号的周期与第一分频器的分频比的乘积的百分之几(例如2%)时,启动阶段结束。

根据一种实施方式,当启动阶段结束时,相位比较器的输出连接到电荷泵电路,电荷泵电路的输出连接到电压控制振荡器的输入。

换句话说,在启动阶段期间,当电荷泵电路已经被断开连接,并且预充电电流已经被施加到电阻性电容性滤波器时,此时电荷泵电路将在启动阶段结束时重新连接到相位比较器。

当然,如果在启动阶段期间使电荷泵电路与相位比较器保持连接,则在启动阶段结束时不修改该连接。

根据一种实施方式,在启动阶段期间,当初始基准信号和第一分频器的输出信号已经被二分频时,在启动阶段结束时不继续这些二分频。

换句话说,当启动阶段已经结束时,初始基准信号被递送到相位比较器,而递送到相位比较器的反馈信号是第一分频器的输出信号。

此外,当启动阶段已经结束时,有利地可以在启动阶段的结束之后在基准信号的第一类型的第一信号沿(例如,第一上升信号沿)上执行第一分频器的最后复位。

这使得可以将基准信号和来自第一分频器的反馈信号同步。

根据另一方面,提出了一种集成电路,其包括锁相环,该锁相环包括:相位比较器;电压控制振荡器;第一分频器,连接在振荡器的输出与相位比较器的第一输入之间;递送电路,被配置以便在环路的启动阶段中,在相位比较器的第二输入上递送具有50%的占空比的基准信号;复位电路,被配置以便在上述启动阶段中,在基准信号的第一类型的每个信号沿处复位第一分频器,相位比较器被配置以便在上述启动阶段中,在基准信号的第二类型的每个信号沿处递送控制脉冲;以及控制电路被配置以便在上述控制脉冲期间,增加振荡器的控制电压。

根据一个实施例,递送电路包括:用于接收初始基准信号的输入;连接到上述输入的二分频分频器;以及输出,被配置以便递送被二分频的初始基准信号作为基准信号,并且其中集成电路还包括另一二分频分频器,该另一二分频分频器连接在第一分频器的输出和相位比较器的第一输入之间。

根据一个实施例,控制电路包含电流源,该电流源能够在上述脉冲时被激活,并且被配置以便在被激活之后,向连接在振荡器的输入处的电阻性电容性滤波器施加预充电电流。

根据一个实施例,电阻性电容性滤波器包括:第一支路,连接在振荡器的上述输入与接地之间,并且包含与具有第一电容的第一电容器串联连接的电阻性网络,上述电阻性网络包含:第一电阻器,连接在振荡器的上述输入与中间节点之间,并且具有第一电阻;以及第二电阻器,连接在中间节点与第一电容器之间,并且具有第二电阻;以及第二支路,连接在振荡器的上述输入与地之间并且包含具有第二电容的第二电容器,其中第一电容等于第二电容的A倍,并且第一电阻等于第二电阻的A倍,并且其中电流源连接到上述中间节点。

根据一个实施例,集成电路还包括检测电路,该检测电路被配置以便检测启动阶段的结束。

根据一个实施例,检测电路被配置以便检测控制脉冲的持续时间和/或由相位比较器递送的脉冲信号的类型。

因此,检测电路可以被配置以便当控制脉冲的持续时间小于振荡器的输出信号的周期与第一分频器的分频比的乘积的百分之几时,递送表示启动阶段的结束的信号。

作为变型,检测电路可以被配置以便当检测到由相位比较器递送的、请求降低电压控制振荡器的控制电压的脉冲信号的第一脉冲时,递送表示启动阶段的结束的信号。

根据一个实施例,集成电路被配置以便当启动阶段结束时,将相位比较器的输出连接到电荷泵电路,该电荷泵电路具有连接到电压控制振荡器的输入的输出。

根据一个实施例,当启动阶段已经结束时,递送电路被配置为将初始基准信号递送到相位比较器,并且集成电路包含控制电路,该控制电路被配置以便解除激活上述另一二分频分频器,使得被递送到相位比较器的反馈信号是第一分频器的输出信号。

根据一个实施例,复位电路被配置以便当启动阶段已经结束时,在启动阶段的结束之后,在基准信号的第一类型的第一信号沿上执行第一分频器的最后复位。

附图说明

通过检查对本发明的完全非限制性实施例和实施方式以及附图的详细描述,本发明的其他优点和特征将变得明显,其中:

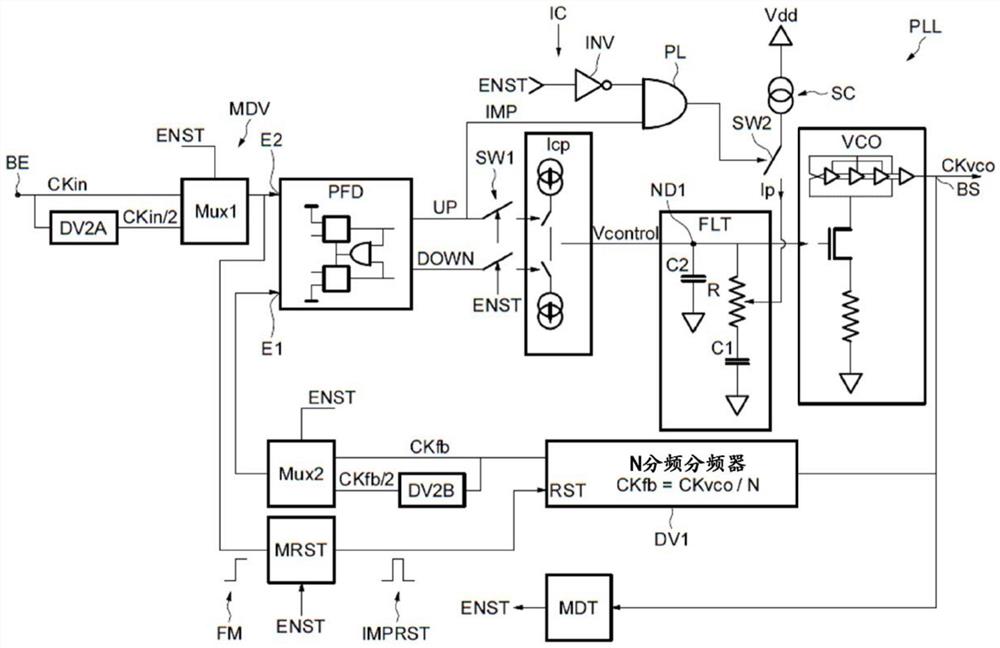

图1示出了锁相环电路的图;

图2是滤波器电路的图;以及

图3是图示用于管理环路PLL的操作的方法的实施方式的定时图。

具体实施方式

在图1中,附图标记PLL表示锁相环电路,其包括用于接收初始基准信号CKin的输入端子BE,并且包括用于递送由电压控制振荡器VCO生成的输出信号CK

作为示例,初始基准信号CKin的频率可以等于16MHz,而输出信号CK

此外,锁相环PLL的输出端子BS连接到第一分频器DV1(例如,分数分频器)的输入,第一分频器DV1被配置为对由本地振荡器VCO递送的信号CK

分频比N等于信号CK

作为示例,在该情况下,该分频比等于800/16,即52。该N分频分频器具有本身已知的常规结构,并且通常由计数器形成,该计数器能够通过在其复位输入RST上接收复位信号或脉冲IMPRST来复位。

第一分频器的输出信号以CKfb为基准。

锁相环PLL涉及启动阶段或步骤,在启动阶段或步骤的结束时,在环路的相位比较器PFD(具有常规且已知的结构)的输入处递送的基准信号与信号CKfb几乎同步。当然,当基准信号和信号CKfb几乎同步时,基准信号和输出信号CK

在该示例中,当逻辑信号ENST具有例如逻辑值“1”时,该启动阶段的结束在此出现。

现在假设,在该示例中,初始基准信号CKin具有任何占空比,特别是除了50%以外的占空比。

为此,环路PLL包括递送电路MDV,递送电路MDV被配置为在相位比较器PFD的第二输入E2上递送基准信号CKin/2,基准信号CKin/2是初始基准信号CKin的二分频。

为此,在该情况下,递送电路包含例如二分频分频器DV2A(其实际上是计数器),该二分频分频器DV2A连接到输入端子BE并且递送基准信号CKin/2。

此外,递送电路MDV包含第一复用器Mux1,第一复用器Mux1由信号ENST控制,并且在一方面第一复用器Mux1接收基准信号CKin/2和初始基准信号CKin。

在启动阶段期间(即,当逻辑信号ENST具有逻辑值“0”时),复用器Mux1在输入E2上递送经二分频的初始基准信号,这从而形成在相位比较器PFD的第二输入E2上接收的基准信号。

在相位比较器PFD的第一输入E1上递送的反馈信号来自第二复用器Mux2,该第二复用器Mux2也由信号ENST控制。

第一分频器CKfb的输出信号被递送到第二复用器Mux2的第一输入。

第二复用器Mux2的第二输入接收信号CKfb/2,信号CKfb/2由另一二分频分频器DV2B递送,并且因此由信号CKfb的二分频得到。

因此,在该示例中,在环路PLL的启动阶段期间,由于相位比较器的输入E2接收基准信号CKin/2,因此在相位比较器的第一输入E1上递送的反馈信号是信号CKfb/2。

如常规的,相位比较器PFD,取决于在其两个输入处存在的信号,递送控制脉冲UP或控制脉冲DOWN,控制脉冲UP被配置为增加在振荡器VCO的输入处的控制电压或命令电压,控制脉冲DOWN被配置为减少该控制电压。

此外,环路PLL包含电阻性电容性滤波器FLT,其具有连接到电压控制振荡器VCO的命令或控制输入的节点ND1。

此外,锁相环PLL包含具有常规且本身已知的结构的电荷泵电路CHP,电荷泵电路CHP被配置为接收两个控制脉冲UP和DOWN,并且向电阻性电容性滤波器FLT递送电流,从而产生能够被施加到振荡器的输入的控制电压Vcontrol。

就是说,在该实施例中,相位比较器PFD通过一组第一开关SW1连接到电荷泵电路CHP的输入,该组第一开关SW1能够由逻辑信号ENST命令。

在另一实施例中,该组第一开关SW1可以由逻辑门代替,该逻辑门的一个输入连接到逻辑信号ENST,该逻辑信号ENST使得可以断开电荷泵电路CHP内部的开关。

因此,在该实施例中,当锁相环处于其启动阶段(例如,ENST=0)时,开关SW1断开,从而将电荷泵电路CHP与相位比较器PFD的输出断开连接。

如图2中所图示的,在该情况下,滤波器FLT包含连接在节点ND1和接地GND之间的第一支路BR1,并且包含也连接在节点ND1和接地GND之间的第二支路BR2。

第一支路包括与第一电容器C1串联连接的电阻性网络R。

电阻性网络R包含连接在节点ND1和中间节点ND2之间的第一电阻器R1,并且包含连接在中间节点ND2和第一电容器C1之间的第二电阻器R2。

为了简化起见,C1、C2、R1和R2也将分别表示第一电容器C1的电容、第二电容器C2的电容、第一电阻器R1的电阻和第二电阻器R2的电阻。

在该示例中,第一电容器C1的电容C1等于第二电容器C2的电容C2的常数A倍的值。作为指示,A的值大约为10。

第一电阻器R1的电阻R1就其部分而言等于第二电阻器R2的电阻R2的A倍的值。

因此,乘积R2C1等于乘积R1C2,即等于乘积R2C2的A倍。

另外,在启动阶段期间,预充电电流Ip将被施加到中间节点ND2。

另外,由于C1等于aC2,将花费相同的时间对C1和C2进行预充电,因此该时间等于滤波器的常数除以A。

如图1中所图示的,该预充电电流Ip来自电流源SC,该电流源SC能够通过第二开关SW2来激活,该第二开关SW2由逻辑AND门(附图标记PL)的输出命令。

该门PL在第一输入上接收信号UP的控制脉冲IMP,并且在第二输入上接收由反相器INV反相的信号ENST。

在启动阶段期间,信号ENST处于“0”,并且在启动阶段之后处于“1”。

因此,在启动阶段期间,第二开关SW2由信号UP的脉冲命令,而在启动阶段之后,第二开关SW2总是断开。

更精确地,在启动阶段期间,如果信号UP处于高水平(代表脉冲IMP),则开关SW2闭合,并且电流源在中间节点ND2上递送预充电电流Ip。

并且只要信号UP处于1,这种情况就持续,即,只要存在控制脉冲IMP,这种情况就持续。

相反,一旦脉冲IMP消失(信号UP处于零),则开关SW2断开并且没有预充电电流被递送到节点ND2。

因此,电容性滤波器FLT在脉冲IMP期间充电,并且这些充电操作使得可以增加在振荡器VCO的输入处的控制电压,从而使得可以增加该振荡器的输出信号的频率。

因此,电流源SC和滤波器FLT形成控制电路的一部分,该控制电路被配置以便在上述控制脉冲IMP期间增加振荡器的控制电压。

如上所述,通过将复位脉冲IMPRST施加到分频器的复位输入RST,来复位第一分频器DV1。

在启动阶段中,响应于基准信号(在这种情况下为信号CKin/2)的每个上升信号沿FM,通过复位电路MRST来获得该复位脉冲IMPRST。

当然,可以在信号CKin/2的每个下降信号沿上执行该复位。

此外,如将在下面更详细地看到的,一旦启动阶段已经结束,复位电路MRST就将在基准信号的第一上升信号沿上递送最后的复位脉冲,此时,该基准信号将是启动阶段的结束之后的信号CKin。

可以通过逻辑电路容易地产生复位电路MRST。

此外,并入了锁相环PLL的集成电路IC还包含检测电路MDT,检测电路MDT被配置以便检测启动阶段的结束,并且因此将逻辑值1递送到信号ENST。

当与“up”信号的高状态相对应的控制脉冲IMP的持续时间T小于振荡器VCO的输出信号的标称周期T

作为示例,该阈值可以被取为等于2%。

因此,根据第一种可能性,为了检测该启动阶段结束条件,检测电路MDT可以被配置以便在脉冲IMP的持续时间期间,对信号CK

根据另一可能的实施例,检测电路MDT可以包含接收信号UP的低通滤波器,该低通滤波器的时间常数与所述百分之几的阈值链接。

根据该滤波器的输出是否递送高信号,检测电路MDT将递送逻辑值“0”或逻辑值“1”的信号ENST。

作为变型,当检测到与信号“DOWN”的高状态相对应的第一控制脉冲时,也可以认为达到启动阶段的结束。现在更具体地参考图3,以便说明用于管理之前图中图示的环路PLL的操作的方法的一种实施方式。

该图3具有定时图的形式。

图3的第一行示出了初始基准信号CKin,如所见的,其具有50%以外的占空比。

第二行示出了基准信号CKin/2,基准信号CKin/2由初始基准信号的二分频产生,并且此时其具有等于50%的占空比。

如上所述,该信号CKin/2是在相位比较器PFD的第二输入E2上递送的基准信号。

此外,可以看出,在基准信号CKin/2的每个上升信号沿处,由复位电路MRST发射复位脉冲IMPRST,复位脉冲IMPRST将第一分频器DV1复位,即将形成该第一分频器的计数器复位到0。

此外,在基准信号CKin/2的每个下降信号沿上,相位比较器PFD将基准信号CKin/2的相位与反馈信号CKFB/2的相位进行比较,并且从而递送信号UP的控制脉冲IMP。

当存在脉冲IMP时,该脉冲IMP使得可以将预充电电流Ip施加到滤波器FLT的中间节点ND2。

随着该启动阶段的进行,可以注意到,由于信号CK

另外,如上所述,当脉冲IMP的持续时间T小于或等于分频比N与振荡器信号的周期TCK

此时,第一复用器Mux1在相位比较器的第二输入E2上递送初始基准信号CKin,初始基准信号CKin变为基准信号。

此外,在相位比较器PFD的第一输入E1上递送的反馈信号变为直接来自分频器的信号CKfb(即,事先没有被二分频)。

同时,开关SW1闭合,将相位比较器PFD的两个输出(分别递送两个信号UP和DOWN)连接到电荷泵电路的输入,以便恢复锁相环的常规操作。

开关SW2断开,将预充电电流Ip的施加中断。

此时,用于调节本地振荡器VCO的控制电压Vcontrol的电流是由电荷泵电路递送的电流Icp。

就是说,为了加速信号CK

然后,锁相环在几个循环之后将准备好递送其输出信号。

该输出信号可以例如作为用于微处理器的时钟信号。