半导体集成电路装置及电平位移电路

文献发布时间:2023-06-19 09:35:27

技术领域

本公开涉及一种半导体集成电路装置,其输出与输入信号相应的输出信号。

背景技术

就半导体集成电路装置而言,在与外部进行信号输入输出的接口电路中,需要做到高速工作和低功耗这两点。为了同时实现高速工作和低功耗,输入输出(IO)晶体管采用以例如1.8[V]的低电压工作的晶体管。另一方面,接口电路必须构成为可供例如3.3[V]的高电压信号输入输出。

专利文献1公开了一种技术,用以低电压工作的晶体管构成向外部输出高电压信号的输出电路。在该技术中,通过将低电压晶体管级联到高电压电源与输出焊盘之间,来缓和低电压晶体管的源极漏极之间的电压。驱动输出信号的P型晶体管的源极与高电压电源相连,漏极经由另一晶体管与输出焊盘相连,在高电压与低电压之间发生位移的信号施加到栅极上。此外,使另一晶体管的栅极与电压比高电压电源低的电压源(以下称为低电压电源)相连,并使施加于各晶体管的电压不超过耐压。然而,在专利文献1的电路中存在以下问题:当高电压电源和低电压电源上升时,如果高电压电源侧先上升,则超过晶体管的耐压,晶体管可能会遭到破坏。

在专利文献2中,在信号电压电平转换电路中,即使高电压电源先上升且低电压电源未上升,也通过从高电压电源将降压后的电压供往低电压电源侧来防止超过耐压。

专利文献1:日本公开专利公报特开2007-60201号公报

专利文献2:日本公开专利公报特开平6-152383号公报

发明内容

-发明要解决的技术问题-

然而,在专利文献1的结构中,存在以下问题:在高电压电源先上升且低电压电源未上升的情况下,不必要的电流从高电压电源经由低电压电源及连接于其后的电路流向接地(ground)。

本公开的目的在于:提供一种电路,即使高电压电源比低电压电源先上升,也不会超过耐压,且不会有上述不必要的电流流动。

-用以解决技术问题的技术方案-

第一方面的公开是一种半导体集成电路装置,接收数据输入信号,输出根据所述数据输入信号变化的输出信号,该半导体集成电路装置包括输出端子、P型的第一晶体管、P型的第二晶体管、降压电路、电源开关电路以及第一电平位移电路(level shiftcircuit),所述输出端子输出所述输出信号,所述第一晶体管的源极与第一电源相连,所述第二晶体管的源极与所述第一晶体管的漏极相连,且该第二晶体管的漏极与所述输出端子相连,所述降压电路从所述第一电源生成第二电源,所述电源开关电路包括与所述第二电源相连的第三晶体管和与第三电源相连的第四晶体管,且将所述第二电源和所述第三电源中的高电位作为第四电源输出,所述第一电平位移电路在所述第一电源与所述第四电源之间发生位移,所述第一晶体管的栅极与所述第一电平位移电路的输出相连,所述第二晶体管的栅极与所述第四电源相连。

根据该方面,将从第一电源生成的第二电源和第三电源中的高电位作为第四电源输出。并且,源极与第一电源相连的第一晶体管的栅极与在第一电源与第四电源之间发生位移的第一电平位移电路的输出相连,源极与第一晶体管的漏极相连的第二晶体管的栅极与第四电源相连。这样一来,能够提供一种半导体集成电路,不管第一电源和第三电源的上升顺序如何,都不会超过耐压。

-发明的效果-

根据本公开,能够提供一种半导体集成电路装置,即使高电压电源比低电压电源先上升,也不会超过耐压,且不会有不必要的电流流动。

附图说明

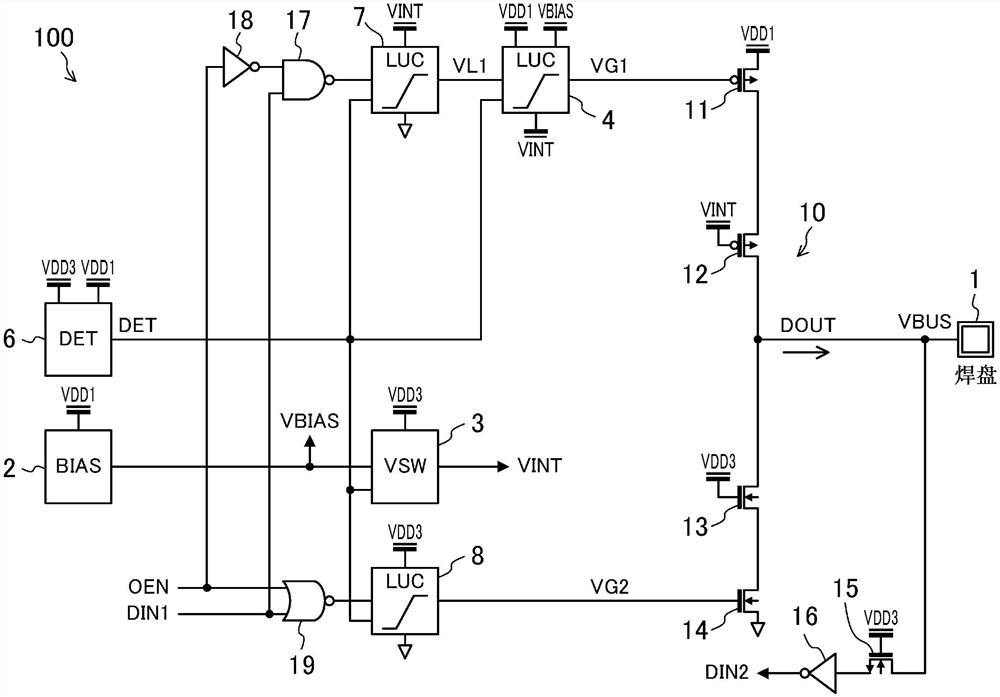

图1是第一实施方式所涉及的半导体集成电路装置的电路结构图;

图2是电源检测电路的电路结构图;

图3A是偏压生成电路的电路结构图;

图3B是偏压生成电路的另一例的电路结构图;

图3C是电平位移电路装置的电路结构图;

图4A是电源开关电路的电路结构图;

图4B是电源开关电路的另一例的电路结构图;

图4C是电源开关电路的另一例的电路结构图;

图5是电平位移电路的电路结构图;

图6是电平位移电路的电路结构图;

图7A是电平位移电路装置的电路结构图;

图7B是电平位移电路装置的另一例的电路结构图;

图8是第一实施方式所涉及的半导体集成电路装置的另一例的电路结构图;

图9是第二实施方式所涉及的半导体集成电路装置的电路结构图。

具体实施方式

下面参照附图对实施方式进行说明。需要说明的是,在以下所示的电路结构图中,以本公开所涉及的构成要素为中心进行简化图示。因此,例如,图示中直接连接的构成要素在实际的电路结构中,有时会在二者间布置有其他构成要素,二者间接相连。此外,以下说明的各晶体管是金氧半场效晶体管(Metal Oxide Semiconductor Field EffectTransistor,MOSFET)。

<第一实施方式>

图1是第一实施方式所涉及的半导体集成电路装置的电路结构图。图1的半导体集成电路装置100接收数据输入信号DIN1,输出根据该数据输入信号DIN1变化的输出信号DOUT。输出信号DOUT从输出端子1输出。该半导体集成电路装置100例如设在LSI的信号的输入输出部。例如,LSI的输入输出焊盘和输出焊盘相当于输出端子1。

半导体集成电路装置100与第一电源VDD1和第三电源VDD3相连。需要说明的是,在本申请说明书中,将“VDD1”“VDD3”用作表示电源本身和该电源所施加的电位这二者的符号。关于后面要说明的“VDD2”“VDD4”“GND”也相同,用作表示电源本身和该电源所施加的电位这二者的符号。

半导体集成电路装置100正常工作时的第一电位VDD1与第三电位VDD3互不相同。在下述说明中,为了方便说明,设第三电位比第一电位VDD1低。第一电位VDD1例如是3.3[V],第三电位VDD3例如是1.8[V]。此处,在本实施方式中,将从各电源施加有规定的稳态电位的状态称为正常工作时。

数据输入信号DIN1是低振幅信号,例如在接地电位GND~0.9[V]之间发生位移。输出信号DOUT在接地电位GND与第一电位VDD1之间发生位移。

如图1所示,半导体集成电路装置100包括串联连接在第一电源VDD1与输出端子1之间的P型晶体管11、12、作为降压电路的偏压生成电路2、电源开关电路3以及电平位移电路装置4。P型晶体管11的栅极与电平位移电路装置4的输出VG1相连,P型晶体管12的栅极与第四电源VINT相连。P型晶体管11相当于第一晶体管,P型晶体管12相当于第二晶体管。P型晶体管11、12的耐压是第三电位VDD3。

偏压生成电路2将第一电源VDD1降压而生成第二电源VBIAS。在下述说明中,为了方便说明,设半导体集成电路装置100正常工作时的第二电位VBIAS比第一电位VDD1和第三电位VDD3低。第二电位VBIAS例如是1.65[V]。

电源开关电路3将由偏压生成电路2生成的第二电源VBIAS的电位和第三电源VDD3的电位中的高电位作为第四电源VINT输出。

在输出端子1与接地GND之间,串联连接有N型晶体管13、14。N型晶体管13、14的耐压是第三电位VDD3。N型晶体管13相当于第五晶体管。

即,在第一电源VDD1与接地GND之间,P型晶体管11、12和N型晶体管13、14按照记载顺序串联连接而构成输出部10,连接P型晶体管12的漏极与N型晶体管13的漏极之间的布线(node)与输出端子1相连。N型晶体管13的栅极与第三电源VDD3相连,N型晶体管14的栅极与后述电平位移电路8相连。

也可以让输出端子1作为输入输出端子发挥作用。例如,在图1中,输出端子1经由N型晶体管15与反相器16相连,N型晶体管15的栅极与第三电源VDD3相连,输出端子1具有将数据输入信号DIN2向半导体集成电路装置100的内部传输的输入端子的功能。

例如,半导体集成电路装置100在输出使能信号OEN为低电平时,从输出端子1输出根据数据输入信号DIN1变化的输出信号DOUT,在输出使能信号OEN为高电平时,变为能够从外部装置(省略图示)接收信号至输出端子1的状态。

如图1所示,输出使能信号OEN经由反相器18输入NAND电路17的一输入端子。数据输入信号DIN1施加于NAND电路17的另一输入端子。并且,NAND电路17的输出布线与电平位移电路7相连。

电平位移电路7将在接地电位GND与核心电源的电压电平(例如,0.9[V])之间发生位移的输入信号IN转换为在接地电位GND与第四电位VINT之间发生位移的输出信号OUT,并输出到电平位移电路装置4。

电平位移电路装置4接收后述电源检测电路6的输出DET和后述电平位移电路7的输出VL1,将在第四电位VINT与第一电位VDD1之间发生位移的信号VG1输出到P型晶体管11的栅极。

此外,输出使能信号OEN和数据输入信号DIN1经由NOR电路19输入电平位移电路8。

电平位移电路8将在接地电位GND与核心电源的电压电平(例如,0.9[V])之间发生位移的输入信号IN转换为在接地电位GND与第三电位VDD3之间发生位移的输出信号OUT,并输出到N型晶体管14的栅极。

正如上述背景技术中所述,如果要在专利文献1的结构中保证耐压,则存在不能先让高电压电源侧上升的制约。其原因在于,如果高电压电源先上升,则超过耐压的电压可能会施加于输出级晶体管。另一方面,在本公开所涉及的半导体集成电路装置100中,在高电压电源先上升的情况下,也不会超过耐压。

下面参照附图进行具体说明。需要说明的是,在下述说明中,对第一电源VDD1先上升时的电路的工作情况进行说明,有时会省略第三电源VDD3先上升时的说明。其原因在于,本公开所涉及的半导体集成电路装置100在第三电源VDD3先上升的情况下,也不会超过耐压而正常工作,在现有技术中,也同样不会超过耐压。

如图2所示,电源检测电路6是在检测到第一电源VDD1和第三电源VDD3达到规定的稳态电位这一情况时输出高电平信号的电路。具体而言,电源检测电路6包括生成第一电源VDD1的中间电位的电阻分压电路41和与电阻分压电路41的后级相连且接收第三电源VDD3的供给的缓冲器42。所述中间电位设为下述电位,其在第一电位VDD1施加于第一电源VDD1且第三电位VDD3施加于第三电源VDD3时,保证缓冲器42的输出DET为高电平。即,电源检测电路6在正常工作时,输出DET为高电平。另一方面,在电源的接通时序(以下称为上电时序)时,如果第三电源VDD3未上升,则即使第一电源VDD1上升,输出DET也为低电平。需要说明的是,因为缓冲器42能够应用现有技术的结构,所以此处省略其详细说明。

图3A、图3B是偏压生成电路2的结构例。

图3A是推挽型偏压电路,由前级电路和后级电路两级结构。在图3A的偏压生成电路2A中,前级电路是在第一电源VDD1与接地GND之间,由电阻元件21、N型晶体管22、P型晶体管23以及电阻元件24按照记载顺序串联连接而成的。后级电路是在第一电源VDD1与接地GND之间,由N型晶体管25和P型晶体管26串联连接而成的。在前级电路中,N型晶体管22的栅极与漏极相连,其连接布线N21与后级电路的N型晶体管25的栅极相连。同样,在前级电路中,P型晶体管23的栅极与漏极相连,其连接布线N22与后级电路的P型晶体管26的栅极相连。

例如,在图3A的偏压生成电路2中,(1)使前级电路的两个电阻元件21、24彼此的电阻值相等,(2)使前级电路的N型晶体管22和P型晶体管23的驱动能力(通态电阻)一致,(3)使后级电路的N型晶体管25和P型晶体管26的驱动能力(通态电阻)一致,由此能够输出大概为第一电位VDD1的一半的电压。

图3B的偏压生成电路2B在图3A的偏压生成电路2A的基础上,在偏压生成电路2A的输出布线N23处设有用于向第一电源VDD1上拉的P型晶体管27。P型晶体管27的栅极与电平位移电路装置5相连。电平位移电路装置5的输入XIN与接地GND相连。

电平位移电路装置5是下述电路:在上电时序时,将低电平信号作为输出信号XOUT输出,在正常工作时,将高电平信号作为输出信号XOUT输出。即,在偏压生成电路2B中,在上电时序时,从第一电源VDD1经由P型晶体管27向输出布线N23供给电流。这样一来,因为第二电源VBIAS随第一电源VDD1的电位的上升而上升,所以能够改善第二电源VBIAS的上升特性。其结果是,在上电时序时,能够使电平位移电路装置4(参照图1)又早又可靠地达到期望的初始逻辑。此外,在正常工作时,将高电平信号作为输出信号XOUT输出,因此P型晶体管27截止,不影响第二电源VBIAS的输出。

图3C示出电平位移电路装置5的结构例。

如图3C所示,电平位移电路装置5包括第一输入反相器51、第二输入反相器52、电平位移电路53以及输出反相器56,第一输入反相器51和第二输入反相器52串联连接,输出反相器56连接在第一电位VDD1与第二电位VBIAS之间。

第一输入反相器51将输入信号XIN反转,并生成在接地电位GND与第二电位VBIAS之间发生位移的第一输入信号XIN1。第二输入反相器52接收第一输入反相器51的输出,并生成在接地电位GND与第二电位VBIAS之间发生位移的第二输入信号XIN2。在本实施方式中,因为电平位移电路装置5的输入XIN与接地GND相连,所以将高电平信号作为第一输入信号XIN1输出,将低电平信号作为第二输入信号XIN2输出。需要说明的是,在本申请说明书中,“XIN1”“XIN2”及后述“XOUT”用作表示信号本身和该信号被传输到的布线这二者的符号。

电平位移电路53具有下述功能:在正常工作时,将在接地电位GND与第二电位VBIAS之间发生位移的信号转换为在第二电位VBIAS与第一电位VDD1之间发生位移的信号。

电平位移电路53包括转换部54和初始设定部55,转换部54由晶体管构成,即六个P型晶体管51a~51f和两个N型晶体管51g、51h,初始设定部55在上电时序时将电平位移电路53的输出设为规定输出。

在转换部54中,作为第一晶体管的P型晶体管51a、作为第二晶体管的P型晶体管51b以及作为第三晶体管的N型晶体管51g在第一电源VDD1与第一输入布线XIN1之间彼此串联连接。此外,作为第四晶体管的P型晶体管51d、作为第五晶体管的P型晶体管51e以及作为第六晶体管的N型晶体管51h在第一电源VDD1与第二输入布线XIN2之间彼此串联连接。

P型晶体管51a的栅极经由作为第一布线的布线N53与P型晶体管51d的漏极和P型晶体管51e的源极相连。P型晶体管51d的栅极经由作为第二布线的布线N54与P型晶体管51a的漏极和P型晶体管51b的源极相连。此外,P型晶体管51b、51e的栅极和N型晶体管51g、51h的栅极与第二电源VBIAS相连。

作为第七晶体管的P型晶体管51c连接在布线N54与第二电源VBIAS之间,其栅极与P型晶体管51b和N型晶体管51g的中间节点相连。作为第八晶体管的P型晶体管51f连接在布线N53与第二电源VBIAS之间,其栅极与P型晶体管51e和N型晶体管51h的中间节点相连。

并且,布线N53的信号经由输出反相器56反转,且作为在第二电位VBIAS与第一电位VDD1之间发生位移的输出信号XOUT输出。需要说明的是,在布线N54且与输出反相器56对应的位置,设有与输出反相器56形状相同的虚设反相器57。

初始设定部55是下述电路:在上电时序的初期,将布线N53引导至高电平,并进行引导以从电平位移电路装置5的输出布线XOUT暂时输出高电平信号。

初始设定部55包括作为第九晶体管的P型晶体管55a和作为第十晶体管的P型晶体管55b,P型晶体管55a和P型晶体管55b在第一电源VDD1与布线N54之间彼此串联连接。此外,初始设定部55包括作为第十一晶体管的P型晶体管55c和作为第十二晶体管的P型晶体管55d,P型晶体管55c连接在第一电源VDD1与布线N53之间,P型晶体管55d连接在第一电源VDD1与布线N53之间。P型晶体管55a的栅极与漏极彼此相连。P型晶体管55b的栅极与P型晶体管55c的漏极相连,P型晶体管55c的栅极与P型晶体管55b的漏极相连。即,P型晶体管55b与P型晶体管55c交叉耦合。而且,P型晶体管55d的栅极与输出布线XOUT相连。

下面对上电时序时的初始设定部55的工作情况进行说明。在下述说明中,设第一电源VDD1先上升。

首先,在上电时序的初期状态(第一电位VDD1=0[V]且第二电位VBIAS=0[V])下,布线N53和布线N54均为0[V]。

并且,当第一电源VDD1上升后,布线N53的电位随之上升。虽然在布线N54电位也上升,但由于通过二极管连接的P型晶体管55a降低阈值电压Vt2的降压作用,与布线N53相比,布线N54的电位上升延迟。这样一来,P型晶体管55b处于比P型晶体管55c弱的导通状态,因此布线N53为高电平,布线N54为低电平。而且,当N53为高电平时,输出信号XOUT为低电平,因此P型晶体管55d导通。这样一来,P型晶体管55d起到帮助布线N53变为高电平的作用。需要说明的是,在上电时序时,在第二电位VBIAS小于N型晶体管51h、51g的阈值电压Vt1的期间(VBIAS<Vt1的期间),N型晶体管51h、51g均截止。因此,处于向转换部54的输入被切断的状态。

然后,当VBIAS>Vt1时,N型晶体管51h、51g均导通。此处,如上所述,电平位移电路装置5的输入XIN与接地GND相连,因此N型晶体管51h的漏极为低电平,P型晶体管51f导通。这样一来,电平位移电路53的输出即布线N53为第二电位VBIAS,即,布线N53为低电平。因此,电平位移电路装置5的输出信号XOUT为高电平信号,即,输出第一电位VDD1。

需要说明的是,在正常工作时,因为VBIAS>Vt1的关系成立,所以将以上段落的记载看作是将高电平信号作为电平位移电路53的第一输入信号XIN1输入且低电平信号作为电平位移电路53的第二输入信号XIN2输入的情况的正常工作也无妨。

另一方面,对下述情况的工作情况进行说明:将高电平信号作为电平位移电路装置5的输入XIN输入,即,将低电平信号作为电平位移电路53的第一输入信号XIN1输入且将高电平信号作为电平位移电路53的第二输入信号XIN2输入。在此情况下,在电平位移电路53中,N型晶体管51g的漏极为低电平,P型晶体管51c导通。这样一来,布线N54为第二电位VBIAS,即,布线N54为低电平,电平位移电路53的输出即布线N53为高电平。因此,电平位移电路装置5的输出信号XOUT为低电平信号,即,输出第二电位VBIAS。

需要说明的是,初始设定部55的各晶体管的驱动能力与转换部54的各晶体管的驱动能力相比设得相对较低,因此在电平位移电路53正常工作时,初始设定部55的影响能够忽略。

图4A到图4C是电源开关电路3的结构例。

图4A的电源开关电路3A是交叉耦合型开关电路,且包括P型晶体管31和P型晶体管32,P型晶体管31连接在第二电源VBIAS与第四电源VINT之间,P型晶体管32连接在第三电源VDD3与第四电源VINT之间。P型晶体管31相当于第三晶体管,P型晶体管32相当于第四晶体管。

在图4A中,N31是表示第二电源VBIAS与P型晶体管31之间的连接布线的符号,N32是表示第三电源VDD3与P型晶体管32之间的连接布线的符号,N33是表示第四电源VINT与P型晶体管31、32之间的连接布线的符号。并且,P型晶体管31的栅极与布线N32相连,P型晶体管32的栅极与布线N31相连。

下面对电源开关电路3A的工作情况进行说明。

在上电时序时,如果仅第一电源VDD1上升,则第三电位VDD3=0[V],因此P型晶体管31导通,P型晶体管32截止,从第二电源VBIAS供给由偏压电位生成电路生成的第二电位VBIAS作为第四电源VINT。

在正常工作时,因为满足第二电位VBIAS<第三电位VDD3的关系,所以P型晶体管31截止,P型晶体管32导通,从第三电源VDD3供给第三电位VDD3作为第四电源VINT。

像这样,在电源开关电路3中,P型晶体管31、32具有彼此互斥的关系,即,构成为第二电源VBIAS与第三电源VDD3之间不会导通。这样一来,在仅第一电源VDD1先上升且第三电源VDD3未上升的情况下,也不会像现有技术那样有不必要的电流流动。

图4B的电源开关电路3B在图4A的电源开关电路3A的基础上,包括反相器33,反相器33接收电源检测电路6的输出DET,作为在接地GND与第二电位VBIAS之间发生位移的反转信号输出。而且,在电源开关电路3B中,布线N31不与第二电源VBIAS相连,而与反相器33的输出相连。

下面对电源开关电路3B的工作情况进行说明。

在上电时序时,如果仅第一电源VDD1上升,则电源检测电路6的输出DET为低电平,因此布线N31为第二电位VBIAS。其结果是,与电源开关电路3A的情况一样,P型晶体管31导通,P型晶体管32截止,从第二电源VBIAS供给第二电位VBIAS作为第四电源VINT。

在正常工作时,因为电源检测电路6的输出DET为高电平,所以布线N31为低电平(接地电位GND)。因此,P型晶体管31截止,P型晶体管32导通,从第三电源VDD3供给第三电位VDD3作为第四电源VINT。

像这样,在电源开关电路3B中,尤其是在第四电源VINT的负载电流增加的正常工作时,接地电位GND施加于P型晶体管32的栅极,因此与电源开关电路3A相比,能够提高第四电源VINT的电流供给能力。

图4C的电源开关电路3C在图4B的电源开关电路3B的基础上,在布线N32与布线N33之间设有二极管钳位电路34,在布线N31与布线N33之间设有二极管钳位电路35。

例如,如果第一电源VDD1先上升后,即,变为将第二电位VBIAS供到布线N31的状态后,第三电源VDD3上升,则有时第三电位VDD3和第二电位VBIAS暂时变为接近的电压。在此情况下,P型晶体管31、32的电阻值均变高,对第四电源VINT的电流供给能力暂时降低,因此有时第四电位VINT会暂时变得不稳定。

于是,通过像电源开关电路3C那样构成,在第四电位VINT暂时降低的情况下,从第二电源VBIAS或第三电源VDD3经由二极管钳位电路34、35中的至少一者向第四电源VINT供给电流。这样一来,能够避免第四电位VINT降低过度。

需要说明的是,在图4C中,也可以仅设置二极管钳位电路34、35中的一者,能够得到相同的效果。

图5是电平位移电路7的结构例。

图5的电平位移电路7是交叉耦合型电平位移电路。在电平位移电路7中,P型晶体管74a和N型晶体管74b、74c在第四电源VINT与接地GND之间按照记载顺序彼此串联连接,P型晶体管74d和N型晶体管74e、74f在第四电源VINT与接地GND之间按照记载顺序彼此串联连接。

经由反相器71反转的输入信号IN施加于N型晶体管74f的栅极,输入信号IN经由反相器71、72施加于N型晶体管74c的栅极。

P型晶体管74a的栅极经由布线N71与P型晶体管74d的漏极相连,P型晶体管74d的栅极经由布线N72与P型晶体管74a的漏极相连。并且,布线N72经由反相器75与布线VL1相连,该反相器75在接地电位GND与第四电位VINT之间发生位移。

N型晶体管74b、74e的栅极与电源检测电路6的输出DET相连。这样一来,电源检测电路6的输出DET为低电平,即,在上电时序时,N型晶体管74b、74e截止。

而且,用于设定初始值(用于下拉)的N型晶体管74g连接在布线N72与接地GND之间。N型晶体管74g的栅极经由在接地电位GND与第四电位VINT之间发生位移的反相器73与电源检测电路6的输出DET相连。这样一来,如果电源检测电路6的输出DET为低电平且从第一电源VDD1或第三电源VDD3供给稳态电压,则通过N型晶体管74g导通,布线N72被下拉,高电平信号输出到布线VL1。即,如果仅第一电源VDD1上升,则高电平信号输出到布线VL1,从接收到该信号的后述电平位移电路装置4输出高电平信号,因此P型晶体管11可靠地截止。

需要说明的是,因为电平位移电路7的正常工作情况与众所周知的交叉耦合型电平位移电路相同,所以此处省略其详细说明。

图6是电平位移电路8的结构例。

图6的电平位移电路8的基本结构与电平位移电路7相同,连接有第三电源VDD3来代替第四电源VINT这一点以及下拉晶体管74h的连接位置与电平位移电路7不同。

具体而言,在电平位移电路8中,N型下拉晶体管74h连接在布线N71与接地GND之间。这样一来,当电源检测电路6的输出DET为低电平且从第一电源VDD1或第三电源VDD3供给稳态电压时,低电平信号输出到布线VG2。这样一来,N型晶体管14可靠地截止。

需要说明的是,因为上述以外的结构和工作情况与电平位移电路7的情况相同,所以此处省略其详细说明。

图7A和图7B是电平位移电路装置4的结构例。

图7A的电平位移电路装置4A包括第一输入反相器51、第二输入反相器52、电平位移电路53A以及输出反相器56、58,第一输入反相器51和第二输入反相器52串联连接,输出反相器56、58连接在第一电源VDD1与第四电源VINT之间。在图7A中,用相同的符号表示与电平位移电路装置5(参照图3C)共同的构成要素,有时省略其说明。

电平位移电路53A的工作情况与图3C的电平位移电路53相同或相似,具有下述功能:在正常工作时,将在接地电位GND与第四电位VINT之间发生位移的信号转换为在第四电位VINT与第一电位VDD1之间发生位移的信号。

电平位移电路53A包括转换部54和初始设定部55A、59A,转换部54由与电平位移电路装置5共同的构成要素构成,初始设定部55A、59A在上电时序时将电平位移电路53的输出设为规定输出。

在初始设定部55A中,第一电源VDD1与布线N53之间未设置P型晶体管55d这一点与图3C的初始设定部55不同。另一方面,初始设定部55A的功能与初始设定部55相同,在上电时序的初期,将布线N53引导至高电平,并进行引导以从电平位移电路装置4A的输出布线OUT暂时输出高电平信号。

初始设定部59A包括作为逻辑电路的2输入的NOR电路59a和作为第九晶体管的N型晶体管59c。

NOR电路59a的一输入经由作为第十晶体管的N型晶体管59d与布线N53相连。此外,NOR电路59a的另一输入与电源检测电路6的输出DET相连。N型晶体管59d的栅极与第四电源VINT(相当于第二电源)相连。NOR电路59a的驱动电源是第四电源VINT。

N型晶体管59c的漏极经由作为第十一晶体管的N型晶体管59b与布线N54相连,源极与作为第三电源的接地GND相连,栅极与NOR电路59a的输出相连。N型晶体管59b的栅极与第二电源VBIAS(相当于第四电源)相连。

下面对上电时序时的初始设定部59A的工作情况进行说明。在下述说明中,设第一电源VDD1先上升。

首先,在上电时序的初期状态(第一电位VDD1=0[V]且第二电位VBIAS=0[V])下,电源检测电路6的输出DET为0[V],NOR电路59a的两个输入均为0[V]。

并且,当第一电源VDD1开始上升后,第二电位VBIAS和第四电位VINT随之上升。当第四电位VINT上升到规定电位时,NOR电路59a的输出为高电平,N型晶体管59c导通。此时,第二电位VBIAS也上升,因此N型晶体管59b导通。这样一来,布线N54与接地GND之间导通,布线N54为低电平,布线N53为高电平。因为布线N53的信号经由两个反相器56、58输出到布线VG1,所以P型晶体管11能更可靠地截止。

当布线N53为高电平时,该信号经由N型晶体管59d施加于NOR电路59a的输入。这样一来,NOR电路59a的输出变为低电平,N型晶体管59c截止,布线N54与接地GND之间的连接被切断。而且,在正常工作时,电源检测电路6的输出DET为高电平,因此不管布线N53的状态如何,NOR电路59a的输出都是低电平,初始设定部59A不会影响正常工作。

如上所述,通过同时使用初始设定部55A、59A,能够更可靠地确定上电时序的初始值。

图7B的电平位移电路装置4B在图7A的电平位移电路装置4A的基础上,在NOR电路59a的输出布线与第四电源VINT之间,设有辅助进行初始值设定的电容元件59e。通过采用这样的结构,在上电时序的第一电源VDD1上升时,利用电容元件59e使NOR电路59a的输出布线提升到第四电位VINT,N型晶体管59c的电流量增加,迅速可靠地进行向布线N54的初始值的位移。

总而言之,在图1的半导体集成电路装置100中,如果第一电源VDD1先上升,则电源检测电路6的输出DET为低电平,第二电源的第二电位VBIAS上升且为第一电位VDD1的1/2。此时,通过电源开关电路3的工作,从第四电源VINT输出第二电位VBIAS。如上所述,此时,在电源开关电路3中,不会像现有技术那样有不必要的电流流动。

与P型晶体管11的前级相连的电平位移电路7和电平位移电路装置4均在第一电源VDD1上升的同时,迅速输出高电平信号,P型晶体管11截止。这样一来,能够切断在P型晶体管11中流动的电流。此时,因为P型晶体管12的栅极与第四电源VINT相连,所以第二电位VBIAS施加于P型晶体管12的栅极。

而且,与N型晶体管14的前级相连的电平位移电路8的电平位移器在第一电源VDD1上升的同时,迅速输出低电平信号,因此N型晶体管14截止。这样一来,能够切断在N型晶体管14中流动的电流。

根据上述,本公开所涉及的半导体集成电路装置100在仅第一电源VDD1先上升的情况下,也不会产生不必要的电流,且不会超过构成电路的各晶体管的耐压。此外,能够使输出部10的输出为高阻抗状态,从而能够防止对与输出端子1相连的其他装置(省略图示)造成不良影响。

(第一实施方式的变形例)

图8是第一实施方式所涉及的半导体集成电路装置的电路结构图的另一例。

在图8的半导体集成电路装置100A中,N型晶体管13、15的栅极与第四电源VINT相连这一点与图1的结构不同。

通过采用这样的结构,因为N型晶体管13、15的栅极施加有第四电位VINT,所以即使从与半导体集成电路装置100A共同的第一电源VDD1所连接的其他装置向输出端子1施加第一电位VDD1的信号,也能够避免超过耐压。

因为其他结构和工作情况与上述说明一样,所以此处省略其详细说明。

<第二实施方式>

图9是第二实施方式所涉及的半导体集成电路装置的电路结构图。

在图9的半导体集成电路装置100B中,设有输出端子1的上拉功能这一点与图1的结构不同。上拉功能是指在输出端子1的输出处于高阻抗状态时,经由上拉电阻输出高电平信号的功能。需要说明的是,在下述说明中,以与第一实施方式的不同点为中心进行说明,在图9中,用相同的符号表示与图1共同的构成要素,有时省略说明。

如图9所示,半导体集成电路装置100B包括上拉电路90,上拉电路90由按照记载顺序彼此串联连接在第一电源VDD1与输出端子1之间的P型晶体管91、92以及上拉电阻93构成。

半导体集成电路装置100B还包括电平位移电路7和电平位移电路装置4,电平位移电路7经由反相器95接收上拉信号PU,电平位移电路装置4驱动P型晶体管的栅极。

电平位移电路7将在接地电位GND与核心电源的电压电平(例如,0.9[V])之间发生位移的输入信号IN转换为在接地电位GND与第三电位VDD3之间发生位移的输出信号OUT,并输出到电平位移电路装置4。

电平位移电路装置4接收电源检测电路6的输出DET和电平位移电路7的输出VL1,将在第四电位VINT与第一电位VDD1之间发生位移的信号输出到P型晶体管91的栅极。

P型晶体管92的栅极与第四电源VINT相连。

需要说明的是,电平位移电路7和电平位移电路装置4的电路结构与上述结构相同,此处省略其详细说明。

下面对半导体集成电路装置100B的工作情况进行说明。

首先,在正常工作时,如果上拉信号PU为高电平,则在半导体集成电路装置100B中,电平位移电路7和电平位移电路装置4的输出为低电平。这样一来,P型晶体管91、92均导通,来自第一电源VDD1的电流经由上拉电阻93流入输出端子1,输出端子1被上拉。需要说明的是,如果半导体集成电路装置100B的输出为低电平,则因为用N型晶体管13、14下拉的能力比用上拉电阻93上拉的能力高,所以输出端子为低电平。

此外,在上电时序时,如果上拉信号PU为高电平,则P型晶体管91、92的栅极与下述电路相连,该电路与P型晶体管11、12的栅极所连接的电路相同。因此,P型晶体管91、92与所述第一实施方式的P型晶体管11、12同样地进行工作。即,在上拉电路90中,P型晶体管91迅速可靠地截止,不会超过耐压,能够使输出为高阻抗状态。这样一来,能够防止对与输出端子1相连的其他装置(省略图示)造成不良影响。

需要说明的是,本公开不限于上述实施方式所示的构成,在不脱离本公开的主旨的范围内,也可将上述实施方式中说明的各构成要素组合起来构成新的实施方式。

-产业实用性-

在本公开中,能够提供一种半导体集成电路装置,即使高电压电源比低电压电源先上升,也不会超过耐压,且不会有不必要的电流流动,非常有用。

-符号说明-

1 输出端子

11 P型晶体管(第一晶体管)

12 P型晶体管(第二晶体管)

13 N型晶体管(第五晶体管)

2 偏压生成电路(降压电路)

3 电源开关电路

31 P型晶体管(第三晶体管)

32 P型晶体管(第四晶体管)

4 电平位移电路

51a P型晶体管(第一晶体管)

51b P型晶体管(第二晶体管)

51c P型晶体管(第七晶体管)

51d P型晶体管(第四晶体管)

51e P型晶体管(第五晶体管)

51f P型晶体管(第八晶体管)

51g N型晶体管(第三晶体管)

51h N型晶体管(第六晶体管)

53 电平位移电路

55a P型晶体管(第九晶体管)

55b P型晶体管(第十晶体管)

55c P型晶体管(第十一晶体管)

59a NOR电路(逻辑电路)

59b N型晶体管(第十一晶体管)

59c N型晶体管(第九晶体管)

59d N型晶体管(第十晶体管)

100 半导体集成电路装置

N53 布线(第一布线)

N54 布线(第二布线)

VDD1 第一电源

VBIAS 第二电源(第二电源、第四电源)

VDD3 第三电源

GND 接地(第三电源、第五电源)

VINT 第四电源(第二电源、第四电源)