时间交织数字模拟转换器及其转换方法

文献发布时间:2023-06-19 09:36:59

技术领域

本发明涉及电路技术领域,尤其涉及一种时间交织模拟数字转换器及其转换方法。

背景技术

各种应用对高速和大带宽(bandwidth)的数字模拟转换器(digital-to-analogconverter,DAC)都有很大的需求。时间交织(time-interleaved)DAC可以实现高速数字模拟转换操作,但是由于不同DAC通道之间的失配(mismatch)而导致失真。因此,需要创新的时间交织DAC架构,该时间交织DAC架构可以减轻由不同DAC通道之间的增益失配、偏移失配和/或时序失配引起的失真。

发明内容

有鉴于此,本发明提供一种时间交织模拟数字转换器及其转换方法,以减轻由不同DAC通道之间的增益失配、偏移失配和/或时序失配引起的失真。

根据本发明的第一方面,公开一种时间交织数字模拟转换器,用于将数字信号转换为模拟信号,包括:

数字处理电路,用于根据该时间交织数字模拟转换器的数字信号,产生多个数据序列,其中,该多个数据序列包括第一数据序列和第二数据序列;

时域动态元素匹配电路,用于将该第一数据序列的一部分与该第二数据序列的一部分交换,以产生第一调整后的数据序列和第二调整后的数据序列,其中,第一调整后的数据序列包括该第一数据序列的第一比特和该第二数据序列的第一比特,第二调整后的数据序列包括第一数据序列的第二比特和第二数据序列的第二比特;

多个数字模拟转换器,每个数字模拟转换器具有至少一个数字模拟转换器单元,其中,该多个数字模拟转换器包括第一数字模拟转换器和第二数字模拟转换器,第一数字模拟转换器包括回应于第一调整后的数据序列而操作的第一数字模拟转换器单元,以及第二数字模拟转换器包括回应于第二调整后的数据序列而操作的第二数字模拟转换器单元;以及

组合电路,用于通过组合该多个数字模拟转换器的模拟输出来产生模拟信号。

根据本发明的第二方面,公开一种时间交织数字模拟转换方法,用于将数字信号转换为模拟信号,包括:

根据该数字信号产生多个数据序列,其中,该多个数据序列包括第一数据序列和第二数据序列;

通过将该第一数据序列的一部分与该第二数据序列的一部分交换来执行时域动态元素匹配操作以产生第一调整后的数据序列和第二调整后的数据序列,其中,该第一调整后的数据序列包括:该第一数据序列的第一比特和该第二数据序列的第一比特,以及该第二调整后的数据序列包括第一数据序列的第二比特和第二数据序列的第二比特;以及

通过组合各自具有至少一个数字模拟转换器单元的多个数字模拟转换器的模拟输出来产生模拟信号,其中,该多个数字模拟转换器包括第一数字模拟转换器和第二数字模拟转换器,该第一数字模拟转换器包括响应于该第一调整的数据序列进行操作的第一数字模拟转换器单元,并且第二数字模拟转换器包括响应于第二调整的数据序列进行操作的第二数字模拟转换器单元。

本发明的时间交织数字模拟转换器由于包括时域动态元素匹配电路,用于将该第一数据序列的一部分与该第二数据序列的一部分交换,以产生第一调整后的数据序列和第二调整后的数据序列。通过这种方式使得增益、偏移更加平滑,例如每个周期模拟信号的增益、偏移更加平均,避免了增益和偏移的大幅波动;因此,本发明可以减轻时间交织模拟转换器的不同DAC通道所使用的之间的增益失配、偏移失配和/或时序失配引起的失真。

附图说明

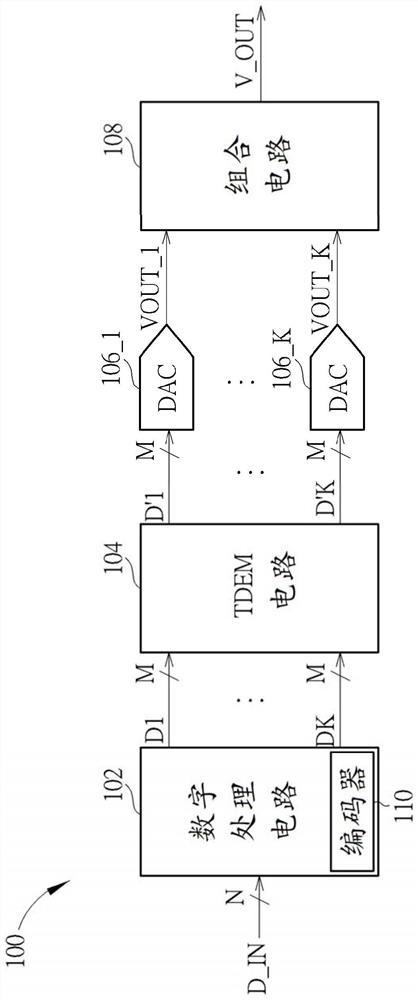

图1是示出根据本发明的实施例的具有时域动态元素(或元件)匹配(ime-domaindynamic element matching,TDEM)的时间交织的数字模拟转换器(DAC)的框图。

图2是示出根据本发明的实施例的图1所示的组合电路的操作的图。

图3是示出根据本发明的实施例的在时间交织DAC中使用的DAC的框图。

图4是示出根据本发明的实施例的没有TDEM的时间交织DAC操作的图。

图5是示出根据本发明的实施例的利用TDEM的时间交织DAC操作的图。

图6是示出根据本发明的实施例的具有TDEM的另一种时间交织DAC的框图。

图7是示出根据本发明的实施例的没有TDEM的另一种时间交织DAC操作的图。

图8是示出根据本发明的实施例的利用TDEM的另一时间交织DAC操作的图。

图9是示出根据本发明的实施例的图1和图6所示的TDEM电路的示例性设计的框图。

图10是示出根据本发明的实施例的随机序列交换操作的图。

具体实施方式

贯穿以下描述和权利要求使用某些术语,其指代特定部件。如本领域技术人员将理解的,电子设备制造商可以用不同的名称来指代部件。本文文件无意区分名称不同但功能相同的部件。在以下描述和权利要求中,术语“包括”和“包含”以开放式方式使用,因此应解释为表示“包括但不限于...”。同样,术语“耦接”旨在表示间接或直接的电连接。因此,如果一个设备耦接到另一设备,则该连接可以是通过直接电连接,或者是通过经由其他设备和连接的间接电连接。

图1是示出根据本发明的实施例的具有时域动态元素(或元件)匹配(time-domaindynamic element matching,TDEM)的时间交织的数字模拟转换器(digital-to-analogconverter,DAC)的框图。时间交织DAC 100(时间交织的DAC 100)包括数字处理电路102、TDEM电路104、多个DAC 106_1至106_K和组合电路108。每个DAC 106_1至106_K(DAC 106_1-106_K中的每一个)可视为时间交织DAC 100的一个DAC元件(或称为子DAC(sub-DAC))。时间交织DAC 100用于将数字信号D_IN转换为模拟信号V_OUT。在本实施例中,时间交织DAC 100可以是K通道(channel)N比特(bit)时间交织DAC,每个DAC 106_1-106_K(DAC 106_1-106_K中的每一个)可以具有M个DAC单元,其中,K,M和N为正整数,K>1,N≥1,M=2N-1。数字处理电路102布置为根据数字信号D_IN产生多个数字输入D1至DK,其中每个数字输入D1-DK(数字输入D1-DK中的每一个)包括M个数据序列。例如,数字输入Di包括数据序列Di_1至Di_M,其中

TDEM电路104布置为采用本发明提出的TDEM方案,用于调整数字输入D1-DK以产生调整后的数字输入(或称为调整数字输入)D'1-D'K,其中每个调整后的数字输入D'1-D'K包括M个调整后的数据序列(或称为调整数据序列)。例如,调整后的数字输入D’i包括调整后的数据序列D’i_1-D’i_M,其中

DAC 106_1-106_K布置为接收调整后的数字输入D’1-D’K,并将调整后的数字输入D’1-D’K分别转换为模拟输出VOUT_1-VOUT_K。组合电路108布置为通过组合DAC 106_1-106_K的模拟输出VOUT_1-VOUT_K来产生模拟信号V_OUT。

例如,组合电路108可以通过将交织应用于模拟输出VOUT_1-VOUT_K来产生模拟信号V_OUT。图2是示出根据本发明实施例的组合电路的操作或运行(operation)的图。假设时间交织DAC 100是两通道时间交织DAC,其中K=2。因此,时间交织DAC 100包括两个DAC106_1和106_2(也称为“P-DAC”和“N-DAC”),分别用于将数字模拟转换应用于调整后的数据输入D'1和D'2。本发明所提出的时间交织DAC 100与常规时间交织DAC之间的一个关键区别在于,经由本发明所提出的TDEM方案来产生DAC106_1和106_2的数字输入。在时钟周期CLK_S(具有周期Ts)的上升沿采样并输出在DAC 106_1产生的转换电压,并且在时钟CLK_S的下降沿采样并输出在DAC 106_2产生的转换电压。因此,DAC 106_1的模拟输出VOUT_1和DAC106_2的模拟输出VOUT_2在组合电路108处交织以产生模拟信号V_OUT。

结合图1所示,在本实施例中,每个DAC 106_1-106_K可以具有M个DAC单元,并且数字处理电路102可以具有编码器110,该编码器110用于将数字信号D_IN的每个N比特代码字(codeword)编码为一个M比特温度计(thermometer)代码,其中一个温度计代码的M比特分别分配给包括在数字输入D1-DK之一中的M个数据序列。换句话说,数字输入D1-DK包含相同温度计代码的不同比特。一个温度计代码的比特用于控制DAC单元的开/关状态。图3是示出根据本发明的实施例的在时间交织DAC中使用的DAC的框图。每个DAC 106_1-106_K可以具有相同的结构。为了清楚和简单起见,图3中仅示出了DAC106_1。DAC106_1包括多个DAC单元302_1-302_M,多个DAC单元302_1-302_M回应于包括在调整后的数字输入D'1中的调整后的数据序列D'1_1、D'1_2、D'1_3、…、D'1_M而操作或运行(进行操作、运行或工作),调整后的数字输入D'1从TDEM电路104产生。由于调整后的数字输入D'1-D'K是通过将TDEM技术应用于数字输入D1-DK而得出的,因此可以减轻时间交织DAC 100的不同DAC通道(channel)所使用的DAC 106_1-106_K之间的增益失配(或不匹配)、偏移失配和/或时序失配引起的失真。本发明提议的TDEM方案的更多详细信息将如下所述。

图4是示出根据本发明的实施例的没有TDEM的时间交织DAC操作的图。假设时间交织DAC 100是如图2所示的2通道3比特(2-channel 3-bit)时间交织DAC,考虑TDEM电路104直接将数字输入D1和D2分别旁通(bypasse)到DAC 106_1和106_2的情况,DAC 106_1(“P-DAC”)的DAC单元可以响应于由编码器110产生的每个偶数温度计码C0、C2、C4、C6、C8、C10的比特而操作或运行(operate),以及DAC106_2(“N-DAC”)的DAC单元可以响应于从编码器110产生的每个奇数温度计代码C1、C3、C5、C7、C9、C11的比特而操作或运行(进行操作、运行或工作)。在此示例中,温度计代码C0从最高有效位(MSB)到最低有效位(LSB)可以是“0000001”,温度计代码C1从MSB到LSB可以是“0000111”,温度计代码C2从MSB到LSB可以是“0011111”,温度计代码C3从MSB到LSB可以是“0001111”,温度计代码C4从MSB到LSB可以是“1111111”,温度计代码C5从MSB到LSB可以是“0001111”,温度计代码C6从MSB到LSB的可以是“0000011”,温度计代码C7从MSB到LSB可以是“0011111”,温度计代码C8从MSB到LSB可以是“0000111”,温度计代码C9从MSB到LSB可以是“0000011”,温度计代码C10从MSB到LSB可以是“0001111”,温度计代码C11从MSB到LSB可以是“0000111”。

在此示例中,未启用TDEM功能(未经过TDEM电路而直接到DAC)。当DAC 106_1(“P-DAC”)的DAC单元(表示为“cell-1”,“cell-2”,“cell-3”,“cell-4”,“cell-5”,“cell-6”和“cell-7”)接收到一个温度计代码的比特时,任意接收到“1”的DAC单元都打开(turn on),而任意接收到“0”的DAC单元都关闭(turn off)。当DAC 106_2(“N-DAC”)的DAC单元(表示为“cell-1”、“cell-2”、“cell-3”、“cell-4”、“cell-5”、“cell-6”和“cell-7”)接收到一个温度计代码的比特时,任意接收到“1”的DAC单元都打开(turn on),而任意接收到“0”的DAC单元都关闭(turn off)。例如,当DAC 106_1(“P-DAC”)的DAC单元接收到温度计代码C0的比特时,DAC单元“cell-1”打开,而DAC单元“cell-2”到“cell-7”关闭;当DAC 106_2(“N-DAC”)的DAC单元(表示为“cell-1”、“cell-2”、“cell-3”、“cell-4”、“cell-5”、“cell-6”和“cell-7”)接收到温度计代码C1的比特时,则DAC单元“cell-1”到“cell-3”打开,而DAC单元“cell-4”到“cell-7”关闭。

馈入到(feed into)DAC 106_1(“P-DAC”)的DAC单元“cell-1”到“cell-7”中的数据序列D1_1-D1_M(M=7)由温度计代码C0、C2、C4、C6、C8和C10设置。此外,馈入到DAC 106_2(“N-DAC”)的DAC单元“cell-1”到“cell-7”的数据序列D2_1-D2_M(M=7)由温度计代码C1、C3、C5,C7,C9和C11设置。例如,馈入到DAC 106_1(“P-DAC”)的DAC单元“cell-1”中的数据序列D1_1由“111111”设置,馈入到DAC 106_2(“N-DAC”)的DAC单元“cell-1”中的数据序列D2_1由“111111”设置。又例如,馈入到DAC 106_1(“P-DAC”)的DAC单元“cell-2”中的数据序列D1_2由“011111”设置,馈入到DAC 106_2(“N-DAC”)的DAC单元“cell-2”中的数据序列D2_2由“111111”设置。

为了对时间交织DAC的不同DAC通道所使用的DAC元件之间的增益失配(或不匹配)、偏移失配和/或时序失配进行搅乱(dither),本发明提出了TDEM方案。图5是示出根据本发明的实施例的利用TDEM的时间交织DAC操作的图。假设时间交织DAC 100是如图2所示的2通道时间交织DAC。在该示例中,使TDEM电路104能够将TDEM技术应用于数字输入D1和D2以产生调整后的数字输入D'1和D'2,以分别给向DAC 106_1和106_2,其中DAC 106_1(“P-DAC”)的DAC单元“cell-1”至“cell-7”分别回应于调整后的数据序列D’1_1-D’1_M(M=7)而操作或运行(进行操作、运行或工作),并且DAC 106_2(“N-DAC”)的DAC单元“cell-1”至“cell-7”分别回应于调整后的数据序列D'2_1-D'2_M(M=7)而操作或运行。

如图5所示,通过开启DAC 106_2(“N-DAC”)的DAC单元“cell-1”并关闭DAC 106_1(“P-DAC”)的DAC单元“cell-2”-“cell-5”及DAC 106_2(“N-DAC”)的DAC单元“cell-6”-“cell-7”,输出代表温度计代码C0的电压电平(voltage level);通过开启DAC 106_1的DAC单元“cell-1”(“P-DAC”)和DAC 106_2(“N-DAC”)的DAC单元“cell-2”-“cell-3”并关闭DAC106_2(“N-DAC”)的DAC单元“cell-4”-“cell-5”和DAC 106_1(“P-DAC”)的DAC单元“cell-6”-“cell-7”,输出代表温度计代码C1的电压电平;并且通过开启DAC 106_2(“N-DAC”)的DAC单元“cell-1”和“cell-3”以及DAC 106_1(“P-DAC”)的DAC单元“cell-2”、“cell-4”和“cell-5”,并关闭DAC 106_1(“P-DAC”)的DAC单元“cell-6”和DAC 106_2(“N-DAC”)的DAC单元“cell-7”,输出代表温度计代码C2的电压电平;等等。根据本发明提出的TDEM方案,由第一DAC的DAC单元和第二DAC的DAC单元相继处理的第一比特和第二比特在时域中互换或交换,使得第二比特和第一比特由第一DAC的DAC单元和第二DAC的DAC单元相继处理。此外,在图5所示的示例中(图5右边表格所示),是将温度计代码C0所在的周期中的cell-7与温度计代码C1所在的周期中的cell-7交换,温度计代码C0的cell-6与温度计代码C1的cell-6交换。但是在一些实施例中也可以将温度计代码C0所在的周期中的cell-7与温度计代码C1所在的周期中的cell-6交换。也就是说,本实施例中的交换中,未必是同一位置(同一顺序或同一排位)的比特或DAC单元,只要两者的数值或状态相同即可。例如在一个示例中,也可以将温度计代码C2所在的周期中的cell-3与温度计代码C3所在的周期中的cell-4交换。另外,本实施例中两个周期之间相互交换的比特或DAC单元数量最少为一个,最多取决与两个周期之间相同的比特或DAC单元,具体数量可以是随机的(图5中即表示了交换的数量是随机的),本发明不作限制。

在先前技术中,例如图5左边表格所示,在一个时间周期中,例如温度计代码C0所在的周期中,模拟信号或模拟输出V_OUT由DAC 106_1(“P-DAC”)决定,而DAC 106_1(“P-DAC”)中的DAC单元(例如DAC106_1中的cell-1至cell-7)具有固定的增益、偏移;在下一个时间周期时,例如温度计代码C1所在的周期中,模拟信号或模拟输出V_OUT由DAC106_2(“N-DAC”)决定,而DAC 106_2(“P-DAC”)中的DAC单元(例如DAC 106_2中的cell-1至cell-7)具有固定的增益、偏移(一般不同于温度计代码C0所在的周期的增益、偏移)。上述描述同样适用于温度计代码C2到C11所在的周期。因此对于每个时间周期,所输出的模拟信号V_OUT均有相应的增益和偏移,从而因不同DAC通道之间的失配而导致失真。而本发明实施例中,在一个时间周期中(例如温度计代码C0所在的周期中)根据下一个时间周期中(例如温度计代码C1所在的周期中)对应DAC单元的状态或数值,从而将一个时间周期中与下一个时间周期中状态或数值相同或相等的DAC单元进行互换,这样得到的模拟信号V_OUT不会发生变化,但是因为所使用的DAC单元发生了变化,因此所输出的模拟信号V_OUT的固定的增益、偏移相比先前技术发生了变化,也即可以通过这种方式使得增益、偏移更加平滑(例如每个周期模拟信号V_OUT的增益、偏移更加平均,避免了增益和偏移的大幅波动)。因此本发明实施例搅乱(dither)了时间交织DAC的DAC通道所使用的DAC单元,从而可以减轻时间交织模拟转换器的不同DAC通道所使用的之间的增益失配、偏移失配和/或时序失配引起的失真。

在本发明的一些实施例中,本发明所提出的TDEM方案可以与典型的DEM方案协作,以进一步减少单通道DAC的元素或元件(element)匹配误差,并改善时间交织DAC的性能。

图6是示出根据本发明的实施例的另一具有TDEM的时间交织DAC的框图。时间交织DAC 100和600之间的主要区别在于,数字处理电路602包括DEM电路610,该DEM电路610布置为采用不同于本发明上述所提出的TDEM方案的DEM方案。DEM电路610布置为通过将DEM算法应用于从编码器110产生的每个温度计代码来设置数字输入D1-DK。作为示例而非限制,DEM电路610所采用的DEM算法可以是数据加权平均(data weighted averaging,DWA)算法、随机加扰算法(random scrambling algorithm)或其他可用的DEM算法。DEM电路610根据基于对应的DAC 106_i的M个DAC单元执行的DEM算法来设置一个数字输入Di的M个数据序列,其中

图7是示出根据本发明的实施例的,在没有TDEM的情况下的另一种时间交织DAC操作的图。假设时间交织DAC 100是如图2所示的2通道(两通道)时间交织DAC。考虑TDEM电路104直接将数字输入D1和D2分别旁通到DAC 106_1和106_2的情况,DAC 106_1(“P-DAC”)的DAC单元响应于数字输出D1而进行操作或运行,并且DAC 106_2的DAC单元响应于数字输入D2而进行操作或运行。DEM电路610将DEM算法应用于每个温度计代码C0-C11。因此,DAC106_1的DAC单元响应于偶数温度计代码C0、C2、C4、C6、C8、C10的DEM结果而操作或运行,并且DAC 106_2的DAC单元响应于奇数温度计代码C1、C3、C5、C7、C9、C11的DEM结果而操作或运行。

根据本发明所采用的DEM算法,温度计代码C0的DEM结果从MSB到LSB可以是“0001000”,温度计代码C1的DEM结果从MSB到LSB可以是“0100101”,温度计代码C2的DEM结果从MSB到LSB可以是“0011111”,温度计代码C3的DEM结果从MSB到LSB可以是“1011010”,温度计代码C4的DEM结果从MSB到LSB可以是“1111111”,温度计代码C5的DEM结果从MSB到LSB的可以是“0101101”,温度计代码C6的DEM结果从MSB到LSB可以是“1000100”,温度计代码C7的DEM结果从MSB到LSB的可以是“1011011”,温度计代码C8的DEM结果从MSB到LSB的可以是“0000111”,温度计代码C9的DEM结果从MSB到LSB可以是“0100100”,温度计代码C10的DEM结果从MSB到LSB可以是“1101010”,温度计代码C11的DEM结果从MSB到LSB可以是“1010001”。

在此示例中,先假设未启用TDEM功能。此时,当DAC 106_1(“P-DAC”)的DAC单元(以“cell-1”,“cell-2”,“cell-3”,“cell-4”,“cell-5”,“cell-6”和“cell-7”表示)接收到一个温度计代码的DEM结果时,任意接收“1”的DAC单元打开,任意接收“0”的DAC单元关闭。当DAC 106_2(“N-DAC”)的DAC单元(以“cell-1”,“cell-2”,“cell-3”,“cell-4”,“cell-5”,“cell-6”和“cell-7”表示)接收到一个温度计代码的DEM结果时,任意接收到“1”的DAC单元都打开,任意接收到“0”的DAC单元都关闭。例如,当DAC 106_1(“P-DAC”)的DAC单元接收温度计代码C0的DEM结果时,DAC单元“cell-4”打开,而DAC单元“cell-1”至“cell-3”和“cell-5”至“cell7”关闭;当DAC 106_2(“N-DAC”)的DAC单元接收到温度计代码C1的DEM结果时,DAC单元“cell-1”、“cell-3”和“cell-6”打开,DAC单元“cell-2”、“cell-4”、“cell-5”和“cell-7”关闭。

馈入到DAC 106_1(“P-DAC”)的DAC单元“cell-1”-“cell-7”中的数据序列D1_1-D1_M(M=7)通过温度计代码C0、C2、C4、C6、C8和C10的DEM结果来设置。另外,馈入到DAC106_2的DAC单元“cell-1”-“cell-7”(“N-DAC”)中的数据序列D2_1-D2_M(M=7)通过温度计代码C1、C3、C5、C7、C9和C11的DEM结果来设置。例如,馈入到DAC 106_1(“P-DAC”)的DAC单元“cell-1”的数据序列D1_1为“011010”,馈入到DAC 106_2(“N-DAC”)的DAC单元“cell-1”的数据序列D2_1为“101101”。又例如,馈入到DAC 106_1(“P-DAC”)的DAC单元“cell-2”的数据序列D1_2为“011011”,馈入到DAC 106_2(“N-DAC”)的DAC单元“cell-2”的数据序列D2_2为“010100”。

为了对时间交织DAC的不同DAC通道所使用的DAC元件之间的增益失配(或不匹配)、偏移失配和/或时序失配进行搅乱,本发明提出了TDEM方案。图8是示出根据本发明的实施例的利用TDEM的另一时间交织DAC操作的图。假设时间交织DAC 100是如图2所示的2通道(两通道)时间交织DAC。在该示例中,使TDEM电路104能够将TDEM技术应用于数字输入D1和D2以产生调整后的数字输入D'1和D'2,以分别输入到DAC 106_1和106_2,其中数字输入D1和D2由DEM电路610设置,DAC 106_1(“P-DAC”)的DAC单元“cell-1”-“cell-7”分别回应于调整后的数据序列D'1_1-D'1_M(M=7)而操作或运行,DAC 106_2(“N-DAC”)的DAC单元“cell-1”-“cell-7”分别回应于调整后的数据序列D'2_1-D'2_M(M=7)而操作或运行。

如图8所示,通过开启DAC 106_1(“P-DAC”)的DAC单元“cell-4”并关闭DAC 106_1(“P-DAC”)的DAC单元“cell-1”、“cell-3”和“cell-6”,以及关闭DAC 106_2(“N–DAC”)的DAC单元“cell-2”、“cell-5”和“cell-7”,输出代表温度计代码C0的电压电平;通过开启DAC106_2(“N-DAC”)的DAC单元“cell-1”、“cell-3”和“cell-6”并关闭DAC 106_1(“P-DAC”)的DAC单元“cell-2”、“cell-5”和“cell-7”和DAC 106_2(“N-DAC”)的DAC单元“cell-4”,输出代表温度计代码C1的电压电平;通过打开DAC106_1(“P-DAC”)的DAC单元“cell-1”、“cell-3”和“cell-5”和DAC 106_2(“N-DAC”)的DAC单元“cell-2”和“cell-4”,以及关闭DAC 106_1(“P-DAC”)的DAC单元“cell-6”和DAC 106_2(“N-DAC”)的DAC单元“cell-7”,输出代表温度计代码C2的电压电平;等等。根据本发明提出的TDEM方案,由第一DAC的DAC单元和第二DAC的DAC单元相继处理的第一比特和第二比特在时域中交换,使得第二比特和第一比特由第一DAC的DAC单元和第二DAC的DAC单元相继处理。

关于图5和图8所示的示例,TDEM电路104将第一数据序列的一部分与第二数据序列的一部分交换,以产生第一调整后的数据序列(被馈送到位于时间交织DAC的第一通道的第一DAC的一个DAC单元中)和第二调整后的数据序列(被馈送到位于时间交织DAC的第二通道的第二DAC的一个DAC单元中),这样第一调整数据序列包括第一数据序列的第一比特和第二数据序列的第一比特,第二调整数据序列包括第一数据序列的第二比特和第二数据序列的第二比特。在本发明的一些实施例中,可以随机选择第二数据序列的第一比特和第一数据序列的第二比特,从而避免由TDEM引起的数据相关噪声。

此外,通过如图5和8所示的适当的比特交换,由一个DAC单元处理的调整后的数据序列包括来自数字处理电路102/602的不同数据序列的比特。因此,可以通过使用属于不同DAC的DAC单元来确定代表一个温度计代码的电压电平。以此方式,可以通过所提出的TDEM方案来减轻由不同DAC通道所使用的DAC元件之间的增益失配、偏移失配和/或定时失配引起的失真。

DAC单元的固有特性可以包括建立时间,该建立时间是响应于数字输入而产生稳定的模拟输出所需要的时间。如果DAC单元的两个连续比特具有不同的值,则DAC单元可能需要两个建立时间周期以产生代表两个连续比特的不同的稳定电压。如果DAC单元的两个连续比特具有相同的值,则DAC单元可能只需要一个建立时间周期即可连续产生代表两个连续比特的相同稳定电压。为了确保高速DAC操作,TDEM方案可以进一步检查数据序列中包含的比特,以选择合适的比特交换时序(timing)。具体地,可以基于数据序列中包括的比特的比较结果来控制不同数据序列的比特交换的时序。

图9是示出根据本发明的实施例的图1和图6所示的TDEM电路104的示例性设计的框图。在本实施例中,TDEM电路104包括检测电路902和交换电路904。检测电路902布置为检查一个数字输入的第一数据序列和另一数字输入的第二数据序列以产生通知信号。交换电路904布置为根据通知信号将第一数据序列的一部分与第二数据序列的一部分交换。例如,检测电路902检测要被连续处理的两比特是否具有相同的二进制值,其中要被连续处理的两个比特包括属于第一数据序列的一个比特(例如,第一温度计码的一个比特),并且属于第二数据序列的一个比特(例如紧接在第一温度计码之后的第二温度计码的一个比特),并产生通知信号,用于通知交换电路904检测到具有相同二进制值的两个比特。响应于通知信号,交换电路904随机确定是否将第一数据序列的一部分与第二数据序列的一部分交换。由于交换电路904执行随机序列交换,所以可以避免由TDEM引起的与数据有关的噪声。

假设时间交织DAC 100/600是如图2所示的2通道时间交织DAC。检测电路902可以检查数字输入D1的数据序列D1_1和数字输入D2的数据序列D2_1以产生通知信号CS_1,检查数字输入D1的数据序列D1_2和数字输入DK的数据序列D2_2,以产生通知信号CS_2,依此类推。交换电路904可以在由通知信号CS_1通知之后,将比特交换应用于数据序列D1_1和D2_1以产生调整后的数据序列D'1_1和D'2_1,可以在通过通知信号CS_2通知之后,将比特交换应用于数据序列D1_2和D2_2以产生经调整的数据序列D'1_2和D'2_2,以此类推。

在本发明的一些实施例中,DAC 106_1-106_K可以分别由时钟输入触发。例如,时间交织DAC 100/600可以进一步包括图9中所示的时钟产生电路906。时钟产生电路906布置为根据由时钟源(未显示)提供的外部时钟CLK来产生多个时钟输入RZ_1-RZ_K。交换电路904可以进一步布置为调整时钟输入RZ_1-RZ_K,以产生分别提供给DAC 106_1-106_K的多个调整后的时钟输入RZ'_1-RZ'_K。时钟输入RZ_1-RZ_K中的每一个分别包括用于多个DAC单元的多个参考时钟。每个调整后的时钟输入RZ’_1-RZ’_K包括用于控制相应DAC的DAC单元的多个时钟。

交换电路904可以根据通知信号,通过将一个时钟输入的第一参考时钟的一部分与另一时钟的第二参考时钟的一部分交换来产生一个调整后的时钟输入的第一时钟和另一个调整后的时钟输入的第二时钟。如上所述,交换电路904在由通知信号通知之后,随机确定是否将第一数据序列的一部分与第二数据序列的一部分交换。类似地,响应于通知信号,交换电路904随机确定是否将第一参考时钟的一部分与第二参考时钟的一部分交换。例如,当交换电路904决定将第一数据序列的一部分与第二数据序列的一部分交换时,交换电路904进一步将第一参考时钟的一部分与第二参考时钟的一部分交换。具有TDEM的时间交织DAC可以正常运行。

假设时间交织DAC 100是如图2所示的2通道3位时间交织DAC。时钟输入RZ_1包括最初为DAC 106_1的M个DAC单元产生的参考时钟RZ_11-RZ_1M(M=7)。时钟输入RZ_2包括最初为DAC 106_2的M个DAC单元产生的参考时钟RZ_21-RZ_2M(M=7)。当启用TDEM方案以调整数据输入D1和D2以分别为DAC 106_1和106_2产生调整后的数据输入D'1和D'2时,交换电路904进一步调整时钟输入RZ_1和RZ_2以产生分别用于DAC 106_1和106_2的调节时钟输入RZ'_1和RZ'_2,其中DAC 106_1的M个DAC单元由包括在调节后的脉输入RZ'_1中的时钟RZ'_11-RZ'_1M提供时钟,DAC 106_2的M个DAC单元由包括在调整后的时钟输入RZ'_2中的时钟RZ'_21-RZ'_2M提供时钟。具体地,交换电路904可以将时钟交换应用于参考时钟RZ_11和RZ_21以产生输入时钟RZ'_11和RZ'_21,将时钟交换应用于参考时钟RZ_12和RZ_22以产生时钟RZ'_12和RZ'_22,等等。

图10是示出根据本发明的实施例的随机序列交换操作的图。假设时间交织DAC100/600是如图2所示的2通道3比特时间交织DAC。数字处理电路102/602提供数据序列D1_1和DK_1(以下以K=2为示例),其中数据序列D1_1是最初为DAC 106_1产生的数字输入D1的一部分,数据序列DK_1是最初为DAC 106_2产生的数字输入DK(K=2)的一部分。时钟产生电路906提供参考时钟RZ_11和RZ_K1(K=2)。TDEM电路104根据数据序列D1_1和DK_1产生调整后的数据序列D'1_1和D'K_1(K=2),并根据参考时钟RZ_11产生时钟RZ'_11和RZ'_K1(K=2)和RZ_K1。具体地,DAC 106_1的一个DAC单元(例如“cell-1”)由时钟RZ’_11提供时钟,并且回应于调整后的数据序列D’1_1而操作。DAC 106_2的一个DAC单元(例如,“cell-1”)由时钟RZ’_K1(K=2)提供时钟,并且回应于调整后的数据序列D’K_1(K=2)而工作。

关于调整数据序列D'1_1和D'K_1(K=2)以及时钟RZ'_11和RZ'_K1(K=2)的产生,检测电路902监视或监测(monitor)数据序列D1_1和DK_1(K=2),用于依次并交替地检查将由DAC 106_1的DAC单元(例如“cell-1”)和DAC 106_2的DAC单元(例如“cell-1”)处理的比特。如图10的顶部所示,数据序列D1_1最初是通过参考时钟RZ_11的上升沿采样的,数据序列DK_1(K=2)最初是通过参考时钟RZ_K1的上升沿采样的(K=2)。因此,要连续处理的比特是“10100101100”。检测电路902发现要连续处理的两个比特具有相同的值“0”,并产生通知信号以通知交换电路904。在检测电路902通知后,交换电路904随机确定是否启用比特交换以更改馈入DAC 106_1的DAC单元(例如“cell-1”)和DAC 106_2的DAC单元(例如“cell-1”)的数据序列的比特样式(pattern),并随机确定是否启用时钟交换,用于改变提供给DAC106_1的DAC单元(例如“cell-1”)和DAC 106_2的DAC单元(例如“cell-1”)的时钟脉冲序列。在本实施例中,例如,交换电路904响应于由于检测到具有相同值“0”的两个比特而产生的通知信号,决定执行比特交换和时钟交换。如图10的底部所示,交换电路904通过将数据序列D1_1的一部分1002与数据序列DK_1的一部分1004(K=2)交换来产生调整后的数据序列D'1_1和D'K_1(K=2),并通过将参考时钟RZ_11的一部分1006与参考时钟RZ_K1的一部分(K=2)交换来产生时钟RZ’_11和RZ’_K1(K=2)。调整后的数据序列D’1_1由时钟RZ’_11的上升沿采样,使得由DAC 106_1的一个DAC单元(例如“cell-1”)要处理的比特为“11110”。调整后的数据序列D'K_1(K=2)通过时钟RZ'_K1(K=2)的上升沿进行采样,使得由DAC 106_K的一个DAC单元(例如“cell-1”)要处理的比特为“000010”。应当注意,通过使用DAC 106_1的DAC单元(例如“cell-1”)和DAC 106_K的DAC单元(例如“cell-1”)来转换相同的比特序列“10100101100”。

本发明对DAC单元的设计没有限制。因此,取决于实际的DAC单元设计,可以省略时钟交换。即,交换电路904的时钟交换功能可以是可选的。另外,本实施例中,当不是所交换的不是同一位置(同一顺序或同一排位)的比特或DAC单元时,上述时钟交换也可以根据所交换的比特或DAC单元进行相应的交换,在此不再赘述。

本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该装置和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。