一种LDPC码的分层译码中迭代数据处理方法及译码器系统

文献发布时间:2023-06-19 09:36:59

技术领域

本发明涉及无线通信技术领域,尤其是一种LDPC码的分层译码中迭代数据处理方法及译码器系统。

背景技术

随着高速数据传输业务的快速发展以及5G标准商用化,人们对信息传输的质量和速率要求越来越高,高速LDPC(Low-density Parity-check,低密度奇偶校验)码译码器在通信系统中的应用需求更加强烈。在固有的信道环境下,如何既满足越来越高的数据传输速率要求,又保证信息传输的可靠性,是信道编码技术研究的主要任务和目标。

目前,LDPC码译码时主要是有串行译码、并行译码和部分并行译码算法,基于PLDA(Parallel layered Decoding Algorithm,分层译码)算法,PLDA算法由于其在资源和速率方面的兼顾成为实际系统中的通用算法,然而在进行译码时,实现消息迭代计算和置换网络设计的复杂度较大,从而影响译码器的实现难度。

发明内容

为解决现有技术中的技术问题,本发明提供了一种LDPC码的分层译码中迭代数据处理方法及译码器系统。

本发明的技术方案为:一种LDPC码的分层译码中迭代数据处理方法,包括以下步骤:

S1对LDPC码的校验节点消息R

S2消息迭代处理

1、第1分层至第7分层顺序执行节点消息更新,记符号t(t=1,2,,,7)表示为层数,m(m=1,2,,,80)表示分层内的行数,迭代次数l=1,2,,,9;

a、对于第t分层内的80行,同时执行变量节点消息更新运算,公式为:

其中Q

b、对于第t层内的80行,同时执行校验节点消息更新运算,公式为:

其中α表示为归一化因子;

c、对于第t层内的80行,同时执行后验概率消息更新运算,公式为:

2、译码判决

每一次迭代处理完成之后,对译码序列

S3停止迭代

若达到设定的最大迭代次数,则停止迭代,且将

优选地,所述LDPC码为QC-LDPC码,其码长X为4480、码率7/8、行重为24、列重为3、循环置换矩阵为7×7的子矩阵。

优选地,一种译码器系统,包括:

控制模块:译码器中最核心的控制模块,主要用于控制、协调译码器其他模块按照预定的执行顺序依次完成迭代译码工作;

校验变量节点消息联合处理模块:主要用于完成一个分层内所有行中非零元素对应的节点消息更新运算,包括变量节点消息Q

校验节点消息存储模块:主要用于存储迭代过程中更新的R

后验概率消息寄存模块:用于寄存迭代过程中更新的Q

数据置换网络模块:主要功能是将一个分层中所有非零元素所在列对应的 Q

信道消息输入缓存模块:主要用于接收输入的

译码码字输出缓存模块:作用是缓存后验概率消息寄存模块传递来的一帧判决码字,并将其输出至芯片外。

优选地,所述校验变量节点消息联合处理模块由80个节点消息联合处理单元构成,任一所述节点消息联合处理单元由一个CNU单元和一个VNU单元构成,所述CNU单元主要用于完成校验节点消息更新运算,所述VNU单元由 VNU_1单元和VNU_2单元构成,所述VNU_1单元主要用于完成变量节点消息更新运算,所述VNU_2单元主要用于完成后验概率消息更新运算。

优选地,所述CNU单元主要工作过程为:

1)取VNU_1单元更新的LDPC码的行重数值个数的变量节点消息

2)求这LDPC码的行重数值个数的

3)根据index将min1、min2数值与各符号对应进行合并,即可求得一组更新的校验节点消息

优选地,还包括了次最小值寻找单元,其工作流程如下:

1)将输入的LDPC码的行重数值个数的Q数值分成两组,平均分配;

2)两组分别选取本组内的最小值,再将两个分组内选取的两个最小值进行比较,较小者为min1,较大者为min2,最小值位置index由较小者决定;

3)选取的min1为整个LDPC码的行重数值个数的Q数值中的最小数值;选取的min2若与min1没在同一分组内,则为整个LDPC码的行重数值个数的 Q数值中的次最小数值。

优选地,所述次最小值寻找单元由2输入1输出比较单元、2输入1输出排列次序分配单元与2输入2输出排列次序分配单元构成,级联三个基本单元单元组成树状结构,所述2输入1输出比较单元由1个2输入比较器和1个2输入的选择器组成,所述2输入1输出排列次序分配单元由1个2输入比较器和2 个2输入选择器构成,所述2输入2输出排列次序分配单元由1个2输入比较器和3个2输入选择器组成。

优选地,还包括一种归一化因子α优化方法,其具体步骤为:

1)将Min1右移1位,Min2右移2位;

2)再将经过移位Min1数值与未经过移位Min1的数值末尾位相加,得到 Min1归一化因子α,再将经过移位Min2数值与未经过移位Min2的数值末尾位相加,得到Min2归一化因子α。

优选地所述后验概率消息寄存模块由640个APP寄存块组成,第 c(c=1,2,,,640)个APPc寄存块按照列先后次序存储第c个CB所在列对应的7个 Q

优选地,所述数据置换网络模块由选通单元MUX1、选通单元MUX2、数据移位单元以及节点消息互连网络单元构成,所述选通单元MUX1单元完成译码迭代开始前的消息初始化工作,当初始化使能信号有效时,将信道消息输入模块收集到的一帧信道信息途径选通单元MUX1传递给APP寄存块组,反之,选通单元MUX1传递数据移位单元输出数据至APP寄存块组;

在译码迭代开始的第1个时钟周期Q

节点消息互连网络单元主要用于将APP寄存块组存储的Q

其中Q

与现有技术相比,本发明具有如下有益效果:

经过Vivado 14.4开发环境下的布局布线结果以及实际电路测试表明,译码器实现后的工作频率最高可达142.5Mhz。采用码长为4480的QC-LDPC码,其码速为7/8;设置迭代次数为9,一次迭代运算需要7个时钟周期;设计中加入了一级流水线处理以及译码迭代开始时初始化处理,因此需要额外2个时钟周期,根据吞吐量计算得到译码器最大可达到8.59Gbps的译码吞吐量。

附图说明

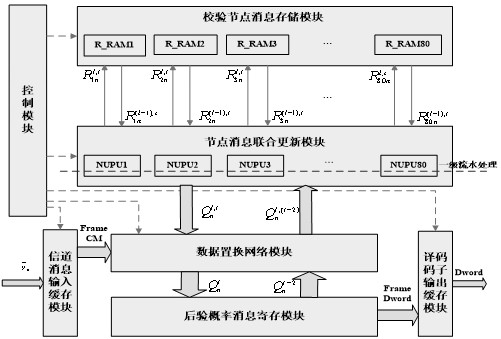

图1为发明的译码器总体设计框图示意图;

图2为发明的数据迭代处理设计的原理框图示意图;

图3为发明的节点消息联合处理单元结构框图示意图;

图4为发明的CNU单元总体设计框示意图;

图5为发明的Finder_Min1_Min2单元结构框图示意图;

图6为发明的2输入1输出比较单元设计框图示意图;

图7为发明的2输入1输出排列次序分配单元设计框图示意图;

图8为发明的2输入2输出排列次序分配单元设计框图示意图;

图9为发明的优化的归一化设计框图示意图;

图10为发明的校验节点处理单元CNU中数据分配器示意图;

图11为发明的VNU_1优化硬件设计电路示意图;

图12为发明的VNU_2优化硬件设计电路示意图;

图13为发明的校验节点消息存储模块设计框图示意图;

图14为发明的数据移位器设计框图示意图;

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明的描述中,需要理解的是,术语中“前”、“后”、“左”、“右”、“上”、“下”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了方便描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位,以特定的方位构造和操作,因此不能理解为对本发明的限制,本发明中各实施例的技术方案可进行组合,实施例中的技术特征亦可进行组合形成新的技术方案。

实施例

请参阅附图1至附图2所示,一个码长为4480,码率7/8,行重为24,列重为3的规则QC-LDPC码作为高速LDPC译码器设计码型,其循环置换矩阵为7×7 的子矩阵,目前标准中使用的码型绝大部分均为该类码型,本发明介绍的方法均可使用。其校验矩阵H

整个译码器译码流程如下(迭代次数l=1,2,,,9):

第一步、初始化:

对于n=1,2,,,4480

其中,

第二步:消息迭代处理:

1):第1分层至第7分层顺序执行节点消息更新,记符号t(t=1,2,,,7)表示为层数,m(m=1,2,,,80)表示分层内的行数。

a、对于第t分层内的80行,同时执行变量节点消息更新运算。

b、对于第t层内的80行,同时执行校验节点消息更新运算。

c、对于第t层内的80行,同时执行后验概率消息更新运算。

2):译码判决

每一次迭代处理完成之后,对译码序列

第三步、停止迭代

若达到设定的最大迭代次数,则停止迭代,且将

首先将从以下三方面对译码器总体设计框架进行说明:

1)、译码器总体设计框架

根据上面叙述的迭代流程,对该译码器进行总体方案规划,并划分各功能模块,其译码器结构由以下几个子功能模块组成,分别为:控制模块、信道消息输入缓存模块、译码码字输出缓存模块、节点消息联合处理模块、校验节点消息存储模块、后验概率消息寄存模块、数据置换网络模块。

各功能模块简要说明:

控制模块:译码器中最核心的控制模块,其职能是控制、协调译码器其他模块按照预定的执行顺序依次完成迭代译码工作。

节点消息联合处理模块:主要用于完成一个分层内所有行中非零元素对应的节点消息更新运算(包括变量节点消息Q

校验节点消息存储模块:主要用于存储迭代过程中更新的R

后验概率消息寄存模块:用于寄存迭代过程中更新的Q

数据置换网络模块:主要功能是将一个分层中所有非零元素所在列对应的 Q

信道消息输入缓存模块:主要用于接收输入的

译码码字输出缓存模块:作用是缓存后验概率消息寄存模块传递来的一帧判决码字,并将其输出至芯片外。

数据迭代处理主要用于完成整个译码器的数据处理、传递、存储等核心功能,该模块是迭代译码的核心。从图1可以看出,数据迭代处理设计主要由校验变量节点处理模块(Node Unite Processing Module,NUPM)、数据置换网络模块(Data InterconnectionNetwork Module,DINM)、校验节点消息存储模块 (Check Node Memory Module,CNMM)、后验概率消息寄存模块(APP-Register Module,APP-RM)等组成。四个模块互相协调,共同完成迭代译码工作,缺一不可。

从附图2可以看出,校验变量节点处理模块NUPM主要由80个NUPU组成。一个NUPU的功能是更新分层t内第m(m=1,2,,,80)行中非零元素位置对应的校验节点消息R

CNU单元主要用于完成校验节点消息更新运算。为了描述方便,将校验节点消息更新计算公式(3)改写为公式(5)、(6)、(7),即l次迭代译码时,更新第t分层m行中非零元素位置对应的

其中,sign()为求符号运算,满足要求

在设计实际电路中,不难看出,CNU单元的设计难点在于Finder_Min1_Min2 单元,即求min1、min2、index值,特别是对行度数较大的LDPC码而言这一问题显得更加突出,如本文所选LDPC码的行度数为24。这里我们提出一种基于概率的次最小值寻找方案,具体实现方案为:将输入的24个Q数值分成两组,前12个为第一组,后12个为第二组,两组分别选取本组内的最小值,再将两个分组内选取的两个最小值进行比较,较小者为min1,较大者为min2,索引值 index由较小者决定。分析得知,此方案选取的min1为24个Q数值中的最小数值;选取的min2若与min1没在同一分组内,则为24个Q数值中的次最小数值,反之,选取的min2有可能不是24个Q数值中的次最小数值,min2值的选取总是存在一定的概率成分,因此称此方案为基于概率的次最小值寻找方案。图5 为Finder_Min1_Min2单元结构框图。

Finder_Min1_Min2单元主要由三个基本单元组成,即2输入1输出比较 (CompareTwo To One,C2-1)单元、2输入1输出排列次序分配(Rank Order Sorter Two to One,ROS2-1)单元、2输入2输出排列次序分配(Rank Order Sorter Two to Two,ROS2-2)单元。级联三个基本单元单元组成树状Finder_Min1_Min2 实现结构,其各基本单元设计框图分别如附图6、附图7、附图8所示。

从附图6可以看出,C2-1单元由1个2输入比较器和1个2输入的选择器组成。输入信号是2个无符号数据a0、a1;输出信号为最小值min1与索引值index。 C2-1单元实现的功能如下:

if a0≤a1

min1=a0,index=0

else

min1=a1,index=1

如附图7是ROS2-1设计框图,ROS2-1单元由1个2输入比较器和2个2 输入选择器组成.。输入信号为前一级2组C2-1单元或ROS2-1单元的输出信号,分别为2个无符号数据a、b,2个最小值位置索引值index_a、index_b;输出信号包括min1、index。ROS2-1单元实现的功能如下:

if a≤b

min1=a,index={index0,index_a}

else

min1=b,index={index0,index_b}

附图8为ROS2-2设计框图,ROS2-2单元由1个2输入比较器和3个2输入选择器组成.。输入信号为前一级2组ROS2-1单元的输出信号,分别为2个无符号数据a、b,2个最小值位置索引值index_a、index_b;输出信号包括min1、 min2、index。ROS2-2单元实现的功能如下:

if a≤b

min1=a,min2=b,index={index0,index_a}

else

min1=b,min2=a,index={index0,index_b}

附图5展示了Finder_Min1_Min2单元设计框图,它由三个基本单元级联而成。针对24个输入信号的Finder_Min1_Min2单元需要分5步来实现,其中第一步由12个C2-1单元组成,最后一步需要1个ROS2-2单元,中间三步由10 个ROS2-1单元级联组成。根据三个基本单元所使用的比较器和选择器数目,可以估算Finder_Min1_Min2单元共需要23个2输入比较器和35个2输入选择器,需要说明的是Finder_Min1_Min2单元中无符号数据位宽均为4,索引index数据位宽为级联的比较层数k,即k=5。本发明提出的Finder_Min1_Min2结构与现有技术中的Finder_Min1_Min2结构资源消耗对比如表1所示。

表1 Finder_Min1_Min2结构资源消耗对比

从附图4可以看出,Finder_Min1_Min2单元输出的Min1和Min2数值需要分别乘以归一化因子α,这里选取α=0.75。硬件实现中,传统的方法是将 Min1(Min2)分别右移1位和2位,再将两个移位数值相加。然而传统方法得到的归一化数值与实际归一化数值之间有较大的误差,影响译码性能,比如4位二进制数0011,右移1位为001,右移2位为00,两移位数值相加为0001,与实际归一化值2.25相差1.25。为了缓解这一问题,本文提出了一种优化的归一化处理方案,具体方法是先将Min1(Min2)分别右移1位和2位,再将两个移位数值与Min1(Min2)的末尾位相加,得到的归一化数值与实际归一化数值之间相差不大,如上面列举的二进制数值0011,经过该方法处理后归一化数值为0010,与实际值仅相差0.25。使用b

校验节点处理单元CNU中数据分配器(Data Distributor)主要用于完成将m 行校验节点压缩R

迭代译码过程中,为了防止中间数据过大产生溢出,需要对中间数据进行适当的限制。从附图4可以看出,本文对CNU单元输入的24个变量节点消息Q 的数值Mag(Q)(数据位宽均为6bit)分别进行了数据截取处理。截取准则为:如果Mag(Q)大于15,则将其数值截取为15,除此之外,Mag(Q)保持不变。Q 消息的数值Mag(Q)经过截取处理后,数值均不大于15,因此仅需要4bit就可以表示Q消息的数值大小。如此以来,不仅防止了中间数据溢出,同时减少了后续Finder_Min1_Min2单元的资源消耗。

从附图3可以看出,VNU单元由VNU_1单元和VNU_2单元两部分组成,分别用于完成式2、4所示的运算过程。VNU_1主要用于完成变量节点消息

在VNU_1单元中,SM-2’S单元用来完成将符号-数值(Sign Magnitude,SM) 数据格式的

译码迭代过程中需要处理3种节点消息,它们分别为:变量节点消息Q

后验概率消息寄存模块用于寄存所有的Q

本发明中Q

从附图1可以看出,数据置换网络设计包括两个选通单元MUX1、MUX2,一个数据移位单元(Data Shift Unit,DSU)以及节点消息互连网络单元。在介绍各单元之前先对一些符号进行说明。

Q

Q

MUX1单元完成译码迭代开始前的消息初始化工作,当初始化使能信号Initial_En有效时,将信道消息输入模块收集到的一帧信道信息途径选通单元 MUX1传递给APP消息寄存器组,反之,选通单元MUX1传递数据移位单元输出数据至APP消息寄存器组。

在译码迭代开始的第1个时钟周期Q

节点消息互连网络单元主要用于将APP消息寄存器组存储的Q

根据矩阵行置换原则,由第t-1分层转换至第t分层仅需要将t-1分层中640 个80×7的列块进行单一的循环左移。硬件实现时,只需直接将第1分层非零元素所在列对应的Q

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。