一种具有高电源噪声抑制比的锁相环电路

文献发布时间:2023-06-19 09:36:59

技术领域

本发明涉及锁相环电路。

背景技术

锁相环技术已经被广泛应用在通信领域和几乎所有数字系统中来产生时钟。随着工艺技术提升和电源电压下降,对锁相环的设计也越来越严苛,主要包括低抖动输出,占用面积小,调谐范围宽以及对电源噪声要有高抑制能力以便用于超大规模集成电路系统中。

如图2所示,传统的锁相环电路主要由鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)和分频器(Divider)构成。具体工作原理是鉴频鉴相器可以甄别输入基准时钟(REFCLK)和反馈时钟(FBCLK)之间的频率和相位差值。通过电荷泵可以把该差值转化成充放电电流,随后经过环路滤波器输出压控振荡器的电压控制信号VCTRL,压控振荡器根据输入电压信号产生基于环路参数的时钟信号CKOUT。

在具有大规模数字电路的芯片内,为了实现在糟糕的电源噪声情况下更小的输出抖动(Jitter)特性,往往采用两种方法来设计锁相环电路。第一种是采用具有低抖动输出的LC振荡器,但是基于LC架构的VCO需要消耗大量的面积和功耗。另外一种方法是采用基于线性稳压器的电源调制锁相环技术,但是由于其有限的输入控制电压范围会导致调谐范围比较窄,与目前大规模集成电路中宽调谐范围的需求不符。

发明内容

本发明的目的在于提供一种具有高电源噪声抑制比的锁相环电路,解决现有抑制电源噪声技术中过多消耗面积功耗和调谐范围较窄的问题。

实现上述目的的技术方案是:

一种具有高电源噪声抑制比的锁相环电路,包括:鉴频鉴相器、电荷泵、环路滤波器和分频器,还包括:自校准频率电路和电源噪声抑制压控振荡器,

所述鉴频鉴相器的输出端连接所述电荷泵的输入端;

所述电荷泵的输出端连接所述环路滤波器的输入端和所述电源噪声抑制压控振荡器的第一输入端;

所述电源噪声抑制压控振荡器的输出端作为电路信号输出端,并连接所述分频器的输入端;

所述分频器的输出端输出反馈时钟给所述鉴频鉴相器的一个输入端,所述鉴频鉴相器的另一个输入端接收基准时钟;

所述自校准频率电路的两个输入端分别接收反馈时钟和基准时钟,输出端连接所述电源噪声抑制压控振荡器的第二输入端。

优选的,所述自校准频率电路包括:频率检测器和状态机控制单元,

所述频率检测器的两个输入端分别接收反馈时钟和基准时钟,输出端连接所述状态机控制单元的输入端,所述状态机控制单元的输出端连接所述电源噪声抑制压控振荡器的第二输入端。

优选的,所述电源噪声抑制压控振荡器包括:运算放大器、PMOS管、K比特的电流源阵列电路、电阻、电容和延迟单元(DELAY CELL),其中,

所述运算放大器的反相输入端作为所述电源噪声抑制压控振荡器的第一输入端,正相输入端通过所述电阻接地;

所述运算放大器的输出端分别连接所述PMOS管的栅极和所述K比特的电流源阵列电路的第一输入端;

所述K比特的电流源阵列电路的第二输入端作为所述电源噪声抑制压控振荡器的第二输入端;

所述PMOS管的源极一方面通过所述电容连接所述PMOS管的栅极,另一方面接电源;所述PMOS管的漏极通过所述电阻接地;

所述K比特的电流源阵列电路的输出端连接所述延迟单元的输入端,所述延迟单元的输出端作为所述电源噪声抑制压控振荡器的输出端。

优选的,所述运算放大器的反相输入端接收所述环路滤波器的输出;

所述K比特的电流源阵列电路接收所述自校准频率电路输出的编码K,切换VCO的波段;

所述延迟单元输出时钟信号。

本发明的有益效果是:本发明基于传统的锁相环电路架构,结合自校准频率电路(AFC)和电源噪声抑制压控振荡器(SRVCO)电路设计,可以在实现宽调谐范围的情况下有较小的KVCO(VCO的增益),适应了最新大规模集成电路中对锁相环宽输出范围的需求。并通过具有电源噪声抑制能力的压控振荡器实现相比于传统架构提升输出抖动(Jitter)约2-5倍的性能,在抑制电源噪声方面有较大优势。

附图说明

图1是现有技术中锁相环电路结构图;

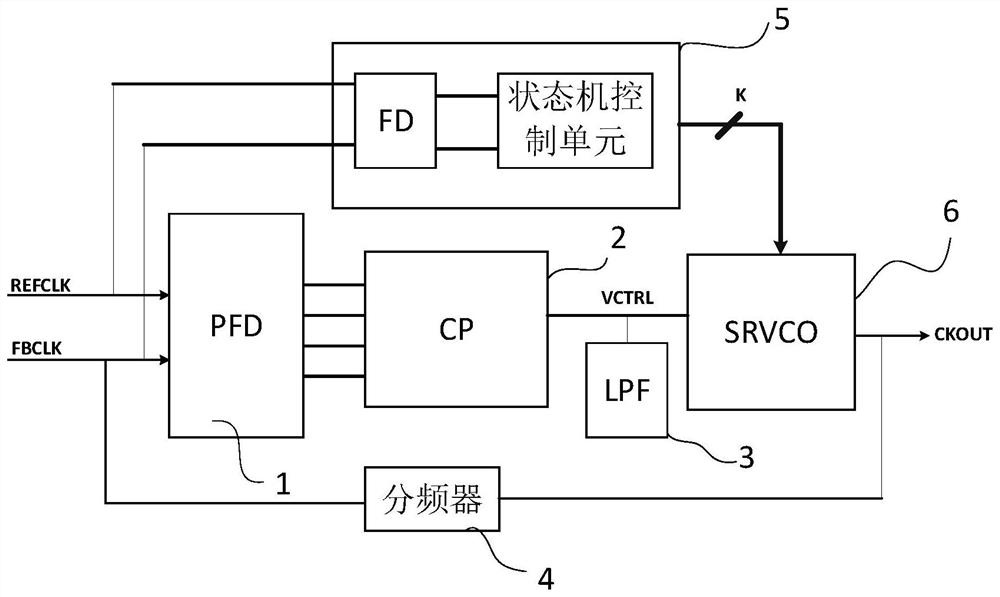

图2是本发明的锁相环电路的结构图;

图3是本发明中采用AFC技术与未采用AFC技术压控振荡器KVCO特性对比图;

图4是本发明中电源噪声抑制压控振荡器的电路图。

具体实施方式

下面将结合附图对本发明作进一步说明。

请参阅图1和图3,本发明的具有高电源噪声抑制比的锁相环电路,包括:鉴频鉴相器1、电荷泵2、环路滤波器3、分频器4、自校准频率电路5和电源噪声抑制压控振荡器6。

鉴频鉴相器1的输出端连接电荷泵2的输入端;电荷泵2的输出端连接环路滤波器3的输入端和电源噪声抑制压控振荡器6的第一输入端;电源噪声抑制压控振荡器6的输出端作为电路信号输出端,并连接分频器4的输入端。

分频器4的输出端输出反馈时钟FBCLK给鉴频鉴相器1的一个输入端,鉴频鉴相器1的另一个输入端接收基准时钟REFCLK。

自校准频率电路5的两个输入端分别接收反馈时钟FBCLK和基准时钟REFCLK,输出端连接电源噪声抑制压控振荡器6的第二输入端。

自校准频率电路5包括:频率检测器(Frequency Detector,FD)和状态机控制(State Machine)单元。频率检测器的两个输入端分别接收反馈时钟FBCLK和基准时钟REFCLK,输出端连接状态机控制单元的输入端,状态机控制单元的输出端连接电源噪声抑制压控振荡器6的第二输入端。

对于应用在大规模数字集成电路系统中的锁相环,电源噪声是限制环形振荡器型锁相环性能的主要因素,并且随着工艺进步,希望锁相环可以覆盖更宽的调谐范围,这样就会要求更大的KVCO,而增大的KVCO会直接影响整个锁相环对电源噪声的抑制能力,如公式1所示,从公式中容易得出,KVCO的降低可以直接减少电源噪声对输出时钟抖动性能的影响。

其中,KVCO代表VCO的增益;Icp代表电荷泵充放电电流大小;N代表Divider分频比;H

因此本发明采用自校准频率技术(AFC)可以扩展整个压控振荡器的调谐范围,并且在单个BAND(波段)中可以实现较小的KVCO,如图3所示。由于KVCO和锁相环电源噪声的抑制能力是反比关系,即KVCO越小,锁相环对电源噪声抑制能力越强,整个锁相环输出的时钟性能越好。

如图4所示,电源噪声抑制压控振荡器6包括:运算放大器A1、PMOS管M1、K比特的电流源阵列电路M2、电阻R1、电容C1和延迟单元61。

运算放大器A1的反相输入端作为电源噪声抑制压控振荡器6的第一输入端,正相输入端通过电阻R1接地。运算放大器A1的输出端分别连接PMOS管M1的栅极和K比特的电流源阵列电路M2的第一输入端。K比特的电流源阵列电路M2的第二输入端作为电源噪声抑制压控振荡器6的第二输入端。PMOS管M1的源极一方面通过电容C1连接PMOS管M1的栅极,另一方面接电源VDD;PMOS管M1的漏极通过电阻R1接地。K比特的电流源阵列电路M2的输出端连接延迟单元61的输入端,延迟单元61的输出端作为电源噪声抑制压控振荡器6的输出端。

运算放大器A1的反相输入端接收环路滤波器的输出VCTRL。延迟单元61输出时钟信号CKOUT。运算放大器A1、PMOS管M1、电阻R1和电容C1构成电压转电流电路,用于产生延迟单元61的供给电流。K比特的电流源阵列电路M2接收自校准频率电路5输出的编码K,来实现多个VCO的Band(波段)切换,可有效降低整个电源噪声抑制压控振荡器6的KVCO。图中,V

基本原理是通过前馈电容耦合的方式保证线性调整器的栅源电压保持恒定,从而使得输出的漏极电流不受电源噪声影响,则镜像至DELAYCELL的电流不受电源电压影响,可以达到较好的高频电源抑制能力,同时低频电源噪声能力由整个线性调整器环路增益所决定。具体的公式如下所示:

其中,K代表AFC输出的增益控制位;Gm2代表电流阵列单个MOS管的跨导值;R

从以上推导过程可以看出,相比于传统的线性调制器压控振荡器技术,采用的具有电源抑制能力的压控振荡器可以将电源噪声衰减环路增益倍,提高了VCO对电源噪声的抑制能力,通过仿真可实现30dB以上的电源噪声抑制效果。

综上,本发明结合自校准频率技术和带有电源抑制能力压控振荡器的电路结构,可以有效提高输出时钟信号的抖动性能2-5倍,在抑制电源噪声方面有较大优势,仿真结果如下表所示。

以上实施例仅供说明本发明之用,而非对本发明的限制,有关技术领域的技术人员,在不脱离本发明的精神和范围的情况下,还可以作出各种变换或变型,因此所有等同的技术方案也应该属于本发明的范畴,应由各权利要求所限定。