低功率触发器电路

文献发布时间:2023-06-19 09:36:59

背景技术

触发器可以指存储“高”值(功率高或逻辑为一)或“低”值(功率低或逻辑为零)的顺序电路。触发器可以存储取决于一个或多个输入信号的值的下一个值。通常,触发器可以包括数据、时钟、置位和/或复位输入信号。

数据(通常用“D”表示)输入信号典型地在接收到给定时钟沿时被记时到触发器中并出现在相反时钟沿上、在触发器输出处。置位(通常用“S”表示)和复位(通常用“R”表示)输入信号一般不被记时,这意味着当置位和复位信号变为活跃时(例如,走高),存储的值立即改变,而不等待时钟沿的到来。活跃置位信号强制将存储的值(通常用“Q”表示)设为高,而不管先前存储的值。活跃复位信号强制将存储的值设为低,而不管先前存储的值。在置位/复位触发器(即具有置位和复位输入信号二者的触发器)中,置位和复位信号典型地受到限制,使得在任意给定时间处其中的至多一个可以是活跃的。由于触发器是现代数字设计的基本组成部分,因此始终需要将其功耗和面积最小化。提出一种新的触发器设计,该新的触发器设计与传统设计相比将减少其功耗和面积。

发明内容

下面呈现了一个或多个方面的简化概述,以提供对这些方面的基本理解。该概述不是对所有设想的方面的广泛概览,且既不旨在识别所有方面的关键或重要的元素,也不旨在描绘任意或所有方面的范围。其唯一的目的是以简化的形式呈现一个或多个方面的一些概念,以作为之后呈现的更加详尽的描述的序言。

本公开呈现了触发器电路的示例。示例触发器电路可以包括触发器数据输入端子和触发器输出端子;提供第一时钟信号的第一时钟端子和提供第二时钟信号的第二时钟端子,其中,第二时钟信号是第一时钟信号的反相;第一传输门,耦合在触发器数据输入端子和第一节点之间,其中,第一传输门包括第一P沟道门极端子和第一N沟道门极端子,并且第一P沟道门极端子和第一N沟道门极端子分别连接至第一时钟端子和第二时钟端子;第一锁存器,耦合在第一节点和第二节点之间,其中,第一锁存器包括第一逻辑门和第二逻辑门,第一逻辑门具有耦合至第一节点的第一输入端子和耦合至第二节点的第一输出端子,第二逻辑门具有耦合至第二节点的第二输入端子和耦合至第一节点的第二输出端子,并且其中第二逻辑门包括至少一个第一压降部件和第一反相器;第二传输门,耦合在第二节点和第三节点之间,其中,第二传输门包括第二P沟道门极端子和第二N沟道端子,并且第二P沟道门极端子和第二N沟道端子分别连接至第一时钟端子和第二时钟端子;第二锁存器,耦合在第三节点和触发器输出端子之间,其中,第二锁存器包括第三逻辑门和第四逻辑门,第三逻辑门具有耦合至第三节点的第三输入端子和耦合至触发器输出端子的第三输出端子,第四逻辑门具有耦合至触发器输出端子的第四输入端子和耦合至第三节点的第四输出端子,并且其中第四逻辑门包括至少一个第二压降部件和第二反相器。

为了实现前述和相关目的,一个或多个方面包括了在权利要求中充分描述并特别指出之后的本文中的特征。以下描述和附图详细阐述了一个或多个方面的某些说明性特征。然而,这些特征只指示了各个方面的原理可以被运用的、各个方面中的几种,且该描述旨在包括所有这些方面及其等同物。

附图说明

下文将结合附图描述已公开的方面,这些附图提供为只是示出而不是限制已公开的方面,其中,类似的符号表示类似的元件,并且:

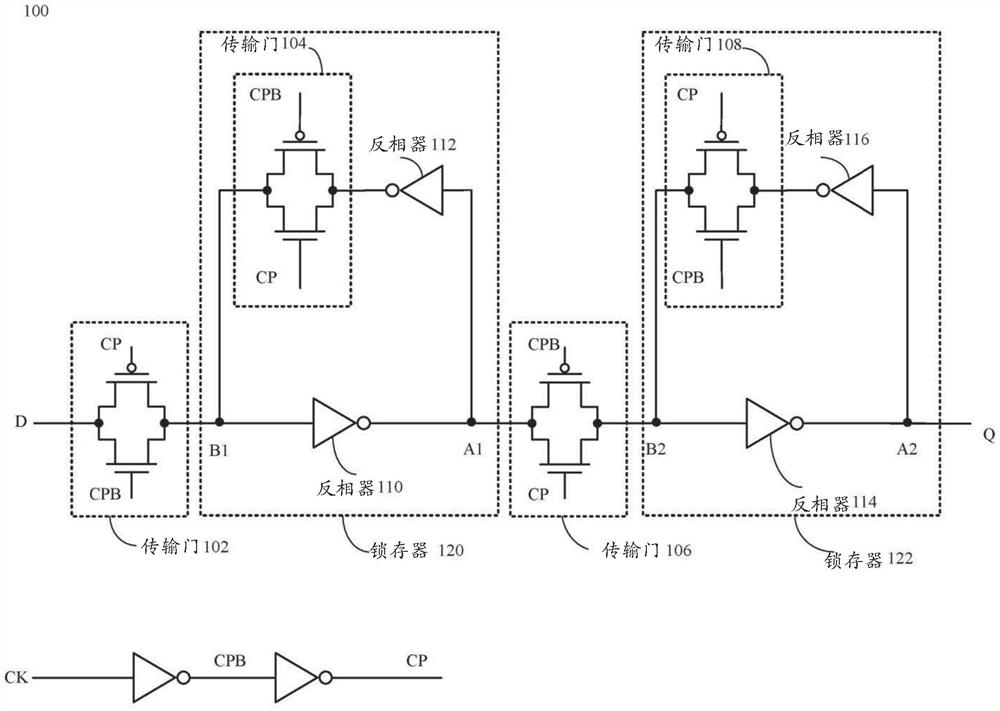

图1是示出传统触发器电路的框图;

图2是示出图1的传统触发器电路在时域中的信号的时序图;

图3是示出另一种传统触发器电路的框图;

图4A和4B是示出图3的传统触发器电路在时域中的信号的时序图;

图5是示出根据本发明的一个实施例的示例触发器电路的框图;

图6是示出根据本发明的一个实施例的示例触发器电路的一个或多个示例部件的框图;

图7是示出本发明的一个实施例的另一种示例触发器电路的框图;和

图8是示出图5或图7的触发器电路在时域中的信号的时序图。

具体实施方式

现在参考附图描述各个方面。在以下描述中,出于解释的目的,阐述了许多具体的细节以便提供对一个或多个方面的透彻理解。然而,显而易见的是,没有这些具体细节也可以实践这个(这些)方面。

触发器电路可以设计为包括由传输门分开的两个锁存器。例如,图1展示了传统触发器电路100,该传统触发器电路包括按顺序(sequentially)耦合在一起的传输门102、锁存器120、传输门106和锁存器122。传输门也可以指通过门或传送门。根据耦合至传输门的N沟道端子和P沟道的信号,传输门可以处于闭合状态(也可以称为“连接状态”)或打开状态。例如,触发器电路100的传输门102耦合在数据输入端子(图1中展示为“D”)和锁存器120之间。另一个传输门106耦合在锁存器120和锁存器122之间。锁存器120包括一对交叉耦合的反相器110和112以及在反馈中耦合至反相器112的传输门104。与锁存器120类似,锁存器122包括另一对交叉耦合的反相器114和116以及耦合至反相器116的传输门108。如图1中所示,时钟信号CK被反相以生成反相时钟信号CPB,该反相时钟信号CPB被提供至传输门102、104、106和108的相应N沟道端子。反相时钟信号CPB可以进一步被反相以生成时钟脉冲CP。时钟脉冲CP可以被提供至传输门102、104、106和108的相应P沟道端子。

图2展示了示出图1的传统触发器电路在时域中的信号的时序图。当CK为低时,CPB为高,传输门102处于闭合状态,这意味着从数据输入端子输入的信号可以通过传输门102到节点B1。B1处的数据值被反相器110反相并出现在节点A1处。因此,B1处的数据值为高且A1处的数据值为低。在CK的上升沿,传输门102改变到打开状态,且传输门106处于闭合状态。因此,节点A1处的数据值为低,且B2处的数据值改变到等于节点A1处的电压,如图1所示,从高下降到低。传输门104也改变到闭合状态以形成反馈回路来维持B1处的数据值。同时,节点B2处的数据值被反相,且因此,A2和Q处的数据值从低升到高。

如所示,图1的传统触发器可以正常运作以生成正确的信号。然而,传输门104和108以及反相器112和116可能引起高功耗。额外的功耗来自于传输门在时钟分配网络上的额外负载以及反相器的逻辑运算。因此,提出不具有反馈结构的另一种传统触发器电路。

图3展示了示出不具有反馈结构的另一种传统触发器电路的框图。

如所示,传统触发器电路300可以包括按顺序连接在一起的传输门302、反相器306、传输门304和反相器308。与提供至触发器电路100的时钟信号类似,时钟脉冲(CP)和反相时钟信号(CPB)被分别提供至传输门302和304的P沟道端子和传输门302和304的N沟道端子。在不具有反馈结构的情形下,触发器电路300的功耗可能低于触发器电路100。然而,触发器电路300可能会出现一些将导致逻辑错误的稳定性问题。

图4A和4B是示出图3的传统触发器电路300在时域中的信号的时序图。图4A展示了出现在节点B1和A1处的逻辑错误,这进一步导致节点B2和A2处的错误。图4B展示了可能出现在B2和A2处的逻辑错误。

更详细地,当时钟信号为低时,传输门302处于闭合状态。因此,B1处的数据值等于数据输入端子处的数据值。例如,在时间点T1前,B1处的数据值维持与D处的数据值(即,高)相同。在时间点T1时、在时钟信号的上升沿,传输门302改变到打开状态。当数据输入端子D处的数据值在时间点T2下降到低时,节点B1处的数据值应当已经维持在高处,因为传输门302现在是打开的。然而,由于传输门302处的泄漏,节点B1处的电压逐渐下降至与数据输入端子D处的电压相同的水平。节点B1处的数据值被反相并出现在节点A1处,使节点A1处的电压升到高。因为传输门304在时间点T2时处于闭合状态,B2处的数据值将跟随节点A1处的数据值升到高,并进一步被反相以出现在节点A2处。节点A2/Q处的数据值因此下降到低。

此外,当数据输入端子D处的数据值为低且时钟信号在时间点T4升到高时,传输门302是打开的。因为数据输入端子D处的数据值和节点B1处的数据值都为低,因此在时间点T4和T5之间,传输门302处不出现泄漏。然而,当数据输入端子D处的数据值在时间点T5升到高时,泄漏出现,且节点B1处的数据值跟随数据输入端子D处的电压升到高。节点B1处的数据值被反相器306反相,并且因此,端子A1处的数据值降到低。类似地,节点B2处的数据值降到低,且A2/Q处的数据值升到高。如所示,逻辑错误可能由于传输门302中的泄漏而出现。

如图4B中所示,类似的逻辑错误也可能由于传输门304处的泄漏而出现。当时钟信号CK在时间点T3从高降到低时,传输门302闭合且传输门304处于打开状态。节点B2处的数据值应当已经维持在高处。然而,因为节点A1处的数据值在时间点T3时升到高并且由于传输门304处的泄漏,节点B2处的数据值跟随节点A1处的数据值升到高。节点B2处的数据值进一步被反相器306反相,使A2/Q处的数据值从高降到低。

此外,当时钟信号CK在时间点T6从高降到低时,传输门304也处于打开状态,并且B2处的数据值应当已经维持在高处。然而,当节点A1处的数据值在时间点T6下降时,节点B2处的数据值也可能由于传输门304的泄漏而下降。节点B2处的数据值进一步被反相器306反相,使A2/Q处的数据值从低升到高。

图5是示出根据本发明的一个实施例的示例触发器电路的框图。如所描绘,示例触发器电路500可以包括按顺序连接在一起的传输门502、锁存器504、传输门506和锁存器508。

更详细地,传输门502可以耦合在数据输入端子D和第一节点(下文称为“节点B1”)之间。传输门502可以包括P沟道晶体管和N沟道晶体管,P沟道晶体管和N沟道晶体管分别具有P沟道门极端子和N沟道门极端子。在示例中,传输门502的P沟道门极端子可以耦合至时间脉冲CP,且传输门502的N沟道门极端子可以耦合至反相时钟信号CPB。P沟道晶体管和N沟道晶体管的源极和漏极端子分别连接在一起。

锁存器504可以耦合在节点B1和第二节点(下文称为“节点A1”)之间。在示例中,锁存器504可以包括第一逻辑门(例如,反相器510)和第二逻辑门(例如,逻辑门514)。反相器510的输入端子可以耦合至节点B1,并且反相器510的输出端子可以耦合至节点A1,而逻辑门514的输入端子可以耦合至节点A1,且逻辑门514的输出端子可以耦合至节点B1。根据图6的进一步描述,逻辑门514可以进一步包括至少一个压降部件和反相器。

此外,传输门506可以耦合在节点A1和第三节点(下文称为“节点B2”)。与传输门502类似,传输门506也可以包括P沟道晶体管和N沟道晶体管,P沟道晶体管和N沟道晶体管分别具有P沟道门极端子和N沟道门极端子。与传输门502不同,传输门506的P沟道门极端子可以耦合至反相时钟信号CPB,且传输门506的N沟道门极端子可以连接至时钟脉冲CP。

更进一步,锁存器508可以耦合在节点B2和第四节点(下文称为“节点A2/Q”)之间。与锁存器504类似,锁存器508可以包括第三逻辑门(例如,反相器512)和第四逻辑门(例如,逻辑门516)。反相器512的输入端子可以耦合至节点B2,并且反相器512的输出端子可以耦合至节点A2/Q,而逻辑门516的输入端子可以耦合至节点A2/Q,且逻辑门516的输出端子可以耦合至节点B2。如图6中所示,与逻辑门514类似,逻辑门516可以进一步包括至少一个压降部件和反相器。

图6是示出根据本发明的一个实施例的示例触发器电路的一个或多个示例部件的框图。如所描绘,逻辑门514/516可以包括反相器604和至少一个压降部件602。尽管图6中展示了多个压降部件602,但在一些实施例中可以实施一个压降部件602。

反相器604可以包括N沟道晶体管和P沟道晶体管,N沟道晶体管和P沟道晶体管的门极端子可以被连接以形成逻辑门514/516的输入端子。N沟道晶体管和P沟道晶体管的漏极端子可以被连接以形成逻辑门514/516的输出端子。P沟道晶体管的未连接的源极端子可以称为反相器604的电压端子。N沟道晶体管的未连接的漏极或源极端子可以称为反相器604的接地端子。

如所示,至少一个压降部件602可以耦合在电源端子和反相器604的电压端子之间,该电源端子进一步耦合至输入高电压值(例如,电源电压“V

如图6中进一步所示,至少一个压降部件602中的每个部件可以P沟道晶体管或N沟道晶体管的形式实施(例如,图6中的U1、U2、U3和U4)。P沟道或N沟道晶体管的门极端子可以连接至其漏极或源极端子。

图7是示出根据本发明的一个实施例的另一种示例触发器电路的框图。如所描绘,示例触发器电路700中的逻辑门714/716中的每一个可以包括P沟道晶体管和N沟道晶体管。

更详细地,逻辑门714可以包括反相器718、P沟道晶体管730和N沟道晶体管732。反相器718的输入端子可以耦合至节点A1,且反相器718的输出端子可以耦合至节点B1。

P沟道晶体管730的门极端子可以连接至其漏极端子或源极端子。类似地,N沟道晶体管732的门极端子可以连接至其漏极端子或源极端子。P沟道晶体管730可以耦合在V

与逻辑门714类似,逻辑门716可以包括反相器720、P沟道晶体管734和N沟道晶体管736。反相器720的输入端子可以耦合至节点A2,并且反相器720的输出端子可以耦合至节点B2。

P沟道晶体管734的门极端子可以连接至其漏极端子或源极端子。类似地,N沟道晶体管736的门极端子可以连接至其漏极端子或源极端子。P沟道晶体管734可以耦合在V

图8是示出图5或图7的示例触发器电路在时域中的信号的时序图。

在时间点T1之前,数据输入端子D处的数据值为高,且时钟信号为低。因此,传输门702处于闭合状态,且节点B1处的数据值为高。在时间点T1,时钟信号从低升到高,且因此传输门702处于打开状态。节点B1处的电压应当保持相同,直到时钟信号CK从高下降到低,即,传输门702再次处于闭合状态。然而,当数据输入端子D处的数据值在时间点T2从高降到低时,且由于传输门702处的泄漏,如果未在锁存器704中提供反馈结构,则电压将已经降到低。在该示例中,传输门702处的泄漏仍然可能出现,但是逻辑门714可以在节点B1处提供高数据值以防止节点B1处的电压降到低。

更详细地,因为包括P沟道晶体管730和N沟道晶体管732,因此当节点A1处的数据值为低时,反相器718的N沟道晶体管等效于打开状态。在非限制性示例中,P沟道晶体管730/734和反相器718/720的阈值电压值(下文称为“V

此外,当时钟信号CK在时间点T3从高降到低时,传输门702当前处于闭合状态;节点B1处的数据值等于低输入数据值;节点A1处的电压为高;传输门706处于打开状态。由于传输门706处的泄漏,电压会升到高。因为包括P沟道晶体管734和N沟道晶体管736,反相器720的P沟道晶体管由于节点A2/Q处的高电压而基本处于打开状态。因此,传输门706、反相器720中的N沟道晶体管和N沟道晶体管736可以被视为按顺序连接。类似地,因为传输门706的电阻通常远大于两个N沟道晶体管相结合的电阻,因此节点B2处的电压可以接近零,即,接地点处的电压。因此,防止了节点B2处的数据值在时间点T3升到高。

将图5或图7的示例触发器电路与图1中的传统触发器结构相比较,似乎传统结构可以提供更稳定的输出信号。然而,因为反馈可能太强且提供的电压太高来写入新值,因此传统结构中的锁存器(即,锁存器120或锁存器122)需要被断开,而断开锁存器所需要的传输门因为增加了时钟树负载而可能是功耗的。

因此,图1中的传统结构可能导致比图5或图7的示例触发器电路更高的总功率。

提供先前的描述以使得本领域技术人员能够实践本文描述的各个方面。对这些方面的各种修改对于本领域技术人员将是显而易见的,并且本文限定的一般原理可以被应用于其他方面。因此,权利要求并不旨在局限于本文所展示的方面,而是应被赋予与语言权利要求相一致的全部范围,其中,除非特别说明,否则以单数形式提及元件并不旨在表示“一个且唯一一个”,而是表示“一个或多个”。除非另有特别说明,否则术语“一些”指一个或多个。本领域普通技术人员已知或之后知道的本文描述的各个方面的元件的所有结构或功能性的等同物,均通过引用明确地纳入本文,并且旨在由权利要求包含。而且,无论权利要求中是否明确记载了本文所公开的内容,这些公开都未旨在献给公众。除非使用短语“作为……的手段”来明确记载权利要求要素,否则该要素不应当被解释为手段加功能。

此外,术语“或”旨在表示包括的“或”而非排他的“或”。即,除非特别说明或从上下文明确得知,否则短语“X使用A或B”旨在表示任何自然包括的排列。即,以下任一情形都满足短语“X使用A或B”:X使用A;X使用B;或X使用A和B二者。另外,除非特别说明或从上下文明确得知指向单数形式,否则本申请或所附权利要求所使用的冠词“一(a)”和“一种(an)”一般应当被解释为表示“一个或多个”。