译码方法、装置及设备

文献发布时间:2023-06-19 09:36:59

技术领域

本申请涉及通信技术领域,尤其涉及一种译码方法、装置及设备。

背景技术

在通信技术领域,通信设备(例如终端设备、基站等)可以通过极化码(Polar码)的方式进行信道编码和译码。

在现有技术中,在通过极化码进行译码时,可以采用置信度传播(BeliefPropagation,BP)译码算法进行译码,其中一种BP译码算法基于BP迭代图,通过置换来得到多种Tanner图,在多种Tanner图上进行迭代得到译码结果,然而,在上述BP译码算法中,迭代次数较多,导致译码时延较大。

发明内容

本申请提供一种译码方法、装置及设备,降低了译码时延。

第一方面,本申请实施例提供一种译码方法,该方法可以包括:获取N个对数似然比LLR,根据K个信息比特所在比特位的可靠度,在K个信息比特中确定M个待分裂比特,根据N个LLR、M个待分裂比特、预设极大值和预设极小值,确定至少两条译码路径,并在至少两条译码路径中确定译码结果。其中,N个LLR为根据接收到的数据确定得到的,接收到的数据对应N个待译码比特,N个待译码比特中包括K个信息比特,N为大于或等于1的整数,K为正整数,1≤K≤N;M为小于或等于K的正整数。

在上述过程中,先获取N个LLR,并在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到完整的译码路径,并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

在一种可能的实施方式中,可以通过如下可行的实现方式根据N个LLR、M个待分裂比特、预设极大值和预设极小值,确定至少两条译码路径,并在至少两条译码路径中确定译码结果:通过N个LLR,初始化译码网络中的每个变量节点的LLR,译码网络中包括m+1层变量节点,每层变量节点包括N个变量节点,N=2

在上述过程中,在获取得到N个LLR之后,根据该N个LLR初始化译码网络中各变量节点的LLR,根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并校验初始译码路径,若对该初始译码路径校验成功,则确定得到译码结果。若对初始译码路径校验失败,则在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到两条完整的译码路径,并对得到的路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

在一种可能的实施方式中,可以通过如下可行的实现方式将译码网络中待分裂比特对应的第一层变量节点向右传递的LLR分别更新为预设极大值和预设极小值,通过译码网络得到至少两条译码路径,并在至少两条译码路径中确定译码结果:

执行LLR更新步骤,LLR更新步骤包括:将译码网络中第s个待分裂比特对应的第一层变量节点的向右传递的LLR分别更新为预设极大值和预设极小值,初始时,s为1;

执行译码路径确定步骤,译码路径确定步骤包括:根据已存在的L

执行译码结果确定步骤,译码结果确定步骤包括:判断L

重复执行LLR更新步骤、译码路径确定步骤和译码结果确定步骤,直至判断L

在上述过程中,先对一个待分裂比特进行分裂,得到L

在一种可能的实施方式中,可以通过如下可行的实现方式根据已存在的L

在上述过程中,可以使得确定得到的译码路径的个数L

在一种可能的实施方式中,根据已存在的L

在一种可能的实施方式中,在消息传递规则中,在译码网络的一个BP译码单元中,第一变量节点接收到的向左传递的信息与第二变量节点向右传递的信息无关;

其中,一个译码单元中包括变量节点V

在一种可能的实施方式中,消息传递规则如公式一:

其中,L

在上述过程中,向左传递至变量节点V

在一种可能的实施方式中,可以通过如下可行的实现方式判断L

在上述过程中,当CRC长度大于或等于第一阈值时,通过CRC校验即可准确的判断是否存在正确的译码路径,当CRC长度小于或等于第二阈值时,通过CRC校验以及CMP的取值,可以准确的判断是否存在正确的译码路径。

在一种可能的实施方式中,

其中,LLR

在一种可能的实施方式中,根据K个信息比特所在比特位的可靠度,在K个信息比特中确定M个待分裂比特,包括:确定M的大小;按照K个信息比特所在比特位的可靠度从高到低的顺序,对K个信息比特进行排序;将排序后的K个信息比特中的最后M个信息比特确定为M个待分裂比特。

在上述过程中,确定得到的M个待分裂比特为所在比特位的可靠度最低的M个信息比特,即,M个待分裂比特为译码最可能出错的信息比特,使得对M个待分裂比特进行分裂即可确定正确的译码路径,无需对所有的信息比特进行分裂,使得译码效率较高。

在一种可能的实施方式中,M为

第二方面,本申请实施例提供一种译码装置,包括获取模块、第一确定模块和第二确定模块,其中,

所述获取模块用于,获取N个对数似然比LLR,所述N个LLR为根据接收到的数据确定得到的,所述接收到的数据对应N个待译码比特,所述N个待译码比特中包括K个信息比特,所述N为大于或等于1的整数,所述K为正整数,1≤K≤N;

所述第一确定模块用于,根据所述K个信息比特所在比特位的可靠度,在所述K个信息比特中确定M个待分裂比特,所述M为小于或等于所述K的正整数;

所述第二确定模块用于,根据所述N个LLR、所述M个待分裂比特、预设极大值和预设极小值,确定所述至少两条译码路径,并在所述至少两条译码路径中确定译码结果。

在一种可能的实施方式中,所述第二确定模块具体用于:

通过所述N个LLR,初始化译码网络中的每个变量节点的LLR,所述译码网络中包括m+1层变量节点,每层变量节点包括N个变量节点,N=2

根据初始化后的所述译码网络中第一层变量节点的LLR确定初始译码路径,并判断所述初始译码路径是否为正确的译码路径;

在确定所述初始译码路径不是正确的译码路径时,将所述译码网络中所述待分裂比特对应的第一层变量节点向右传递的LLR分别更新为所述预设极大值和所述预设极小值,并通过所述译码网络得到至少两条译码路径。

在一种可能的实施方式中,所述第二确定模块具体用于:

执行LLR更新步骤,所述LLR更新步骤包括:将所述译码网络中第s个待分裂比特对应的第一层变量节点的向右传递的LLR分别更新为所述预设极大值和所述预设极小值,初始时,所述s为1;

执行译码路径确定步骤,所述译码路径确定步骤包括:根据已存在的L

执行译码结果确定步骤,所述译码结果确定步骤包括:判断所述L

重复执行所述LLR更新步骤、所述译码路径确定步骤和所述译码结果确定步骤,直至判断所述L

在一种可能的实施方式中,所述第二确定模块具体用于:

根据所述已存在的L

若2L

若2L

在一种可能的实施方式中,所述第二确定模块具体用于:

按照预设的消息传递规则,在所述译码网络中,分别根据已存在的L

按照预设的消息传递规则,在所述译码网络中,分别根据已存在的L

在一种可能的实施方式中,在所述消息传递规则中,在所述译码网络的一个BP译码单元中,第一变量节点接收到的向左传递的信息与第二变量节点向右传递的信息无关;

其中,一个译码单元中包括变量节点V

在一种可能的实施方式中,所述消息传递规则如公式一所述:

其中,L

在一种可能的实施方式中,所述第二确定模块具体用于:

在循环冗余校验CRC长度大于或等于第一阈值时,若对所述L

在CRC长度小于或等于第二阈值时,若对所述L

在一种可能的实施方式中,

其中,LLR

在一种可能的实施方式中,所述第一确定模块具体用于:

确定所述M的大小;

按照所述K个信息比特所在比特位的可靠度从高到低的顺序,对所述K个信息比特进行排序;

将排序后的所述K个信息比特中的最后M个信息比特确定为所述M个待分裂比特。

在一种可能的实施方式中,所述M为

第三方面,本申请实施例提供一种译码装置,包括:存储器、处理器以及计算机程序,所述计算机程序存储在所述存储器中,所述处理器运行所述计算机程序执行如权利要求1-11任一项所述的译码方法。

第四方面,本申请实施例提供一种译码装置,包括输入接口和逻辑电路,其中,

所述输入接口用于,获取N个对数似然比LLR,所述N个LLR为根据接收到的数据确定得到的,所述接收到的数据对应N个待译码比特,所述N个待译码比特中包括K个信息比特,所述N为大于或等于1的整数,所述K为正整数,1≤K≤N;

所述逻辑电路用于,根据所述K个信息比特所在比特位的可靠度,在所述K个信息比特中确定M个待分裂比特,所述M为小于或等于所述K的正整数;根据所述N个LLR、所述M个待分裂比特、预设极大值和预设极小值,确定所述至少两条译码路径,并在所述至少两条译码路径中确定译码结果。

在一种可能的实施方式中,所述逻辑电路还用于执行上述第一方面任一项所述的译码方法。

第五方面,本申请实施例提供一种存储介质,所述存储介质包括计算机程序,所述计算机程序用于实现如第一方面任一项所述的译码方法。

第六方面,本申请实施例提供一种芯片或者集成电路,包括:存储器和处理器;

所述存储器,用于存储程序指令,有时还用于存储中间数据;

所述处理器,用于调用所述存储器中存储的所述程序指令以实现如上所述的译码方法。

第七方面,本申请实施例提供一种程序产品,所述程序产品包括计算机程序,所述计算机程序存储在存储介质中,所述计算机程序用于实现上述的译码方法。

本申请实施例提供的译码方法、装置及设备,获取N个LLR,根据K个信息比特所在比特位的可靠度,在K个信息比特中确定M个待分裂比特,根据N个LLR、M个待分裂比特、预设极大值和预设极小值,确定至少两条译码路径,并在至少两条译码路径中确定译码结果。在上述过程中,先获取N个LLR,并在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到完整的译码路径,并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

附图说明

图1为本申请实施例提供的通信系统的架构图;

图2为本申请实施例提供的信道传输流程图;

图3为本申请实施例提供的BP译码网络的示意图;

图4为本申请实施例提供的译码单元的示意图;

图5为本申请实施例提供的一种译码方法的流程示意图;

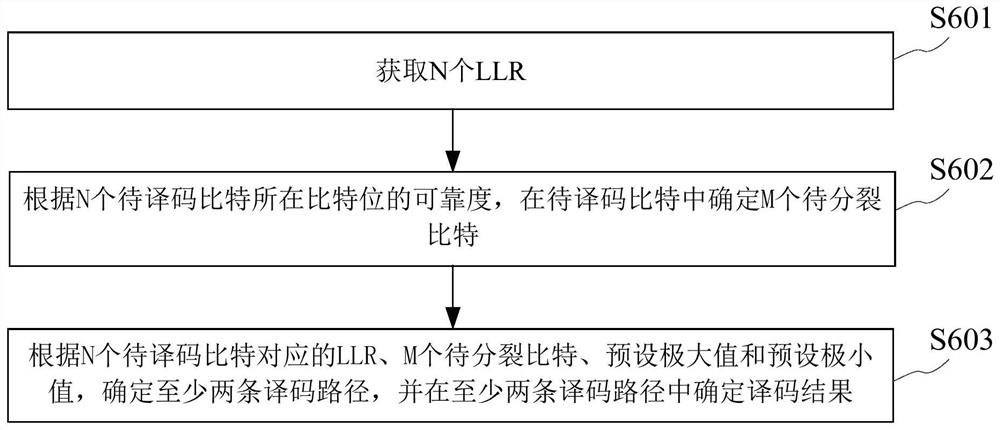

图6为本申请实施例提供的另一种译码方法的流程示意图;

图7为申请提供的一种仿真示意图;

图8为申请提供的另一种仿真示意图;

图9为本申请实施例提供的一种译码装置的结构示意图;

图10为本申请实施例提供的译码装置的硬件结构示意图;

图11为本申请实施例提供的另一种译码装置的结构示意图。

具体实施方式

本申请实施例可以应用于各种采用Polar编码的领域,例如:数据存储领域、光网络通信领域,无线通信领域等等。其中,本申请实施例提及的无线通信系统包括但不限于:窄带物联网系统(Narrow Band-Internet of Things,NB-IoT)、全球移动通信系统(GlobalSystem for Mobile Communications,GSM)、增强型数据速率GSM演进系统(Enhanced Datarate for GSM Evolution,EDGE)、宽带码分多址系统(Wideband Code Division MultipleAccess,WCDMA)、码分多址2000系统(Code Division Multiple Access,CDMA2000)、时分同步码分多址系统(Time Division-Synchronization Code Division Multiple Access,TD-SCDMA),长期演进系统(Long Term Evolution,LTE)以及下一代5G移动通信系统的三大应用场景增强型移动宽带(enhanced Mobile Broad Band,eMBB)、超高可靠与低延迟的通信(Ultra Reliable Low Latency Communication,URLLC)、大规模机器通信(massiveMachine-Type Communications,mMTC)以及未来可能的通信系统。当然,采用Polar编码的领域还可以为其它,本申请对此不作具体限定。

本申请涉及的通信装置主要包括网络设备或者终端设备。本申请中的发送设备可以为网络设备,则接收设备为终端设备。本申请中的发送设备为终端设备,则接收设备为网络设备。

在本申请实施例中,终端设备(terminal device)可以包括但不限于移动台(Mobile Station,MS)、移动终端(Mobile Terminal,MT)、移动电话(Mobile Telephone,MT)、手机(handset)及便携设备(portable equipment)等,该终端设备可以经无线接入网(Radio Access Network,RAN)与一个或多个核心网进行通信。例如,终端设备可以是移动电话(或称为“蜂窝”电话)、具有无线通信功能的计算机等,终端设备还可以是便携式、袖珍式、手持式、计算机内置的或者车载的移动装置或设备。

在本申请实施例中,网络设备可以是LTE系统中的演进型基站(Evolutional NodeB,eNB或eNodeB),或者,网络设备可以是5G通信系统中的gNB或者传输和接收点(transmission reception point,TRP)、微基站等,或者网络设备可以为中继站、接入点、车载设备、可穿戴设备以及未来演进的公共陆地移动网络(Public Land Mobile Network,PLMN)中的网络设备,或者在其他多种技术融合的网络中,或者在其他各种演进网络中的基站等。

例如,网络设备可以为基站(Base Station,BS),基站可以向多个移动台(MobileStation,MS)提供通信服务,基站还可以连接到核心网设备。其中,基站包含基带单元(Baseband Unit,BBU)和远端射频单元(英文:Remote Radio Unit,RRU)。BBU和RRU可以放置在不同的地方,例如:RRU拉远,放置于高话务量的区域,BBU放置于中心机房。BBU和RRU也可以放置在同一机房。BBU和RRU也可以为一个机架下的不同部件。

图1为本申请实施例提供的通信系统的架构图。请参见图1,包括发送设备101和接收设备102。

可选的,当发送设备101为终端设备时,则接收设备102为网络设备。当发送设备101为网络设备时,则接收设备为终端设备。

请参见图1,发送设备101中包括编码器,发送设备101可以通过编码器进行编码,并将编码后的序列通过信道传输至接收设备102。接收设备102中包括译码器,接收设备可以通过译码器对接收到的序列进行译码。

需要说明的是,图1只是以示例的形式示意一种通信系统的架构图,并非对通信系统的架构图的限定。

图2为本申请实施例提供的信道传输流程图。请参见图2,发送设备对发送的数据进行信源编码以及信道编码,编码后的序列经过映射调制之后在信道上传输至接收设备。接收设备可以对接收到的序列进行解映射解调处理、信道译码处理以及信源译码处理以恢复出发送设备发送的数据。

在本申请中,可以采用比特分裂的序列置信度传播(Bit Splitting BeliefPropagation List,BS-BPL)译码算法进行译码,为了便于理解,首先对BP译码网络进行说明。假设码长N=2

可选的,BP译码网络可以被划分为多个译码单元,每个译码单元包括4个变量节点和2个校验节点,该4个变量节点和2个校验节点为可以直接连接的节点。该4个变量节点可以分别记为:变量节点V

下面,以码长N=8为例,对BP译码网络进行说明。

图3为本申请实施例提供的BP译码网络的示意图。请参见图3,BP译码网络中包括4层变量节点和3层校验节点,每层变量节点包括8个变量节点,每层校验节点中包括8个校验节点。其中,图3中的圆圈表示变量节点,方框表示校验节点。

请参见图3,变量节点V

在BP迭代过程中,每个变量节点可以接收左侧节点传递的LLR,向右侧节点传递LLR,接收右侧节点传递的LLR,以及向左侧节点传递LLR。针对一个变量节点,上述LLR均可能不同。为了便于理解和描述,在下文中,将一个变量节点向右传递的LLR、以及该变量节点接收到的其左侧节点向其传递的LLR称为右传信息(R信息),将一个变量节点向左传递的LLR、以及该变量节点接收到的其右侧节点向其传递的LLR称为左传信息(L信息),将BP迭代之后一个变量节点的LLR称为变量节点的LLR。其中,一个节点的LLR、L信息和R信息可能不同。

下面,结合图4,对BP译码网络中的信息传递方式进行说明。

图4为本申请实施例提供的译码单元的示意图。请参见图4,包括变量节点V

请参见图4,变量节点V

校验节点C

其中,g()为运算符号,g()表示两个信息相加。由上述公式二可知,向左传递至变量节点V

在本申请中,在通过BP译码算法进行译码时,根据接收到的数据确定N个LLR,并根据该N个LLR初始化译码网络中各变量节点的LLR,根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并校验初始译码路径,若对该初始译码路径校验成功,则确定得到译码结果。若对初始译码路径校验失败,则在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到完整的译码路径(译码路径的长度为N),并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

下面,通过具体实施例对本申请所示的技术方案进行详细说明。需要说明的是,下面几个实施例可以独立存在,也可以相互结合,对于相同或相似的内容,在不同的实施例中不再重复说明。

图5为本申请实施例提供的一种译码方法的流程示意图。请参见图5,该方法可以包括:

S501、获取N个LLR。

其中,N个LLR为根据接收到的数据确定得到的,接收到的数据对应N个待译码比特,N个待译码比特中包括K个信息比特,N为大于或等于1的整数,K为正整数,1≤K≤N,N=2

可选的,在接收设备接收到数据之后,对数据进行解调得到N个LLR。

其中,接收设备接收到的数据为译码前的数据,即,接收设备接收到的数据为发送设备编码后经过信道传输至接收设备的数据。待译码比特是指译码后的比特,即,接收设备对接收到的数据译码成功后的比特,换句话说,该译码比特是指发送设备进行编码之前的比特。

可选的,当发送设备发送的比特序列包含打孔、截断或者重复时,接收设备接收到的LLR的个数可能大于或者小于2

可选的,接收设备获取到的LLR的个数,与发送设备发送的比特的个数相同。

例如,假设发送设备发送的待发送比特序列中包括2

可选的,接收设备获取到的LLR的个数与待译码比特的个数相同。

例如,假设接收设备获取到2

在接收设备中,译码器将2

S502、通过N个LLR,初始化译码网络中的每个变量节点的LLR。

初始之前,BP译码网络中信息比特对应的变量节点的LLR为零,各冻结比特对应的第一层变量节点的LLR为预设值(例如正无穷大或者负无穷大),其中,BP译码网络中各冻结比特对应的第一层变量节点向右传递的R信息为预设值,且在BP迭代过程中,BP译码网络中各冻结比特对应的第一层变量节点向右传递的R信息均不变。

例如,请参见图3,初始时,BP译码网络中的变量节点V

在初始化时,在BP译码网络中利用该N个LLR进行一次BP迭代,以向BP译码网络中除冻结比特对应的第一层变量节点之外的变量节点赋值(LLR)。可选的,一次BP迭代可以为从右向左的一次消息传递,或者,一次BP迭代可以为从右向左,再从左向右的一次消息传递,或者,一次BP迭代可以为从左向右,再从右向左的一次消息传递等。当然,一次BP迭代还可以为其它形式的消息传递,本申请实施例对此不作具体限定。需要说明的是,为了便于描述,在本申请中,以一次BP迭代包括为从右向左,再从左向右的一次消息传递为例进行说明。

例如,请参见图3,由于码长N为8,因此,在S501中可以获取得到8个LLR,分别记为:LLR1、LLR2、LLR3、……、LLR8,则将LLR1赋值给变量节点V

S503、根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并判断初始译码路径是否为正确的译码路径。

可选的,可以对初始化后的译码网络中的第一层变量节点的LLR进行硬判,以得到初始译码路径。例如,针对任意一个变量节点的LLR,若该LLR的值大于或等于0,则硬判值为0,若LLR的值小于0,则硬判值为1。

例如,请参见图3,假设根据变量节点V

可选的,在循环冗余校验(Cyclic Redundancy Check,CRC)长度大于或等于第一阈值时,若对初始译码路径进行CRC校验成功,则确定初始译码路径为正确的译码路径,则将初始译码路径确定为译码结果。

在CRC长度小于或等于第二阈值时,若对初始译码路径进行CRC校验成功,且码字路径度量(codeword path metric,CMP)最小且收敛时,则确定初始译码路径为正确的译码路径,并将初始译码路径确定为译码结果,CMP用于指示硬判值和LLR值的符合程度。

可选的,CMP可以为如下公式三所示:

其中,LLR

CMP收敛是指,再进行一次或者多次BP迭代,CMP值不变,或者CMP值的变化小于预设门限值。

在确定初始译码路径为正确的译码路径时,则将初始译码路径确定为译码结果,则本次译码结束。则不再执行S504-S515。

在确定初始译码路径不是正确的译码路径时,则继续执行S504-S515。

S504、在对初始译码路径校验失败时,根据K个信息比特所在比特位的可靠度,在K个信息比特中确定M个待分裂比特。

可选的,可以通过如下可行的实现方式确定M个待分裂比特:可以先确定M的大小,按照K个信息比特所在比特位的可靠度从高到低的顺序,对K个信息比特进行排序,将排序后的最后M个信息比特确定为M个待分裂比特。

可以根据待译码比特中信息比特的个数K确定M的大小,例如,M为

可选的,可以通过多种可行的实现方式获取信息比特所在比特位的可靠度。例如,可以通过极化重量(polarization weight,PW)获取信息比特所在比特位的可靠度,或者,可以通过高斯近似的方式获取信息比特所在比特位的可靠度,或者,可以通过查表方式获取信息比特所在比特位的可靠度。

可选的,在确定得到的M个待分裂比特中,待分裂比特按照所在的比特位的序号从小到大的顺序进行排列。例如,假设M个待分裂比特中包括比特u1(比特位的序号为1),u4(比特位的序号为4)和u7(比特位的序号为7),则在该3个待分裂比特的排序顺序为:u1、u4和u7,即,u1为第一个待分裂比特,u4为第二个待分裂比特,u7为第三个待分裂比特。

S505、将译码网络中第s个待分裂比特对应的第一层变量节点向右传递的LLR分别更新为预设极大值。

其中,初始时,s为1,s为小于或等于M的正整数。

其中,预设极大值为一个趋近于无穷大的值,例如,预设极大值可以为10

假设第s个待分裂比特为待译码比特中的第j个比特,则第s个待分裂比特对应的第一层变量节点为V

S506、按照预设的消息传递规则,分别根据已存在的L

可选的,L

例如,当s等于1时,已存在的译码路径数量L

针对任意一条已存在的译码路径,该已存在的译码路径对应的各变量节点的LLR为,确定得到该译码路径时各变量节点的LLR。例如,在经过BP迭代之后,各变量节点的LLR得到了更新,根据更新后的第一层变量节点的LLR可以确定得到一条译码路径,则该一条译码路径对应的各变量节点的LLR为,更新后的各变量节点的LLR。

针对任意一条已存在的译码路径,将第s个待分裂比特对应的第一层变量节点向右传递的R信息设置为预设极大值,该已存在的译码路径对应的其它变量节点的LLR不变,在BP译码网络中进行消息传递(BP迭代),BP迭代之后,各变量节点的LLR发生更新,根据更新后的第一层变量节点的LLR,可以得到一条新的译码路径。对已存在的L

可选的,预设的消息传递规则可以为图2所示的消息传递规则。

可选的,由于按照图2所示的消息传递规则进行消息传递时,译码的稳定性较差。为了提高译码的稳定性,本申请对消息传递规则进行了改变,在本申请的消息传递规则中,在译码网络的一个BP译码单元中,第一变量节点接收到的向左传递的信息与第二变量节点向右传递的信息无关;其中,一个译码单元中包括变量节点V

例如,本申请所示的息传递规则可以如公式一:

其中,L

由上述公式一可知,向左传递至变量节点V

S507、将译码网络中第s个待分裂比特对应的第一层变量节点向右传递的LLR分别更新为预设极小值。

其中,预设极小值为一个趋近于无穷小的值,例如,预设极小值可以为10

S508、按照预设的消息传递规则,分别根据已存在的L

需要说明的是,S507-S508的执行过程可以参见S505-S506的执行过程,此处不再进行赘述。

需要说明的是,通过S505-S508,可以得到2L

S509、判断2L

若是,则执行S510。

若否,则执行S511。

S510、在2L

在S510之后,执行S512。

可选的,可以根据2L

例如,PM可以为如下公式四所示:

其中,PM(i)为第i条译码路径的路径度量值,LLR(1,i)为第1层第i个变量节点的LLR,R(1,i)为第一层第i个变量节点向右传递的R信息,L(1,i)为向第1层第i个节点传递的L信息。sgn()为阶跃函数,sgn()为0或1。

S511、将该2L

在S511之后,执行S512。

S512、判断L

若是,则执行S513。

若否,则执行S514。

可选的,在CRC长度大于第一阈值时,若对L

在CRC长度小于第二阈值时,若对L

可选的,CMP可以如上述公式三所示,此处不再进行赘述。

在上述过程中,先在2L

S513、在L

S514、将S加1,并判断S是否大于M。

若是,则执行S515。

若否,执行S505。

S515、本次译码失败。

由于对M个待分裂比特分裂完成之后,均没有确定得到译码结果,则本次译码失败。

在图5所示的实施例中,在通过BP译码算法进行译码时,获取N个LLR,并根据该N个LLR初始化译码网络中各变量节点的LLR,根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并校验初始译码路径,若对该初始译码路径校验成功,则确定得到译码结果。若对初始译码路径校验失败,则在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到两条完整的译码路径,并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

图6为本申请实施例提供的另一种译码方法的流程示意图。请参见图6,该方法可以包括:

S601、获取N个LLR。

其中,N个LLR为根据接收到的数据确定得到的,接收到的数据对应N个待译码比特,N个待译码比特中包括K个信息比特,N为大于或等于1的整数,K为正整数,1≤K≤N。

需要说明的是,S601的执行过程可以参见S501的执行过程,此处不再进行赘述。

S602、根据K个信息比特所在比特位的可靠度,在K个信息比特中确定M个待分裂比特,M为大于或等于K的正整数。

中,假设接收端根据接收到的信息解调得到8(N=8)个LLR,该8个LLR分别记为:LLR1、LLR2、LLR3、……、LLR8,该8个LLR对应8个待译码比特。再假设K=4,在8个待译码比特需要说明的是,S602的执行过程可以参见S502-S504的执行过程,此处不再进行赘述。

S603、根据N个LLR、M个待分裂比特、预设极大值和预设极小值,确定至少两条译码路径,并在至少两条译码路径中确定译码结果。

需要说明的是,S603的执行过程可以参见S505-S515的执行过程,此处不再进行赘述。

在图6所示的实施例中,在通过BP译码算法进行译码时,获取N个LLR,并根据该N个LLR初始化译码网络中各变量节点的LLR,根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并校验初始译码路径,若对该初始译码路径校验成功,则确定得到译码结果。若对初始译码路径校验失败,则在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到两条完整的译码路径,并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

在上述任意一个实施例的基础上,下面,通过具体示例,对上述方法实施例所示的技术方案进行详细说明。

示例性的,在通信的过程中,第1、2、3、5个比特位上的比特为冻结比特,其它比特位上的比特为信息比特,则BP译码网络可以如图3所示。

请参见图3,初始时,BP译码网络中的变量节点V

判断初始译码路径是否为正确的译码路径(可以参见S503)。在确定初始译码路径为正确的译码路径时,则将初始译码路径确定为译码结果,则本次译码结束。在确定初始译码路径不是正确的译码路径时,则继续执行下述步骤。

在对初始译码路径校验失败时,先确定M的大小,假设确定得到的M等于3,根据每个信息比特所在比特位的可靠度,在K=4个信息比特中确定3个待分裂比特。假设3个待分裂比特分别为待译码比特中的第4、6和7个比特。

在译码路径11对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径11时的LLR)的基础上,将第4个比特对应的第一层中的变量节点V

在译码路径11对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径11时的LLR)的基础上,将第4个比特对应的第一层中的变量节点V

通过上述对第一个待分裂比特进行分裂之后,得到两条译码路径:译码路径21和译码路径22。

假设最大保留路径数L为2,则译码路径21和译码路径22均被保留。

判断译码路径21和译码路径22中是否存在正确的译码路径(可以参见S512)。若是,则将正确的译码路径确定为译码结果,本次译码结束。若否,则继续执行下述步骤。

在译码路径21对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径21时的LLR)的基础上,将第6个比特对应的第一层中的变量节点V

在译码路径21对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径21时的LLR)的基础上,将第6个比特对应的第一层中的变量节点V

在译码路径22对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径22时的LLR)的基础上,将第6个比特对应的第一层中的变量节点V

在译码路径22对应的BP译码网络(该BP译码网络中各变量节点的LLR为确定得到译码路径22时的LLR)的基础上,将第6个比特对应的第一层中的变量节点V

通过上述对第一个待分裂比特进行分裂之后,得到四条译码路径:译码路径31、译码路径32、译码路径33和译码路径34。

由于最大保留路径数L为2,则根据译码路径31、译码路径32、译码路径33和译码路径34的路径度量值,在该4条译码路径中确定2条译码路径。假设确定得到的两条译码路径为译码路径32和译码路径33。

需要说明的是,按照上述对译码路径21和译码路径22的处理方式,对译码路径32和译码路径33进行处理,直至得到译码结果或者译码失败。

在上述过程中,根据接收到的数据确定N个LLR,并根据该N个LLR初始化译码网络中各变量节点的LLR,根据初始化后的译码网络中第一层变量节点的LLR确定初始译码路径,并校验初始译码路径,若对该初始译码路径校验成功,则确定得到译码结果。若对初始译码路径校验失败,则在K个信息比特中确定至少一个待分裂比特,先对一个待分裂比特进行分裂,得到两条完整的译码路径,并对得到的译码路径进行校验,若校验成功则译码成功,若没有校验成功,则继续对其它待分裂比特进行分裂,直至译码成功或者对对所有待分裂比特分裂完成。在上述过程中,每进行一次比特分裂均可以确定得到完整的译码路径,若对得到的译码路径校验成功,则确定得到译码结果,不再对其它比特进行分裂,降低了译码延时。

在上述任意一个实施例的基础上,下面,结合图7-图8所示仿真数据对基于本申请所示的译码方法的时延进行说明。

当本申请译码对应的仿真参数和现有译码对应的仿真参数如表1所示时,通过本申请所示的译码方式与通过现有的译码方式的仿真结果可以如图7所示。

表1

请参见表1,本申请所参考的现有的译码算法为CA-SCL译码算法,本申请所示的译码算法为BS-BPL译码算法。下面,结合图7,对码长N为1024时,不同L(最大路径保留数)下,BS-BPL译码算法与CA-SCL译码算法的性能进行说明。

图7为申请提供的一种仿真示意图。请参见图7,横轴表示信噪比(signal tonoise ratio,SNR),纵轴表示误块率(Block Error Rate,BLER)。其中,BS-BPL2是指译码算法为BS-BPL译码算法,L等于2,CA-SCL2是指译码算法为CA-SCL译码算法,L等于2,依次类推,其它不再进行赘述。

请参见图7,码长N=1024,无论L的取值为多少,BS-BPL译码算法对应的BLER均小于CA-SCL译码算法对应的BLER,即,采用本申请中的BS-BPL译码算法,可以明显的降低译码过程中的误块率,使得译码性能更高。

图8为申请提供的另一种仿真示意图。请参见图8,横轴表示SNR,纵轴表示BLER。请参见图8,码长N=2048,当待分裂比特的数量M越大时,能够纠正错误的BP译码的可能性越大,译码性能越好。其中,CS(500)中的500、CS(650)中的650、以及CS(1024)中的1024是指M,其中,当M=650时的译码性能基本与M=K(1024)时的译码性能一致,可以说明部分节点在BP迭代中仅起到输出功能,对其信息纠正并不能改变其它比特的信息,这也说明了BP迭代过程中存在某些比特的重要性比较低,某些比特的重要性比较高的现象。由图8可知,无论M取值为多少,采用本申请中的BS-BPL译码算法,均可以明显的降低译码过程中的误块率,使得译码性能更高。

下面,结合表3,示意出CA-SCL译码算法与本发明提出的BS-BPL译码算法的时延对比。其中,在表3中,N=2048,K=1024,对于相同的L,CA-SCL译码算法和BS-BPL译码算法的路径排序时延相同,因此,只考虑译码算法本身的时延。两种算法均考虑全并行处理,因此CA-SCL算法对于不同的L时延相同,且不随SNR而改变。从表3中可以看出,本发明提出的BS-BPL算法时延随着信噪比的提升,时延大幅度下降。

表3

图9为本申请实施例提供的一种译码装置的结构示意图。该译码装置10可以设置在终端设备中,也可以设置在网络设备中。请参见图9,译码装置10可以包括获取模块11、第一确定模块12和第二确定模块13,其中,

所述获取模块11用于,获取N个对数似然比LLR,所述N个LLR为根据接收到的数据确定得到的,所述接收到的数据对应N个待译码比特,所述N个待译码比特中包括K个信息比特,所述N为大于或等于1的整数,所述K为正整数,1≤K≤N;

所述第一确定模块12用于,根据所述K个信息比特所在比特位的可靠度,在所述K个信息比特中确定M个待分裂比特,所述M为小于或等于所述K的正整数;

所述第二确定模块13用于,根据所述N个LLR、所述M个待分裂比特、预设极大值和预设极小值,确定所述至少两条译码路径,并在所述至少两条译码路径中确定译码结果。

可选的,获取模块11可以执行图5实施例中的S501,以及图6实施例中的S601。

可选的,第一确定模块12可以执行图5实施例中的S502-S504,以及图6实施例中的S602。

可选的,第二确定模块13可以执行图5实施例中的S505-S515,以及图6实施例中的S603。

需要说明的是,本申请实施例提供的译码装置可以执行上述方法实施例所示的技术方案,其实现原理以及有益效果类似,此处不再进行赘述。

在一种可能的实施方式中,所述第二确定模块13具体用于:

通过所述N个LLR,初始化译码网络中的每个变量节点的LLR,所述译码网络中包括m+1层变量节点,每层变量节点包括N个变量节点,N=2

根据初始化后的所述译码网络中第一层变量节点的LLR确定初始译码路径,并判断所述初始译码路径是否为正确的译码路径;

在确定所述初始译码路径不是正确的译码路径时,将所述译码网络中所述待分裂比特对应的第一层变量节点向右传递的LLR分别更新为所述预设极大值和所述预设极小值,并通过所述译码网络得到至少两条译码路径。

在一种可能的实施方式中,所述第二确定模块13具体用于:

执行LLR更新步骤,所述LLR更新步骤包括:将所述译码网络中第s个待分裂比特对应的第一层变量节点的向右传递的LLR分别更新为所述预设极大值和所述预设极小值,初始时,所述s为1;

执行译码路径确定步骤,所述译码路径确定步骤包括:根据已存在的L

执行译码结果确定步骤,所述译码结果确定步骤包括:判断所述L

重复执行所述LLR更新步骤、所述译码路径确定步骤和所述译码结果确定步骤,直至判断所述L

在一种可能的实施方式中,所述第二确定模块13具体用于:

根据所述已存在的L

若2L

若2L

在一种可能的实施方式中,所述第二确定模块13具体用于:

按照预设的消息传递规则,在所述译码网络中,分别根据已存在的L

按照预设的消息传递规则,在所述译码网络中,分别根据已存在的L

在一种可能的实施方式中,在所述消息传递规则中,在所述译码网络的一个BP译码单元中,第一变量节点接收到的向左传递的信息与第二变量节点向右传递的信息无关;

其中,一个译码单元中包括变量节点V

在一种可能的实施方式中,所述消息传递规则如公式一所述:

其中,L

在一种可能的实施方式中,所述第二确定模块13具体用于:

在循环冗余校验CRC长度大于或等于第一阈值时,若对所述L

在CRC长度小于或等于第二阈值时,若对所述L

在一种可能的实施方式中,

其中,LLR

在一种可能的实施方式中,所述第一确定模块12具体用于:

确定所述M的大小;

按照所述K个信息比特所在比特位的可靠度从高到低的顺序,对所述K个信息比特进行排序;

将排序后的所述K个信息比特中的最后M个信息比特确定为所述M个待分裂比特。

在一种可能的实施方式中,所述M为

需要说明的是,本申请实施例提供的译码装置可以执行上述方法实施例所示的技术方案,其实现原理以及有益效果类似,此处不再进行赘述。

图10为本申请实施例提供的译码装置的硬件结构示意图。请参见图10,该译码装置20可以包括:处理器21以及存储器22,其中,

存储器22,用于存储计算机程序,还可以用于存储中间数据;

处理器21,用于执行存储器存储的计算机程序,以实现上述译码方法中的各个步骤。具体可以参见前面方法实施例中的相关描述。

可选地,存储器22既可以是独立的,也可以跟处理器21集成在一起。在有些实施方式中,存储器22甚至还可以位于译码装置20之外。

当所述存储器22是独立于处理器21之外的器件时,所述译码装置20还可以包括总线23,用于连接所述存储器22和处理器21。

可选的,译码装置20还可以进一步包括接收器。例如,接收器用于获取数据,或者获取N个LLR。

本实施例提供的解调译码装置20可以为终端设备,或者也以为网络设备,可用于执行上述的解调译码方法,其实现方式和技术效果类似,本实施例此处不再赘述。

图11为本申请实施例提供的另一种译码装置的结构示意图。请参见图11,该译码装置30可以包括输入接口31和逻辑电路32,其中,

所述输入接口31用于,获取N个对数似然比LLR,所述N个LLR为根据接收到的数据确定得到的,所述接收到的数据对应N个待译码比特,所述N个待译码比特中包括K个信息比特,所述N为大于或等于1的整数,所述K为正整数,1≤K≤N;

所述逻辑电路32用于,根据所述K个信息比特所在比特位的可靠度,在所述K个信息比特中确定M个待分裂比特,所述M为小于或等于所述K的正整数;根据所述N个LLR、所述M个待分裂比特、预设极大值和预设极小值,确定所述至少两条译码路径,并在所述至少两条译码路径中确定译码结果。

可选的,输入接口31可以具有图9实施例中的获取模块11的功能。逻辑电路32可以具有图9实施例中的第一确定模块12和第二确定模块13的功能。

可选的,输入接口31可以具有图10实施例中的接收器的功能。逻辑电路32可以具有图10实施例中的处理器21的功能。逻辑电路32还可以执行译码方法中其它的步骤。

可选的,译码装置30还可以包括输出接口。例如,输出接口可以输出译码结果。

本申请实施例提供的译码装置30可以执行上述方法实施例所示的技术方案,其实现原理以及有益效果类似此处不再进行赘述。

本申请实施例还提供一种存储介质,所述存储介质包括计算机程序,所述计算机程序用于实现如上所述的译码方法。

本申请实施例还提供一种芯片或者集成电路,包括:存储器和处理器;

所述存储器,用于存储程序指令,还可以用于存储中间数据;

所述处理器,用于调用所述存储器中存储的所述程序指令以实现如上所述的译码方法。

可选的,存储器可以是独立的,也可以跟处理器集成在一起。在有些实施方式中,存储器还可以位于所述芯片或者集成电路之外。

本申请实施例还提供一种程序产品,所述程序产品包括计算机程序,所述计算机程序存储在存储介质中,所述计算机程序用于实现上述的解码方法。

结合本发明实施例公开内容所描述的方法或者算法的步骤可以硬件的方式来实现,也可以是由处理器执行软件指令的方式来实现。软件指令可以由相应的软件模块组成,软件模块可以被存放于随机存取存储器(Random Access Memory,RAM)、闪存、只读存储器(Read Only Memory,ROM)、可擦除可编程只读存储器(Erasable Programmable ROM,EPROM)、电可擦可编程只读存储器(Electrically EPROM,EEPROM)、寄存器、硬盘、移动硬盘、只读光盘(CD-ROM)或者本领域熟知的任何其它形式的存储介质中。一种示例性的存储介质耦合至处理器,从而使处理器能够从该存储介质读取信息,且可向该存储介质写入信息。当然,存储介质也可以是处理器的组成部分。处理器和存储介质可以位于ASIC中。另外,该ASIC可以位于基站或终端中。当然,处理器和存储介质也可以作为分立组件存在于接收设备中。

应理解,上述处理器可以是中央处理单元(英文:Central Processing Unit,简称:CPU),还可以是其他通用处理器、数字信号处理器(英文:Digital Signal Processor,简称:DSP)、专用集成电路(英文:Application Specific Integrated Circuit,简称:ASIC)等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。结合发明所公开的方法的步骤可以直接体现为硬件处理器执行完成,或者用处理器中的硬件及软件模块组合执行完成。

存储器可能包含高速RAM存储器,也可能还包括非易失性存储NVM,例如至少一个磁盘存储器,还可以为U盘、移动硬盘、只读存储器、磁盘或光盘等。

总线可以是工业标准体系结构(Industry Standard Architecture,ISA)总线、外部设备互连(Peripheral Component,PCI)总线或扩展工业标准体系结构(ExtendedIndustry Standard Architecture,EISA)总线等。总线可以分为地址总线、数据总线、控制总线等。为便于表示,本申请附图中的总线并不限定仅有一根总线或一种类型的总线。

上述存储介质可以是由任何类型的易失性或非易失性存储设备或者它们的组合实现,如静态随机存取存储器(SRAM),电可擦除可编程只读存储器(EEPROM),可擦除可编程只读存储器(EPROM),可编程只读存储器(PROM),只读存储器(ROM),磁存储器,快闪存储器,磁盘或光盘。存储介质可以是通用或专用计算机能够存取的任何可用介质。

本申请中,“至少一个”是指一个或者多个,“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,A和/或B,可以表示:单独存在A,同时存在A和B,单独存在B的情况,其中A,B可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“以下至少一项(个)”或其类似表达,是指的这些项中的任意组合,包括单项(个)或复数项(个)的任意组合。例如,a,b,或c中的至少一项(个),可以表示:a,b,c,a-b,a-c,b-c,或a-b-c,其中a,b,c可以是单个,也可以是多个。

本领域技术人员应该可以意识到,在上述一个或多个示例中,本发明实施例所描述的功能可以用硬件、软件、固件或它们的任意组合来实现。当使用软件实现时,可以将这些功能存储在计算机可读介质中或者作为计算机可读介质上的一个或多个指令或代码进行传输。计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。

在本发明所提供的几个实施例中,应该理解到,所揭露的设备和方法,可以通过其它的方式实现。例如,以上所描述的设备实施例仅仅是示意性的,例如,所述模块的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个模块可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或模块的间接耦合或通信连接,可以是电性,机械或其它的形式。

所述作为分离部件说明的模块可以是或者也可以不是物理上分开的,作为模块显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。

另外,在本发明各个实施例中的各功能模块可以集成在一个处理单元中,也可以是各个模块单独物理存在,也可以两个或两个以上模块集成在一个单元中。上述模块成的单元既可以采用硬件的形式实现,也可以采用硬件加软件功能单元的形式实现。