半导体器件及其制造方法

文献发布时间:2023-06-19 11:39:06

技术领域

本公开涉及半导体器件及其制造方法。

背景技术

集成电路(IC)通常被设计用于实现各种器件,包括例如晶体管、电阻器、电容器等。这些器件通常被设计为使用导电迹线的连接来形成电路。日益密集的IC在速度、功能和成本方面产生了益处,但也导致了越来越困难的设计和制造问题。

发明内容

根据本公开的一个实施例,提供了一种半导体器件,包括:衬底;第一栅极结构、第二栅极结构和第三栅极结构,所述第一栅极结构、所述第二栅极结构和所述第三栅极结构位于所述衬底上方并沿着第一方向布置,其中,所述第一栅极结构、所述第二栅极结构和所述第三栅极结构在不同于所述第一方向的第二方向上延伸,并且所述第二栅极结构位于所述第一栅极结构和所述第三栅极结构之间;以及第一源极/漏极区域,所述第一源极/漏极区域位于所述第一栅极结构和所述第三栅极结构之间,并且位于所述第二栅极结构的一个端部处。

根据本公开的另一实施例,提供了一种半导体器件,包括:第一半导体鳍部和第二半导体鳍部;第一栅极结构,所述第一栅极结构跨所述第一半导体鳍部和所述第二半导体鳍部;第二栅极结构,所述第二栅极结构跨所述第二半导体鳍部并与所述第一半导体鳍部间隔开;以及第一外延结构和第二外延结构,所述第一外延结构和所述第二外延结构位于所述第一半导体鳍部上方并位于所述第一栅极结构的相反侧,其中,所述第一外延结构和所述第二外延结构具有不同长度。

根据本公开的又一实施例,提供了一种用于制造半导体器件的方法,包括:在衬底上方形成有源区域;在所述衬底上方并跨所述有源区域形成栅极结构,其中,所述栅极结构具有基本上恒定的间距;去除所述栅极结构中的至少一个栅极结构的一部分以暴露所述有源区域的一部分;以及至少在所述有源区域的暴露部分上形成第一外延结构。

附图说明

在结合附图进行阅读时,可以通过下面的具体实施方式最佳地理解本公开的各个方面。要注意的是,根据行业的标准惯例,各种特征不是按比例绘制的。事实上,为了讨论的清楚起见,各种特征的尺寸可能被任意地增大或减小。

图1A至图6D示出了根据本公开的一些实施例的在制造半导体器件的各个阶段中的方法。

图7A是根据一些实施例的各个阶段中的半导体器件的顶视图。

图7B是沿着图7A的线B-B截取的截面视图。

图7C是沿着图7A的线C-C截取的截面视图。

图7D是沿着图7A的线D-D截取的截面视图。

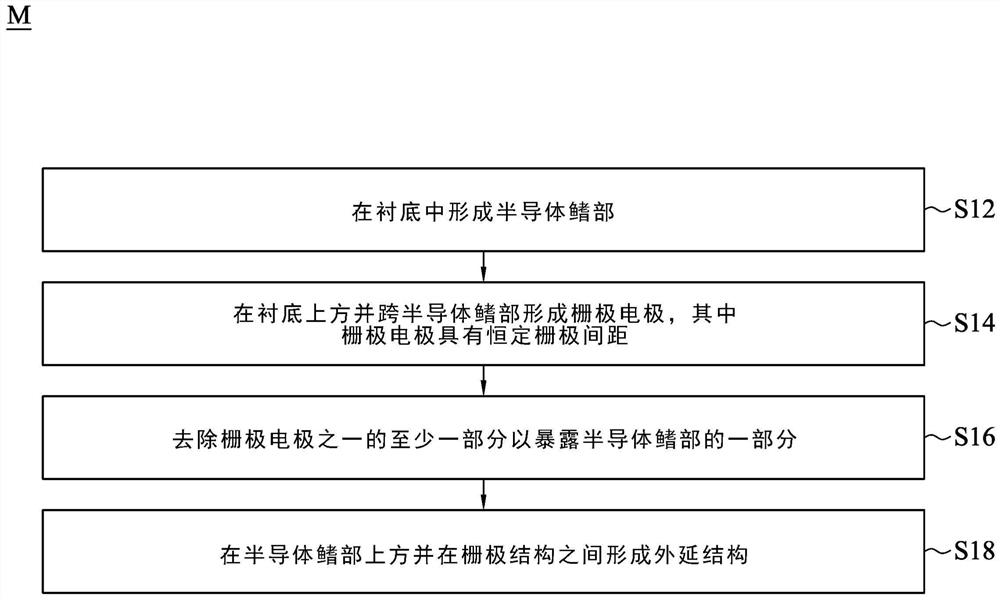

图8是根据本公开的一些实施例的用于形成半导体器件的方法的流程图。

图9是根据一些实施例的各个阶段中的半导体器件的顶视图。

图10是根据本公开的一些实施例的集成电路的布局图。

图11是根据本公开的一些实施例的集成电路的布局图。

图12是根据本公开的一些实施例的集成电路的布局图。

图13是根据本公开的一些实施例的集成电路的布局图。

图14是根据本公开的一些实施例的集成电路的布局图。

图15是根据本公开的一些实施例的生成IC布局图的方法的流程图。

图16是根据本公开的一些实施例的IC器件设计系统的框图。

图17是根据本公开的一些实施例的IC制造系统1700和与其相关联的IC制造流程的框图。

具体实施方式

以下公开内容提供了许多不同的实施例或示例,以用于实现所提供的主题的不同特征。下面描述了组件和布置的具体示例以简化本公开。当然,这些只是示例,并不旨在要进行限制。例如,在下面的描述中,在第二特征上方或在第二特征上形成第一特征可以包括第一特征和第二特征直接接触形成的实施例,并且还可以包括可以在第一特征和第二特征之间形成附加特征的实施例,使得第一特征和第二特征可以不直接接触。此外,本公开可以在各种示例中重复附图标记和/或字母。这种重复是为了简单和清晰的目的,其本身并不指示所讨论的各种实施例和/或配置之间的关系。

此外,为了便于描述,可以在本文中使用空间相关术语,例如“下面”、“下方”、“下”、“上方”、“上”等,来描述如图中所示的一个元素或特征与另一个(或多个)元素或特征的关系。除了图中所描绘的定向之外,空间相关术语还旨在包含正在使用或操作的器件的不同定向。装置可以以其他方式定向(旋转90度或在其他定向上),并且本文使用的空间相对描述符也可以被相应地解释。

如本文所使用的,“大约”、“约”、“近似”或“基本上”通常表示在给定值或范围的20%以内、10%以内或5%以内。本文给出的数值是近似值,这表示在没有明确说明的情况下可以推断出术语“约”、“大约”、“近似”或“基本上”。

鳍部可以通过任何合适的方法进行图案化。例如,可以使用一个或多个光刻工艺(包括双图案化或多图案化工艺)来对鳍部进行图案化。一般来说,双图案化或多图案化工艺将光刻和自对准工艺结合起来,允许创建具有例如比使用单个直接光刻工艺以其他方式可获得的间距更小的间距的图案。例如,在一个实施例中,在衬底上方形成牺牲层,并使用光刻工艺对该牺牲层进行图案化。间隔体是使用自对准工艺沿着图案牺牲层形成的。然后去除牺牲层,并随后使用剩余的间隔体对鳍部进行图案化。

本公开的一些实施例涉及具有切割栅极结构的半导体器件。切割栅极结构(包括去除虚设栅极)提高了布线资源的利用率。去除虚设栅极也降低了半导体器件的功耗和寄生电容。下面,在在体半导体衬底上形成具有多个鳍部的FinFET晶体管的上下文中讨论了这些实施例。

图1A至图6D示出了根据本公开的一些实施例的在制造半导体器件的各个阶段中的方法。贯穿各个视图和说明性实施例,相同的附图标记用于指定相同的元素。图1A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图,图1B是沿着图1A的线B-B截取的截面视图,图1C是沿着图1A的线C-C截取的截面视图,图1D是沿着图1A的线D-D截取的截面视图。衬底110被提供。衬底110包括从衬底110的顶表面突出的第一半导体鳍部112和第二半导体鳍部114。在一些实施例中,第一半导体鳍部112和第二半导体鳍部114包括硅。要注意的是,图1A-1D中的第一半导体鳍部112和第二半导体鳍部114的数量是说明性的,不应限制本公开所要求保护的范围。

在一些实施例中,衬底110可以是半导体材料,并且可以包括例如梯度层或埋置氧化物。在一些实施例中,衬底110包括可以未掺杂或掺杂的体硅(例如p型、n型或其组合)。可以使用适合于半导体器件形成的其他材料。其他材料(例如锗、石英、蓝宝石和玻璃)可以替代地用于衬底110。替代地,硅衬底110可以是绝缘体上半导体(SOI)衬底或多层结构(例如在体硅层上形成的硅锗层)的有源层。

第一半导体鳍部112和第二半导体鳍部114可以例如通过使用光刻技术对衬底110进行图案化和蚀刻来形成。在一些实施例中,在衬底110上方沉积光致抗蚀剂材料层(未示出)。光致抗蚀剂材料层根据所需图案(在这种情况下为第一半导体鳍部112和第二半导体鳍部114)被辐射(曝光),并被显影以去除光致抗蚀剂材料的一部分。剩余的光致抗蚀剂材料保护下层材料不受后续工艺步骤(例如蚀刻)的影响。应注意的是,其他掩模(例如氧化物或氮化硅掩模)也可用于蚀刻工艺。

在一些其他实施例中,第一半导体鳍部112和第二半导体鳍部114可以外延地生长。例如,下层材料的暴露部分(例如衬底110的暴露部分)可用于外延工艺以形成第一半导体鳍部112和第二半导体鳍部114。掩模可用于在外延生长工艺中控制第一半导体鳍部112和第二半导体鳍部114的形状。

在衬底110中形成多个隔离结构120,例如浅沟隔离(STI),以将各个器件分隔开。隔离结构120的形成可以包括在衬底110中蚀刻沟槽并由诸如氧化硅、氮化硅或氧化硅之类的绝缘体材料填充沟槽。经填充的沟槽可以具有多层结构,例如用氮化硅填充沟槽的热氧化物内衬层。在一些实施例中,隔离结构120可以使用以下工艺顺序来创建:生长衬垫氧化物、形成低压化学气相沉积(LPCVD)氮化物层、使用光致抗蚀剂和掩模来图案化STI开口、在衬底110中蚀刻沟槽(以形成半导体鳍部112和114)、可选地生长热氧化物沟槽内衬以改进沟道界面、用氧化物填充沟槽、使用化学机械平坦化(CMP)去除多余的氧化物、以及使热氧化物沟槽内衬和氧化物凹陷以形成隔离结构120,使得半导体鳍部112和114的顶部部分从隔离结构120的顶表面突出。

图2A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图,图2B是沿着图2A的线B-B截取的截面视图,图2C是沿着图2A的线C-C截取的截面视图,图2D是沿着图2A的线D-D截取的截面视图。界面层130被共形地形成以覆盖半导体鳍部112和114。为了清楚起见,界面层130在图2B-2D中被示出,而在图2A中被省略。在一些实施例中,界面层130可以包括二氧化硅、氮化硅、高k电介质材料或其他合适的材料。在各种示例中,界面层130可以通过热氧化工艺、ALD工艺、CVD工艺、负压CVD(SACVD)工艺、可流动CVD工艺、PVD工艺或其他合适的工艺来沉积。举例来说,界面层130可以用于防止后续工艺(例如,随后形成栅极结构)对半导体鳍部112和114造成损害。

随后,在界面层130上方形成栅极堆叠140a、140b、140c、140d和140e。栅极堆叠140a-140e中的每一个包括:栅极结构142a(或142b或142c或142d或142e)、形成在栅极结构142a(或142b或142c或142d或142e)上方的衬垫层144和形成在衬垫层144上方的硬掩模层146。在一些实施例中,可以在界面层130上方形成栅极层(未示出),并且在栅极层上方形成衬垫层144和硬掩模层146。然后,使用衬垫层144和硬掩模层146作为掩模来对栅极层进行图案化,以形成栅极结构142a-142e。如此,栅极结构142a、142b、142c、142d、142e、衬垫层144和硬掩模层146被称为虚设栅极堆叠140a、140b、140c、140d和140e。在一些实施例中,栅极结构142a-142e可以由多晶硅(poly-Si)、多晶硅锗(poly-SiGe)或其他合适的材料制成。衬垫层144可以由二氧化硅或其他合适的材料制成,硬掩模层146可以由氮化硅或其他合适的材料制成。如果采用先栅极(gate-first)技术,则栅极结构142a-142e和界面层130用作栅极电极和栅极电介质层。

在图2A中,栅极堆叠140a-140e具有基本上相同的间距。即,栅极堆叠140a和栅极堆叠140b之间的间距P1与栅极堆叠140b和栅极堆叠140c之间的间距P2基本上相同,栅极堆叠140b和栅极堆叠140c之间的间距P2与栅极堆叠140c和栅极堆叠140d之间的间距P3基本上相同,并且栅极堆叠140c和栅极堆叠140d之间的间距P3与栅极堆叠140d和栅极堆叠140e之间的间距P4基本上相同。在一些实施例中,间距P1可以在约20nm到约100nm的范围内。

图3A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图,图3B是沿着图3A的线B-B截取的截面视图,图3C是沿着图3A的线C-C截取的截面视图,图3D是沿着图3A的线D-D截取的截面视图。去除了栅极堆叠140a-140e的至少一部分。例如,在图3A-3D中,去除了栅极堆叠140c(参见图2A),使得半导体鳍部112和114d的最初由栅极堆叠140c覆盖的部分被暴露。在一些实施例中,在栅极堆叠140a-140e上方形成掩模层,并且对掩模层进行图案化以暴露栅极堆叠140c。掩模层可以由光致抗蚀剂或硬掩模(例如氮化硅层)形成。随后,通过例如蚀刻工艺去除暴露的栅极堆叠140c。

图4A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图,图4B是沿着图4A的线B-B截取的截面视图,图4C是沿着图4A的线C-C截取的截面视图,图4D是沿着图4A的线D-D截取的截面视图。去除了界面层130未被栅极堆叠140a、140b、140d和140e覆盖的部分,以暴露半导体鳍部112和114的部分。然后,间隔体结构150至少形成在栅极堆叠140和界面层130的相反侧。间隔体结构150可以包括密封间隔体和主间隔体(未示出)。间隔体结构150包括一种或多种电介质材料,例如氧化硅、氮化硅、氮氧化硅、SiCN、SiC

图5A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图。图5B是沿着图5A的线B-B截取的截面视图,图5C是沿着图5A的线C-C截取的截面视图,图5D是沿着图5A的线D-D截取的截面视图。凹槽102分别形成在半导体鳍部112和114的未被栅极堆叠140a、140b、140d和140e和间隔体结构150覆盖的部分中。栅极堆叠140a、140b、140d和140e和间隔体结构150在形成凹槽中用作蚀刻掩模。蚀刻工艺包括干法蚀刻工艺、湿法蚀刻工艺或其组合。然后通过例如执行选择性生长工艺在凹槽中形成外延结构160a-160e和165a-165e。外延结构160a-160e形成于半导体鳍部112中,并且外延结构165a-165e形成于半导体鳍部114中。

外延结构160a-160e和165a-165e是通过外延生长半导体材料形成的。半导体材料包括:单元素半导体材料,例如锗(Ge)或硅(Si);复合物半导体材料,例如砷化镓(GaAs)或砷化铝镓(AlGaAs);或半导体合金,例如硅锗(SiGe)或磷砷化镓(GaAsP)等。外延结构160a-160e和165a-165e可以如图5D所示彼此分隔开或合并在一起。在一些实施例中,外延结构160a-160e和165a-165e是源极/漏极外延结构。在一些实施例中,在需要N型器件的情况下,外延结构160a-160e(或165a-165e)可以包括外延生长的硅磷(SiP)或硅碳(SiC)。在一些实施例中,在需要P型器件的情况下,外延结构165a-165e(或160a-160e)可以包括外延生长的硅锗(SiGe)。在半导体鳍部112和114上方形成的外延结构160a-160e和165a-165e具有不同的导电类型,并且可以在不同的工艺中形成。外延工艺包括CVD沉积技术(例如,气相外延(VPE)和/或超高真空CVD(UHV-CVD))、分子束外延和/或其他合适的工艺。在一些实施例中,省略了外延结构160a-160e和165a-165e的形成。

在图6A中,外延结构160a和165a形成在栅极堆叠140a的一侧,外延结构160b和165b形成在栅极堆叠140a的另一侧并在栅极堆叠140a和140b之间,外延结构160c和165c形成在栅极堆叠140b和140d之间,外延结构160d和165d形成在栅极堆叠140e的一侧并在栅极堆叠140d和140e之间,外延结构160e和165e形成在栅极堆叠140e的另一侧。外延结构160b、160d、165b和165d中的每一个可以具有长度L1,并且外延结构160c和165c中的每一个的长度L2可以大于长度L1。

外延结构160a-160e和165a-165e可以称为对应晶体管的源极/漏极区域。外延结构160a和160b以及栅极结构142a形成晶体管T1,外延结构160b和160c以及栅极结构142b形成晶体管T2,外延结构160c和160d以及栅极结构142d形成晶体管T3,外延结构160d和160e以及栅极结构142e形成晶体管T4,外延结构165a和165b以及栅极结构142a形成晶体管T5,外延结构165b和165c以及栅极结构142b形成晶体管T6,外延结构165c和165d以及栅极结构142d形成晶体管T7,以及外延结构165d和165e以及栅极结构142e形成晶体管T8。

外延结构160b可以是晶体管T2的源极,外延结构160c可以是晶体管T2的漏极。外延结构160d可以是晶体管T3的源极,外延结构160c可以是晶体管T3的漏极。也就是说,晶体管T2和T3共享相同的漏极(即,外延结构160c)。此外,外延结构165b可以是晶体管T6的源极,外延结构165c可以是晶体管T6的漏极。外延结构165d可以是晶体管T7的源极,外延结构165c可以是晶体管T7的漏极。也就是说,晶体管T6和T7共享相同的漏极(即,外延结构165c)。

栅极结构142a和142b具有间距P1,栅极结构142d和142e具有与间距P1基本上相同的间距P4,栅极结构142b和142d具有大于间距P1的间距P5。例如,栅极结构142b和142d的间距P5基本上是栅极结构142a和142b的间距P1的两倍。

随后,层间电介质(ILD)170形成在外延结构160a-160e和165a-165e、栅极堆叠140a、140b、140d和140e、间隔体结构150和隔离结构120上方。ILD 170可以通过化学气相沉积(CVD)、高密度等离子体CVD、旋涂、溅射或其他合适的方法形成。在一些实施例中,ILD170包括氧化硅。在一些其他实施例中,ILD 170可以包括氮氧化硅、氮化硅或低k材料。在一些实施例中,预先在外延结构160a-160e和165a-165e、栅极堆叠140a、140b、140d和140e、间隔体结构150和隔离结构120上方共形地形成接触蚀刻停止层(CESL),并且在CESL上方形成ILD 170。然后,执行平坦化工艺,例如化学机械平坦化(CMP)工艺,以使ILD170平坦化从而暴露栅极电极142a、142b、142d和142e。

图6A是根据一些实施例的用于在各个阶段中制造半导体器件的方法的顶视图。图6B是沿着图6A的线B-B截取的截面视图,图6C是沿着图6A的线C-C截取的截面视图,图6D是沿着图6A的线D-D截取的截面视图。多个源极/漏极开口177形成在ILD 170中,其中源极/漏极开口177暴露了一些外延结构(例如,在这种情况下为外延结构160b、160d、165b和165d)。随后,在开口177中填充导电材料,并且去除导电材料的多余部分以形成接触部190和195。接触部190和195可以由钨、铝、铜或其他合适的材料制成。

接触部190形成在外延结构160b和165b上方,使得外延结构160b通过接触部190电连接到外延结构165b。接触部195形成在外延结构160d和165d上方,使得外延结构160d通过接触部195电连接到外延结构165d。要注意的是,接触部190和195的位置不限于图6A所示的位置。接触部的位置基于不同的电路设计来确定。

在图2A中,栅极堆叠140c是虚设栅极堆叠,它不是半导体器件中的功能栅极。如果没有去除栅极堆叠140c,则将在栅极堆叠140c上方形成附加的导电迹线,以连接晶体管T2和T3的漏极(参见图5A)。此外,另一通孔可以连接到栅极结构142c以使栅极结构142c接地。然而,在图6A中,栅极堆叠140c被去除,晶体管T2和T3的漏极(即外延结构160c)被直接连接。通过这种配置,省略了附加的导电迹线和通孔,有效地节省了紧凑布局结构中的金属布线资源。此外,在没有接地虚设栅极的情况下,降低了栅极结构142b和142d之间的寄生电容,并且降低了虚设栅极接地的功耗。例如,当去除一个或多个N型和P型虚设栅极时,在一些实施例中半导体器件的速度增加约1.61%,并且在一些实施例中节省约1.7%的功率。当去除一个或多个N型虚设栅极时,在一些实施例中半导体器件的速度增加约0.32%,并且在一些实施例中节省约6.55%的功率。

在一些实施例中,采用替换栅极(RPG)工艺方案。在RPG工艺方案中,虚设多晶硅栅极(在这种情况下为例如栅极电极142a、142b、142d、142e(参见图6A-6D))是预先形成的,并随后被金属栅极替换。图7A是根据一些实施例的不同阶段中的半导体器件的顶视图,图7B是沿着图7A的线B-B截取的截面视图,图7C是沿着图7A的线C-C截取的截面视图,图7D是沿着图7A的线D-D截取的截面视图。在一些实施例中,去除了栅极结构142a、142b、142d和142e以形成开口152,其中间隔体结构150作为它们的侧壁。在一些其他实施例中,也去除了界面层130(参见图6B和6C)。替代地,在一些实施例中,去除了栅极结构142a、142b、142d和142e,而保留界面层130。栅极结构142a、142b、142d和142e(以及界面层130)可以通过干法蚀刻、湿法蚀刻、或干法蚀刻和湿法蚀刻的组合来去除。

然后多个栅极结构180形成在开口152中。栅极结构180跨(crossover)半导体鳍部112和/或114。栅极结构180可以被称为功能栅极结构。在一些实施例中,栅极结构180中的每一个包括栅极电介质层182和位于栅极电介质层182上方的栅极电极184。

栅极电介质层182共形地形成在开口152中。栅极电介质层182位于半导体鳍部112和/或114上方。栅极电介质层182可以是介电常数(k)高于SiO

栅极电极184可以包括(一个或多个)功函数金属层185、(一个或多个)帽盖层、(一个或多个)填充层186、和/或金属栅极堆叠中所需的其他合适的层。功函数金属层185可以包括n型和/或p型功函数金属。示例性n型功函数金属包括Ti、Ag、TaAl、TaAlC、TiAlN、TaC、TaCN、TaSiN、Mn、Zr、其他合适的n型功函数材料或其组合。示例性p型功函数金属包括TiN、TaN、Ru、Mo、Al、WN、ZrSi

图8是根据本公开的一些实施例的用于形成半导体器件的方法M的流程图。尽管方法M被示出和/或描述为一系列动作或事件,但是应当理解,该方法不限于所示出的顺序或动作。因此,在一些实施例中,可以按照与图示不同的顺序执行动作,并且/或者可以同时执行动作。此外,在一些实施例中,所示出的动作或事件可以被细分为多个动作或事件,这些动作或事件可以在单独的时间执行或与其他动作或子动作同时执行。在一些实施例中,可以省略一些所示出的动作或事件,并且可以包括其他未示出的动作或事件。

在方框S12,在衬底中形成半导体鳍部。图1A-1D示出了与方框S12中的动作相对应的一些实施例的顶视图和截面视图。在方框S14,在衬底上方并跨半导体鳍部形成栅极电极,其中栅极电极具有恒定间距。图2A-2D示出了与方框S14中的动作相对应的一些实施例的顶视图和截面视图。在方框S16,去除栅极电极之一的至少一部分以暴露半导体鳍部的一部分。图3A-3D示出了与方框S16中的动作相对应的一些实施例的顶视图和截面视图。在方框S18,在半导体鳍部上方并在栅极结构之间形成外延结构。图4A-4D示出了与方框S18中的动作相对应的一些实施例的顶视图和截面视图。

图9是根据一些实施例的不同阶段中的半导体器件200的顶视图。图9和图6A中半导体器件之间的区别涉及栅极结构的配置。在图9中,半导体器件200包括多个栅极结构和多个外延结构。OD部分对应于外延结构,G部分对应于栅极结构。栅极结构沿着x方向布置,相邻栅极结构的间距不同。例如,相邻栅极结构242a和242b具有间距P21,相邻栅极结构242b和242c具有间距P22,相邻栅极结构242c和242d具有间距P23,相邻栅极结构242d和242e具有间距P24,相邻栅极结构242f和242g具有间距P25,相邻栅极结构242g和242h具有间距P26,并且相邻栅极结构242h和242i具有间距P27。间距P21(或P25或P26或P27)基本上是间距P22(或P23)的两倍,间距P24基本上是间距P22(或P23)的三倍。即,相邻栅极结构的每个间距是间距P22(或P23)的n倍,其中n是正整数。此外,栅极结构具有基本上相同的宽度。

外延结构沿着x方向延伸,并且外延结构的长度可能不同。例如,外延结构260a和260b位于栅极结构242b的相反侧,并且外延结构260a和260b和栅极结构242b形成晶体管T21。外延结构260a的长度L21与外延结构260b的长度L22不同。例如,长度L21基本上是长度L22的两倍。此外,外延结构260b和260c位于栅极结构242c的相反侧,并且外延结构260b和260c和栅极结构242c形成晶体管T22。外延结构260b的长度L22与外延结构260c的长度L23基本上相同。此外,外延结构260c和260d位于栅极结构242d的相反侧,并且外延结构260c和260d和栅极结构242d形成晶体管T23。外延结构260c的长度L23与外延结构260d的长度L24不同。例如,长度L24基本上是长度L23的三倍。也就是说,外延结构的每个长度是长度L22(或L23)的m倍,其中m是正整数。图9中的半导体器件200的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似。因此,下文中将不再重复对这方面的描述。

图6A(或图7A或图9)中的结构可应用于各种集成电路/电路单元以增加布线灵活性。图10是根据本公开的一些实施例的集成电路300的布局图。集成电路300是SDFQ(或SDFSNQ)电路。集成电路300的布局图包括多个有源区域、多个栅极结构和多个导电特征。OD部分对应于有源区域(例如,外延结构),G部分对应于栅极结构,MP部分对应于导电特征,并且标签302对应于集成电路300的单元边界。导电特征形成在栅极结构上方。有源区域沿着x方向延伸,栅极结构沿着y方向延伸。

栅极结构的部分被去除。例如,去除栅极结构342a的一部分以形成沿着y方向延伸和布置的栅极结构342aa和342ab。外延结构360a和360b和栅极结构342b形成晶体管T31。外延结构360a插入在栅极结构342aa和342ab之间。也就是说,外延结构360a位于栅极结构342aa和342ab的端部之间,并且栅极结构342aa、外延结构360a和栅极结构342ab沿着y方向依次布置。此外,外延结构360a的长度L31基本上是外延结构360b的长度L32的两倍。

外延结构360j和360k位于栅极结构342ab的相反侧。外延结构360j和360k具有基本上相同的长度,其与外延结构360b的长度L32基本上相同。外延结构360j(或360k)和外延结构360a沿着y方向布置。外延结构360a的边缘361a基本上与外延结构360j的边缘361j对准。

此外,在图10中,栅极结构342e的一部分被去除。图10中的栅极结构具有恒定/统一的间距。例如,栅极结构342c和342d具有间距P31,栅极结构342d和342f具有基本上是间距P31两倍的间距P32,栅极结构342f和342g具有基本上与间距P31相同的间距P33。外延结构360c和360d和栅极结构342d形成晶体管T32,外延结构360d和360e和栅极结构342f形成晶体管T33。也就是说,晶体管T32和T33共享公用源极/漏极(即,在这种情况下为外延结构360d)。外延结构360d位于栅极结构342e的一个端部343e处并且位于栅极结构342d和342f之间。外延结构360d的长度L34基本上是外延结构360c的长度L33的两倍,外延结构360d的长度L34基本上是外延结构360e的长度L35的两倍。此外,长度L34大于栅极结构342d和342e的间距(或栅极结构342e和342f的间距),该间距与栅极结构342c和342d的间距P31基本上相同。此外,栅极结构342e的端部343e位于隔离结构正上方。

此外,在图10中,栅极结构342f的一部分被去除。栅极结构342e和342f具有基本上是间距P31两倍的间距P34。外延结构360f和360g和栅极结构342e形成晶体管T34,外延结构360g和360h和栅极结构342g形成晶体管T35。也就是说,晶体管T34和T35共享公用源极/漏极(即,在这种情况下为外延结构360g)。外延结构360g位于栅极结构342f的一个端部处并且位于栅极结构342e和342g之间。外延结构360g的长度L37基本上是外延结构360f的长度L36的两倍,外延结构360g的长度L37基本上是外延结构360h的长度L38的两倍。此外,外延结构360i位于栅极结构342f和342g之间,并且外延结构360g和360i沿着y方向布置。外延结构360i的长度L39小于外延结构360g的长度L37,例如,基本上是外延结构360g的长度L37的一半。图10中的集成电路300的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似,因此下文中将不再重复对这方面的描述。

图11是根据本公开的一些实施例的集成电路400的布局图。集成电路400是MB2SDFQ电路。集成电路400的布局图包括多个有源区域、多个栅极结构和多个导电特征。OD部分对应于有源区域(例如,外延结构),G部分对应于栅极结构,MP部分对应于导电特征,标签402对应于集成电路400的单元边界。有源区域沿着x方向延伸,栅极结构沿着y方向延伸。

栅极结构的部分被去除。例如,栅极结构442c的一部分被去除。图11中的栅极结构具有恒定/统一的间距。例如,栅极结构442a和442b具有间距P41,栅极结构342b和342d具有基本上是间距P41两倍的间距P42,栅极结构442d和442e具有基本上与间距P41相同的间距P43。外延结构460a和460b和栅极结构442b形成晶体管T41,外延结构460b和460c和栅极结构442d形成晶体管T42。也就是说,晶体管T41和T42共享公用源极/漏极(即,在这种情况下为外延结构460b)。外延结构460b位于栅极结构442c的一个端部处并且位于栅极结构442b和442d之间。外延结构460b的长度L42基本上是外延结构460a的长度L41的两倍,外延结构460b的长度L42基本上是外延结构460c的长度L43的两倍。

此外,在图11中,去除栅极结构442b的一部分,并且在栅极结构442b的一个端部处形成外延结构460d。外延结构460d和460e和栅极结构442c形成晶体管T43,并且外延结构460d的长度基本上是外延结构460e的长度的两倍。此外,去除栅极结构442g的一部分,并且在栅极结构442g的一个端部处并且在栅极结构442f和442h之间形成外延结构460f。去除栅极结构442h的一部分,并且在栅极结构442h的一端处并且在栅极结构442g和442i之间形成外延结构460g。图11中的集成电路400的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似,因此下文中将不再重复对这方面的描述。

图12是根据本公开的一些实施例的集成电路500的布局图。集成电路500是MB2SRLSDFQD1电路。集成电路500的布局图包括多个有源区域、多个栅极结构和多个导电特征。OD部分对应于有源区域(例如,外延结构),G部分对应于栅极结构,MP部分对应于导电特征,标签502对应于集成电路500的单元边界。有源区域沿着x方向延伸,栅极结构沿着y方向延伸。

栅极结构的部分被去除。例如,栅极结构542c的一部分被去除。图12中的栅极结构具有恒定/统一的间距。例如,栅极结构542a和542b具有间距P51,栅极结构542b和542d具有基本上是间距P51两倍的间距P52,栅极结构542d和542e具有基本上与间距P51相同的间距P53。外延结构560a和560b和栅极结构542b形成晶体管T51,外延结构560b和560c和栅极结构542d形成晶体管T52。也就是说,晶体管T51和T52共享公用源极/漏极(即,在这种情况下为外延结构560b)。外延结构560b位于栅极结构542c的一个端部处并且位于栅极结构542b和542d之间。外延结构560b的长度L52基本上是外延结构560a的长度L51的两倍,外延结构560b的长度L52基本上是外延结构560c的长度L53的两倍。

此外,在图12中,去除栅极结构542b的一部分,并且在栅极结构542b的一个端部处形成外延结构560d。外延结构560d和560e和栅极结构542c形成晶体管T53,并且外延结构560d的长度基本上是外延结构560e的两倍。此外,去除栅极结构542g的一部分,并且在栅极结构542g的一个端部处并且在栅极结构542f和542h之间形成外延结构560f。去除栅极结构542h的一部分,并且在栅极结构542h的一个端部处并且在栅极结构542g和542i之间形成外延结构560g。图12中的集成电路500的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似,因此下文中将不再重复对这方面的描述。

图13是根据本公开的一些实施例的集成电路600的布局图。集成电路600是SDFQD1电路。集成电路600的布局图包括多个有源区域、多个栅极结构和多个导电特征。OD部分对应于有源区域(例如,外延结构),G部分对应于栅极结构,MP部分对应于导电特征,标签602对应于集成电路600的单元边界。有源区域沿着x方向延伸,栅极结构沿着y方向延伸。

栅极结构的部分被去除。例如,栅极结构642c的一部分被去除。图13中的栅极结构具有恒定/统一的间距。例如,栅极结构642a和642b具有间距P61,栅极结构642b和642d具有基本上是间距P61两倍的间距P62,栅极结构642d和642e具有基本上与间距P61相同的间距P63。外延结构660a和660b和栅极结构642b形成晶体管T61,外延结构660b和660c和栅极结构642d形成晶体管T62。也就是说,晶体管T61和T62共享公用源极/漏极(即,在这种情况下为外延结构660b)。外延结构660b位于栅极结构642c的一个端部处并且位于栅极结构642b和642d之间。外延结构660b的长度L62基本上是外延结构660a的长度L61的两倍,外延结构660b的长度L62基本上是外延结构660c的长度L63的两倍。

此外,在图13中,去除栅极结构642d的一部分,并且在栅极结构642d的一个端部处形成外延结构660d。外延结构660d和660e和栅极结构642c形成晶体管T63,并且外延结构660d的长度基本上是外延结构660e的两倍。图13中的集成电路600的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似,因此下文中将不再重复对这方面的描述。

图14是根据本公开的一些实施例的集成电路700的布局图。集成电路700是SDFSNQD1电路。集成电路700的布局图包括多个有源区域、多个栅极结构和多个导电特征。OD部分对应于有源区域(例如,外延结构),G部分对应于栅极结构,MP部分对应于导电特征,标签702对应于集成电路700的单元边界。有源区域沿着x方向延伸,栅极结构沿着y方向延伸。

栅极结构的部分被去除。例如,栅极结构742c的一部分被去除。图14中的栅极结构具有恒定/统一的间距。例如,栅极结构742a和742b具有间距P71,栅极结构742b和742d具有基本上是间距P71的两倍的间距P72,栅极结构742d和742e具有基本上与间距P71相同的间距P73。外延结构760a和760b和栅极结构742b形成晶体管T71,外延结构760b和760c和栅极结构742d形成晶体管T72。也就是说,晶体管T71和T72共享公用源极/漏极(即,在这种情况下为外延结构760b)。外延结构760b位于栅极结构742c的一个端部处并且位于栅极结构742b和742d之间。外延结构760b的长度L72基本上是外延结构760a的长度L71的两倍,外延结构760b的长度L72基本上是外延结构760c的长度L73的两倍。此外,栅极结构742e的一部分也被去除。

此外,在图14中,去除栅极结构742g的一部分,并且在栅极结构742g的一个端部处形成外延结构760d。外延结构760d和760e和栅极结构742f形成晶体管T73,并且外延结构760d的长度基本上是外延结构760e的两倍。图14中的集成电路700的其他相关结构细节与图6A-6D(或图7A-7D)中的半导体器件相同或相似,因此下文中将不再重复对这方面的描述。

图15是根据本公开的一些实施例的生成IC布局图的方法1500的流程图。在一些实施例中,生成IC布局图包括生成基于生成的IC布局图制造的上面针对图9-14讨论的布局图200、300、400、500、600或700中的一个。在一些实施例中,生成IC布局图是操作IC制造系统作为制造IC器件(例如,存储器电路、逻辑器件、处理器件、信号处理电路等)的一部分。

在一些实施例中,方法1500的部分或全部由计算机的处理器执行。在一些实施例中,方法1500的部分或全部由下面针对图16讨论的IC器件设计系统1600的处理器1602执行。方法1500的部分或全部操作能够作为在设计室(例如下面针对图17讨论的设计室1720)中执行的设计程序的一部分来执行。

在一些实施例中,方法1500的操作按照图15所示的顺序执行。在一些实施例中,方法1500的操作同时地和/或以图15所示顺序以外的顺序执行。在一些实施例中,在执行方法1500的一个或多个操作之前、之间、期间和/或之后执行一个或多个操作。

在操作1510,在衬底上布置第一有源区域和第二有源区域,其中第一有源区域和第二有源区域具有不同的长度。布置第一有源区域和第二有源区域包括布置与上面针对图5A-7D讨论的外延结构160c和160b相对应的有源区域。在各种实施例中,布置有源区域包括:布置上面针对图5A-7D讨论的外延结构165c和165b;布置上面针对图9讨论的外延结构260a和260b;布置上面针对图10讨论的外延结构360a和360b;布置上面针对图11讨论的外延结构460b和460c;布置上面针对图12讨论的外延结构560b和560c;布置上面针对图13讨论的外延结构660b和660c;以及布置上面针对图14讨论的外延结构760b和760c。

在操作1520,在第一有源区域和第二有源区域上方布置第一栅极结构、第二栅极结构和第三栅极结构,其中第一有源区域位于第一栅极结构和第二栅极结构之间,第二有源区域位于第二栅极结构和第三栅极结构之间。布置第一栅极结构、第二栅极结构和第三栅极结构包括布置与上面针对图5A-7D讨论的栅极结构142b、142d和142e相对应的第一栅极结构、第二栅极结构和第三栅极结构。在各种实施例中,布置第一栅极结构、第二栅极结构和第三栅极结构包括:布置上面针对图9讨论的栅极结构242a、242b和242c;布置上面针对图9讨论的栅极结构242e、242d和242c;布置上面针对图10讨论的栅极结构342d、342f和342g;布置上面针对图11讨论的栅极结构442b、442d和442e;布置上面针对图12讨论的栅极结构542b、542d和542e;布置上面针对图13讨论的栅极结构642b、642d和642e;以及布置上面针对图14讨论的栅极结构742b、742d和742e。

在操作1530,在一些实施例中,生成IC布局图。IC布局图包括如上面针对操作1510-1520讨论地布置的第一栅极结构、第二栅极结构、源极/漏极区域和主体区域。在一些实施例中,生成IC布局图包括将IC布局图存储在存储设备中。在各种实施例中,将IC布局图存储在存储设备中包括将IC布局图存储在非易失性、计算机可读存储器或单元库(例如数据库)中和/或包括通过网络存储IC布局图。在一些实施例中,将IC布局图存储在存储设备中包括通过下面针对图16讨论的IC器件设计系统1600的网络1614存储IC布局图。

在操作1540,在一些实施例中,基于IC布局图制造一个或多个半导体掩模中的至少一个或半导体器件层中的至少一个组件。下面参照图17讨论制造一个或多个半导体掩模或半导体器件的层中的至少一个组件。

在操作1550,在一些实施例中,基于IC布局图执行一个或多个制造操作。在一些实施例中,执行一个或多个制造操作包括基于IC布局图执行一个或多个光刻曝光。下面针对图17讨论基于IC布局图执行一个或多个制造操作,例如一个或多个光刻曝光。

通过执行方法1500的部分或全部操作,生成了例如上面针对图1A-7D和图9-14讨论的IC布局图和对应的半导体器件(其中各种实施例包括切割栅极结构),从而改进半导体器件的金属布线资源。

图16是根据本公开的一些实施例的IC器件设计系统1600的框图。根据一些实施例,如上面针对图15所讨论的方法1500的一个或多个操作可以使用IC器件设计系统1600来实现。

在一些实施例中,IC器件设计系统1600是包括硬件处理器1602和非暂态计算机可读存储介质1604的计算设备。除其他以外,非暂态计算机可读存储介质1604是用计算机程序代码(即一组可执行指令1606)进行编码的或存储计算机程序代码。由硬件处理器1602执行指令1606表示(至少部分地)IC器件设计系统,该IC器件设计系统实现了上面针对图15的方法1500(下文中所述的过程和/或方法)的一部分或全部。

处理器1602经由总线1608电耦合到非暂态计算机可读存储介质1604。处理器1602还通过总线1608电耦合到I/O接口1610。网络接口1612还经由总线1608电连接到处理器1602。网络接口1612连接到网络1614,使得处理器1602和非暂时的计算机可读存储介质1604能够经由网络1614连接到外部元件。处理器1602被配置为执行编码在非暂态计算机可读存储介质1604中的指令1606,以使得IC器件设计系统1600可用于执行部分或全部所述处理和/或方法。在一个或多个实施例中,处理器1602是中央处理单元(CPU)、多处理器、分布式处理系统、专用IC(ASIC)和/或合适的处理单元。

在一个或多个实施例中,非暂态计算机可读存储介质1604是电子、磁性、光学、电磁、红外和/或半导体系统(或装置或设备)。例如,非暂态计算机可读存储介质1604包括半导体或固态存储器、磁带、可移动计算机磁盘、随机存取存储器(RAM)、只读存储器(ROM)、刚性磁盘和/或光盘。在使用光盘的一个或多个实施例中,非暂态计算机可读存储介质1604包括光盘只读存储器(CD-ROM)、光盘读/写(CD-R/W)和/或数字视频光盘(DVD)。

在一个或多个实施例中,非暂态计算机可读存储介质1604存储被配置为使IC器件设计系统1600可用于执行部分或全部所述过程和/或方法的指令1606。在一个或多个实施例中,非暂态计算机可读存储介质1604还存储有利于执行部分或全部所述过程和/或方法的信息。在各种实施例中,非暂态计算机可读存储介质1604存储至少一个IC布局设计图1620或至少一个设计规范1622之一或其组合,每一个都在上面针对图1A-7D和9-14讨论。。

IC器件设计系统1600包括I/O接口1610。I/O接口1610耦合到外部电路。在各种实施例中,I/O接口1610包括键盘、按键、鼠标、轨迹球、轨迹板、显示器、触摸屏和/或光标方向键之一或其组合,以用于向处理器1602传送信息和命令和/或从处理器1602传送信息和命令。

IC器件设计系统1600还包括耦合到处理器1602的网络接口1612。网络接口1612允许IC器件设计系统1600与一个或多个其他计算机系统所连接的网络1614通信。网络接口1612包括:无线网络接口,例如蓝牙、WIFI、WIMAX、GPRS或WCDMA;或有线网络接口,例如以太网、USB或IEEE-1364。在一个或多个实施例中,在两个或更多个系统1600中实现所述过程和/或方法的部分或全部。

IC器件设计系统1600被配置为通过I/O接口1610接收信息。通过I/O接口1610接收的信息包括以下项之一或其组合:至少一个设计规则指令、至少一组准则、至少一个设计规则、至少一个DRM和/或由于由处理器1602处理的其他参数。信息经由总线1608传输到处理器1602。IC器件设计系统1600被配置为通过I/O接口1610发送和/或接收与用户接口相关的信息。

在一些实施例中,所述过程和/或方法的部分或全部被实现为用于由处理器执行的独立软件应用。在一些实施例中,所述过程和/或方法的部分或全部被实现为作为附加软件应用的一部分的软件应用。在一些实施例中,所述过程和/或方法的部分或全部被实现为软件应用程序的插件。在一些实施例中,所述过程和/或方法中的至少一种被实现为作为EDA工具的一部分的软件应用。在一些实施例中,IC布局图是使用诸如可从CADENCEDESIGNSYSTEMS公司得到的VIRTUOSO

在一些实施例中,这些过程被实现为存储在非暂态计算机可读记录介质中的程序的功能。非暂态计算机可读记录介质的示例包括但不限于外部/可移动和/或内部/内置存储或存储器单元,例如光盘(例如DVD)、磁盘(例如硬盘)、半导体存储器(例如ROM、RAM、存储卡)等中的一项或多项。

通过可用于实现图15的方法1500的一个或多个操作,IC器件设计系统1600和非暂态计算机可读存储介质(例如,非暂态计算机可读存储介质1604)使上面针对方法1500和图15讨论的益处得以实现。

图17是根据本公开的一些实施例的IC制造系统1700的框图和与其相关联的IC制造流程。在一些实施例中,基于布局设计,使用IC制造系统1700制造以下项中的至少一者:(A)一个或多个半导体掩模或(B)半导体IC层中的至少一个组件。

在图17中,IC制造系统1700包括实体,例如设计室1720、掩模室1730和IC制造商/制造者(“fab”)1750等,它们在与制造IC器件1760相关的设计、开发和制造周期和/或服务中交互。系统1700中的实体通过通信网络连接。在一些实施例中,通信网络是单个网络。在一些实施例中,通信网络是各种不同的网络,例如内联网和互联网。通信网络包括有线和/或无线通信信道。每个实体与一个或多个其他实体交互,并且向一个或多个其他实体提供服务和/或从一个或多个其他实体接收服务。在一些实施例中,设计室1720、掩模室1730和IC制造商/制造者1750中的两者或更多者由单个较大公司拥有。在一些实施例中,设计室1720、掩模室1730和IC制造商/制造者1750中的两者或更多者在公共设施中共存并使用公共资源。

设计室(或设计团队)1720基于图15的方法1500以及上面针对图1A-7D和图9-14的讨论生成IC设计布局图(或设计)1722。IC设计布局图1722包括各种几何图案,它们对应于构成要制造的集成电路器件1760的各个组件的金属、氧化物或半导体层的图案。各个层组合形成各种特性。例如,IC设计布局图1722的一部分包括各种IC特征,例如有源区域、栅极电极、源极和漏极、层间互连的金属线或通孔以及用于接合焊盘的开口,以形成于半导体衬底(例如硅晶圆)及设置在半导体衬底上的各个材料层中。设计室1720实现了包括图15的方法1500以及上面针对图1A-7D和9-14的讨论的适当设计程序,以形成IC设计布局图1722。设计程序包括一个或多个逻辑设计、物理设计或地点和布线。IC设计布局图1722呈现在具有几何图案的信息的一个或多个数据文件中。例如,IC设计布局图1722可以用GDSII文件格式或DFII文件格式表示。

掩模室1730包括数据准备1732和掩模制造1744。掩模室1730使用IC设计布局图1722来制造一个或多个掩模1745,以用于根据IC设计布局图1722制造IC器件1760的各个层。掩模室1730执行掩模数据准备1732,其中IC设计布局图1722被转换为代表性数据文件(“RDF”)。掩模数据准备1732向掩模制造1744提供RDF。掩模制造1744包括掩模写入器。掩模写入器将RDF转换为衬底上的图像,例如掩模(刻线(reticle))1745或半导体晶圆1753。设计布局图1722由掩模数据准备1732操纵,以符合掩模写入器的特定特性和/或IC制造商/制造者1750的要求。在图17中,将掩模数据准备1732和掩模制造1744示为单独的元素。在一些实施例中,掩模数据准备1732和掩模制造1744统称为掩模数据准备。

在一些实施例中,掩模数据准备1732包括光学邻近校正(OPC),其使用光刻增强技术来补偿图像误差,例如可能由衍射、干涉、其他工艺效果等引起的那些误差。OPC调整IC设计布局图1722。在一些实施例中,掩模数据准备1732还包括分辨率增强技术(RET),例如离轴照明、亚分辨率辅助特性、相移掩模、其他合适的技术等或其组合。在一些实施例中,还使用了将OPC视为逆成像问题的逆光刻技术(ILT)。

在一些实施例中,掩模数据准备1732包括掩模规则检查器(MRC),掩模规则检查器检查在OPC中经过处理的IC设计布局图1722,其包含某些几何和/或连接限制以确保足够裕度的一组掩模创建标准规则,以说明半导体制造工艺等的可变性。在一些实施例中,MRC修改IC设计布局图1722以补偿在掩模制造1744期间的限制,其可以撤消由OPC执行的部分修改以满足掩模创建标准规则。

在一些实施例中,掩模数据准备1732包括模拟将由IC制造商/制造者1750实现以制造IC器件1760的处理的光刻工艺检查(LPC)。LPC基于IC设计布局图1722模拟此处理,以创建模拟制造的设备,例如IC器件1760。LPC模拟中的处理参数可以包括与IC制造周期的各种工艺相关联的参数、与用于制造IC的工具相关联的参数和/或制造工艺的其他方面。LPC考虑了各种因素,例如航空图像对比度、聚焦深度(“DOF”)、掩模误差增强因子(“MEEF”)、其他合适的因素等或其组合。在一些实施例中,在由LPC创建模拟制造的设备之后,如果模拟设备的形状不足以满足设计规则,则重复OPC和/或MRC以进一步改善IC设计布局图1722。

应当理解,出于清楚的目的,对掩模数据准备1732的上述描述进行了简化。在一些实施例中,数据准备1732包括诸如逻辑操作(LOP)之类的附加特征,以根据制造规则修改IC设计布局图1722。另外,在数据准备1732期间应用于IC设计布局图1722的工艺可以以各种不同的顺序执行。

在掩模数据准备1732之后和掩模制造1744期间,基于修改的IC设计布局图1722制造掩模1745或一组掩模1745。在一些实施例中,掩模制造1744包括基于IC设计布局图1722执行一个或多个光刻曝光。在一些实施例中,基于修改的IC设计布局图1722,电子束(e-beam)或多个电子束的机构用于在掩模(光掩模或刻线)1745上形成图案。掩模1745可以以各种技术形成。在一些实施例中,使用二进制技术形成掩模1745。在一些实施例中,掩模图案包括不透明区域和透明区域。用于曝光已涂覆在晶圆上的图像敏感材料层(例如光致抗蚀剂)的辐射光束(例如紫外线(UV)光束)被不透明区域阻挡并通过透明区域传输。在一个示例中,掩模1745的二元掩模版本包括透明衬底(例如熔融石英)和涂覆在二元掩模的不透明区域中的不透明材料(例如铬)。在另一示例中,使用相移技术形成掩模1745。在掩模1745的相移掩模(PSM)版本中,在相移掩模上形成的图案中的各种特征被配置为具有适当的相位差以增强分辨率和成像质量。在各种示例中,相移掩模可以是衰减的PSM或交替的PSM。由掩模制造1744生成的(一个或多个)掩模用于各种工艺。例如,这样的(一个或多个)掩模用于:在离子注入工艺中,在半导体晶圆1753中形成各种掺杂区域;在蚀刻工艺中在半导体晶圆1753中形成各种蚀刻区域;和/或其他合适的工艺。

IC制造商/制造者1750包括晶圆制造1752。IC制造商/制造者1750是一家集成电路制造企业,包括用于制造各种不同IC产品的一个或多个制造设施。在一些实施例中,IC制造商/制造者1750是半导体铸造厂。例如,可以有用于多个IC产品的前端制造的制造设施(前段制程(FEOL)制造),而第二制造设施可以提供用于IC产品的互连和封装的后端制造(后段制程(BEOL)制造),第三制造设施可以为铸造企业提供其他服务。

IC制造商/制造者1750使用由掩模室1730制造的(一个或多个)掩模1745来制造IC器件1760。因此,IC制造商/制造者1750至少间接地使用IC设计布局图1722来制造IC器件1760。在一些实施例中,半导体晶圆1753由IC制造商/制造者1750使用(一个或多个)掩模1745制造以形成IC器件1760。在一些实施例中,IC制造包括至少间接地基于IC设计布局图1722执行一个或多个光刻曝光。半导体晶圆1753包括硅衬底或具有在其上形成的材料层的其他适当衬底。半导体晶圆1753还包括各种掺杂区域、电介质特征、多级互连等(在随后的制造步骤中形成)中的一者或多者。

基于上述讨论,可以看出本公开提供了优点。然而,要理解的是,其他实施例可以提供额外的优点,并且并非所有的优点都必须在本文中公开,并且对于所有实施例不需要特定的优点。一个优点是,由于去除了虚设栅极,因此可以省略虚设栅极上方的附加导电迹线和/或通孔,并且可以有效地节省紧凑布局结构中的金属布线资源。另一个优点是,由于去除了虚设栅极,因此降低了虚设栅极接地的功耗。此外,去除虚设栅极也降低了栅极结构之间的寄生电容。

根据一些实施例,半导体器件包括衬底、第一栅极结构、第二栅极结构、第三栅极结构和第一源极/漏极区域。第一栅极结构、第二栅极结构和第三栅极结构位于衬底上方并沿着第一方向布置。第一栅极结构、第二栅极结构和第三栅极结构沿着不同于第一方向的第二方向延伸,并且第二栅极结构位于第一栅极结构和第三栅极结构之间。第一源极/漏极区域位于第一栅极结构和第三栅极结构之间,并且第一源极/漏极区域位于第二栅极结构的一个端部处。

根据一些实施例,半导体器件包括第一半导体鳍部、第二半导体鳍部、第一栅极结构、第二栅极结构、第一外延结构和第二外延结构。第一栅极结构跨第一半导体鳍部和第二半导体鳍部。第二栅极结构跨第二半导体鳍部并与第一半导体鳍部间隔开。第一外延结构和第二外延结构位于第一半导体鳍部上方并且位于第一栅极结构的相反侧。第一外延结构和第二外延结构具有不同的长度。

根据一些实施例,用于制造半导体器件的方法包括在衬底上方形成有源区域。栅极结构形成在衬底上方并跨有源区域。栅极结构具有基本上恒定的间距。去除栅极结构中的至少一个的一部分以暴露有源区域的一部分。第一外延结构至少形成在有源区域的暴露部分上。

以上概述了若干实施例的特征,以便本领域技术人员可以更好地理解本公开的各个方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改其他过程和结构的基础,以实现相同的目的和/或实现本文介绍的实施例的相同优点。本领域技术人员还应当认识到,这样的等效结构不背离本公开的精神和范围,并且它们可以在不背离本公开的精神和范围的情况下在本公开中进行各种改变、替换和更改。

示例1.一种半导体器件,包括:衬底;第一栅极结构、第二栅极结构和第三栅极结构,所述第一栅极结构、所述第二栅极结构和所述第三栅极结构位于所述衬底上方并沿着第一方向布置,其中,所述第一栅极结构、所述第二栅极结构和所述第三栅极结构在不同于所述第一方向的第二方向上延伸,并且所述第二栅极结构位于所述第一栅极结构和所述第三栅极结构之间;以及第一源极/漏极区域,所述第一源极/漏极区域位于所述第一栅极结构和所述第三栅极结构之间,并且位于所述第二栅极结构的一个端部处。

示例2.根据示例1所述的半导体器件,其中,所述第一栅极结构和所述第二栅极结构具有第一间距,并且所述第二栅极结构和所述第三栅极结构具有与所述第一间距基本上相同的第二间距。

示例3.根据示例1所述的半导体器件,其中,所述第一源极/漏极区域具有所述第一方向上的长度,并且所述第一源极/漏极区域的所述长度大于所述第一栅极结构和所述第二栅极结构的间距。

示例4.根据示例1所述的半导体器件,还包括隔离结构,所述隔离结构位于所述衬底上方并且与所述第一源极/漏极区域相邻,其中,所述第二栅极结构的所述端部位于所述隔离结构正上方。

示例5.根据示例1所述的半导体器件,还包括第二源极/漏极区域,位于所述第一栅极结构和所述第二栅极结构之间。

示例6.根据示例5所述的半导体器件,其中,所述第二源极/漏极区域的长度小于所述第一源极/漏极区域的长度。

示例7.根据示例5所述的半导体器件,其中,所述第二源极/漏极区域的长度基本上为所述第一源极/漏极区域的长度的一半。

示例8.根据示例5所述的半导体器件,其中,所述第一源极/漏极区域和所述第二源极/漏极区域沿着所述第二方向布置。

示例9.一种半导体器件,包括:第一半导体鳍部和第二半导体鳍部;第一栅极结构,所述第一栅极结构跨所述第一半导体鳍部和所述第二半导体鳍部;第二栅极结构,所述第二栅极结构跨所述第二半导体鳍部并与所述第一半导体鳍部间隔开;以及第一外延结构和第二外延结构,所述第一外延结构和所述第二外延结构位于所述第一半导体鳍部上方并位于所述第一栅极结构的相反侧,其中,所述第一外延结构和所述第二外延结构具有不同长度。

示例10.根据示例9所述的半导体器件,其中,所述第一外延结构位于所述第二栅极结构的一个端部处,并且所述第一外延结构的长度大于所述第二外延结构的长度。

示例11.根据示例10所述的半导体器件,其中,所述第一外延结构的长度基本上是所述第二外延结构的长度的两倍。

示例12.根据示例9所述的半导体器件,还包括第三外延结构和第四外延结构,所述第三外延结构和所述第四外延结构位于所述第二半导体鳍部上方并位于所述第二栅极结构的相反侧。

示例13.根据示例12所述的半导体器件,其中,所述第三外延结构和所述第四外延结构具有基本上相同的长度。

示例14.根据示例12所述的半导体器件,其中,所述第二外延结构和所述第三外延结构具有基本上相同的长度。

示例15.根据示例12所述的半导体器件,其中,所述第一外延结构的边缘基本上与所述第四外延结构的边缘对准。

示例16.根据示例15所述的半导体器件,其中,所述第三外延结构位于所述第一栅极结构和所述第二栅极结构之间。

示例17.一种用于制造半导体器件的方法,包括:在衬底上方形成有源区域;在所述衬底上方并跨所述有源区域形成栅极结构,其中,所述栅极结构具有基本上恒定的间距;去除所述栅极结构中的至少一个栅极结构的一部分以暴露所述有源区域的一部分;以及至少在所述有源区域的暴露部分上形成第一外延结构。

示例18.根据示例17所述的方法,其中,所述第一外延结构形成在所述栅极结构中的两个栅极结构之间。

示例19.根据示例17所述的方法,还包括:在所述有源区域上方并在所述栅极结构中的相邻的两个栅极结构之间形成第二外延结构,其中,形成所述第一外延结构使得所述第一外延结构的第一长度大于所述第二外延结构的第二长度。

示例20.根据示例19所述的方法,其中,所述第一长度为所述第二长度的n倍,并且n为正整数。

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件的制造方法、半导体器件的制造装置、半导体器件、半导体器件的制造程序、半导体用处理剂以及转印用部件