薄膜晶体管及其制备方法、显示面板

文献发布时间:2023-06-19 11:45:49

技术领域

本发明实施例涉及显示技术领域,尤其涉及一种薄膜晶体管及其制备方法、显示面板。

背景技术

随着显示技术的不断发展,显示面板的应用范围也越来越广泛,人们对显示面板的要求也越来越高。其中,薄膜晶体管(Thin Film Transistor,TFT)是显示面板中的重要器件,对显示面板的运行性能和显示效果起到了至关重要的作用。然而,现有的薄膜晶体管的制备方法存在缺陷,使得制作出的薄膜晶体管的实际沟道长度小于设计长度,且误差较大。因此,现有的薄膜晶体管的良率较低。

发明内容

本发明实施例提供一种薄膜晶体管及其制备方法、显示面板,以增大薄膜晶体管的沟道长度,减小沟道长度的误差,提升薄膜晶体管的良率。

为实现上述技术目的,本发明实施例提供了如下技术方案:

一种薄膜晶体管的制备方法,包括:

在半导体层上依次制作栅极绝缘层和栅极,以及对所述半导体层进行导体化,在所述半导体层上形成沟道区和源漏区;其中,沿所述沟道区的长度方向,所述栅极绝缘层的尺寸大于所述沟道区的设计长度;

在对应所述源漏区的位置制作源漏电极,形成薄膜晶体管。

进一步地,采用一道掩膜工艺同时制作所述栅极绝缘层和所述栅极;

优选地,所述在半导体层上依次制作栅极绝缘层和栅极,包括:

在半导体层上依次制作栅极绝缘材料层和栅极材料层;

采用半色调掩膜工艺对所述栅极绝缘材料层和所述栅极材料层进行图案化,形成所述栅极绝缘层和所述栅极;其中,沿所述沟道区的长度方向,所述栅极绝缘层的尺寸大于所述栅极的尺寸。

进一步地,在所述半色调掩膜工艺中采用的半色调掩膜板包括至少三种光透过率,所述至少三种光透过率分别对应光刻胶层的不同位置;

优选地,所述栅极绝缘材料层包括绝缘主区、绝缘尾区和刻蚀区;所述绝缘尾区位于所述绝缘主区的外侧,所述刻蚀区位于所述绝缘尾区的外侧;所述半色调掩膜板包括光透过率依次减小的第一透光区、第二透光区和第三透光区;

所述光刻胶层为正性光刻胶,所述第三透光区与所述绝缘主区对应,所述第二透光区与所述绝缘尾区对应,所述第一透光区与所述刻蚀区对应;

或者,所述光刻胶层为负性光刻胶,所述第一透光区与所述绝缘主区对应,所述第二透光区与所述绝缘尾区对应,所述第三透光区与所述刻蚀区对应。

进一步地,所述采用半色调掩膜工艺对所述栅极绝缘材料层和所述栅极材料层进行图案化,包括:

在所述栅极材料层上形成光刻胶层;

采用所述半色调掩膜板对所述光刻胶层进行曝光和显影,去除所述光刻胶层上对应所述源漏区的部分;

对所述栅极绝缘材料层和所述栅极材料层进行第一次刻蚀,形成栅极绝缘层;

去除所述光刻胶层对应所述栅极以外的部分;

对所述栅极材料层进行第二次刻蚀,形成所述栅极;

优选地,在对所述栅极绝缘材料层和所述栅极材料层进行第一次刻蚀的同时,或者在对所述栅极绝缘材料层和所述栅极材料层进行第一次刻蚀之后,还包括:对所述半导体层进行导体化。

进一步地,采用两道掩膜工艺分别制作所述栅极绝缘层和所述栅极;

优选地,所述在半导体层上依次制作栅极绝缘层和栅极,包括:

在半导体层上制作栅极绝缘材料层,对所述栅极绝缘材料层进行图案化,形成栅极绝缘层;

在所述栅极绝缘层上制作栅极材料层,对所述栅极材料层进行图案化,形成所述栅极。

进一步地,所述半导体层的材料包括氧化物;采用干刻工艺形成所述栅极绝缘层,利用所述干刻工艺对所述半导体层进行导体化。

相应地,本发明还提供了一种薄膜晶体管,该薄膜晶体管可以采用本发明任意实施例所提供的薄膜晶体管制备方法制备而成,薄膜晶体管包括:

半导体层,所述半导体层包括沟道区和源漏区,对应所述源漏区的位置设置有源漏电极;

栅极绝缘层,位于所述半导体层靠近所述源漏电极的一侧;

栅极,位于所述栅极绝缘层靠近所述源漏电极的一侧;其中,所述栅极绝缘层沿所述沟道区的长度方向的尺寸大于所述沟道区的设计长度。

进一步地,所述栅极绝缘层包括绝缘主区和绝缘尾区;沿所述沟道区的长度方向,所述绝缘主区的尺寸与所述栅极的尺寸相等,所述绝缘尾区位于所述绝缘主区的两侧;

优选地,沿所述沟道区的长度方向,所述栅极的长度范围为3um-5um,位于所述栅极一侧的所述绝缘尾区的长度范围为500nm-800nm;

优选地,所述绝缘尾区关于所述绝缘主区对称。

进一步地,所述半导体层的材料包括氧化物;

优选地,所述氧化物包括铟镓锌氧化物、铟锡锌氧化物或氧化铟锌中的至少一种。

相应地,本发明还提供了一种显示面板,包括如本发明任意实施例所述的薄膜晶体管。

本发明实施例提供了一种薄膜晶体管的制备方法,通过在薄膜晶体管的制备过程中,设置栅极绝缘层的尺寸大于沟道区的设计长度,有利于对半导体层的导体化扩散作用形成缓冲。与现有技术相比,一方面,本发明实施例有利于增大沟道区的实际长度,使得沟道区的实际长度更加接近设计长度,提高了薄膜晶体管的良率,以及提升了薄膜晶体管的特性均一性。另一方面,对半导体层的导体化扩散作用形成缓冲的部分对应形成了LDD结构。因此,本发明实施例通过设置栅极绝缘层的尺寸大于沟道区的设计长度将过渡区外移,不仅有利于使得沟道区的长度更加接近设计长度,有利于提高薄膜晶体管的良率和特性均一性;而且过渡区还起到了LDD的作用,有利于降低薄膜晶体管的漏电流,提升薄膜晶体管的性能。

附图说明

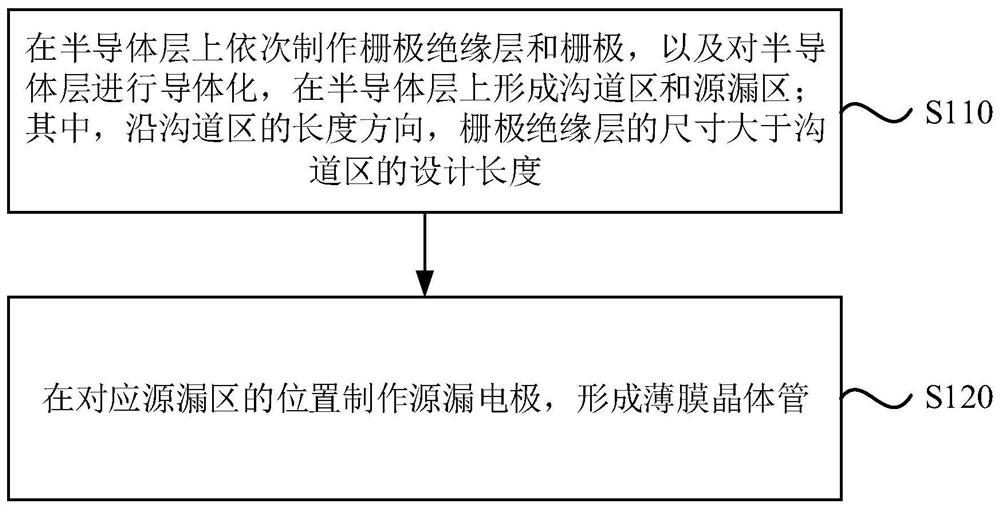

图1为本发明实施例提供的一种薄膜晶体管的制备方法的流程示意图;

图2为图1的制备方法在各步骤中形成的结构示意图;

图3为现有的一种薄膜晶体管的俯视结构示意图;

图4为沿图3中A-A的剖面结构示意图;

图5为本发明实施例提供的另一种薄膜晶体管的制备方法的流程示意图;

图6-图7为图5的制备方法在各步骤中形成的结构示意图;

图8为本发明实施例提供的又一种薄膜晶体管的制备方法的流程示意图;

图9-图10为图8的制备方法在各步骤中形成的结构示意图;

图11为本发明实施例提供的一种薄膜晶体管的结构示意图。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

图1为本发明实施例提供的一种薄膜晶体管的制备方法的流程示意图,图2为图1的制备方法在各步骤中形成的结构示意图。参见图1和图2,该薄膜晶体管的制备方法包括以下步骤:

S110、在半导体层20上依次制作栅极绝缘层30和栅极40,以及对半导体层20进行导体化,在半导体层20上形成沟道区201和源漏区203;其中,沿沟道区201的长度方向X,栅极绝缘层30的尺寸大于沟道区201的设计长度。

其中,半导体层20包括沟道区201和源漏区203,沿沟道区201的长度方向X,源漏区203位于沟道区的两侧。沟道区201的长度方向X是指薄膜晶体管导通时的电流流动方向。下面结合图3和图4对沟道区201的长度方向X进行解释,图3为现有的一种薄膜晶体管的俯视结构示意图,图4为沿图3中A-A的剖面结构示意图。参见图3和图4,薄膜晶体管包括层叠设置的缓冲层10、半导体层20、栅极绝缘层30、栅极40、介电层50和源漏电极60。由于薄膜晶体管为对称结构,本发明实施例对源极和漏极不做区分,可以设定左侧的源漏电极60为源极,右侧的源漏电极60为漏极,也可以设定右侧的源漏电极60为源极,左侧的源漏电极60为漏极。当薄膜晶体管导通时,沟道区201的载流子在源极和漏极之间流动,形成电流,因此,电流的流通路径方向定义为沟道区201的长度方向X。

继续参见图3和图4,源漏区203与源漏电极60搭接。在现有技术中,为了保证源漏电极60与半导体层20能够良好接触,减小源漏电极60与半导体层20的搭接阻抗,提升薄膜晶体管的性能,需要对半导体层20的源漏区203进行导体化,即降低源漏区203的电阻。然而,经发明人研究发现,现有的导体化工艺存在缺陷,导致了半导体层20的沟道区201的实际长度小于设计长度204。出现该问题的原因在于,在半导体层20的半导体化工艺中(例如,采用等离子体对半导体层20进行导体化,等离子体破坏半导体层20中的一些化学键,实现导体化),栅极绝缘层30对半导体层20形成遮挡。现有技术设置栅极绝缘层30的尺寸与沟道区的设计长度204相等,在理想状态下,栅极绝缘层30对应的部分形成沟道区201。但是,由于等离子体的扩散作用,等离子体由源漏区203扩散至沟道区201,对源漏区203和沟道区201的交界区域进行导体化,形成位于源漏区203和沟道区201之间的过渡区。由于过渡区的存在,源漏区201的实际沟道长度小于设计长度204。薄膜晶体管中的沟道区201的长度决定了薄膜晶体管的特性,当沟道区201的长度与设计长度204相比过小时,薄膜晶体管无法准确建立电场,从而导致性能不良的现象,良率较低。

有鉴于此,继续参见图2,本发明实施例在薄膜晶体管的制备方法中,设置栅极绝缘层30的尺寸大于沟道区201的设计长度204,有利于增大沟道区201的实际长度,使得沟道区201的实际长度更加接近设计长度204(图2中示出了沟道区201的实际长度与设计长度204相等),从而有利于提高薄膜晶体管的良率,以及提升薄膜晶体管的特性均一性。

具体地,栅极绝缘层30包括绝缘主区301和绝缘尾区302,在沟道区的长度方向X上,绝缘主区301的尺寸与沟道区的设计长度204相等,绝缘尾区302位于绝缘主区301的两侧。相应地,半导体层20包括沟道区201、过渡区202和源漏区203,在沟道区的长度方向X上,过渡区202位于沟道区201的两侧,源漏区203位于过渡区202的两侧。

其中,沟道区201为半导体性质,电阻最大;过渡区202进行了部分导体化,过渡区202的电阻小于沟道区201的电阻;源漏区203进行了完全导体化,源漏区203的电阻最小。其中,过渡区202的结构相当于轻掺杂漏极结构(Lightly Doped Drain,LDD),相当于在源漏电极60和沟道区201之间串联了一个大电阻,降低了沟道区201的水平电场,减少了电场加速引起的碰撞电离所产生的热载流子,可以有效地抑制漏电流。由此可见,对于现有技术,沟道区201和源漏区203中间的过渡区只能够起到减小沟道区201长度的不良作用,然而,经过发明人的巧妙设计,在本发明实施例中,可以将过渡区202外移,不仅有利于使得沟道区201的长度更加接近设计长度204,而且过渡区202还起到了LDD的作用,有利于降低薄膜晶体管的漏电流。

其中,过渡区202由等离子体的扩散形成,在相同的工艺条件下,过渡区202的长度可以认为是恒定的。可以理解的是,绝缘尾区302的长度越长,对沟道区201的遮挡效果越好,在导体化过程中形成的沟道区201的长度越长;相反,绝缘尾区302的长度越短,在导体化过程中形成的沟道区201的长度越短。最优的方案是,绝缘尾区302的设置使得沟道区201的长度与设计长度204相等。在实际应用中,可以根据需要设定绝缘尾区302的长度,以使沟道区201的实际长度与设计长度204更加接近。

可选地,沟道区201的设计长度204的长度范围为3um-5um,沿沟道区201的长度方向X,位于绝缘主区301一侧的绝缘尾区302的长度范围为500nm-800nm。其中,由于薄膜晶体管为对称设置,绝缘尾区302对称设置于绝缘主区301的两侧,这里设定一侧的绝缘尾区302的长度范围为500nm-800nm,相应地,另一侧的绝缘尾区302的长度范围也为500nm-800nm。这样设置,有利于过渡区202的长度与绝缘尾区302的长度相等,从而有利于绝缘主区301的长度与沟道区201的长度相等,有利于沟道区201的长度与设计长度204相等。

继续参见图2,可选地,栅极40的尺寸与沟道区201的设计长度204相等,即栅极40的尺寸与绝缘主区301的尺寸相等。那么,栅极绝缘层30的尺寸大于栅极40的尺寸,栅极绝缘层30上大于栅极40尺寸的区域为绝缘尾区302。可选地,沿沟道区201的长度方向X,栅极40的长度范围为3um-5um,位于栅极40一侧的绝缘尾区302的长度范围为500nm-800nm。

S120、在对应源漏区203的位置制作源漏电极60,形成薄膜晶体管。

其中,源漏电极60采用导电材料制作而成,导电材料例如可以是钼或钛铝钛等。可选地,在源漏电极60和半导体层20之间还设置有介电层50,介电层50对应源漏区203的位置设置有过孔,源漏电极60通过过孔连接至源漏区203。示例性地,源漏电极60的制作步骤包括:首先在源漏区203和栅极40上制作介电层50,并对介电层50进行图案化,形成暴露源漏区203的过孔;然后在介电层50上制作电极材料层(例如,采用沉积工艺),电极材料层通过过孔与源漏区203搭接;最后对电极材料层进行图案化,形成源漏电极60。

综上所述,本发明实施例提供了一种薄膜晶体管的制备方法,通过在薄膜晶体管的制备过程中,设置栅极绝缘层30的尺寸大于沟道区的设计长度204,有利于对半导体层20的导体化扩散作用形成缓冲。与现有技术相比,一方面,本发明实施例有利于增大沟道区201的实际长度,使得沟道区201的实际长度更加接近设计长度204,提高了薄膜晶体管的良率,以及提升了薄膜晶体管的特性均一性。另一方面,对半导体层20的导体化扩散作用形成缓冲的部分对应形成了LDD结构。因此,本发明实施例通过设置栅极绝缘层30的尺寸大于沟道区的设计长度204将过渡区202外移,不仅有利于使得沟道区201的长度更加接近设计长度204,有利于提高薄膜晶体管的良率和特性均一性;而且过渡区202还起到了LDD的作用,有利于降低薄膜晶体管的漏电流,提升薄膜晶体管的性能。

在上述各实施例的基础上,栅极绝缘层30和栅极40的制备方法有多种,示例性地,可以采用一道掩膜工艺同时制作栅极绝缘层30和栅极40,也可以采用两道掩膜工艺分别制作栅极绝缘层30和栅极40。下面就栅极绝缘层30和栅极40的制备方法进行具体说明,但不作为对本发明的限定。

图5为本发明实施例提供的另一种薄膜晶体管的制备方法的流程示意图,图6-图7为图5的制备方法在各步骤中形成的结构示意图。参见图5-图7,在本发明的一种实施方式中,可选地,薄膜晶体管的制备方法包括以下步骤:

S210、在半导体层20上依次制作栅极绝缘材料层31和栅极材料层41。

其中,栅极绝缘材料层31的材料包括氧化硅(SiOx)和氮化硅(SiNx)中的至少一种。示例性地,可以采用沉积工艺在半导体层20上制作栅极绝缘材料层31。

栅极材料层41的材料可以包括铝(Al)、铝合金、银(Ag)、银合金、铜(Cu)、铜合金、钼(Mo)、钼合金、铬(Cr)、钽(Ta)、钕(Nd)或钛(Ti)中至少一种。示例性地,可以采用沉积工艺将栅极材料层41制作在栅极绝缘材料层31上。

S220、采用半色调掩膜工艺对栅极绝缘材料层31和栅极材料层41进行图案化,形成栅极绝缘层30和栅极40;其中,沿沟道区201的长度方向,栅极绝缘层30的尺寸大于栅极40的尺寸。

其中,半色调掩膜工艺是光刻工艺中的一种,示例性地,可以将S220划分为以下几个步骤:

S221、在栅极材料层41上形成光刻胶层70。

其中,光刻胶层70的材料可以包括正性光刻胶或负性光刻胶,对于正性光刻胶,被曝光的部分可溶于显影液中,未被曝光的部分不可溶于显影液中;对于负性光刻胶,被曝光的部分不可溶于显影液中,未被曝光的部分可溶于显影液中。光刻胶层70的材料一般为有机物,示例性地,可以采用静态涂胶或动态涂胶等方式进行光刻胶层70的涂布。

S222、采用半色调掩膜板80对光刻胶层70进行曝光。

其中,与普通掩膜板不同的是,半色调掩膜板80能够使得光刻胶层70在一次曝光和显影工艺中形成不同的厚度。半色调掩膜板80包括至少三种光透过率,至少三种光透过率分别对应光刻胶层70的不同位置。若光刻胶层70为正性光刻胶,光透过率越高,对应的显影后的光刻胶层70的厚度越薄;光透过率越低,对应的显影后的光刻胶层70的厚度越厚。若光刻胶层70为负性光刻胶,光透过率越低,对应的显影后的光刻胶层70的厚度越薄;光透过率越高,对应的显影后的光刻胶层70的厚度越厚。

示例性地,栅极绝缘材料层31包括绝缘主区311、绝缘尾区312和刻蚀区313;绝缘尾区312位于绝缘主区311的外侧,刻蚀区313位于绝缘尾区312的外侧。例如,绝缘尾区312关于绝缘主区311对称,刻蚀区313关于绝缘主区311对称,以使制备出的薄膜晶体管为对称的薄膜晶体管。

其中,栅极绝缘材料层31的各区域与各膜层的对应关系如下:

第一方面,栅极绝缘材料层31的各区域与半导体层20存在对应关系:绝缘主区311对应半导体层20的沟道区201,绝缘尾区312对应半导体层20的过渡区202,刻蚀区313对应半导体层20的源漏区203。

第二方面,若设置半导体层20的沟道区201的长度与栅极40的尺寸相等,栅极绝缘材料层31的各区域与栅极材料层41存在对应关系:绝缘主区311对应栅极材料层41的栅极区,绝缘尾区312和刻蚀区313对应栅极材料层41的刻蚀区。

第三方面,栅极绝缘材料层31的各区域与光刻胶层70存在对应关系:绝缘主区311对应光刻胶层70的保留区,绝缘尾区312对应光刻胶层70的半保留区,刻蚀区313对应光刻胶层70的不保留区。

第四方面,栅极绝缘材料层31的各区域与半色调掩膜板80存在对应关系:半色调掩膜板80包括光透过率依次减小的第一透光区801、第二透光区802和第三透光区803。以光刻胶层70为正性光刻胶为例,第三透光区803与栅极绝缘材料层31的绝缘主区311(即光刻胶层70的保留区)对应,第二透光区802与栅极绝缘材料层31的绝缘尾区312(即光刻胶层70的半保留区)对应,第一透光区801与栅极绝缘材料层31的刻蚀区313(即光刻胶层70的不保留区)对应。这样,在后续的刻蚀工艺中,栅极绝缘层31可以保留绝缘主区311和绝缘尾区312,以及保留位于绝缘主区311上的栅极材料层41的部分。

S223、对曝光后的光刻胶层70进行显影,去除光刻胶层70上对应源漏区203的部分。

其中,光刻胶层70上对应源漏区203的部分为光刻胶层70的不保留区,去除光刻胶层70的不保留区以暴露出栅极绝缘材料层31的刻蚀区313。具体地,由于半色调掩膜板80上第一透光区801的透过率最高,例如可以是全透,因此,光刻胶层70对应第一透光区801(半导体层20的源漏区203)的部分被全部去除;由于第二透光区802的透过率较第一透光区801较低,例如可以是半透,因此,光刻胶层70对应第二透光区802的部分被部分去除;由于第三透光区803的透过率最低,例如可以是不透光,因此,光刻胶层70对应第三透光区803的部分的厚度最厚。也就是说,曝光后的光刻胶层70呈现阶梯状。

S224、对栅极绝缘材料层31和栅极材料层41进行第一次刻蚀,形成栅极绝缘层30。

其中,由于在S223中,光刻胶层70保留了半保留区和保留区,不保留区被去除,使得栅极绝缘材料层31对应刻蚀区313的部分被暴露。因此,在刻蚀工艺下,栅极绝缘材料层31和栅极材料层41对应不保留区的部分全部被刻蚀,暴露出半导体层20的源漏区203。此时栅极绝缘材料层未被刻蚀的部分为栅极绝缘层30,栅极材料层41未被刻蚀的部分在后续步骤中继续被刻蚀。示例性地,对栅极绝缘材料层和栅极材料层41进行刻蚀的工艺为干刻工艺或湿刻工艺。沿沟道区201的长度方向,栅极绝缘层30的尺寸与第一次刻蚀后的栅极材料层41的尺寸相等。

可选地,半导体层20的材料包括氧化物,可选地,氧化物包括铟镓锌氧化物(Indium Gallium Zinc Oxide,IGZO)、铟锡锌氧化物(Indium Tin Zinc Oxide,ITZO)或氧化铟锌(Indium Zinc Oxide,IZO)中的至少一种。对氧化物半导体层20的导体化工艺可以是利用等离子体等刻蚀气体破坏氧化物内部的一些化学键,导致氧化物内的氧释放出来,氧空位含量增多,实现氧化物的导体化。因此,可以采用干刻工艺对栅极绝缘材料层31和栅极材料层41进行刻蚀。以及,干刻工艺采用等离子体等刻蚀气体,这样在采用等离子体对栅极绝缘材料层31和栅极材料层41进行第一次刻蚀的同时,栅极绝缘材料层31的刻蚀区313被等离子体腐蚀,栅极材料层41的不保留区被等离子体腐蚀,同时半导体层20的源漏区203被等离子体处理而电阻降低,进行导体化,即利用干刻工艺对半导体层20进行导体化。这样设置,无需采用额外的步骤对半导体的源漏区203进行单独的导体化,从而有利于简化薄膜晶体管的制备工艺。

S225、去除光刻胶层70对应栅极区以外的部分。

其中,光刻胶层70对应栅极区以外的部分(即光刻胶层70的半保留区)的厚度较薄,这部分的光刻胶层70更加容易去除。示例性地,对光刻胶层70的去除工艺可以是灰化工艺或湿法去除等。去除光刻胶层70的半保留区后,剩余光刻胶层70的保留区,使得栅极材料层41对应栅极区以外的部分被暴露。

S226、对栅极材料层41进行第二次刻蚀,形成栅极40。

示例性地,对栅极材料层41进行第二次刻蚀的工艺为干法刻蚀或湿法刻蚀等。与第一次刻蚀不同,第二次刻蚀仅需刻蚀栅极材料层41,栅极绝缘层30不被刻蚀。例如,第二次刻蚀与第一次刻蚀采用的刻蚀剂不同,或者采用的刻蚀剂的浓度不同,或者刻蚀的时间不同等,以在刻蚀栅极材料层41的同时,保留栅极绝缘层30。

S227、去除剩余的光刻胶层70。

示例性地,对光刻胶层70的去除工艺可以是灰化工艺、湿法去除或研磨工艺等。

通过S221-S227实现了采用半色调掩膜工艺对栅极绝缘材料层31和栅极材料层41进行图案化,形成栅极绝缘层30和栅极40的步骤。

S230、在对应源漏区203的位置制作源漏电极60,形成薄膜晶体管。

本发明实施例通过以上步骤,实现了采用一道掩膜工艺同时制作栅极绝缘层30和栅极40,这样设置有利于减少掩膜工艺的数量,简化工艺制程,减少设备投资费用,从而有利于减少薄膜晶体管或包含薄膜晶体管的显示面板的单价。

需要说明的是,在上述各实施例中,示例性地示出了光刻胶层70为正性光刻胶,并非对本发明的限定。在其他实施例中,还可以设置光刻胶层70为负性光刻胶,这样掩膜板的第一透光区801与绝缘主区301对应,第二透光区802与绝缘尾区302对应,第三透光区803与刻蚀区对应。

还需要说明的是,在上述各实施例中,示例性地示出了在对栅极绝缘材料层31和栅极材料层41进行第一次刻蚀的同时,对半导体层20进行导体化,并非对本发明的限定。在其他实施例中,还可以设置,在对栅极绝缘材料层31和栅极材料层41进行第一次刻蚀之后,再对半导体层20进行导体化。

在上述各实施例的基础上,可选地,在半导体层20上制作栅极绝缘材料层31之前,还包括:在缓冲层10上形成半导体材料层,对半导体材料层进行图案化,形成半导体层20。

其中,半导体材料层的材料包括氧化物,可选地,氧化物包括铟镓锌氧化物、铟锡锌氧化物或氧化铟锌中的至少一种。半导体材料层可以掺杂P型离子,从而形成P型薄膜晶体管;半导体材料层也可以掺杂N型离子,从而形成N型薄膜晶体管。示例性地,可以采用光刻工艺或激光刻蚀工艺对半导体材料层进行刻蚀,以形成半导体层20。

可选地,在衬底上制作缓冲层10,然后执行本发明实施例所提供的制备方法,形成氧化物薄膜晶体管。可选地,在衬底上制作缓冲层10(第一缓冲层),然后执行本发明实施例所提供的制备方法;然后继续形成第二缓冲层,执行低温多晶硅(Low Temperature Poly-silicon,LTPS)薄膜晶体管的制备方法,最终形成低温多晶氧化物(Low TemperaturePolycrystalline Oxide,LTPO)薄膜晶体管。可选地,执行低温多晶硅薄膜晶体管的制备方法,然后在低温多晶硅薄膜晶体管上制作缓冲层10,然后执行本发明实施例所提供的制备方法,形成低温多晶氧化物薄膜晶体管。其中,在形成的LTPO薄膜晶体管中,低温多晶硅薄膜晶体管的源漏电极与氧化物薄膜晶体管的源漏电极可以同层设置,也可以异层设置,在实际应用中可以根据需要进行设定。

图8为本发明实施例提供的又一种薄膜晶体管的制备方法的流程示意图,图9-图10为图8的制备方法在各步骤中形成的结构示意图。参见图8-图10,在本发明的一种实施方式中,可选地,薄膜晶体管的制备方法包括以下步骤:

S310、在半导体层20上制作栅极绝缘材料层31,对栅极绝缘材料层31进行图案化,形成栅极绝缘层30。

其中,栅极绝缘材料层31进行图案化的工艺例如可以是光刻工艺,示例性地,可以将S310划分为以下几个步骤:

S311、在半导体层20上形成栅极绝缘材料层31。

S312、在栅极绝缘材料层31上形成第一光刻胶层71。

S313、采用第一掩膜板81对第一光刻胶层71进行曝光。

其中,对第一光刻胶层71进行曝光采用的第一掩膜板81无需使用半色调掩膜板,使用普通掩膜板即可。第一掩膜板81包括透光区811和非透光区813,以第一光刻胶层71为正性光刻胶为例,非透光区813与第一光刻胶层71的保留区(即栅极绝缘材料层31的绝缘主区311和绝缘尾区312)对应,透光区811与第一光刻胶层71的不保留区(即栅极绝缘材料层31的刻蚀区313)对应。这样,在后续的刻蚀工艺中,栅极绝缘层可以保留绝缘主区311和绝缘尾区312。

S314、对曝光后的第一光刻胶层71进行显影,去除第一光刻胶层71上对应源漏区203的部分。

其中,第一光刻胶层71上对应源漏区203的部分为第一光刻胶层71的不保留区,去除第一光刻胶层71的不保留区以暴露出栅极绝缘材料层31的刻蚀区313。

S315、对栅极绝缘材料层31进行刻蚀,形成栅极绝缘层30。

其中,刻蚀工艺例如可以是干刻工艺或湿刻工艺等,由于栅极绝缘材料层31的刻蚀区313暴露,因此栅极绝缘材料层31的刻蚀区313被刻蚀,暴露出半导体层20的源漏区203。可选地,半导体层20的材料包括氧化物,采用干刻工艺(等离子体等刻蚀气体)对栅极绝缘材料层31进行刻蚀。这样,在采用等离子体对栅极绝缘材料层31进行刻蚀的同时,半导体层20的源漏区203被等离子体处理而电阻降低,进行导体化,即利用干刻工艺对半导体层20进行导体化。这样设置,无需采用额外的步骤对半导体的源漏区203进行单独的导体化,从而有利于简化薄膜晶体管的制备工艺。

S316、去除剩余的第一光刻胶层71。

通过S311-S316实现了对栅极绝缘材料层31进行图案化,形成栅极绝缘层30的步骤。

S320、在栅极绝缘层30上制作栅极材料层41,对栅极材料层41进行图案化,形成栅极40。

其中,对栅极材料层41进行图案化的工艺例如可以是光刻工艺,示例性地,可以将S320划分为以下几个步骤:

S321、在栅极绝缘层30上形成栅极材料层41。

S322、在栅极材料层41上形成第二光刻胶层72。

S323、采用第二掩膜板82对第二光刻胶层72进行曝光。

其中,与第一掩膜板类似,对第二光刻胶层72进行曝光采用的第二掩膜板82无需使用半色调掩膜板80,使用普通掩膜板即可。第二掩膜板82包括透光区821和非透光区823,以第二光刻胶层72为正性光刻胶为例,非透光区823与第二光刻胶层72的保留区(即栅极材料层41的栅极区、或栅极绝缘材料层31的绝缘主区311)对应,透光区821与第一光刻胶层71的不保留区(即栅极材料层41的刻蚀区、或栅极绝缘材料层31的刻蚀区313和绝缘尾区312)对应。这样,在后续的刻蚀工艺中,栅极40可以保留栅极区。

S324、对曝光后的第二光刻胶层72进行显影,对栅极材料层41进行刻蚀,以及去除剩余的第二光刻胶层72。

其中,与形成栅极绝缘层30的步骤类似,形成栅极40也包括显影和刻蚀等步骤。具体地,对曝光后的第二光刻胶层72进行显影后,可以去除第二光刻胶层72上对应源漏区203和过渡区202的部分。第二光刻胶层72上对应源漏区203和过渡区202的部分为第二光刻胶层72的不保留区,去除第二光刻胶层72的不保留区以暴露出栅极材料层41的刻蚀区。

对栅极绝缘材料层31进行刻蚀,可以形成栅极绝缘层30。刻蚀工艺例如可以是干刻工艺或湿刻工艺等,由于栅极材料层41的刻蚀区暴露,因此栅极材料层41的刻蚀区被刻蚀,暴露出半导体层20的源漏区203和栅极绝缘层30的绝缘尾区302。可选地,半导体层20的材料包括氧化物,采用干刻工艺(等离子体等刻蚀气体)对栅极材料层41进行刻蚀。这样,在采用等离子体对栅极材料层41进行刻蚀的同时,半导体层20的源漏区203被等离子体处理而电阻降低,进行导体化,即利用干刻工艺对半导体层20进行导体化。这样设置,无需采用额外的步骤对半导体的源漏区203进行单独的导体化,从而有利于简化薄膜晶体管的制备工艺。

通过S321-S324实现了对栅极材料层41进行图案化,形成栅极40的步骤。

S330、在对应源漏区203的位置制作源漏电极60,形成薄膜晶体管。

本发明实施例通过以上步骤,实现了采用两道掩膜工艺分别制作栅极绝缘层30和栅极40,这样设置无需使用半色调掩膜板,有利于降低工艺难度。

需要说明的是,在上述各实施例中,示例性地以顶栅型(Top Gate Top Contact,TG-TC)结构进行说明,并非对本发明的限定。在其他的薄膜晶体管结构中,只要存在对半导体进行导体化的过程中离子扩散问题的薄膜晶体管,均可以采用本发明实施例多提供的薄膜晶体管的制备方法。

本发明实施例还提供了一种薄膜晶体管,该薄膜晶体管可以采用如本发明任意实施例所提供的薄膜晶体管的制备方法制作而成。图11为本发明实施例提供的一种薄膜晶体管的结构示意图。参见图11,薄膜晶体管包括:缓冲层10、半导体层20、栅极绝缘层30和栅极40。半导体层20包括沟道区201和源漏区203,对应源漏区203的位置设置有源漏电极60。栅极绝缘层30位于半导体层20靠近源漏电极60的一侧;栅极40位于栅极绝缘层30靠近源漏电极60的一侧。其中,栅极绝缘层30沿沟道区201的长度方向X的尺寸大于沟道区201的设计长度。

示例性地,半导体层20的沟道区201和源漏区203之间为过渡区202,在沟道区的长度方向X上,过渡区202位于沟道区201的两侧,源漏区203位于过渡区202的两侧。栅极绝缘层30包括绝缘主区301和绝缘尾区302,在沟道区的长度方向X上,绝缘主区301的尺寸与沟道区的设计长度相等,绝缘尾区302位于绝缘主区301的两侧。

本发明实施例通过设置栅极绝缘层30的尺寸大于沟道区的设计长度,有利于对半导体层20的导体化扩散作用形成缓冲。与现有技术相比,一方面,本发明实施例有利于增大沟道区201的实际长度,使得沟道区201的实际长度更加接近设计长度,提高了薄膜晶体管的良率,以及提升了薄膜晶体管的特性均一性。另一方面,对半导体层20的导体化扩散作用形成缓冲的部分对应形成了LDD结构。因此,本发明实施例通过设置栅极绝缘层30的尺寸大于沟道区的设计长度可以将过渡区202外移,不仅有利于使得沟道区201的长度更加接近设计长度204,有利于提高薄膜晶体管的良率和特性均一性;而且过渡区202还起到了LDD的作用,有利于降低薄膜晶体管的漏电流,提升薄膜晶体管的性能。

继续参见图11,在本发明的一种实施方式中,可选地,沿沟道区201的长度方向X,绝缘主区301的尺寸与栅极40的尺寸相等,即沟道区301的尺寸与栅极40的尺寸相等,绝缘尾区302位于绝缘主区301的两侧。可选地,沿沟道区201的长度方向X,栅极40的长度范围为3um-5um,位于栅极40一侧的绝缘尾区302的长度范围为500nm-800nm。这样设置,有利于过渡区202的长度与绝缘尾区302的长度相等,从而有利于绝缘主区301的长度与沟道区201的长度相等,有利于沟道区201的长度与设计长度相等。

继续参见图11,在本发明的一种实施方式中,可选地,绝缘尾区302关于绝缘主区301对称,以有利于形成结构对称的薄膜晶体管。

在上述各实施例的基础上,可选地,半导体层20的材料包括氧化物。可选地,氧化物包括铟镓锌氧化物(Indium Gallium Zinc Oxide,IGZO)、铟锡锌氧化物(Indium TinZinc Oxide,ITZO)或氧化铟锌(Indium Zinc Oxide,IZO)中的至少一种。其中,氧化物半导体可以利用等离子体等刻蚀气体破坏氧化物内部的一些化学键,导致氧化物内的氧释放出来,氧空位含量增多,实现氧化物的导体化。以及栅极绝缘层30和栅极40的刻蚀可以采用干刻工艺,干刻工艺采用等离子体等刻蚀气体。这样在采用等离子体刻蚀形成栅极绝缘层30和栅极40的同时,半导体层20的源漏区203被等离子体处理而电阻降低,进行导体化,即利用干刻工艺对半导体层20进行导体化。这样设置,无需采用额外的步骤对半导体的源漏区203进行单独的导体化,从而有利于简化薄膜晶体管的制备工艺。

在上述各实施例的基础上,可选地,薄膜晶体管为N型薄膜晶体管或P型薄膜晶体管。

在上述各实施例的基础上,可选地,薄膜晶体管为氧化物薄膜晶体管。或者,可选地,薄膜晶体管为低温多晶氧化物(Low Temperature Polycrystalline Oxide,LTPO)薄膜晶体管。LTPO薄膜晶体管包括氧化物薄膜晶体管和低温多晶硅薄膜晶体管,氧化物薄膜晶体管位于低温多晶硅薄膜晶体管之上,或者低温多晶硅薄膜晶体管位于氧化物薄膜晶体管之上。其中,在形成的LTPO薄膜晶体管中,低温多晶硅薄膜晶体管的源漏电极与氧化物薄膜晶体管的源漏电极可以同层设置,也可以异层设置,在实际应用中可以根据需要进行设定。

本发明实施例还提供了一种显示面板,显示面板可以为有机发光二极管显示面板(Organic Light-Emitting Diode,OLED)、液晶显示面板(Liquid Crystal Display,LCD)、微发光二极管显示面板(Micro Light Emitting Diode,Micro LED)、量子点发光二极管(Quantum Dot Light Emitting Diodes,QLED)或电泳显示面板(ElectrophoresisDisplay,EPD)中的至少一种。显示面板包括如本发明任意实施例所提供的薄膜晶体管,该薄膜晶体管可设置于显示面板的阵列基板的电路中,该电路可以是多路复用电路、像素电路或移位寄存器电路等。该薄膜晶体管可以在显示面板的电路中起到开关晶体管的作用或驱动晶体管的作用。由于本发明实施例提供的显示面板包括本发明任意实施例所提供的薄膜晶体管,其原理和产生的效果类似,不再赘述。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 一种薄膜晶体管、显示面板及薄膜晶体管的制备方法

- 薄膜晶体管的制备方法、薄膜晶体管及显示面板