SiC半导体元件的制造方法及SiC半导体元件

文献发布时间:2023-06-19 18:27:32

技术领域

本发明涉及一种SiC(碳化硅)半导体元件的制造方法及SiC半导体元件。

背景技术

在使用了SiC衬底的MOS型晶体管(SiC MOSFET)中,当通过热氧化将SiO

作为降低界面缺陷密度的方法,在专利文献1中公开了如下方法:在SiC衬底的表面上沉积Si薄膜,然后使Si薄膜氧化而形成SiO

作为降低界面缺陷密度的其他方法,在非专利文献1中公开了如下方法:通过热氧化将SiO

现有技术文献

专利文献

专利文献1:日本公开专利公报特开平11-067757号公报

非专利文献

非专利文献1:G.Y.Chung et al.,IEEE Electron Device Lett.,vol.22,176(2001)

非专利文献2:K.Kawahara et al.,Appl.Phys.Express,vol.6,051301(2013)

非专利文献3:F.Devynck et al.,Phys.Rev.B,vol.84,235320(2011)

非专利文献4:K.Kawahara et al.,J.Appl.Phys.vol.113,033705(2013)

发明内容

-发明要解决的技术问题-

虽然利用上述在先技术文献中所公开的方法,能够大幅度地降低SiO

本发明正是为解决上述技术问题而完成的,其主要目的在于:提供一种SiC半导体元件的制造方法,该方法能够大幅度地降低SiO

-用以解决技术问题的技术方案-

本发明所涉及的SiC半导体元件的制造方法包括:在1200℃以上的温度下使用H

-发明的效果-

根据本发明,能够提供一种SiC半导体元件的制造方法,该方法能够大幅度地降低SiO

附图说明

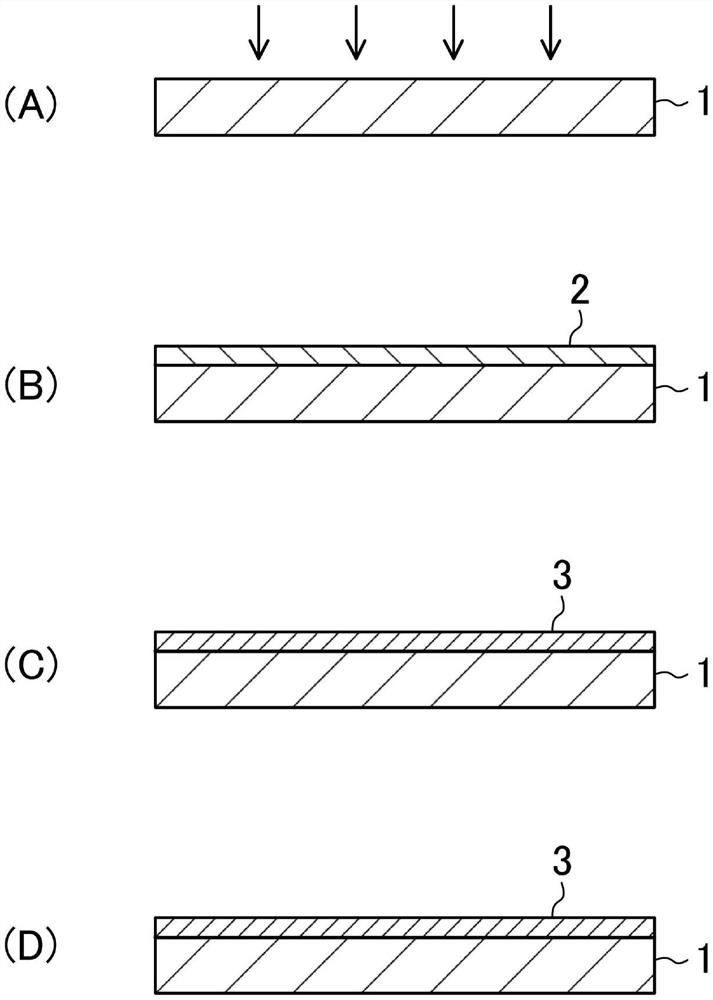

图1(A)~图1(D)是示出本发明的一实施方式中的SiC半导体元件的制造方法的图;

图2是示出SiO

图3是示出存在于SiC衬底侧的缺陷的种类的曲线图;

图4是示出存在于SiC衬底侧的缺陷的种类的曲线图;

图5是示出SiO

图6是示出SiO

图7是示出SiO

图8是示出界面缺陷密度对H

图9是示出界面缺陷密度对N

图10是示出SiO

图11(A)~图11(C)是示出本发明的其他实施方式中的SiC半导体元件的制造方法的图;

图12是示出界面缺陷密度对H

图13是示出界面缺陷密度对N

图14是示出SiO

图15是示出在富Si气氛中高温H

具体实施方式

在说明本发明的实施方式之前,先说明想到本发明的经过。

在使用SiC衬底制造半导体元件时,通常会在半导体元件的制造工序开始之前或在制造工序的中途进行下述工序,即:对SiC衬底的表面进行牺牲氧化之后,用氢氟酸等药液除去形成在SiC衬底的表面上的氧化膜。由此,能够除去意外附着到表面上的杂质、最表面附近的SiC晶体的损伤(化学组成的偏差等),能够实现半导体元件的特性的稳定化、成品率的提高。

确实,在进行牺牲氧化之后除去氧化膜,对于除去附着到SiC衬底的表面上的杂质、最表面附近的SiC晶体的损伤等是有效的,但是有可能在SiC衬底的表面上残留有很多缺陷。实际上,已知如果使SiC晶体氧化,则在SiC表面附近就会产生高密度的点缺陷(非专利文献2)。此外,也有理论计算报告指出:如果使SiC晶体氧化,则在氧化膜与SiC之间的界面就会产生由于过剩的C原子引起的界面缺陷(非专利文献3)。如上所述,能够认为:即使稍微对SiC晶体进行氧化,也会产生大量的界面缺陷和SiC侧的点缺陷,这是不可避免的。

为了对此进行验证,本申请的发明人等研究了:作为将SiO

(验证试样的制作)

为了验证高温H

如图1(A)所示,作为预处理工序,使用高温H

需要说明的是,作为SiC衬底1,使用了在SiC衬底1上形成有SiC外延层(未图示)的衬底。此处,SiC衬底1采用n型4H-SiC(0001)衬底,将SiC外延生长层的施主浓度设为5×10

接着,如图1(B)所示,通过CVD法在SiC衬底1上沉积了Si薄膜2。在SiH

接着,如图1(C)所示,对Si薄膜2进行热氧化,形成了SiO

接着,如图1(D)所示,在N

需要说明的是,为了便于比较,制作了以下试样:没有进行图1(A)所示的使用高温H

(对界面缺陷密度的分析)

对于利用图1(A)~图1(D)所示的方法形成的SiO

图2是示出其结果的曲线图,横轴表示导带底(E

如图2所示,进行了作为预处理的H

特别是在比导带底(E

根据上述的分析结果可知,在对表面进行牺牲氧化之后除去了氧化膜的SiC衬底1的表面残留有很多缺陷,为了效率良好地除去这些缺陷,使用高温H

(对于SiC衬底侧缺陷的分析)

对于利用图1(A)~图1(D)所示的方法形成的SiO

图3是示出其结果的曲线图,横轴表示温度,纵轴表示DLTS信号。此处,C所示的曲线表示的情况为:进行了作为预处理的使用高温H

如图3所示,在进行了使用N

根据上述结果发现,在通过使用NO气体的热处理进行了界面氮化处理的情况下,在界面氮化处理中,SiC衬底1的表面稍微被氧化。另一方面,发现在通过使用N

上述结果还表明,即使通过高温H

例如,在上述内容中,说明了已进行了使用NO气体的界面氮化处理的试样,但在以下试样中也观测到同样的DLTS峰N1、N2、N3,该试样是:进行使用高温H

也就是说,即使进行高温H

需要说明的是,验证中使用的试样是使用n型SiC衬底制作的试样,而对于使用p型SiC衬底并利用与图1(A)~图1(D)所示的方法相同的方法制作的试样,也采用DLTS法对存在于SiC衬底侧的缺陷的种类进行了分析。

图4是示出其结果的曲线图,C所示的曲线表示的情况为:进行了作为预处理的H

如图4所示,在进行了使用N

根据上述结果可知,在使用p型SiC衬底的情况下,也是在通过使用NO气体的热处理进行界面氮化处理的情况下SiC衬底1的表面被氧化,而在通过使用N

表1示出箭头N1~N3、P1所示的缺陷的种类OX-N1、OX-N2、OX-N3、OX-P1的能量位置和缺陷密度。此处,E

[表1]

根据表1能够推测:在进行了作为预处理的H

也就是说,如图3、图4所示,在进行了作为预处理的H

(对于SiO

对于利用图1(A)~图1(D)所示的方法形成的SiO

(A)对由电压应力引起的C-V特性偏移的评价

对于利用图1(A)~图1(D)所示的方法形成的SiO

图5是示出其结果的曲线图,横轴表示电压,纵轴表示电容。如图5所示,即使对SiO

(B)对于SiO

对于利用图1(A)~图1(D)所示的方法形成的SiO

图6是示出其结果的曲线图,横轴表示电场(V/t

(C)SiO

为了验证使用N

图7是示出其结果的曲线图,横轴表示膜厚方向上的位置,零表示SiO

如图7所示,在SiO

根据上述结果可知,通过使用N

根据上述结果可知,通过在对表面进行牺牲氧化之后,使用高温H

(界面缺陷密度对H

图8是示出将使用高温H

如图8所示,可知在1200℃以上的温度下,界面缺陷密度大幅度地降低。另一方面,在1100℃的温度下,几乎没有观察到H

(界面缺陷密度对N

图9是示出在SiC衬底1的表面上形成SiO

如图9所示,可知在1350℃以上的温度下,界面缺陷密度大幅度地降低。另一方面,在低于1350℃的温度下,几乎没有观察到N

图10是示出将在N

如图10所示,在1350℃以上的温度下进行界面氮化处理时,在SiC衬底与SiO

如上所述,本实施方式中的SiC半导体元件的制造方法包括:在1200℃以上的温度下用H

(其他实施方式)

在上述实施方式中,SiO

也就是说,如果在使用高温H

图11(A)~图11(C)是示出在不使SiC衬底氧化的条件下将SiO

如图11(A)所示,作为预处理工序,使用高温H

需要说明的是,作为SiC衬底1,能够使用在SiC衬底1上形成有SiC外延层(未图示)的衬底。此外,优选在预处理工序之前,在对SiC外延层的表面进行牺牲氧化之后,除去氧化膜。需要说明的是,由于后述的理由,优选在富Si气氛中进行使用H

接着,如图11(B)所示,通过等离子体CVD法在SiC衬底1上沉积SiO

需要说明的是,也可以采用热CVD法进行SiO

即使在上述那样的条件下进行SiO

接着,如图11(C)所示,在N

(界面缺陷密度对H

图12是示出利用图11(A)~图11(C)所示的方法形成SiO

如图12所示,可知在1200℃以上的温度下,界面缺陷密度大幅度地降低。另一方面,在1100℃的温度下,几乎没有观察到H

(界面缺陷密度对N

图13是示出将SiO

如图13所示,可知在1400℃以上的温度下,界面缺陷密度大幅度地降低。另一方面,在1300℃的温度下,几乎没有观察到N

(SiO

图14是示出对SiO

如图14所示,在使用高温H

另一方面,在使用NO气体使界面氮化的情况下,也在SiO

(富Si气氛中的高温H

如上所述,即使在SiC衬底1不被氧化的条件下在SiC衬底1上沉积了SiO

图15为曲线图,其示出:当在富Si气氛中进行了使用高温H

此处,在H

如图15所示,在富Si气氛中进行了使用高温H

对于在富Si气氛中进行了使用高温H

如上所述,本实施方式中的SiC半导体元件的制造方法包括:在富Si气氛中,在1200℃以上的温度下使用H

(SiC半导体元件)

能够将利用本实施方式的制造方法形成的SiO

在比导带底低0.3eV的能量位置附近的、SiC衬底与SiO

在存在于SiC衬底侧的点缺陷中,比导带底低1.0eV的能量位置处的点缺陷密度、以及比价带顶高0.7eV的能量位置处的点缺陷密度分别在5×10

以上通过优选的实施方式对本发明进行了说明,然而上述内容并不是限定性说明,当然也能够进行各种改变。例如,在上述实施方式中,将SiC外延层形成在SiC衬底的表面上,将SiO

此外,在上述实施方式中,使用了在对表面进行牺牲氧化之后除去了氧化膜的SiC衬底,但也能够将本发明的制造方法应用于没有实施牺牲氧化的SiC衬底。

-符号说明-

1 SiC衬底

2 Si薄膜

3、4 SiO

- 半导体元件及其制造方法

- 半导体元件与其制造方法

- 半导体元件及其制造方法

- 半导体元件及其制造方法

- SiC衬底、SiC衬底的制造方法、SiC半导体装置以及SiC半导体装置的制造方法

- 用于通过植入法掺杂的SiC半导体区的热自愈方法和SiC基半导体元件