用于存储器应用的埋置信号导线

文献发布时间:2023-06-19 18:35:48

相关申请

本申请要求2020年6月24日提交的名称为“Method of Fabrication of BuriedSignal Wires in Memories”的临时专利申请第63/043,211号的优先权和权益,该临时专利申请据此全文以引用方式并入。而且,本申请要求2021年4月16日提交的名称为“BuriedInterconnects for Sub-5nm SRAM Design”的临时专利申请第63/175,854号的优先权和权益,该临时专利申请据此全文以引用方式并入。

背景技术

本节旨在提供与理解本文所述的各种技术相关的信息。如本节的标题所暗示的,这是对相关技术的讨论,绝不应当暗示其是现有技术。一般来讲,相关技术可被认为是或可不被认为是现有技术。因此,应当理解,本节中的任何陈述均应按此意义来理解,并且不作为对现有技术的任何认可。

在一些常规存储器设计中,传统互连导线通常位于基板上方且具体来说晶体管(诸如MOSFET(金属氧化物半导体场效应晶体管))上方的多个层中,以实现集成电路(IC)中的存储器部件之间的互连。遗憾的是,这些常规存储器设计是高度拥塞的且常常由于寄生电阻及电容效应而导致性能降低。而且,传统的布线层通常是指位于集成电路(IC)的基板和其他部件上方的前侧布线层,这进一步导致现代物理布局设计的拥塞问题。因此,需要以允许现代电路设计中的存储器设备之间的改进布线的方式来改进面积效率且减少导线拥塞。

附图说明

本文参考附图描述了各种存储器布局方案和技术的具体实施。然而,应当理解,附图仅示出了本文所述的各种具体实施,并且不旨在限制本文所述的各种技术的实施方案。

图1示出了根据本文所述的各种具体实施的具有可寻址存储元件的存储器架构的图。

图2至图5示出了根据本文所述的各种具体实施的具有埋置金属线的存储器架构的各种图。

图6示出了根据本文所述的各种具体实施的用于提供具有埋置金属线的存储器架构的方法的图。

具体实施方式

本文中所描述的各种具体实施涉及用于在多层结构配置的物理布局设计中提供具有埋置信号线的存储器架构的方案和技术。举例来说,本文中所描述的各种物理布局设计方案和技术可提供包括各种类型的随机存取存储器(RAM)架构和配置的增强型存储器结构。而且,本文中所描述的各种具体实施涉及一种用于在各种制造的存储器设备(诸如例如,包括SRAM、DRAM、eDRAM、MRAM、ReRAM、CeRAM和NVRAM的随机存取存储器(RAM)设备)以及各种其他制造的存储器设备(诸如例如,PCM、FLASH和ROM)中制造埋置信号导线的方法。

可通过实施如本文中所描述的存储器架构方案和技术来实现各种优点和益处。本文所描述的各种配置提供用于制造埋置在集成电路内的存储器信号导线的方案和技术。例如,埋置信号导线可以设置在集成电路的基板内,其中埋置信号导线可以减少金属布线层的拥塞。与传统的非埋置导线相比,埋置信号导线还可以提供低电阻和/或低电容存储器信号布线,从而减少信号延迟和能量消耗。而且,在存储器设备中使用埋置信号导线可通过同时减少存储器存取时间、改善循环时间、减少动态能量消耗且还增加存储密度而对存储器性能具有显著影响。另外,由于埋置信号导线层不那么拥塞,信号可以更宽和/或设置得更分开以减小电阻。在一些情况下,可以通过使埋置信号导线层更高来进一步减小导线的电阻,并且可以将埋置信号导线应用于单向和非单向信号。

在各种具体实施中,当与相同导线宽度的类似非埋置信号导线相比时,由于减少的信号耦合,埋置信号导线可具有较低的电容和电阻。而且,用于存储器字线、位线和/或时钟信号的各种其他关键信号导线可以被实现为埋置信号导线,以便当与实现使用传统基板上方连接的非埋置信号导线相比时提供改进的存储器性能和较低的能量消耗。

本文将参考图1至图6描述提供具有埋置信号线的存储器架构的各种具体实施。

图1示出了根据本文所述的各种具体实施的具有可寻址存储元件144的存储器架构104的图100。

在各种具体实施中,存储器架构104可被实现为具有各种集成电路(IC)部件的系统或设备,这些IC部件被布置和耦接在一起作为提供物理电路设计和各种相关结构的部分的组装或组合。在一些情况下,将存储器架构104设计、提供、制造和/或生产为集成系统或设备的方法可涉及使用本文所述的各种IC电路部件,以便实现与其相关联的各种相关制造方案和技术。此外,存储器架构104可与单个芯片上的计算电路和相关部件集成,并且存储器架构104可在用于各种汽车、电子、移动、服务器和物联网(IoT)应用包括远程传感器节点的各种嵌入式系统中实现和/或并入。

如图1中所示,存储器架构104可包括具有可寻址存储元件144(诸如例如,各种类型的位单元或其他存储器单元)的阵列的存储器电路108。在一些具体实施中,存储器电路108可指以地址存取的可寻址存储器存储元件144的二维(2D)阵列,该地址具有用作行地址120的地址的第一部分和用作列地址128的地址的第二部分。行地址128(Aj到Ak-1)可被提供给行解码器114并由其解码,并且对应的字线(WL)116可被激活。激活的字线导线116用于选择要被激活的存储元件114的对应行,并且来自激活行的数据也可以被写入到对应的位线导线120或从该对应的位线导线读取。列地址128(A0到Aj-1)可被提供给列多路复用器118并由其解码,并且对应位线(BL)120可被激活。在此情况下,列地址128(A0到Aj-1)可用于从对应位线(BL)120选择适当数据,以便在数据总线138上驱动所选数据。此外,存储器电路108可使用时钟来同步存储器存取事件(读/写操作),并且时钟对于存储器存取定时(诸如例如,存储器存取时间、循环时间、设置和/或保持时间)来说也可为关键的。

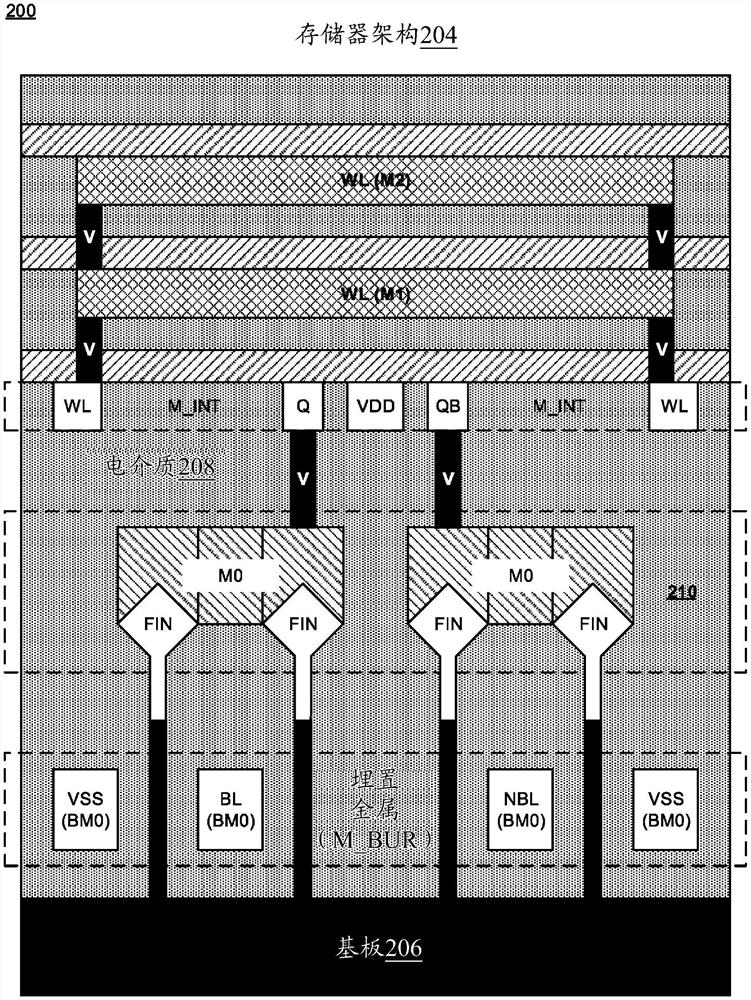

图2示出了根据本文所述的各种具体实施的具有埋置金属线(M_BUR)的存储器架构204的图200。

在各种具体实施中,存储器架构204可被实现为具有各种集成电路(IC)部件的系统或设备,这些IC部件被布置和耦接在一起作为提供物理电路设计和各种相关结构的部分的组装或组合。在一些情况下,将存储器架构204设计、提供、制造和/或生产为集成系统或设备的方法可涉及使用本文所述的各种IC电路部件,以便实现与其相关联的各种相关制造方案和技术。而且,存储器架构204可与单个芯片上的计算电路和相关部件集成,并且存储器架构204可在用于各种汽车、电子、移动、服务器和物联网(IoT)应用包括远程传感器节点的各种嵌入式系统中实现和/或并入。

如图2中所示,存储器架构204可包括多层存储器结构,其具有基板206以及埋置于基板206或电介质208内以用于传输电信号的一个或多个信号导线(例如,BM0)。一个或多个信号导线(例如,BM0)可被称为埋置金属(M_BUR),其设置在基板206内并且还被介电材料208围绕(或包围)。在一些情况下,电信号可指各种类型的关键信号(字线信号、位线信号和时钟信号),所述关键信号被传输到用于存储器相关应用的存储器结构。

在一些具体实施中,存储器结构可指设置在基板206上的晶体管210(诸如例如,鳍式场效应晶体管(FinFET)),并且电信号可指传输到用于存储器相关应用的晶体管210的各种关键信号。在一些情况下,信号导线(BM0)可通过埋置通孔(BV)或穿硅通孔(TSV)耦接到晶体管210。而且,信号导线(BM0)可以指埋置在基板206中的字线(WL)、位线(BL)或时钟信号线(CSL)。在一些情况下,信号导线(BM0)可指埋置在用介电材料208填充的电介质区域中的一个或多个位线(例如,BL/NBL)。晶体管210可具有形成于基板206上方的一个或多个多晶栅(PG)区域。

在其他具体实施中,信号导线(BM0)可指埋置在基板206中以用于将电信号传输到晶体管210(或存储器单元结构)的多个信号导线(例如,BM0:VSS、BL、NBL)。关键信号可指传输到用于存储器相关应用的存储器单元结构的数据信号或时钟信号。而且,关键信号可指在至少一个字线(WL)上传输到存储器单元结构的一个或多个字线(WL)信号,并且关键信号可指在至少一个位线(BL)上传输到存储器单元结构的一个或多个位线(BL)信号。而且,多个信号导线可以指通过第一埋置通孔(BV)耦接到晶体管210的栅极的埋置字线(WL),并且多个信号导线也可以指通过第二埋置通孔(BV)耦接到晶体管210的漏极的埋置位线(BL/NBL)。而且,在一些情况下,埋置字线(WL)可以指通过第一埋置通孔(BV)耦接到晶体管210的栅极的埋置全局字线(GWL)。本文参考图3至图5更详细地描述埋置WL和埋置BL。

在各种具体实施中,多个信号导线可包括埋置在基板206内的至少一个时钟信号线,并且该关键信号可指在至少一个时钟信号线上传输到存储器单元结构(例如,210)的一个或多个时钟信号。多个信号导线还可指埋置在基板206内以用于将关键信号(例如,WL/BL/NBL信号)传输到存储器单元结构(例如,210)的至少一个关键信号线(例如,WL、BL、NBL)。而且,该多个信号导线可包括埋置在基板206内以用于将功率信号(例如,VSS/VDD信号)传输到存储器单元结构(例如,210)的至少一个功率信号线(例如,VSS、VDD)。而且,在各种情况下,至少一个关键信号线(例如,WL、BL、NBL)与至少一个功率信号线(例如,VSS、VDD)分离。本文参考图3至图5更详细地描述埋置关键信号线。

而且,如图2中所示,存储器结构可包括设置在多个层(例如,M0、M_INT、M1、M2)中的多个字线(WL),并且该多个字线(WL)可经由通孔(V)耦接在一起。在一些具体实施中,通孔(V)可指埋置于介电材料208中的埋置通孔(BV)。而且,在中间金属层(M_INT)中,可以在其中设置用于字线(WL)、输出线(Q/QB)和源电源线(VDD)的其他信号线。而且,在一些情况下,输出线(Q/QB)可通过埋置在介电材料208内的通孔(V)或埋置通孔(BV)耦接到存储器单元结构(例如,210)。

在各种具体实施中,存储器结构可指各种制造的存储器设备,诸如例如包括SRAM、DRAM、eDRAM、MRAM、ReRAM、CeRAM和NVRAM的随机存取存储器(RAM)设备,以及各种其他制造的存储器设备,诸如例如PCM、FLASH和ROM。而且,在各种具体实施中,存储器单元结构(例如,210)可指各种类型的位单元,诸如例如SRAM位单元、DRAM位单元、eDRAM位单元、MRAM位单元、ReRAM位单元、PCM位单元、CeRAM位单元、FLASH位单元、NVRAM位单元或ROM位单元。

图3示出了根据本文所述的各种具体实施的具有埋置金属线(M_BUR)的存储器架构304的图300。应了解,如图3中所示的存储器架构304可在范围和特征上类似于图2中所示的存储器架构204,其中类似部件具有类似特征、特性及相关行为。

在各种具体实施中,存储器架构304可被实现为具有各种集成电路(IC)部件的系统或设备,这些IC部件被布置和耦接在一起作为提供物理电路设计和各种相关结构的部分的组装或组合。在一些情况下,将存储器架构304设计、提供、制造和/或生产为集成系统或设备的方法可涉及使用本文所述的各种IC电路部件,以便实现与其相关联的各种相关制造方案和技术。而且,存储器架构304可与单个芯片上的计算电路和相关部件集成,并且存储器架构304可在用于各种汽车、电子、移动、服务器和物联网(IoT)应用包括远程传感器节点的各种嵌入式系统中实现和/或并入。

如图3中所示,存储器架构304可包括多层存储器结构,其具有基板306以及埋置于基板306内以用于传输电信号的一个或多个信号导线(例如,BM0)。一个或多个信号导线(例如,BM0)可被称为埋置金属(M_BUR),其设置在基板306内并且还被介电材料308围绕(或包围)。在一些情况下,电信号可指各种类型的关键信号(字线信号、位线信号和时钟信号),所述关键信号被传输到用于存储器相关应用的存储器结构。

在一些具体实施中,如图3中所示的存储器架构304是指具有埋置位线信号导线(BM0)的多层存储器结构,该埋置位线信号导线具有距基板306的上表面的厚度360和深度370。埋置位线信号导线(BM0)可以包括埋置通孔(例如,BUR BL导线+BUR BL通孔)。在一些情况下,通孔是指物理电子电路的层之间的电连接,并且埋置通孔也可以是指埋置在基板306内的通孔。而且,存储器结构可指具有晶体管鳍(FIN)的FinFET型晶体管310,其中晶体管310是指用作开关或用作放大电子信号的信号放大器的半导体设备。在一些情况下,FinFET可具有至少三个端子,诸如例如源极端子、栅极端子和漏极端子。在先进工艺技术中,FinFET型晶体管可指设置在基板306上方且类似于鳍的三维(3D)存储器结构。

在一些情况下,晶体管310的鳍(FIN)形成晶体管310的源极和漏极,并且金属布线层可设置在基板306上方。金属布线层提供电互连,并且金属布线层可用于形成电子电路。而且,如图3中所示,存储器结构可具有多个金属布线层(例如,M0、M1等),其中最靠近基板306的金属层为第一金属层(M0),附加金属层基于其相对于基板306的位置而递增编号(例如,M1)。在一些情况下,可在基板206上方形成多晶栅(PG),并且可在另一金属层(M1)中形成字线(WL)。而且,其他字线(WL)和输出线(Q)可以形成在中间金属层(M_INT)中。

在一些情况下,埋置位线导线(BUR BL导线)可实现为埋置信号导线,并且埋置位线导线(BL)及其互补埋置位线导线(NBL)可使用埋置通孔(BUR BL通孔)耦接到晶体管310的漏极。在一些情况下,埋置位线导线(BL/NBL)可指平行于晶体管鳍(FIN)延伸的单向导线,其提供在晶体管鳍(FIN)之间埋置并耦接埋置位线导线(BUR BL导线)。在一些具体实施中,与非埋置位线导线相比,以此方式埋置位线导线可导致较低电容及较低单元读取延迟。而且,在一些具体实施中,埋置位线导线可进一步增加用于一些存储器应用的存储器位单元密度。在一些其他情况下,字线(WL)可实现为埋置信号导线,并且字线(WL)导线可为跨越存储器结构而设置的单向导线。

图4示出了根据本文所述的各种具体实施的具有埋置金属线(M_BUR)的存储器架构404的图400。应了解,如图4中所示的存储器架构404可在范围和特征上类似于图2至图3中所示的存储器架构204、304,其中类似部件具有类似特征、特性及相关行为。

在各种具体实施中,存储器架构404可被实现为具有各种集成电路(IC)部件的系统或设备,这些IC部件被布置和耦接在一起作为提供物理电路设计和各种相关结构的部分的组装或组合。在一些情况下,将存储器架构404设计、提供、制造和/或生产为集成系统或设备的方法可涉及使用本文所述的各种IC电路部件,以便实现与其相关联的各种相关制造方案和技术。而且,存储器架构404可与单个芯片上的计算电路和相关部件集成,并且存储器架构404可在用于各种汽车、电子、移动、服务器和物联网(IoT)应用包括远程传感器节点的各种嵌入式系统中实现和/或并入。

如图4中所示,存储器架构404可包括多层存储器结构,其具有基板406以及埋置于基板406内以用于传输电信号的一个或多个信号导线(例如,BM0)。一个或多个信号导线(例如,BM0)可被称为埋置金属(M_BUR),其设置在基板406内并且还被介电材料408围绕(或包围)。在一些情况下,电信号可指各种类型的关键信号(字线信号、位线信号和时钟信号),所述关键信号被传输到用于存储器相关应用的存储器结构。

在一些具体实施中,如图4中所示的存储器架构404是指具有埋置字线导线(BURWL导线)的多层存储器结构,该埋置字线导线还可实现为埋置全局字线导线(BUR GWL导线)。而且,埋置字线信号导线(BM0)可以包括埋置通孔(例如,BUR WL导线+BUR WL通孔),并且另一字线导线(WL)可以设在金属层(M1)中。在一些情况下,全局字线导线(BUR GWL导线)可指到字线(WL M1)的平行带,该字线可例如使用一个或多个埋置通孔(V)(诸如在存储器结构的开始和结束处)埋置且分接在各种位置处。埋置通孔(BUR WL通孔)可用于将埋置字线(BUR WL导线)耦接到晶体管410的多晶栅(PG),该多晶栅可设置在基板上方。

图5示出了根据本文所述的各种具体实施的具有埋置金属线(M_BUR)的存储器架构504的图500。应了解,如图5中所示的存储器架构504可在范围和特征上类似于图2至图4中所示的存储器架构204-404,其中类似部件具有类似特征、特性及相关行为。

在各种具体实施中,存储器架构504可被实现为具有各种集成电路(IC)部件的系统或设备,这些IC部件被布置和耦接在一起作为提供物理电路设计和各种相关结构的部分的组装或组合。在一些情况下,将存储器架构504设计、提供、制造和/或生产为集成系统或设备的方法可涉及使用本文所述的各种IC电路部件,以便实现与其相关联的各种相关制造方案和技术。而且,存储器架构504可与单个芯片上的计算电路和相关部件集成,并且存储器架构504可在用于各种汽车、电子、移动、服务器和物联网(IoT)应用包括远程传感器节点的各种嵌入式系统中实现和/或并入。

如图5中所示,存储器架构504可包括多层存储器结构,其具有基板506以及埋置于基板506内以用于传输电信号的一个或多个信号导线(例如,BM0)。一个或多个信号导线(例如,BM0)可被称为埋置金属(M_BUR),其设置在基板506内并且还被介电材料508围绕(或包围)。在一些情况下,电信号可指各种类型的关键信号(字线信号、位线信号和时钟信号),所述关键信号被传输到用于存储器相关应用的存储器结构。

在一些具体实施中,如图5中所示的存储器架构504是指具有垂直于晶体管鳍(FIN)设置的埋置背侧信号导线530的多层存储器结构。埋置背侧信号导线530实现在基板506的背侧上,并且埋置背侧信号导线530通过缩放的硅通孔(TSV)524耦接到另一埋置信号导线522。在此情况下,埋置信号导线522可耦接到埋置通孔520。

在一些具体实施中,埋置信号导线522、530可使用埋置通孔520或TSV耦接到晶体管510的源极、漏极或栅极,或耦接到其他埋置信号导线层、背侧导线层或非埋置信号导线层。在一些工艺技术中,埋置信号导线524可以埋置在距基板506的顶表面23nm到90nm之间。然而,在其他工艺技术中,可使用不同深度以便提供如本文中所讨论的类似技术范围和效果。而且,基板506可以具有并形成有预定义厚度560。

在各种具体实施中,基板506可由半导体材料形成,诸如例如硅(Si)或化合物III-V(诸如砷化镓(GaAs))或II-VI材料(例如氮化镓(GaN)、碳化硅(SiC)和蓝宝石)。此外,基板506可掺杂有例如硼、磷、砷、锑或它们的一些组合。在一些情况下,埋置信号导线522、530可由导电材料(诸如例如,铝、铜、钌或类似物)形成。此外,在一些情况下,埋置通孔520和TSV524可以在例如50nm-500nm的直径和1μm-10μm的厚度的范围内的尺寸由钨形成。

在各种具体实施中,如参考图1至图5所描述,时钟信号导线可被实现为埋置信号导线;然而,时钟信号导线可以不是单向的或规则的,并且因此,时钟信号导线可以使用多个埋置信号导线层来实现。在一些情况下,存储器结构可具有单向埋置信号导线时钟层,其使用埋置通孔耦接到存储器结构以便在较高非埋置金属层上在另一方向上跟踪信号栅极。

在一些具体实施中,当与非埋置信号导线相比时,埋置时钟信号导线可减小时钟信号导线的电阻和电容,从而导致改进的定时和/或增加的动态能量效率。而且,通过用埋置信号导线移除拥塞,较高非埋置层中的其他有线信号可提供较低电容、提供较低电阻和/或导致较低区域拥塞,例如,如果时钟信号导线在非埋置导线主导的存储器结构中设置为埋置信号导线。此外,在一些情况下,当高频切换时钟由于耦合电容而注入噪声时,埋置时钟信号导线还可导致向存储器结构中的各种其他关键信号提供较低噪声注入。

在一些具体实施中,存储器设备可包括允许每循环时间单个读-写存取的单个端口,或存储器设备可为多端口的以便例如允许多个同时读-写存取,例如,两端口SRAM允许同时读-写存取,并且双端口SRAM允许同时读-写存取(例如,多达两个同时读取、两个同时写入或同时读取和写入)。举例来说,具有N个端口的SRAM可支持N个同时存取。而且,具有多个端口的SRAM可以具有多组字线导线和多组位线导线。因此,在一些情况下,存储器设备可具有多组位线导线及多组字线导线,其中可根据本公开的方面埋置一个或多个位线导线和/或一个或多个字线导线。

在各种具体实施中,可使用各种其他存储器技术,诸如例如DRAM(动态随机存取存储器)、eDRAM(嵌入式动态随机存取存储器)、MRAM(磁性随机存取存储器)、ReRAM(电阻式随机存取存储器)、PCM(相变存储器)、CeRAM(相关电子随机存取存储器)、FLASH、NVRAM(非易失性随机存取存储器)或ROM(只读存储器)。举例来说,DRAM是一种易失性存储器,并且DRAM使用电容器来存储数据,其中电容器电荷缓慢地泄漏且因此必须周期性地刷新存储器单元。eDRAM是一种嵌入式DRAM,并且类似于DRAM,eDRAM使用电容器来存储数据,其中电容器电荷缓慢地泄漏并且因此必须周期性地刷新存储器单元。SRAM是易失性存储器,并且SRAM使用电容器和晶体管来存储数据,其中SRAM不必被周期性地刷新。MRAM为非易失性存储器,且MRAM使用磁畴来存储数据。ReRAM是非易失性存储器,并且ReRAM使用电介质的电阻来存储数据。PCM是非易失性存储器,并且PCM使用物质状态来存储数据。CeRAM是非易失性存储器,并且CeRAM使用电阻来存储数据。FLASH是非易失性存储器,并且Flash存储器使用浮栅晶体管,其中存在两种类型的FLASH存储器,即NAND FLASH或NOR FLASH。NVRAM覆盖任何非易失性存储器设备,例如FLASH、ReRAM、MRAM、PCM。ROM是非易失性只读存储器。

而且,在各种具体实施中,其他存储器信号导线可实现为埋置信号导线,例如全局控制信号,诸如预充电导线、芯片选择导线、写入启用导线或读取启用导线。在一些情况下,埋置信号导线可实现于平行于晶体管鳍设置的电介质区域中。埋置信号导线还可以使用埋置通孔耦接到晶体管,其中这种想法可以提供一层布线。而且,埋置信号导线可以不平行于晶体管鳍设置;或者在使用多层埋置信号导线的情况下,埋置信号导线可以制造在基板的背侧上并且使用缩放的TSV(sTSV)以及埋置导线和/或通孔的组合耦接到有源晶体管。此外,在一些情况下,还可使用微硅通孔(mTSV)连同背侧金属来耦接埋置信号导线。

图6示出了根据本文所述的具体实施的用于提供具有埋置金属线(M_BUR)的存储器架构的方法600的图。

应当理解,即使方法600指示特定的操作执行顺序,但在一些情况下,操作的各个部分也可以不同的顺序并且在不同的系统上执行。在其他情况下,可向方法600添加附加操作和/或步骤和/或从该方法省略附加操作和/或步骤。另外,方法600可在硬件和/或软件中实现。例如,如果在硬件中实现,则方法600可用如图1至图5中所述的各种部件和/或电路实现。而且,在其他情况下,如果在软件中实现,则方法600可被实现为被配置用于提供具有埋置金属线的存储器架构的程序或软件指令过程,如本文所述。在其他情况下,如果在软件中实现,则与实现方法600相关的指令可存储在存储器和/或数据库中。因此,在各种具体实施中,具有处理器和存储器的计算机或各种其他类型的计算设备可被配置为执行方法600。

如参考图6所述,方法600可用于制造和/或生产或者导致制造出和/或生产出集成电路(IC),该IC在如本文所述的物理设计中实现各种布局方案和技术,使用如本文所述的各种相关联设备、部件和/或电路来提供具有埋置金属线的存储器架构。

在框610处,方法600可被配置为提供设置在基板上的存储器单元结构。存储器单元结构可指设置在基板上的晶体管。在各种具体实施中,存储器单元结构是指SRAM位单元、DRAM位单元、eDRAM位单元、MRAM位单元、ReRAM位单元、PCM位单元、CeRAM位单元、FLASH位单元、NVRAM位单元或ROM位单元。

在框620处,方法600可被配置为将信号导线埋置基板中以用于将电信号传输到存储器单元结构。在一些具体实施中,电信号可指经由用于存储器相关应用的埋置信号线传输到晶体管的关键信号。在其他具体实施中,电信号可指经由用于存储器相关应用的埋置信号线传输到晶体管的功率信号。

在框630处,方法600可被配置为制造具有存储器单元结构及埋置于基板中的信号导线的存储器设备,或至少导致其被制造。在各种具体实施中,存储器设备可指SRAM、DRAM、eDRAM、MRAM、ReRAM、PCM、CeRAM、FLASH、NVRAM或ROM。

在一些具体实施中,信号导线可用埋置通孔或硅通孔(TSV)耦接到晶体管。信号导线可以指埋置在基板中的字线、位线或时钟信号线。信号导线可以指埋置在填充有介电材料的浅沟槽隔离区域中的位线。

在一些具体实施中,信号导线可指埋置于基板中用于将电信号传输到晶体管的多个信号导线。该多个信号导线可包括通过第一埋置通孔耦接到晶体管的栅极的埋置字线,并且该多个信号导线可包括通过第二埋置通孔耦接到晶体管的漏极的埋置位线。埋置字线可以指通过第一埋置通孔耦接到晶体管的栅极的埋置全局字线。

在一些具体实施中,关键信号可指传输到用于存储器相关应用的存储器单元结构的数据信号和/或时钟信号。多个信号导线可以包括埋置在基板中的至少一个字线和至少一个位线。关键信号可指在至少一个字线上传输到存储器单元结构的一个或多个字线信号,并且关键信号可指在至少一个位线上传输到存储器单元结构的一个或多个位线信号。多个信号导线可包括埋置在基板中的至少一个时钟信号线,并且该关键信号是指在至少一个时钟信号线上传输到存储器单元结构的一个或多个时钟信号。

在一些具体实施中,多个信号导线可包括埋置信号线和埋置电源线的组合。多个信号导线可以具有埋置在基板中用于将关键信号传输到存储器单元结构的至少一个关键信号线,并且该多个信号导线可以具有埋置在基板中用于将功率信号传输到存储器单元结构的至少一个功率信号线。而且,至少一个关键信号线与至少一个功率信号线分离。

应当预期的是,权利要求的主题不限于本文提供的各种具体实施和/或图示,而是应该包括根据权利要求的那些具体实施的任一修改形式,包括具体实施的部分和参考不同具体实施的各个元件的组合。还应当理解,在任何此类具体实施的开发中,如在任何工程或设计项目中,应该作出许多具体实施特定的决策以实现开发者的特定目标,诸如例如符合系统相关的约束和/或业务相关的约束,这些约束可能在不同具体实施之间变化。此外,应当理解,此类开发工作可能是复杂且耗时的,但是尽管如此,对于受益于本公开的普通技术人员而言,这仍然是设计、制造和生产的常规任务。

本文描述了具有包括基板的存储器结构的设备的各种具体实施。该设备可以包括埋置或部分埋置在基板和电介质中的至少一者内以用于传输电信号的信号导线。

本文描述了具有设置在基板上的存储器单元结构的设备的各种具体实施。该设备可包括埋置或部分埋置在基板和电介质中的至少一者内以用于将关键信号传输到存储器单元结构的多个信号导线。

本文描述了一种方法的各种具体实施。该方法可提供设置在基板上的存储器单元结构。该方法可将信号导线埋置或部分埋置在基板中以用于将电信号传输到存储器单元结构。该方法可制造具有存储器单元结构及埋置或部分埋置在基板中的信号导线的存储器设备,或导致其被制造。

已经详细地参考了各种具体实施,其示例在附图和图示中示出。在以下具体描述中,阐述了许多具体细节以提供对本文提供的公开内容的透彻理解。然而,可以在没有这些具体细节的情况下实践本文提供的公开内容。在各种具体实施中,没有详细描述熟知的方法、规程、部件、电路和网络,以便不会不必要地模糊实施方案的细节。

还应当理解,虽然各个术语“第一”、“第二”等在本文中可用于描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分开。例如,第一元件可被称为第二元件,并且类似地,第二元件可被称为第一元件。此外,第一元件和第二元件分别均为元件,但它们不被认为是相同的元件。

在本文提供的本公开的描述中使用的术语是为了描述特定具体实施的目的,并且不旨在限制本文提供的公开内容。如本文中提供的公开内容和所附权利要求的描述中使用的,单数形式“一个”、“一种”和“该”旨在也包括复数形式,除非上下文另有明确指示。如本文所用,术语“和/或”是指并涵盖相关联的列出项目中的一者或多者的任何和所有可能组合。当在本说明书中使用时,术语“包括”、“包含”和/或“含有”指定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或它们的组的存在或添加。

如本文所用,根据上下文,术语“如果”可被解释为意指“当……时”或“在……时”或“响应于确定”或“响应于检测到”。类似地,根据上下文,短语“如果确定……”或“如果检测到[所述条件或事件]”可被解释为意指“在确定……时”或“响应于确定……”或“在检测到[所述条件或事件]时”或“响应于检测到[所述条件或事件]”。术语“上”和“下”;“上部”和“下部”;“向上”和“向下”;“在……下方”和“在……上方”;以及指示给定点或元件上方或下方的相对位置的各种其他类似术语可与本文所述的各种技术的各种具体实施结合使用。

虽然前述内容涉及本文所述的各种技术的具体实施,但是可以根据本文的公开内容想出其他和另外的具体实施,本文的公开内容可以由所附权利要求确定。虽然以特定于结构特征和/或方法动作的语言描述了本主题,但应当理解,所附权利要求中限定的主题不一定限于上述特定特征或动作。相反,上述的具体特征和/或动作被公开为实现权利要求的示例性形式。

- 用于管芯上控制存储器命令、时序和/或控制信号的系统和方法

- 信号转换单元、存储器以及应用于存储器的驱动方法

- 信号转换单元、存储器以及应用于存储器的驱动方法