利用H2等离子体的可流动膜固化

文献发布时间:2023-06-19 09:30:39

技术领域

本文描述的实施例大体上涉及半导体器件制造领域,并且更具体地,涉及对使用可流动化学气相沉积(FCVD)工艺沉积的非晶硅层进行原位等离子体处理的方法。

背景技术

本文描述的实施例大体上涉及半导体器件制造领域,并且更具体地,涉及对使用可流动化学气相沉积(FCVD)工艺沉积的非晶硅层进行原位等离子体处理的方法。

非晶硅(Amorphous silicon;a-Si)被广泛用于半导体器件制造中,包括作为牺牲材料,例如作为虚设栅极材料,或者作为沟槽填充材料,例如作为沟槽电容器材料。常规沉积的非晶硅通常是保形的,这意味着它通常在基板表面上或其中形成的开口表面上的特征上方具有均匀的沉积厚度。常规沉积的非晶硅的保形性质可导致在其所形成的特征中不希望地形成接缝或空隙。例如,接缝可形成在开口的超过一个垂直表面上沉积的非晶硅层在开口的中心相遇的位置,诸如在虚设栅极的形成期间。这些不希望的接缝可在后续基板处理期间裂开,并导致非晶硅特征的结构失效。在另一示例中,当常规沉积的保形非晶硅在非晶硅材料完全填充沟槽之前将其中的开口夹住时,可在高深宽比沟槽中形成空隙。类似于接缝,空隙可在后续基板处理期间暴露,并且或者可对器件性能或器件功能性产生负面影响。

在需要无缝和无空隙特征的应用中,FCVD非晶硅沉积工艺比常规非晶硅沉积工艺更具优势。不幸的是,使用FCVD工艺沉积的非晶硅,在下文中称为可流动非晶硅,比常规沉积的非晶硅具有不希望的较低致密性和在物理上更柔软,并且因此需要对密度的进一步处理(例如,固化)和增加膜的硬度。由于沉积与固化之间不同的处理温度要求以及晶片转移和温度稳定化要求,诸如UV固化的常规固化方法除了用于沉积FCVD非晶硅层的FCVD处理腔室之外还需要一个或多个处理腔室,并且因此是耗时和设备密集的。此外,UV固化可导致可流动非晶硅膜的实质收缩,诸如以体积计高达所沉积体积的70%的收缩,这在间隙填充应用中是特别不希望的,在间隙填充应用中非晶硅填充材料的收缩将导致所形成的特征中的不希望的空隙。

因此,本领域需要改良的对使用FCVD工艺沉积的非晶硅层进行固化的方法。

发明内容

本文描述的实施例大体上涉及半导体器件制造领域,并且更具体地,涉及对使用可流动化学气相沉积(FCVD)工艺沉积的非晶硅(a-Si)层(在下文中称为可流动非晶硅层)进行等离子体处理的方法。

在一个实施例中,一种处理基板的方法,包括:等离子体处理非晶硅层。等离子体处理非晶硅层包括:使实质上无硅的氢处理气体流入处理腔室的处理容积中,所述处理容积中具有设置在基板支撑件上的基板;形成实质上无硅的氢处理气体的处理等离子体;和将基板的表面上沉积有非晶硅层的基板暴露于处理等离子体。在此,使用FCVD工艺沉积非晶硅层。FCVD工艺包括:将基板定位在基板支撑件上;使处理气体流入处理容积中;形成处理气体的沉积等离子体;将基板的表面暴露于沉积等离子体;和在基板的表面上沉积非晶硅层。

在另一实施例中,一种处理基板的方法,包括:将基板保持在约-100℃与约100℃之间的温度;沉积非晶硅层;和等离子体处理非晶硅层。沉积非晶硅层包括:将基板定位在处理容积中设置的基板支撑件上;使处理气体流入处理容积中;通过将处理气体与电极在小于约300W的RF或其他交流频率功率下电容耦合来形成处理气体的沉积等离子体;将基板的表面暴露于沉积等离子体;和在基板的表面上沉积非晶硅层。在此,处理气体实质上无氧且实质上无氮。等离子体处理非晶硅层包括:使处理气体流入处理容积中;通过将处理气体与电极在约100W与约500W之间的RF或其他交流频率功率下电容耦合来形成处理气体的处理等离子体;和将非晶硅层暴露于处理等离子体长达大于约10秒的持续时间。在此,处理气体包含H

在另一实施例中,一种处理基板的方法包括:将基板保持在约-100℃与约100℃之间的温度;沉积非晶硅层;从处理容积中净化处理气体;和等离子体处理非晶硅层。沉积非晶硅层包括:将基板定位在处理容积中设置的基板支撑件上;使处理气体流入处理容积中,其中处理气体实质上无氧且实质上无氮;通过将处理气体与电极在小于约300W的RF或其他交流频率功率下电容耦合来形成处理气体的沉积等离子体;将基板的表面暴露于沉积等离子体;和在基板的表面上沉积非晶硅层。净化处理容积包括:停止处理气体的流动;熄灭沉积等离子体;使净化气体流入处理容积中;和在等离子体处理非晶硅层之前,从处理容积中排出净化气体。等离子体处理非晶硅层包括:使处理气体流入处理容积中,其中处理气体包含H

附图说明

为了可以详细地理解本公开的上述特征,可通过参考实施例更具体地描述上文简要概述的本公开内容,一些实施例在附图中示出。然而,应注意,附图仅示出本公开的典型实施例,并且因此不应被认为是对其范围的限制,因为本公开可允许其他同等有效的实施例。

图1是根据一个实施例的用于实践本文阐述的方法的示例性处理腔室的示意性截面图。

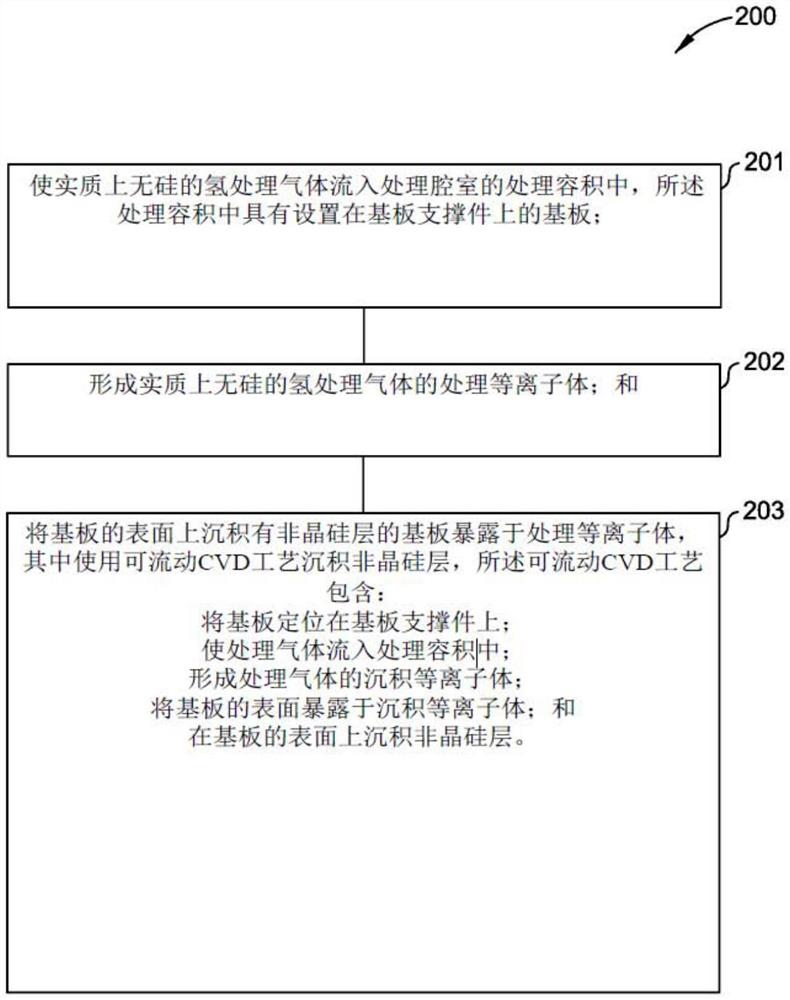

图2是根据一个实施例的对非晶硅层进行等离子体处理的方法的流程图。

具体实施方式

本文描述的实施例大体上涉及半导体器件制造领域,并且更具体地,涉及对使用可流动化学气相沉积(FCVD)工艺沉积的非晶硅(a-Si)层(在下文中称为可流动非晶硅层)进行等离子体处理的方法。

使用FCVD工艺沉积非晶硅有利地提供特征的无接缝形成和高深宽比开口的无空隙填充。然而,使用FCVD工艺沉积的非晶硅通常包含高氢含量,诸如大于约30原子%,这与具有较低氢含量的常规沉积的非晶硅膜相比不希望地导致较低的膜密度和膜品质。因此,本文的方法提供了通过在用于沉积可流动非晶硅层的同一处理腔室中将可流动非晶硅层暴露于原位等离子体来等离子体处理可流动非晶硅层。本文的等离子体处理通过使可流动非晶硅膜的Si-H键断裂来降低可流动非晶硅膜的氢含量,以使得具有悬空键的Si能够形成Si-Si键,从而产生期望的致密膜。在此,与需要单独处理腔室和单独基板处理操作的诸如UV固化的其他固化方法相比,在用于沉积可流动非晶硅层的同一处理腔室中执行等离子体处理可流动非晶硅层,导致总基板处理时间和个别基板处理操作减少。

图1是根据一个实施例的用于实践本文阐述的方法的示例性处理腔室的示意性截面图。可用于实践本文描述的方法的其他示例性沉积腔室包括可购自美国加利福尼亚州圣克拉拉市应用材料公司的

处理腔室100包括腔室盖组件101、一个或多个侧壁102和腔室基座104。腔室盖组件101包括腔室盖106、设置在腔室盖106中的喷头107和设置在腔室盖106与一个或多个侧壁102之间的电绝缘环108。喷头107、一个或多个侧壁102和腔室基座104一起界定处理容积105。穿过腔室盖106设置的气体入口109流体耦接至气体源110。具有从中穿过设置的多个开口111的喷头107用于将来自气体源110的处理气体均匀地分配至处理容积105中。喷头107电耦接至第一电源112,诸如RF电源,此电源经由与处理气体电容耦合而供电以点燃和维持处理气体的等离子体113。在此,RF功率具有约400kHz与约40MHz之间的频率,例如约400kHz或约13.56MHz。在其他实施例中,处理腔室100包含感应等离子体产生器,并且通过将RF功率电感耦合至处理气体来形成等离子体。

处理容积105经由真空出口114流体耦接至真空源,诸如至一个或多个专用真空泵,所述真空出口将处理容积105保持在低于大气压的条件下,并从中排出处理气体和其他气体。设置在处理容积105中的基板支撑件115设置在可移动支撑轴116上,所述可移动支撑轴密封地延伸穿过腔室基座104,诸如被腔室基座104下方的区域中的波纹管(未示出)围绕。在此,处理腔室100通常配置为促进经由一个或多个侧壁102中的一个侧壁中的开口118将基板116移送至基板支撑件115和从基板支撑件115移出,所述开口在基板处理期间通常用门或阀(未示出)密封。

在此,使用诸如电阻加热元件119的加热器和设置在基板支撑件115中的一个或多个冷却通道120中的一者或两者将设置在基板支撑件115上的基板117保持在期望的处理温度。通常,一个或多个冷却通道120流体耦接至冷却剂源(未示出),诸如具有相对较高电阻的改良水源或制冷剂源。在一些实施例中,基板支撑件115或其一个或多个电极(未示出)电耦接至向其供应偏置电压的第二电源121,诸如连续波(continuous wave;CW)RF电源或脉冲RF电源。

图2是根据一个实施例的对可流动非晶硅层进行等离子体处理的方法的流程图。在活动201处,方法200包括使实质上无硅的氢处理气体流入处理腔室的处理容积中。在此,将其上通过可流动CVD工艺形成有非晶硅层的基板设置在处理容积中设置的基板支撑件上。通常,氢处理气体包含氢源气体,诸如H

在活动202处,方法200包括形成氢处理气体的处理等离子体。在此,形成处理等离子体包含经由与由RF或其他交流频率电源供电的喷头电容耦合来点燃和维持氢处理气体的等离子体。在其他实施例中,经由与感应耦合等离子体(inductively coupled plasma;ICP)产生器电感耦合来形成处理等离子体,感应耦合等离子体产生器为诸如线圈围绕或覆盖耦接至RF或其他交流频率电源的处理容积的至少一部分。在此,处理等离子体是原位等离子体,即在设置于基板支撑件上的基板与喷头之间形成的等离子体。在一些实施例中,RF或其他交流频率功率介于约100W与约500W之间,或小于约500W。在一些实施例中,希望在等离子体处理非晶硅层期间将处理容积的压力保持在约1毫托与约2托之间。

在活动203处,方法200包括将基板的表面上沉积有非晶硅层的基板暴露于处理等离子体。通常,在基板的等离子体处理期间,基板支撑件处于升高的基板处理位置,在此为第一基板处理位置。在第一基板处理位置中,基板的表面与喷头的面向基板的表面间隔大于10mm的距离,诸如大于约20mm,或介于约10mm与约300mm之间,诸如介于约20mm与约300mm之间,介于约50mm与约300mm之间,或例如介于约20mm与约100mm之间,介于约100mm与约200mm之间,或介于约200mm与约300mm之间。

在此,等离子体处理非晶硅层包括将基板暴露于处理等离子体长达大于约10秒的持续时间,例如介于约10秒与约60秒之间。在此,使用FCVD工艺沉积非晶硅层,所述FCVD工艺包括:将基板定位在处理容积中设置的基板支撑件上;使处理气体流入处理容积中;形成处理气体的沉积等离子体;将基板的表面暴露于沉积等离子体;和在基板的表面上沉积非晶硅层。通常,在非晶硅层的沉积期间,基板支撑件处于第二基板处理位置。在第二基板处理位置中,基板与喷头的面向基板的表面间隔小于约20mm的距离,诸如介于约5mm与20mm之间,例如介于约7mm与约18mm之间。在一些实施例中,方法200包括使用FCVD工艺沉积非晶硅层。在一些实施例中,方法200包括通过在等离子体处理与非晶硅FCVD工艺之间降低基板支撑件将基板从第二处理位置移动至第一处理位置。

在此,处理气体包含一种或多种硅前驱物,诸如硅烷(SiH

在一些实施例中,基板是基板的表面上形成有多个特征的图案化基板。在一些实施例中,图案化基板在基板的表面上形成有多个开口,并且在基板的表面上沉积非晶硅层包括在多个开口中沉积非晶硅层。在一些实施例中,多个开口具有大于2:1的深宽比(深度与宽度比率),诸如大于5:1、大于10:1、大于20:1,例如大于25:1。在一些实施例中,开口的宽度小于约90nm,诸如小于约65nm、小于约45nm、小于约32nm、小于约22nm,例如小于约16nm,或在约16nm与约90nm之间。

通常,基板由适用于电子器件制造工艺中的任何材料和材料层形成,诸如硅、氧化硅、应变硅、绝缘体上硅(silicon on insulator;SOI)、掺碳氧化硅、非晶硅、掺杂硅、锗、砷化镓、玻璃、蓝宝石、金属、金属氮化物、金属合金和上述项的组合。

在此,形成沉积等离子体包括与喷头电容耦合,具有(待处理的基板表面的)小于约1W/cm

在一些实施例中,处理气体进一步包含载气或稀释气体,诸如He、Ar、H

在一些实施例中,方法包括在等离子体处理非晶硅层之前净化处理气体的处理容积。通常,净化处理气体和处理气体副产物的处理容积包括:停止处理气体的流动;熄灭沉积等离子体;使净化气体流入处理容积中;和在等离子体处理非晶硅层之前从处理容积中排出净化气体。通常,净化气体包含惰性气体,诸如He、Ar、Kr、N

期望地,上文描述的FCVD和后处理工艺提供可流动非晶硅膜,所述可流动非晶硅膜能够在基板表面上无接缝地形成特征,并且能够自底向上无空隙地填充基板表面中所形成的高深宽比开口,诸如具有小于90nm的宽度和大于约10:1的深宽比的开口。对可流动非晶硅层进行等离子体处理降低了可流动非晶硅层中的氢含量,并且增加了其中Si-Si键的数量,从而产生期望的致密膜。在一些实施例中,使用本文描述的FCVD方法沉积的非晶硅层的等离子体处理前氢含量大于约30原子%,而等离子体处理后氢含量小于约20原子%。此外,与诸如UV固化的其他固化方法相比,本文的等离子体处理方法导致较少的膜收缩。在一些实施例中,使用本文提供的等离子体处理方法的可流动非晶硅膜的收缩小于约50%,诸如小于约40%,例如小于约30%。在一些实施例中,在此形成的等离子体处理的非晶硅层具有不小于约4.1的折射率,诸如不小于约4,或不小于约3.9,例如不小于约3.8,其中较高折射率指示提高的膜品质。

尽管前述内容针对本公开的实施例,但可在不脱离本公开的基本范围的情况下设计本公开的其他和进一步实施例,并且本公开的范围由随附权利要求书确定。

- 利用H2等离子体的可流动膜固化

- 等离子体CVD膜中覆盖物的气体流动轮廓调节控制