具有埋入激光源的光子芯片

文献发布时间:2023-06-19 09:30:39

本发明涉及一种包括埋入激光源的光子芯片,并且涉及一种用于制造这种光子芯片的工艺。

光子芯片基本上位于在下面被称为“芯片平面”的平面中。

已知的光子芯片包括:

-衬底,其具有平行于芯片平面的上表面和下表面,该衬底在上表面和下表面之间包括:

·载体,其厚度大于50μm,该载体是没有光学部件的,

·光学层,其经由键合界面键合至载体,该光学层从上表面到键合界面依次包括:

-氧化物子层,以及

-封装子层,

·激光源,其被埋入光学层中,该激光源包括波导,该波导被制造在氧化物子层的面向键合界面的一侧上,并且该波导被封装在封装子层的介电材料中,该波导包括嵌入封装子层中的第一电接触部。

例如,在以下文章中描述了这种光子芯片:J.Durel et al.:"FirstDemonstration of a Back-Side Integrated Heterogeneous Hybrid III-V/Si DBRLasers for Si-Photonics Applications",IEEE International Electron DevicesMeeting(IEDM),December 2016.

该芯片的优点是制造特别简单。然而,希望在保持该优点的同时,通过改善激光源在其工作时所生成的热量的热耗散来进一步改进它。为此,本发明涉及这样一种光子芯片,其中该光子芯片包括形成通孔的互连金属网,该通孔在光学层中从键合界面延伸至波导的第一嵌入电接触部,该互连金属网包括金属通孔,该金属通孔将主要平行于芯片平面延伸的金属线彼此电连接,这些金属线在光学层内是彼此叠置的。

该光子芯片的实施例可以包括从属权利要求的特征中的一个或更多个。

本发明的另一主题是用于制造作为本专利申请的第一主题的光子芯片的工艺。

阅读下面的描述将更好地理解本发明。它仅是以非限制性示例的方式给出的,并参考了附图,其中:

-图1是包括光子芯片的系统的示意图;

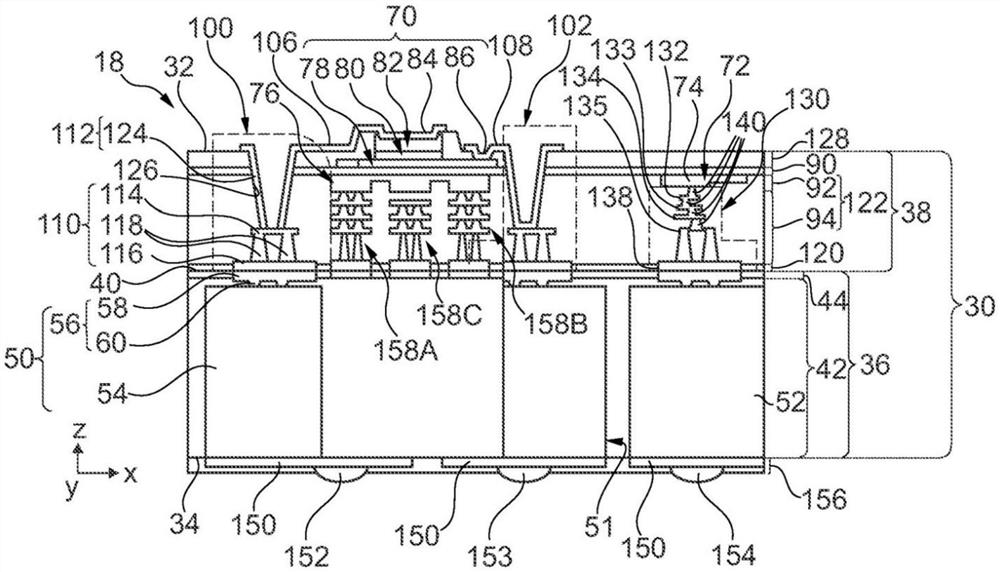

-图2是图1的系统的光子芯片的垂直截面示意图;

-图3是图1的系统的光子芯片的波导的横截面的垂直截面示意图的局部示图;

-图4是用于制造图1的系统的工艺的流程图;

-图5至11是图2的光子芯片的各种制造状态的垂直截面示意图;

-图12是图2的光子芯片的第一变型的垂直截面示意图;

-图13是图2的光子芯片的第二变型的垂直截面示意图;

在这些附图中,相同的附图标记被用于指定相同的元件。在本说明书的其余部分中,将不详细描述本领域技术人员已知的特征和功能。

图1示出了系统2的一部分,其经由焊料凸块的阵列6被焊接至印刷电路板4或PCB。为了简化说明,仅示出了阵列6的四个凸点8至11。

系统2通常采用平行六面体封装的形式,其内部装有电子和光子芯片。只有系统2的焊料凸块从该封装的下表面凸出。为了简化说明,在图1中未示出该封装。在其封装中的系统2被称为“封装中系统”。更一般地,系统2通常也被指定为“集成电路”。

在本说明书的剩余部分中,水平面在附图中由正交坐标系R的X方向和Y方向定义。坐标系R的Z方向对应于竖直方向。诸如“下”、“上”、“上方”、“下方”、“顶部”和“底部”之类的术语是相对于该Z方向定义的。

系统2在其下部包括载体14。阵列6的凸点直接放置在载体14的下表面上。载体14和阵列6一起被称为BGA(“球栅阵列”的缩写)。载体14的上表面包括可以焊接电子和/或光子芯片的焊盘。在图1的特定情况下,系统2包括一个电子芯片16和一个光子芯片18。这两个芯片16和18都被直接焊接至载体14的上表面。

电子芯片仅包括为了执行预设功能而彼此连接的电子部件。因此,电子芯片16是没有光学部件的。

相反,光子芯片18包括用于执行预设功能的光学部件。光学部件是在其使用的过程中生成或改变或引导光学信号的部件。通常,光学信号的波长为1200nm至1700nm。通常,这些光学部件中的至少一个是有源光学部件,即该光学部件:

-必须提供电流或电压才能正常工作,和/或

-将光学信号转换成电信号(光电探测器的情况),或者将电信号转换成光学信号(光学调制器的情况)。

在本实施例中,光子芯片18是没有电子部件的。

为了供应电力或交换电信号,系统2的光子芯片18和电子芯片16被电连接至位于载体14的上表面上的焊盘。芯片16和18还被电连接至印刷电路板4。为此,芯片16和18在此分别通过焊料微凸块阵列20和22被焊接至载体14的上表面的相应焊盘上。在图1中,阵列20和22由位于芯片16和18下面的一些焊料微凸块表示。例如,焊料微凸块被称为“C4凸块”。

载体14包括主要水平延伸的电连接件,例如连接件24。该连接件24将载体14的上表面的某些焊盘彼此电连接,以允许在焊接到这些焊盘上的芯片之间交换电信号或电力。载体14也被竖直连接件穿过,例如连接件26和28。通常,这些竖直连接件通向再分布层(RDL)的水平金属线上。在此,仅示出了该再分布层的一条线25。再分布层的水平线将竖直连接件中的一些电连接至阵列6的相应焊料凸块。竖直连接件特别允许向芯片16和18供电,并且还允许电信号与焊接到印刷电路板4的其他芯片交换。除了水平连接件和竖直连接件之外,载体14通常是没有任何电气或光学部件的。

图2更详细地示出了光子芯片18的一部分。芯片18包括具有水平上表面32和水平下表面34的衬底30。在这些表面32和34之间,衬底30从底部到顶部直接彼此堆叠地包括:

-互连层36,以及

-光学层38。

更精确地,经由基本位于水平平面中的键合界面40,层36和38被直接彼此键合。层38的上表面对应于上表面32,并且层36的下表面对应于下表面34。

层36主要由非导电材料制成。在本说明书中,“非导电材料”表示在20℃时其导电率低于10

在此,层36包括由未掺杂的晶体硅制成的子层42和直接在子层42上制造的表面子层44。在此,子层44由二氧化硅制成。

子层42的下表面对应于表面34。子层42的厚度相当大,以使其相当坚硬并且不会出现太多的弯曲。特别地,子层42的厚度足够允许对芯片18进行处理。因此层36形成了用于光学层38的载体。为此,子层42的厚度大于50μm或80μm或100μm。

子层42包括在下面称为“主通孔”的通孔,其允许形成竖直穿过衬底30的电连接件。每个主通孔从下端延伸到上端。下端与下表面34齐平。上端与键合界面40齐平。因此,这些主通孔恰好穿过互连层36的厚度。相反,主通孔不穿过光学层38并且也不会穿透到其中。

层36不包含埋入氧化硅层。因此,其导致可接受的弯曲的最小厚度小于包含这种埋入氧化硅层的层的厚度。较小的厚度特别允许减小与主通孔的高度成比例的主通孔的寄生电容。因此,优选地,子层42的厚度也小于150μm或100μm。

图2仅示出三个主通孔50至52。然而,一般来说,层36包括更高数量的主通孔。例如,所有主通孔是结构相同的,并且因此,下面将仅详细描述主通孔50。

主通孔50以传统的方式制造。例如,关于这个主题,读者可以查阅以下文章:KenMiyairi et al.:"Full integration and electrical characterization of 3DSilicon Interposer demonstrator incorporating high density TSVs andinterconnects",45th International Symposium on Microelectronics,2012。因此,下面仅描述通孔50的一些细节。

在本实施例中,通孔50从底部至顶部由以下形成:

-采用垂直条状件形式的下部54,以及

-采用互连金属网形式的上部56。

下部54从通孔50的下端竖直延伸到上部56。所述下部的水平横截面积在其整个高度上基本上是恒定的。其高度和其直径在下面分别表示为H1和D1。下部54穿过层36的至少80%,并且优选为至少90%或95%。由于层36的厚度较大,直径D1也较大,因此纵横比H1/D1小于10/1或8/1。具体地,制造纵横比高于10/1的通孔是很难的。在此,高度H1大于子层42的厚度的80%或90%或95%。在这些条件下,高度H1为80μm至142.5μm,并且通常为95μm至130μm。然后,直径H1通常为10μm至20μm。在子层42由诸如硅之类的半导体制成的情况下,优选地,下部54通过电绝缘材料的薄涂层与该半导体电绝缘。为了简化附图,未示出该电绝缘材料的涂层。下部54由金属制成,并且例如,由铜制成。

通孔50的上部56由互连金属网形成。因此,上部56由以下组成:

-主要水平延伸的金属线,以及

-将这些金属线彼此电连接的金属通孔。

将记得的是,“通孔”是竖直电连接件,即主要在垂直于光子芯片的平面的方向上延伸的电连接件。

在氧化硅子层44中制造金属线以及优选的金属通孔。在此,上部56包括:

-金属线58,其与键合界面40齐平,以及

-金属通孔60,其将该线58直接连接至下部54的顶部。

在本说明书中,“金属通孔”表示由金属制成的通孔,并且该通孔的直径小于3μm,并且通常小于1μm。金属通孔的高度也较小,即小于3μm或1μm。

在此,该金属是铜。这种互连金属网的结构对于本领域技术人员而言是已知的。这是再分布层或RDL的互连金属网的问题。

子层44的厚度通常小于10μm或3μm。

上部56的直径等于其金属通孔的最大直径。因此,上部56在此的直径小于10μm,并且通常小于3μm或1μm。

光学层38包括至少一个埋入该层中的光学部件。在此,光学部件从由光学调制器、激光源、波导、光电探测器、解复用器、光多路复用器组成的组中选择。在这组光学部件中,除了波导之外,其余都是有源光学部件。

在本示例性实施例中,仅示出了埋入在层38中的两个光学部件70、72。部件70是激光源,并且部件72是光学调制器。部件72能够根据电气控制信号修改穿过它的光学信号的相位、幅度或强度。这种光学调制器是已知的,并且因此未在此详细描述部件72。部件72包括用于接收电气控制信号的电接触部74。在此,电接触部74被嵌入在光学层38中。在本实施例中,电接触部74位于部件72的下表面上。因此,电接触部74面向键合界面40。在该配置中,电接触部仅能从光学部件72的下方进入电接触部74。

部件70是混合式III-V/硅激光源。部件70例如是分布反馈(DFB)激光器或分布布拉格反射(DBR)激光器。这种激光源对于本领域技术人员而言是已知的,因此未在此详细描述。在此,部件70特别包括波导76以及彼此直接叠置的:

-由n掺杂的半导体制成的下层78,

-有源层80,以及

-由p掺杂的半导体制成的上层82。

部件70还包括分别与上层82和下层78直接接触的上触点84和下触点86。

当在触点84和86之间施加适当的电势差时,有源层80生成由部件70发射的光学信号。

在此,下层78被光学耦合至波导76。为此,层78被放置在波导76上方并通过埋入氧化物的薄子层90与该波导76间隔开。子层90例如由二氧化硅制成。氧化物子层90的厚度小于100nm,并且优选小于50nm或20nm。因此,由有源层80生成的光学信号随后可以由波导76引导。

在本实施例中,波导76包括:

-中心肋状件142(图3),

-两个平行于中心肋状件142的凸起144A和144B(图3),以及

-两个边缘146A和146B(图3),其将中心肋状件142分别机械地热连接至凸起144A和144B。

中心肋状件142在Z方向上的厚度e

凸起144A和144B位于肋状件142的两侧。在此,这些凸起144A和144B中的每个的横截面都是矩形的,并且因此它们也分别具有竖直壁。凸起144A和144B中的每个的上表面与子层90直接机械地接触。凸起144A和144B在Z方向上的厚度等于或小于肋状件142的厚度。在此,凸起144A和144B的厚度等于肋状件142的厚度。

边缘146A和146B分别位于肋状件142的相应侧上。这些边缘平行于X方向地从肋状件142的竖直壁延伸到凸起144A、144B之一的面对竖直壁。每个边缘146A、146B的上表面与子层90直接机械地接触。每个边缘146A、146B的厚度e

肋状件142、凸起144A、144B和边缘146A、146B由相同的材料制成,使得波导76的这些彼此连接的各个部分仅形成单件的材料。在此,波导76由单晶硅制成。

在此,波导76和光学部件72被埋在直接位于氧化物子层90下方的封装子层122内。更具体地,子层122从子层120延伸到子层90。在此,子层122被分为上部光导级92和下部电互连级94。

级92包括所有光学部件以及在子层90下面制造的光学部件的部分。因此,在此,级92包括波导76、光学部件72和其中封装了光学部件和光学部件的部分的固体介电材料。因此,封装在层122中的光学部件(特别是其竖直壁和其下表面)与固体介电材料直接机械地接触。在封装的光学部件的垂直壁与该固体介电材料之间没有空腔。该级92由例如晶体硅子层制造,其中波导76和部件72是在其被封装在介电材料中之前制造的。

级94是没有光学部件和光学部件的任何部分的。在此,如以下将描述的,级94包括封装在固体介电材料中的互连金属网。子层122的介电材料的折射率低于用于制造波导76和部件72的材料的折射率。介电材料例如是二氧化硅。

就其本身而言,在直接位于子层90上的子层128中制造层78、80和82。在此,子层128包括III-V材料(用于制造所述层78、80和82)和介电材料(用于封装所述层78、80和82)。子层128直接在子层90上面水平延伸,并且其上表面对应于表面32。

为了通过层38供应和/或传输电信号,该层38包括被称为“辅通孔”的通孔。每个辅通孔将一个主通孔延伸到光学层38中。为此,每个辅通孔从键合界面40延伸到层38中。为了限制光学部件(相对于这些辅通孔)的布局所要满足的约束条件,辅通孔的直径远小于主通孔的直径。在此,辅通孔的直径小于3μm,并且优选小于1μm。为了促进这种辅通孔的制造,层38的厚度小于15μm或8μm或5μm。

下面,辅通孔被分为两类。第一类被称为“辅贯通孔”,第二类被称为“第二盲孔”。

辅贯通孔穿过层38的厚度,并且因此特别是穿过光导级92。因此,它们从键合界面40竖直延伸到上表面32。它们通常被用于将在上表面32上形成的电轨道电连接至主通孔之一。相反,第二盲孔未完全穿过层38的厚度,并且尤其是未穿过光导级92。因此,它们从键合界面40延伸至位于嵌入层38中的电接触部,例如触点74。

作为说明,图2示出了两个辅贯通孔100和102。通孔100将主通孔50电连接至在表面32上制造的电轨道106。在此,轨道106将通孔100的上端电连接至触点84。通孔100的下端与金属线58直接机械且电气地接触。

辅贯通孔102将主通孔51电连接至在表面32上制造的电轨道108。轨道108将通孔102的端部电连接至触点86。通孔102的下端与通孔51的金属线直接机械且电气地接触。在此,通孔100和102被用于为部件70供电。

通孔102的结构与通孔100的结构相同。因此,仅在下面详细描述通孔100的结构。

在本实施例中,通孔100具有彼此紧邻地设置的下部110和上部112。在制造期间,从光学层的相对侧制造所述部110和112。

下部110是互连金属网。在此,该部110包括:

-金属线114,其被嵌入子层122的级94中,

-金属线116,其与键合界面40齐平,以及

-金属通孔118,其从金属线116直接竖直延伸至金属线114。

以与限定主通孔50的上部58的直径相同的方式限定下部110的直径。所述部110的直径小于3μm或1μm。

在本实施例中,形成所述部110的互连金属网仅包括两级金属线。例如,这些是通常用参考标记M4和M5所指示的级别。

通常,该部110的高度较小,即小于6μm或3μm或1μm。

在此,在氧化硅子层120中制造金属线116,其下表面与键合界面40重合。直接在子层122下面制造子层120。在此,子层120由二氧化硅制成。

金属通孔118位于子层122的级94中。

从由导电材料制成的涂层124形成辅通孔100的上部112。例如,涂层124由铜或铝制成。该涂层124连续地覆盖在层38中挖掘的孔126的垂直壁和底部。更精确地,孔126从上表面32延伸至金属线114。为此,孔126从顶部到底部地连续穿过封装层128、子层90、光导级92和一部分的子层122的级94。

孔126的最大直径小于3μm,并且优选小于1μm。因此,辅通孔100的上部112的最大直径也小于3μm或1μm。

涂层124的上部与轨道106直接机械且电气地接触,并且其下部与金属线114直接机械且电气地接触。在图2的示例中,涂层124不完全填充孔126。因此,孔126的中心没有涂层。为此,涂层124的厚度例如小于500nm或300nm。孔126的中心填充有不导电和钝化的材料。有利地,该不导电的材料的热膨胀系数小于0.8C

层38还包括第二盲孔130。通孔130将电接触部74电连接质主通孔52的上端,以接受用于控制光学部件72的电气控制信号。为此,通孔130从键合界面40竖直延伸至电接触部74。因此,它恰好穿过子层120和子层122的级94。相反,它不穿过光导级92或子层90。与辅贯通孔不同,通孔130不通向上表面32。

仅从面向键合界面40的一侧制造通孔130。在此,通孔130由互连金属网形成。在本实施例中,通孔130从顶部至底部包括:

-四条嵌入的金属线132至135,

-金属通孔140,其将金属线的连续级彼此电连接,以及

-金属线138,其与键合界面40齐平,并且位于子层120中。

金属线138与主通孔52的上端直接机械且电气地接触。在此,互连金属网包括五个不同的金属线级。例如,这五个金属线级通常分别用参考标记M1至M5指示。通孔130的直径也小于3μm或1μm。

激光源70的波导76包括至少一个电接触部,其与凸起144A、144B或肋状件142热耦合。在此,电接触部仅在以下情况下被称为“热耦合”:

-该电接触部位于凸起144A或144B下方或肋状件142下方,以及

-与凸起144A、144B或肋状件142以最短竖直距离d

当距离d

在图2和3所示的实施例中,波导76包括三个电接触部148A、148B和148C(图3)。在此,触点148A、148B由金属通孔140的上端形成,这些触点的上端分别机械地直接抵靠凸起144A和144B的下表面。因此,在触点148A、148B与凸起144A和144B之间的距离d

每个电接触部148A、148B和148C分别通过盲孔158A、158B和158C热连接至互连层36。通孔158A、158B和158C分别在结构上例如与通孔130相同。然而,与通孔130不同的是,通孔158A、158B和158C的功能不一定是将触点148A、148B和148C电连接至层36的主通孔。在此,每个通孔158A、158B和158C的下端与位于子层44中且与界面40齐平的金属线直接机械且电气地接触。在此,该金属线与所有主通孔电绝缘。在此,通孔158A、158B和158C由良好的热导体材料制成。作为“良好的热导体”的材料通常是热导率高于1.2C

激光源70的层78和80分别通过辅通孔100和102热连接至主通孔50和51。因此,通过辅通孔100和102,由激光源70产生的热量部分地耗散至层36。通孔158A、158B和158C的存在改善了由激光源70产生的热量的热耗散。具体地,本领域技术人员已知,在激光源70的工作期间,波导76温度升高。在没有通孔158A、158B和158C的情况下,在波导76下面的子层122的介电材料的存在阻止了将产生的热量有效地去除。通孔158A、158B和158C分别通过子层122形成热桥,该热桥在此由金属形成,并且将波导76热连接至层36。这允许了更有效地去除由激光源70产生的热量。

在下表面34上制造再分布线150(也缩写为RDL),以将主通孔的下端电连接至相应的焊料微凸块。为此,再分布线包括直接固定焊料微凸块的连接焊盘。在图1中,仅示出了三个焊料微凸块152至154。这些微凸块152至154旨在被焊接至位于载体14的上表面上的相应焊盘,并且因此形成焊料微凸块阵列22的一部分。在此,线150被嵌入由非导电材料(诸如聚合物)制成的封装层156中。

现在将参考图4和在图5至11中示出的各种制造状态来描述用于制造系统2的工艺。

首先,在步骤160中,子层90、122和120的堆叠被制造在随后提供的柄部164上(图5)。在此,该堆叠仅形成光学层38的一部分,因为在该阶段明显缺少层128。在该阶段,子层120位于与柄部164相对的一侧,并且具有键合表面166。该表面166适合于通过直接键合,即通过不需要添加材料的键合与另一衬底键合。

步骤160还包括:

-在子层122的级92中制造波导76和光学部件72,

-构造辅通孔130和通孔158A、158B和158C,以及

-制造辅通孔100和102的下部110。

子层90被直接固定至柄部164。柄部164是载体,其允许了容易地处理子层120、122和90的堆叠。为此,柄部164的厚度通常大于250μm或500μm。例如,在此,柄部164是厚度为750μm或775μm的硅衬底。

优选地,子层90是硅绝缘体(SOI)衬底的埋入氧化物层。在这种情况下,通常通过蚀刻,在该SOI衬底的单晶硅层中制造波导76和部件72。一旦波导76和光学部件72在子层90上被制造,则通过依次连续沉积多个氧化物层来将它们埋入子层122的介电材料中。在沉积这些连续氧化物层的过程中,制造了互连金属网,该互连金属网形成了触点148A、148B、148C、辅通孔130、通孔158A、158B和158C以及辅通孔100和102的下部110。因此,从与柄部164相对的一侧制造这些互连金属网。用于在子层90上制造光学部件的工艺、用于将该部件嵌入子层122的工艺以及用于制造互连金属网的工艺是已知的,并且因此不在此详细描述。将注意的是,在制造工艺的这个阶段,制造辅通孔100和102的上部112是不可能的。因此,子层122在该阶段不包括通孔100和102的上部112。

并行地,在步骤162中,在随后提供的柄部170上制造互连层36(图6)。在该状态下,层36具有外表面172,所述外表面位于与柄部170相对的一侧上。该表面172是键合表面,即能够通过直接键合将其键合到表面166。柄部170的厚度大于250μm或500μm,以允许容易地处理层36。在此,柄部170例如是硅衬底。

步骤162还包括在层36中制造主通孔50至52。因此,在步骤162结束时,层36包括这些主通孔50至52。在柄部170上制造这样的层36以及在该层36中制造通孔50至52是常规操作。例如,使用介电涂层来制造通孔50至52的部54,所述介电涂层覆盖有钛或钽的阻挡层并且填充有铜的。例如在上文引用的Ken Miyairi的文章中描述用于制造这些部54的工艺。接下来,制造金属通孔60,以便与主通孔的部54电气地接触。最后,诸如金属线58的金属线被制造并且随后被封装在氧化物子层44中。然后,准备子层44的外表面以使其直接键合至表面166。

在步骤174中,通过直接键合将表面166和172彼此键合。这在图7中示出。然后获得键合界面40。例如,这是如下文所述的直接混合氧化铜键合的问题:Yan Beillard etal.:"Chip to wafer copper direct bonding electrical characterization andthermal cycling",3D Systems Integration Conference(3DIC),2013IEEEInternational.

接下来,在步骤176中,去除柄部164,以便暴露子层90(图8)。例如,通过化学机械抛光(CMP)和选择性化学蚀刻去除柄部164。

在步骤178中,在子层90上、在与光导级92相对的一侧上制造部件70的光放大部(图9),并且将其封装在封装层128的介电材料中。

在步骤180中,制造触点84、86、电轨道106和108以及辅通孔100和102的上部112(图10)。例如,首先挖掘通过子层128、90和子层122的级92的孔(诸如孔126)。接下来,在整个外表面上沉积由导电材料制成的涂层。最后,对该导电涂层进行蚀刻,使得导电涂层仅保留在触点84、86、轨道106和108以及辅通孔100和102的上部112的位置。层38的制造由此完成。

在步骤182中,然后依次去除柄部170,以暴露下表面34(图116)。

在步骤184中,在暴露的下表面34上制造再分布线150、焊料微凸块152至154和封装层156。光子芯片18的制造由此完成。

在步骤186中,电子芯片16和光子芯片18被焊接至位于载体14的上表面上的焊盘上。然后,芯片16和18通过载体14上的水平连接件彼此电连接。

在步骤190中,载体14和芯片16和18被封装在非导电材料中,该非导电材料是良好的热导体,即诸如环氧树脂的材料。此外,优选地,在芯片16和18的上表面上固定有盖,该盖上有散热片(诸如散热器)。例如,使用导热黏合剂将该盖直接黏合至光子芯片18的上表面32和芯片16的上表面。因此,这些上表面可以与热黏合剂直接接触,该热黏合剂与盖接触。这是因为电力和电信号都经由芯片16和18的下表面进行路由的。

接下来,在步骤192中,系统2例如被焊接至印刷电路板4。

图12示出了可以代替系统2中的光子芯片18而使用的光子芯片200。芯片200除下列内容之外与芯片18是相同的:

-光学层38已被光学层202代替,

-辅通孔130已被第二盲孔204代替,以及

-光子芯片200包括第三通孔206。

除了其还包括埋入子层122的级92中的有源电子部件210之外,光学层202与光学层38是相同的。该电子部件210被认为是有源的,因为为了运行需要对其进行供电,并且它发射和/或接收电信号。为此,部件210在其下表面上包括电接触部212。因此,该电接触部212被嵌入子层122并且面向键合界面40。

在此,辅通孔204将电子部件210的电接触部212电连接到主通孔52,仅穿过子层122和子层120的低级94来实现。例如,电子部件210旨在从其经由主通孔52所接收的电信号向光学部件72供应电气控制信号。为此,部件210在其下表面上包括连接至部件72的触点74的另一个电接触部。为了实现这一点,对位于子层122的级94中的互连金属网进行修改,以创建将该另一电接触部和触点74彼此电连接的路径。为了简化图12,图12中未示出互连金属网的这种修改。可以从相对于通孔130所给出的说明中推导出通孔204的结构和制造。

通孔206是将嵌入子层122的级94中的金属线135电连接至在上表面32上制造的电轨道216的通孔。通孔206从表面32竖直延伸至嵌入的金属线135,并且尤其穿过子层90和光导级92来这样做。

电轨道216包括测试焊盘,其允许了在光子芯片200的制造过程中,特别是在去除柄部170之前测试部件210和/或72的操作。为此,尽管图12中未示出,但也修改了位于子层122的级94中的互连金属网,以使用金属线和金属通孔来创建将电接触部212和/或74电连接到金属线135的电路径。

在此,,除了其没有下部110之外,通孔206的结构与通孔100的结构是相同的。通常,通孔206以与通孔100的上部112相同的方式制造,并且通常与该上部112同时制造。

图13示出了可以代替系统2中的光子芯片18而使用的光子芯片250。光子芯片250与光子芯片18相同,除了:

-辅贯通孔100和102已分别被辅贯通孔252和254代替,

-部件70已被激光源256代替,

-辅通孔130已被辅贯通孔258、电子芯片260和第三通孔262代替。

除了其上部270的制造方式不同之外,辅贯通孔252和254与通孔100和102分别是相同的。更精确地,上部270在此是实心通孔。换句话说,除了孔126的中心空心填充有导电材料之外,上部270与上部112是相同的。通常,在这种情况下,通孔252和254的上部270的最大直径小于1μm。

激光源256与部件70相同,除了:

-触点86已被触点274代替,并且

-波导76已被波导276代替。

触点274是将层78电连接至电轨道108的金属通孔。

除了省略了凸起144A和144B之外,波导276与波导76是相同的。同样,省略了触点148A、148B和通孔158A和158B。此外,中心肋状件142的厚度随后被选择为使得由激光源256引导的光学信号主要位于层80中。例如,为此,厚度e

辅贯通孔258将主通孔52直接电连接至在上表面32上制造的电轨道276。轨道276包括焊盘,电子芯片260的第一电接触部被焊接至该焊盘。在此,通孔258的结构与通孔252的结构是相同的。

通孔262将在上表面32上制造的电轨道280直接电连接至金属线135,所述金属线被嵌入在子层122的级94中。为此,除了省略了下部110之外,通孔262的结构与通孔252的结构例如是相同的。电轨道280包括焊接有电子芯片260的第二电接触部的焊盘。

在此,金属线135通过类似于参考图12所述的互连金属网与光学部件72的电接触部74电连接。通常,电子芯片260是换能器,该换能器通过主通孔供电,并且根据通过主通孔(例如通孔52)接收的电信号控制光学部件72。

通孔的水平横截面不一定是圆形的。例如,通孔的横截面可以是正方形或矩形。在这种情况下,“直径”是指这个水平横截面的水力直径。

如前述实施例中的辅通孔的情况所示,通孔的直径在其整个高度上不一定是恒定的。在这种情况下,通孔的“直径”是指这个通孔沿其高度的最大直径。

作为变型,省略了主通孔的上部56。在这种情况下,主通孔的部54的上端直接与键合界面40齐平。

在另一种变型中,省略了金属通孔60。在这种情况下,部54的上端与金属线58直接机械且电气地接触。

在另一个实施例中,主通孔的上部56可以包括在子层44的不同深度处制造的多个附加金属线。然后,部56的金属线的各种级通过金属通孔彼此电连接。然后,这些附加金属线形成再分布层或RDL,其允许例如与界面40齐平的多个金属线彼此电连接。

作为变型,用于形成辅贯通孔的下部的互连金属网也可以包括三级以上的金属线。

作为变型,省略了辅贯通孔的下部110。在这种情况下,孔126的底部随后直接通向主通孔的金属线58。然后这样的辅贯通孔仅包括单个部,即部112。

孔126的中心也可以填充有不同于子层122的介电材料的介电材料。例如,它填充了有机材料。

在另一个实施例中,使用分别从表面32延伸至金属线114的一个或更多个金属通孔来制造辅通孔的上部112。

如果不需要放宽为了限制光学部件(相对于这些辅通孔)的布局所要满足的约束条件,则辅通孔的直径可以大于3μm,特别是等于或大于主通孔的直径。

作为变型,在触点148A、148B与凸起144A、144B之间的距离d

在一个特定实施例中,省略了通孔148C。在这种情况下,来自波导76的热量仅通过通孔158A和158B消散。

作为变型,互连层36可以由硅以外的材料制成。例如,它可以由玻璃制成。

作为另一种变型,层36包括一个或更多个电子部件。

光学层38的子层也可以由其他材料制成。特别地,子层122可以使用另一种介电材料来制造,诸如例如非晶硅、氮化硅(SiN)或氮氧化硅(SiON)。

层38的各种氧化物子层不一定都由同一氧化物制成。作为变型,子层120可以由不同于用于制造子层90的氧化物制成。也可以使用与子层90不同的氧化物来制造子层122。

光学层还可以被直径大于3μm,例如大于10μm或20μm的附加通孔穿过。在这种情况下,在这些附加通孔中的每个的周围都提供了大面积的禁区,并且在该禁区中不制造光学元件。该禁区的尺寸根据以下文章中给出的教导确定:Yan Yang et al.:"Though–Si–via(TSV),Keep–Out–Zone(KOZ)in SOI photonics interposer:A study of impact of TSV-Induced stress on Si ring resonators",IEEE Photonics Journal,volume 5,Number6,December 2013。以下将本文称为“Yang2013”。然而,即使光子芯片包括这些附加通孔中的一些,但光学层中的光学部件的布置仍然是简化的,因为辅通孔的存在仍然限制了光学部件的布局的约束条件。

任何数量的光学部件都可以被埋入子层122的级92中。此外,各种光学部件不一定被埋入级92中的相同深度。如果光学部件或光学部件的一部分由彼此堆叠的材料的各种子层制造,则尤其是这种情况。然后,这些材料子层可以从由晶体硅子层、非晶硅子层、氮化硅(SiN)的子层以及氮氧化硅(SiON)的子层组成的组中选择。

作为变型,通孔158A、158B、158C和266中的一个或更多个的下端被电气且机械地连接至至少一个主通孔,以便改善由激光源产生的热量的热耗散。因此,在第一实施例中,通孔158A、158B和266中的至少一个的下端被电气且机械地连接至用于将芯片18的部件之一电连接至载体14的主通孔。例如:

-通孔158A和158B的下端分别被电气且机械地连接至主通孔50和51,或者

-通孔158A和158B的下端均被电气且机械地连接至主通孔50或51或52,或者

-通孔266的下端被电气且机械连接至主通孔50或51或52。

在第二实施例中,通孔158A、158B和266中的至少一个的下端被电气且机械地连接至附加的主通孔。该附加的主通孔是电隔离的。因此,它与主通孔50、51和52是电隔离的。因此,该附加的主通孔不被用于进行电连接。例如,通孔158A或158B的下端被电气且机械地连接至这种附加的主通孔。

通孔158A、158B、158C中的一个或更多个以及通孔266的直径不一定小于3μm或1μm。其直径也可以大于这些值。

使用通孔158A、158B、158C和266来改善由激光源产生的热量的耗散,类似地适用于改善由至少一部分嵌入子层122中的任何类型的光学或电子部件所产生的热量的耗散。例如,类似于通孔158C或266的通孔也可以用于由光学部件72或电子部件210产生的热量的耗散。

波导76的其他实施例是可能的。例如,作为变型,省略了凸起144B和边缘146B。在这种情况下,也省略了触点148B和通孔158B。凸起144A、144B的厚度可以大于肋状件142的厚度e

光子芯片可以在上表面32上包括电轨道,该电轨道不一定被用于将光学部件电连接到主通孔之一。例如,如关于图13的实施例所述,这样的电轨道276可以仅被用于将焊接在光子芯片的上表面32上的电子芯片电连接至主通孔中之一。

在一个实施例中,光子芯片仅包括第二盲孔。在这种情况下,从与柄部164相对的一侧制造所有第二盲孔。然后,可以颠倒柄部的去除的顺序。因此,可以在柄部164之前移除柄部170。具体地,不需要制造辅贯通孔的上部112。同样在这种情况下,在层38键合到层36之前,第二盲孔已经被完全地制造。

在另一实施例中,光子芯片仅包括辅贯通孔。

替代地,芯片260可以对应于图1的芯片16。在这种情况下,电子芯片260是ASIC,该ASIC通过主通孔供电,并且用其生成的电信号控制光学部件72。

其他制造工艺也是可行的。

部件70或激光源256的一部分可以独立于在此描述的光子芯片的其他特征,通过诸如通孔158A、158B、158C和266的辅通孔(通常是盲孔)热连接至互连层。特别地,这种热连接可以在主通孔穿过光学层的情况下进行,如在文章Yang2013中所述,或者在省略所有主通孔的情况下进行。当省略了主通孔时,层36不再是互连层,而只是光学层38的载体。当省略了主通孔时,优选地,表面子层44的厚度足够小,以不对子层42的辅通孔进行隔热。例如,在这种情况下,省略表面子层44或者其厚度小于100nm或50nm。如果表面子层44的厚度较大,即大于100nm或300nm,则可以保留上部56以形成穿过子层44的热桥,并且只省略主通孔的下部54。在这种情况下,上部56可以通过厚度小于100nm或小于50nm的介电材料的薄层与硅子层42电绝缘。

相对于在本专利申请的引言中引用的J.Durel等人的文章中描述的实施例,通过与层36直接机械接触的通孔将波导76或276热连接至互连层,改善了激光源在其工作期间产生的热量的热耗散。此外,光子芯片的制造仍然特别简单。特别地,通孔158A、158B、158C和266由互连金属网形成的事实简化了这些通孔的制造,从而简化了光子芯片的制造。相对于还穿过上部光导级92的被用于在波导76、276与层36之间创建这些热桥的通孔的情况,这些通孔仅位于下部互连级94中的事实允许了对光学部件的布局的约束条件进行限制。

发明人已知,通常,直接接触波导的一部分的导电接触的存在增加了该波导的光学损耗。然而,优选地,光学损耗中的这种增加必须尽可能地受到限制。在这种情况下,在同一实施例中,结合小于300nm的中心肋状件142的厚度e

在触点148C与肋状件142的下表面之间的距离d

使用凸起144A、144B以及使用其上端直接作用于这些凸起144A、144B的通孔158A、158C也允许了在不显著增加光学损耗的情况下改善散热。具体地,由于边缘146A、146B,在凸起144A、144B中引导的光学信号可以忽略不计。因此,这些凸起直接作用于通孔158A、158B的上端的事实在改善了散热的同时,几乎没有增加光学损耗。

众所周知,光学部件附近存在贯通孔会导致问题。具体地,这种通孔由导电材料制成,其热膨胀系数不同于制造光学部件的材料。因此,响应于温度变化,贯通孔对附近的光学部件施加了随温度变化的机械应力。在机械应力上的这种变化改变了光学部件的光学特性,并导致该光学部件的特性的改变。例如,当光学部件是光学滤波器时,这会改变其中心波长。必须避免光学部件的特性的这种变化。在所述实施例中,主通孔不对光学部件施加实质性的机械应力。具体地,互连层36是完全没有光学部件的。光学部件仅位于光学层中。因此,光学部件可以相对于彼此布置,而不必担心主通孔的布置。特别地,不必考虑每个主通孔周围的任何禁区。部分穿过光导级92的辅贯通孔的直径优选小于或等于3μm,甚至1μm。因此,这种辅贯通孔可以放置在距光学部件4μm甚至2μm处,而不会对光学部件施加机械应力。相比之下,Yang2013中描述的直径大于10μm的贯通孔必须被放置在距光学部件40μm处,以避免其受到机械应力。因此,如果光学部件的直径等于主通孔的直径,则可以将光学部件放置在距辅通孔更近处。因此,在同一光子芯片中,主通孔和辅通孔的组合允许了获得足够厚的光子芯片,以实现可接受的弯曲,同时限制了光学部件相对于通孔的布置所要满足的约束条件。还将注意的是,互连层不一定包含埋入氧化硅层。因此,其导致可接受的弯曲的最小厚度小于包含埋入氧化硅的层的厚度。减小互连层的厚度尤其允许了减小主通孔的寄生电容。具体地,这种寄生电容与主通孔的高度成正比。

对于芯片18、200和250,将激光源放置在氧化物层90的上表面有利于从外部冷却,尤其是凭借系统的封装。

孔126的中心填充有热膨胀系数低于涂层124的非导电材料的事实允许了进一步减小辅通孔对附近光学部件所施加的机械应力。

- 具有埋入激光源的光子芯片

- 高效激射输出DFB半导体激光器装置及光子集成发射芯片