静电保护电路及芯片

文献发布时间:2023-06-19 09:30:39

技术领域

本公开涉及半导体技术领域,具体而言,涉及一种静电保护电路及应用该静电保护电路的芯片。

背景技术

ESD(Electrostatic Discharge,静电放电)保护电路的设计对于集成电路芯片具有重要意义。当ESD发生时,瞬态电压通过芯片管脚(PAD)进入内部电路,电荷的瞬态累积可对芯片内部电路的器件造成损坏。被设计在PAD旁且耦接于PAD的ESD电路可以为这些瞬态电压提供低阻旁路,使其进入电源线(VDD或VSS),保护芯片内部工作电路。

GGNMOS(gate-grounded NMOS,栅极接地的N型MOS管)静电保护电路是一种常用的静电保护电路,由栅极接地的晶体管为ESD电流提供低阻旁路,避免其击穿输入缓冲电路中的晶体管的栅极氧化层。在现有的GGNMOS静电保护电路中,GGNMOS的PN结击穿电压小于输入缓冲电路(buffer)中的晶体管的栅氧化层的击穿电压,当瞬态ESD电流通过芯片管脚(PAD)进入时,GGNMOS的PN结被瞬间击穿,将该电流旁路到电源线,实现保护目的。

但是,随着工艺进步,晶体管栅氧化层的厚度越来越小,已经低于PN结的击穿电压,ESD电流会首先击穿输入缓冲电路的晶体管栅极氧化物,现有的通过GGNMOS形成的ESD保护电路失去意义。

需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

发明内容

本公开的目的在于提供一种静电保护电路,用于至少在一定程度上克服由于相关技术中的缺陷导致的GGNMOS静电保护电路无法适应由技术进步带来的栅氧化层厚度降低的问题。

根据本公开的第一方面,提供一种静电保护电路,包括:

第一静电旁路,至少包括第一P型晶体管,所述第一P型晶体管的漏极耦接于第一节点,源极耦接于第一电压,栅极通过第一电阻模块连接于第一电压,所述第一节点电连接于信号输入引脚;

第二静电旁路,至少包括第一N型晶体管,所述第一N型晶体管的漏极耦接于所述第一节点,源极耦接于所述第二电压,栅极通过第二电阻模块连接于所述第二电压;

输入缓冲电路,至少包括第二N型晶体管和第二P型晶体管,所述第二N型晶体管的栅极和所述第二P型晶体管的栅极耦接于第二节点;

第三N型晶体管,第一端耦接于所述第一节点,第二端耦接于所述第二节点,控制端耦接于第三节点;

控制模块,第一端耦接于所述第一电压,第二端耦接于所述第二电压,输出端耦接于所述第三节点,用于控制所述第三N型晶体管在ESD电流产生时关断;

其中,所述第一电阻模块和所述第二电阻模块用于提供电阻功能。

在本公开的一种示例性实施例中,所述控制模块包括:

第一电容,第一端耦接于所述第一电压,第二端耦接于第四节点;

第三电阻模块,用于提供电阻功能,第一端耦接于所述第四节点,第二端耦接于所述第二电压;

第一反向器,第一端耦接于所述第一电压,第二端耦接于所述第二电压,第三端耦接于所述第四节点,第四端耦接于所述第三节点。

在本公开的一种示例性实施例中,所述第一电阻模块通过第一电阻实现,或者所述第一电阻模块通过第三P型晶体管实现,所述第三P型晶体管的漏极耦接于所述第一P型晶体管的栅极,所述第二P型晶体管的源极耦接于所述第一电压,所述第二P型晶体管的栅极通过第二电阻连接所述第二电压。

在本公开的一种示例性实施例中,所述第二电阻模块通过第三电阻实现,或者所述第二电阻模块通过第四N型晶体管实现,所述第四N型晶体管的漏极耦接于所述第一N型晶体管的栅极,所述第二N型晶体管的源极耦接于所述第二电压,所述第二N型晶体管的栅极通过第四电阻连接所述第一电压。

在本公开的一种示例性实施例中,所述第三电阻模块通过第五电阻实现,或者所述第三电阻模块通过第五N型晶体管实现,所述第五N型晶体管的漏极耦接于所述第四节点,源极耦接于所述第二电压,栅极通过第六电阻耦接于所述第一电压。

在本公开的一种示例性实施例中,还包括:

第一二极管,正极耦接于所述信号输入引脚,负极耦接于所述第一电压;

第二二极管,负极耦接于所述信号输入引脚,正极耦接于所述第一电压;

第七电阻,第一端耦接于所述信号输入引脚,第二端耦接于所述第一节点。

在本公开的一种示例性实施例中,所述输入缓冲电路通过第二反向器实现,所述第二反向器由所述第二P型晶体管和所述第二N型晶体管组成,所述第二反向器的第一端耦接于所述第一电压,第二端耦接于所述第二电压,第三端耦接于所述第二节点,第四端耦接于内部电路。

在本公开的一种示例性实施例中,所述输入缓冲电路通过施密特触发器实现,所述施密特触发器由第四P型晶体管、所述第二P型晶体管、所述第二N型晶体管、第六N型晶体管、第五P型晶体管、第七N型晶体管组成,所述施密特触发器的第一端耦接于所述第一电压,第二端耦接于所述第二电压,第三端耦接于所述第二节点,第四端耦接于内部电路。

根据本公开的一个方面,提供一种芯片,一或多个管脚电连接如上述任意一项所述的静电保护电路。

本公开实施例提供的静电保护电路通过在静电保护电路与输入缓冲电路之间设置栅极受控的NMOS,可以在不影响电路的正常工作的前提下增大击穿输入缓冲电路的难度,有效克服由于栅氧化层厚度降低带来的ESD保护电路失效问题。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

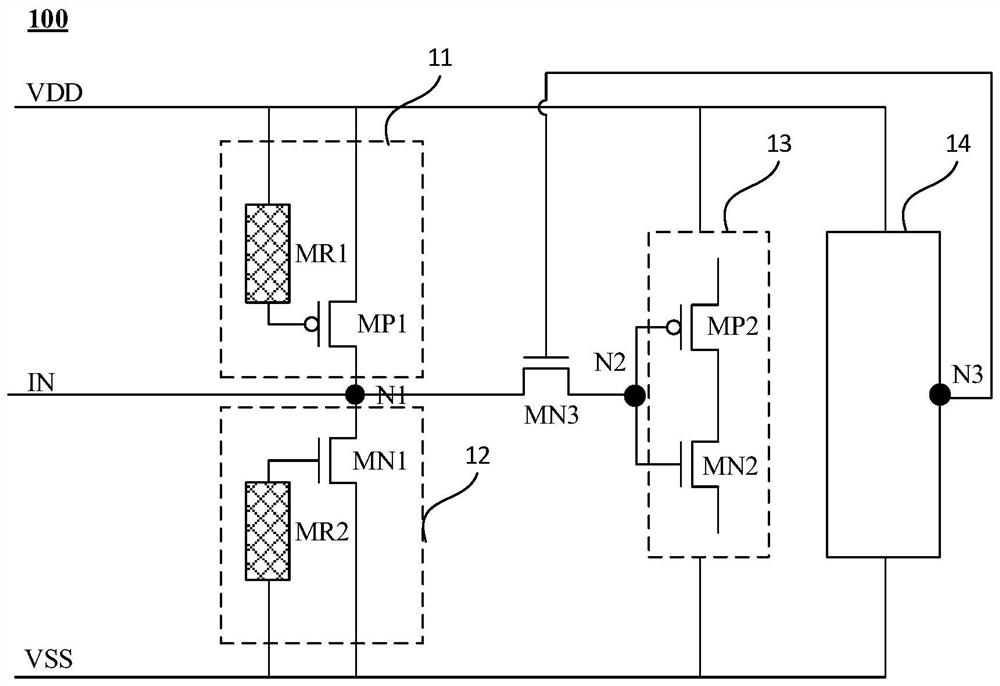

图1是本公开提供的静电保护电路的示意图。

图2是一个实施例中静电保护电路的示意图。

图3A~图3C是本公开三个实施例中各电阻模块的实现电路示意图。

图4是本公开一个实施例中输入缓冲电路的示意图。

具体实施方式

现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提供这些实施方式使得本公开将更加全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施方式中。在下面的描述中,提供许多具体细节从而给出对本公开的实施方式的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而省略所述特定细节中的一个或更多,或者可以采用其它的方法、组元、装置、步骤等。在其它情况下,不详细示出或描述公知技术方案以避免喧宾夺主而使得本公开的各方面变得模糊。

此外,附图仅为本公开的示意性图解,图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。附图中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现这些功能实体,或在一个或多个硬件模块或集成电路中实现这些功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现这些功能实体。

图1是本公开提供的静电保护电路100的示意图。

参考图1,静电保护电路100可以包括:

第一静电旁路11,至少包括第一P型晶体管MP1,第一P型晶体管MP1的漏极耦接于第一节点N1,源极耦接于第一电压VDD,栅极通过第一电阻模块MR1连接于第二电压VSS,第一节点N1电连接于信号输入引脚IN;

第二静电旁路12,至少包括第一N型晶体管MN1,第一N型晶体管MN1的漏极耦接于第一节点N1,源极耦接于第二电压VSS,栅极通过第二电阻模块MR2连接于第一电压VDD;

输入缓冲电路13,至少包括第二N型晶体管MN2和第二P型晶体管MP2,第二N型晶体管MN2的栅极和第二P型晶体管MP2的栅极耦接于第二节点N2;

第三N型晶体管MN3,第一端耦接于第一节点N1,第二端耦接于第二节点N2,控制端耦接于第三节点N3;

控制模块14,第一端耦接于第一电压VDD,第二端耦接于第二电压VSS,输出端耦接于第三节点N3,用于控制第三N型晶体管MN3在ESD电流产生时关断;

其中,第一电阻模块MR1和第二电阻模块MR2用于提供电阻功能。MR1和MR2等价于两个电阻,这两个电阻的阻值较大,用于控制MP1和MN1在没有ESD电流产生时关断,在有ESD电流产生时,MN1或MP1被击穿,为ESD电流提供泄放路径。

在现有技术中,假设MP2和MN2的栅极击穿电压比MP1和MN1的PN结击穿电压高,ESD电流进入N1节点时,MP1或MN1的PN结先于MP2和MN2的栅极被击穿,ESD电流通过MP1或MN1被泄放。但是,随着栅氧厚度的进一步减小,MP2和MN2的栅极击穿电压可能比MP1和MN1的PN结击穿电压低,ESD电流可能会直接击穿MP2和MN2的栅极,从而造成内部电路的损坏。

在图1所示实施例中,MN3在没有ESD电流产生时为导通状态,不影响信号输入引脚IN到输入缓冲电路13的信号传递。在ESD电流产生时,控制模块14控制MN3关断,此时只有第一节点N1电压高于MN3的PN结击穿电压与MN2、MP2栅氧击穿电压之和时,才可能会对MN2、MP2栅氧产生损伤。在一个实施例中,MN3可以与MN1为同型号器件,具有同样的PN结击穿电压,从而,在ESD电流到达信号输入引脚IN时,受到关断的MN3阻挡,为ESD电流通过第一静电旁路11、第二静电旁路12泄放争取了时间,在静电泄放成功之前有效保护了输入缓冲电路13中的晶体管。

在ESD电流通过第一静电旁路11、第二静电旁路12泄放后,即ESD电流消失后,控制模块14控制MN3重新导通,输入缓冲电路13能够正常接收通过信号输入引脚IN输入的信号。

由此,在不影响输入电路的正常功能的条件下,本公开实施例可以应用在输入缓冲电路13中的晶体管的栅氧化层击穿电压小于PN结的击穿电压的情况下,保留GGNMOS静电保护电路的性能优势,又克服了现有的GGNMOS静电保护电路无法适应新型晶体管栅氧化层厚度降低的问题。

图2是一个实施例中静电保护电路100的示意图。

参考图2,在一个实施例中,静电保护电路100还可以包括:

第一二极管Dp,正极耦接于信号输入引脚IN,负极耦接于第一电压VDD;

第二二极管Dn,负极耦接于信号输入引脚IN,正极耦接于第一电压VSS;

第七电阻R7,第一端耦接于信号输入引脚IN,第二端耦接于第一节点N1。

Dp和Dn分别作为基本ESD保护电路中的静电旁路而存在,R7的作用是增大信号输入通路的电阻,让ESD电流可以优先通过Dp或Dn进入电源线。为了防止影响正常信号的处理,R7的阻值一般较小,可以使用多晶硅(poly)电阻。

控制模块14可以包括:

第一电容C,第一端耦接于第一电压VDD,第二端耦接于第四节点N4;

第三电阻模块MR3,用于提供电阻功能,第一端耦接于第四节点N4,第二端耦接于第二电压VSS;

第一反向器CV1,第一端耦接于第一电压VDD,第二端耦接于第二电压VSS,第三端耦接于第四节点N4,第四端耦接于第三节点N3。

当有ESD正电压产生时,ESD电流瞬间通过Dp进入VDD,提高VDD电压值,进而提升电容C另一极板电压值,该高电压脉冲经过反相器之后输出一低电平脉至MN3的栅极,关断MN3,切断了信号输入引脚IN与输入缓存电路13之间的通路,使得静电电流通过第一静电旁路或第二静电旁路泄放到电源线,实现ESD保护功能。

在本公开的一种示例性实施例中,当没有静电电流发生时,第四节点N4的电压值通过第三电阻模块MR3被拉低为低电平,第一反向器CV1向MN3的栅极输出高电平,从而控制MN3导通,避免影响信号输入通路的正常工作。

在图1或图2所示实施例中,使用电阻模块MR1~MR3来实现电阻功能,提供阻值。在本公开实施例中,可以使用多种方式来实现上述电阻模块。

图3A~图3C是本公开三个实施例中各电阻模块的实现电路示意图。

参考图3A,第一电阻模块MR1可以通过第一电阻R1实现,第二电阻模块MR2可以通过第三电阻R3实现,第三电阻模块MR3可以通过第五电阻R5实现。为保护晶体管并控制晶体管MP1和MN1常态为关断,MR1~MR3的阻值较大,因此,通过单一电阻实现电阻模块的功能虽然能够节省成本,但是会占用较大的设计面积。

参考图3B,在另一实施例中,第一电阻模块MR1可以通过第三P型晶体管MP3实现,MP3的漏极耦接于MP1的栅极,源极耦接于第一电压VDD,栅极通过第二电阻R2连接第二电压VSS。

第二电阻模块MR2可以通过第四N型晶体管MN4实现,MN4的漏极耦接于MN1的栅极,源极耦接于第二电压VSS,栅极通过第四电阻R4连接第一电压VDD。

在图3所示实施例中,通过使用常开的MOS管代替单一电阻实现阻值较高的电阻模块,可以有效节省器件面积。导通的MOS管的PN结阻值较高,且本身占用的制造面积较小,而且由于控制MOS管常开,R2和R4的阻值也较小,在一些实施例中,可以用Poly电阻来实现。

参考图3C,第三电阻模块MR3可以通过第五N型晶体管MN5实现,MN5的漏极耦接于第四节点N4,源极耦接于第二电压VSS,栅极通过第六电阻R6耦接于第一电压VDD。

在图3A~图3C所示实施例中,输入缓冲电路13通过第二反向器实现,第二反向器由MP2和MN2组成,第二反向器的第一端耦接于第一电压VDD,第二端耦接于第二电压VSS,第三端耦接于第二节点N2,第四端OUT耦接于内部电路,向内部电路输出CMOS电平信号。

在其他实施例中,输入缓冲电路13还可以通过其他方式实现。

图4是本公开一个实施例中输入缓冲电路的示意图。

参考图4,输入缓冲电路13可以通过施密特触发器实现,施密特触发器由第四P型晶体管MP4、第二P型晶体管MP2、第二N型晶体管MN2、第六N型晶体管MN6、第五P型晶体管MP5、第七N型晶体管MN7组成,作为输入缓冲电路13,施密特触发器的第一端耦接于第一电压VDD,第二端耦接于第二电压VSS,第三端耦接于第二节点N2,第四端OUT耦接于内部电路,向内部电路输出CMOS电平信号。

根据本公开的又一个方面,提供一种芯片,该芯片的一或多个管脚电连接如上所述的静电保护电路。由于芯片包括上述静电保护电路,能够在利用由GGNMOS组成的ESD保护电路的优点的同时,克服GGNMOS电路无法适应栅氧化层厚度降低的问题。

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本申请旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和构思由权利要求指出。

- 静电保护电路及全芯片静电保护电路

- 静电保护电路以及带有静电保护电路的芯片