具有磁通门的电流传感器

文献发布时间:2023-06-19 09:54:18

本发明涉及磁通门电流传感器的领域。

磁通门电流传感器利用形成磁芯的磁性材料的属性,藉此该磁芯从某个磁激励电平饱和。参照图1,对于增大的磁场H,磁场H与磁通密度B之间的传递函数的斜率从磁芯的所谓“饱和”值大幅下降。在图1中,饱和值对应于范围ΔH和ΔB。

参照图2和3,在用于测量在导体中流动的电流Im的常规磁通门电流传感器1中,方波信号发生器2向绕磁芯4缠绕的激励绕组3的端子施加方波激励电压Vex。在激励绕组3中流动的激励电流Iex由测量模块5测量。连接到测量模块5的峰值检测器6提供两项信息:饱和电平以及激励电流Iex的各峰值电流之间的差值。饱和电平用以对激励电压Vex的振幅进行伺服控制。激励电流Iex的各峰值电流之间的差值用以估计待测量电流Im,并且该差值经由电压至电流转换器起作用以对退磁电流的振幅进行伺服控制,该退磁电流在退磁绕组8中流动并且用以补偿由待测量电流Im在磁芯4中产生的磁通量。

磁通门电流传感器在某些应用中是优选的。这特别适用于测量在用户装备的固态功率控制器(SSPC)型的截止构件中流动的电流,或者适用于测量在连接到电机一相的功率电子模块(PEM)型的能量转换器构件中流动的电流。

本发明的目的是提高工业可再现性并降低磁通门电流传感器的成本。

为了实现该目的,提供了一种磁通门电流传感器,包括:围绕导体延伸的磁芯,其中待测量电流在该导体中流动;测量绕组;激励电路,其被布置成生成数字激励信号;获取电路,该获取电路包括模数转换器并被布置成:从测量绕组的端子获取模拟测量电压并产生数字测量信号;退磁伺服控制电路,其被布置成:使用数字测量信号来产生数字退磁信号以用于补偿由待测量电流产生的磁通量;求和电路,其被布置成:对数字激励信号和数字退磁信号进行求和以获得数字注入信号;以及注入电路,该注入电路包括数模转换器并被布置成:从数字注入信号产生模拟激励电流并将该模拟激励电流注入到测量绕组中。

本发明的磁通门电流传感器由此具有单个测量绕组,其同时用以激励磁芯、对磁芯进行退磁、以及获取模拟测量电压以估计待测量电流。这简化了本发明的磁通门电流传感器并且由此减小了其大小、重量和制造成本。

此外,本发明的磁通门电流传感器的处理系统的大部分是数字的。使用主要是数字的处理系统用以进一步降低本发明的磁通门电流传感器的制造成本并提高其工业可再现性。

本发明可以鉴于以下对本发明的特定非限定性实施例的描述而被更好地理解。

参照附图,在附图中:

·图1绘制了磁场与磁通密度之间的传递函数的曲线;

·图2示出了现有技术的磁通门电流传感器;

·图3示出了激励现有技术磁通门电流传感器的磁芯的激励电压的曲线和激励电流的曲线;

·图4示出了本发明的磁通门电流传感器;

·图5示出了用于测量待测量电流的分流桥;

·图6是本发明的磁通门电流传感器中使用的印刷电路和变压器的剖面视图;以及

·图7是与图6的视图类似的、但从上方观看的视图。

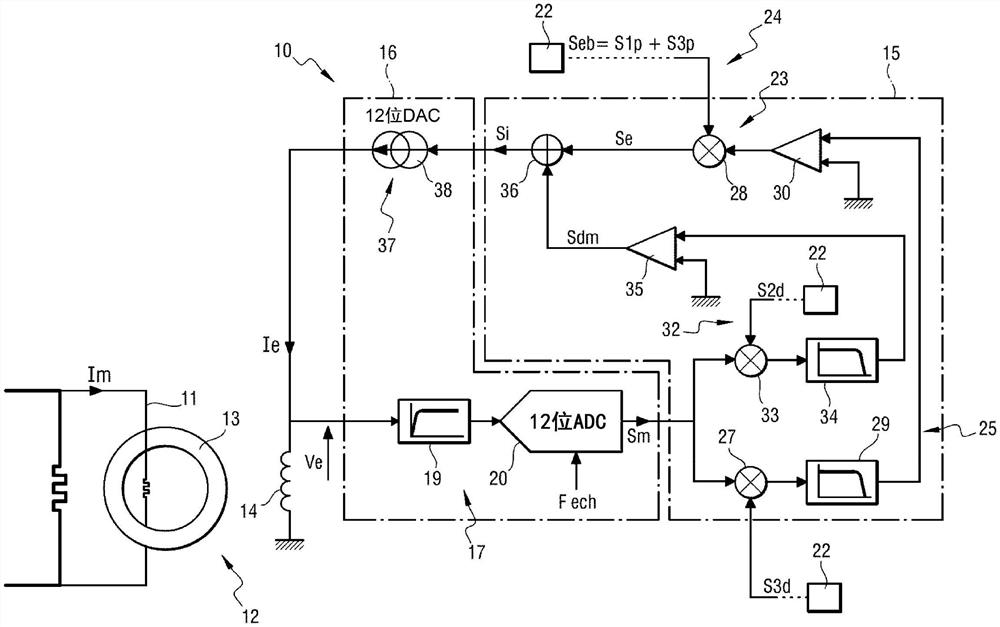

参照图4,在该示例中使用本发明的磁通门电流传感器10来测量待测量且在导体11中流动的电流Im。

磁通门电流传感器10包括变压器12,该变压器12包括磁芯13、初级绕组和次级绕组。初级绕组是导体11。磁芯13围绕导体11延伸。次级绕组是绕磁芯13缠绕的测量绕组14。

磁通门电流传感器10包括形成数字部分15和模拟部分16的多个电子组件。

数字部分15包括数字处理器组件,该数字处理器组件特别是现场可编程门阵列(FPGA),但它可以是某种其他组件:微控制器、处理器专用集成电路(ASIC)等等。

磁通门电流传感器10进一步包括获取电路17。获取电路17形成模拟部分16的一部分。

获取电路17连接到测量绕组14。

获取电路17包括高通滤波器19和连接到高通滤波器19的输出的模数转换器(ADC)20。

在该示例中,ADC 20是12位转换器,该转换器的操作以频率Fech进行时钟控制。在该示例中,Fech=100兆赫兹(MHz)。ADC 20自然地可以呈现不同的特性。

获取电路17从测量绕组14的端子获取模拟测量电压Ve。测量电压Ve被用作高通滤波器19的输入。

所产生的电压被用作ADC 20的输入,该ADC 20产生数字测量信号Sm。

磁通门电流传感器10包括高频发生器22。高频发生器22被纳入FPGA中(其中术语“被纳入”可以用以下任何术语来代替:被编程、被实现、被提供等等)。

高频发生器22产生频率f0的数字参考信号、频率2f0的数字参考信号、以及频率3f0的数字参考信号。

在该示例中,频率f0的数字参考信号具有以下形式:

S1r=sin(ω0t)。

在该示例中,频率2f0的数字参考信号具有以下形式:

S2r=cos(2ω0t)。

在该示例中,频率3f0的数字参考信号具有以下形式:

S3r=sin(3ω0t)。

磁通门电流传感器10进一步包括激励电路23。激励电路23在FPGA中实现。

激励电路23连接到高频发生器22。

激励电路23包括原始激励电路24和激励伺服控制电路25。

原始激励电路24接收频率f0的数字参考信号和频率3f0的数字参考信号,并且原始激励电路24从这些信号产生频率f0的部分数字激励信号和频率3f0的部分数字激励信号。

在该示例中,频率f0的部分数字激励信号具有以下形式:

S1p=k1.sin(ω0t)。

在该示例中,频率3f0的部分数字激励信号具有以下形式:

S3p=k2.sin(3ω0t)。

原始激励电路24将频率f0的部分数字激励信号和频率3f0的部分数字激励信号相加在一起以生成原始数字激励信号。原始数字激励信号具有以下形式:

Seb=S1p+S3p=k1.sin(ω0t)+k2.sin(3ω0t)。

激励伺服控制电路25连接到高频发生器22。

激励伺服控制电路25接收频率3f0的数字参考信号,并且激励伺服控制电路25从该频率3f0的数字参考信号产生频率3f0的数字解调信号。

在该示例中,频率3f0的数字解调信号具有以下形式:

S3d=k3.sin(3ω0t)。

激励伺服控制电路25包括第一乘法器27、第二乘法器28、积分器29、以及第一放大器30。第一放大器30连接到积分器29的输出。

第一乘法器27将数字测量信号Sm乘以频率3f0的数字解调信号。所产生的信号被用作积分器29的输入。

应当观察到,第一乘法器27和积分器29充当第一同步解调器。

第一放大器30由此产生数字误差信号。第二乘法器28将原始数字激励信号Seb乘以数字误差信号以获得数字激励信号。数字激励信号具有以下形式:

Se=k0.(k1.sin(ω0t)+k2.sin(3ω0t))。

磁通门电流传感器10进一步包括退磁伺服控制电路32。退磁伺服控制电路32被纳入FPGA中。

退磁伺服控制电路32连接到高频发生器22。

退磁伺服控制电路32接收频率2f0的数字参考信号,并且退磁伺服控制电路32从该频率2f0的数字参考信号产生频率2f0的数字解调信号。

在该示例中,频率2f0的数字解调信号具有以下形式:

S2d=k4.cos(2ω0t)。

退磁伺服控制电路32包括第三乘法器33、低通滤波器34、以及第二放大器35。第二放大器35连接到低通滤波器34的输出。

第三乘法器33将数字测量信号Sm乘以频率2f0的数字解调信号。所产生的信号被用作低通滤波器34的输入。第二放大器35由此产生作为待测量电流Im的数字镜像的信号,该信号也是数字退磁信号Sdm。数字镜像信号或数字退磁信号Sdm具有以下形式:

Sdm=k.Im。

应当观察到,第三乘法器33和低通滤波器34充当第二同步解调器。

磁通门电流传感器10进一步包括求和电路36。求和电路36在FPGA中实现。

求和电路36对数字激励信号Se和数字退磁信号Sdm进行求和以获得数字注入信号Si。这给出:

Si=k0.(k1.sin(ω0t)+k2.sin(3ω0t))+kIm。

磁通门电流传感器10进一步包括注入电路37。注入电路37形成模拟部分16的一部分。

注入电路37连接到求和电路36和测量绕组14。

注入电路37包括数模转换器(DAC)38。

在该示例中,DAC 38是12位转换器,并且该转换器的操作以频率Fech(Fech=100MHz)进行时钟控制。DAC 38自然地可以呈现不同的特性。

DAC 38获取数字注入信号Si,从数字注入信号Si产生模拟激励电流Ie,并将激励电流Ie注入到测量绕组14中。

下文描述磁通门电流传感器10的操作。

激励电路23生成数字激励信号Se,该数字激励信号Se被变换为激励电流Ie并被注入到测量绕组14中。

测量电压Ve被获取并且随后被数字化以产生数字测量信号Sm。

在第二放大器35的输出处获得作为待测量电流Im的数字镜像的信号。该数字镜像信号被用于估计待测量电流Im。

数字镜像信号也是数字退磁信号Sdm,其用以补偿由待测量电流Im产生的磁通量。

藉由求和电路36和并联连接,容易将数字退磁信号Sdm和数字激励信号Se相加在一起。激励电流由此用以激励磁芯13并且还用以对磁芯13进行退磁。退磁电流由此被纳入激励电流Ie中。

磁芯13的饱和引起测量电压Ve中的不对称性,所述测量电压Ve由频率f0的sin(ω0t)分量(对应于基波)和频率2f0的cos(2ω0t)分量(对应于二次谐波分量)的总和构成。

应当观察到,频率f0的部分数字激励信号和频率3f0的部分数字激励信号的振幅被设置成获得激励电流Ie,其中频率3f0的分量(或三次谐波分量)与频率f0的分量(或基波)同相。

如在使用第一同步解调器进行同步解调之后获得的测量电压Ve的三次谐波分量为正。在磁芯13饱和的情况下,三次谐波分量比基波衰减地更强烈,并且在同步解调之后,三次谐波分量变为负,这是由于三次谐波与基波变成反相。

由此,当激励电流Ie使得磁芯13接近饱和时,测量电压Ve的第一谐波分量和三次谐波分量的振幅之比发生变化,直至三次谐波分量变为零,并且之后直至三次谐波分量的相位反相。与测量电压Ve的三次谐波分量变为零相对应的操作点由此是磁通门电流传感器10的最佳操作点。该最佳操作点对应于绘制传递函数的图1曲线中的弯曲部9。

在来自第一放大器30的输出处获得数字误差信号。

数字误差信号用以对激励电流Ie进行伺服控制。伺服控制包括控制激励电流Ie以使测量电压Ve的三次谐波分量为零。磁通门电流传感器10由此在最佳操作点上连续操作。这用以获得具有由待测量电流Im引入并且在测量电压Ve中可检测的不对称性的最大增益。应当观察到,通过同步地解调三次谐波分量的这种伺服控制对于外部电磁扰动相对不敏感,这是因为所有除了频率3f0之外的频率的信号生成具有由连接到第三乘法器33的输出的低通滤波器34滤波的分量的互调产物。还可以观察到,该伺服控制不需要非常快,这是因为来自外部参数(温度、老化)的变化相对较慢。

由此,测量绕组14同时被用于激励磁芯13、控制激励、测量待测量电流Im、以及补偿由待测量电流Im在磁芯13中产生的磁通量(退磁)。

在单个测量绕组14中组合各功能用以简化磁通门电流传感器10,降低其成本和重量、以及促进其制造。

还应当观察到,用于处理测量的系统主要是数字的:单个FPGA用以执行该处理系统的主要部分。

对处理系统进行数字化增加该处理系统的可靠性和稳健性(特别是在温度方面)、降低其成本、促进其制造、并提高其工业可再现性。

通过由第一同步解调器执行的解调得到的在调节操作点方面的改进还用以获得更好的噪声抗扰性。

此外,同步解调器的使用使得可以在高频下操作,从而允许待测量电流Im的宽带宽,同时保留对外部电磁扰动非常良好的抗扰性。

由于总是在对应于饱和弯曲部9的最佳操作点处执行测量,因此磁通门电流传感器10的灵敏度在温度范围中是恒定的。磁通门电流传感器10的准确性由此在大的温度范围上良好。

如上面提到的,磁通门电流传感器10测量待测量且在导体11中流动的电流Im。

当待测量电流Im较小(例如,小于1安培(A))时这种情况不会引起任何特定的困难。

然而,当待测量电流较大时,出现主要困难。

用以补偿由待测量电流Im在磁芯13中产生的磁通量的退磁电流必须也非常大。退磁电流的振幅需要等于待测量电流的振幅除以变压器12的变压比,该变压比与初级绕组和次级绕组的特性相关联。

然而,测量绕组14的匝数受到其大小和所产生电感的限制。电感越大,(来自数字退磁信号Sdm的)退磁电流的变化率就越受限,并且由此磁通门电流传感器10的带宽就越受限。由此,增加次级绕组的匝数不是有效的解决方案。

增加退磁电流也不是有效的解决方案。具体而言,这会涉及生成与大的退磁电流相关联的非常大的退磁电压,这难以使用标准组件来实现。

应当观察到,该问题并非特定于如上所述的磁通门电流传感器10,而是适用于所有磁通门电流传感器(并且具体而言适用于包括仅专用于退磁的绕组的那些磁通门电流传感器)。

为了解决该困难,利用分流桥以减小待测量电流的振幅。

参照图5至7,磁通门电流传感器10包括印刷电路40,该印刷电路40上特别安装有形成数字部分15和模拟部分16的多个电子组件。

在该示例中,印刷电路40包括第一导电层41、第二导电层42、以及绝缘层43。在该示例中,第一导电层41和第二导电层42中的每一者在印刷电路40的各个相对面上延伸。

第一导电层41具有第一迹线44,并且第二导电层42具有第二迹线45。绝缘层43由此在第一迹线44与第二迹线45之间延伸。

印刷电路40进一步包括具有至少一个第一电镀通孔47的第一贯通组装件以及具有至少一个第二电镀通孔48的第二贯通组装件。在该示例中并且具体而言,第一贯通组装件具有多个第一电镀通孔47,并且第二贯通组装件具有多个第二电镀通孔48。在该示例中,第一电镀通孔47和第二电镀通孔48都具有相同的第一直径。

“电镀通孔”也可以被称为“通孔”。可以通过任何类型的方法来制作“电镀通孔”。具体而言可以通过沉积金属材料或任何类型的导电材料来使“电镀通孔”导电。还可以通过插入由金属或任何类型的导体制成的管或铆钉来使“电镀通孔”导电。

每个第一电镀通孔47和每个第二电镀通孔48通过延伸穿过绝缘层43来将第一迹线44和第二迹线45连接在一起。

第一贯通组装件和第二贯通组装件分别形成分流桥53的第一分支51和第二分支52。

由此,在该示例中,待测量电流Im实际上不是具有待确定值的主电流Ip,而是通过对主电流Ip进行分流来获得待测量电流Im,并且随后将其用于估计主电流Ip的值。主电流Ip在第一迹线44中、分流桥53的第一分支51和第二分支52中、以及第二迹线45中流动。

在该示例中,由此可以清楚地看到,传送待测量电流的上述导体11由第二贯通组装件(或第二分支52)构成。

在该示例中,主电流Ip等于10A。

第一贯通组装件中的第一电镀通孔47的数目比第二贯通组装件中的第二电镀通孔48的数目大九倍。第二分支52的第二电阻由此比第一分支51的第一电阻大九倍。

在分流桥53的第二分支52中流动的待测量电流Im等于1A,而在分流桥53的第一分支51中流动的电流等于9A。

在该示例中,利用在相同印刷电路40中毗邻的多个相同直径的电镀通孔的电特性的可再现性属性。

第一分支51的第一电阻和第二分支52的第二电阻并非准确已知,但由于该可再现性,因此非常准确地知晓这两个电阻的比率。

第一贯通组装件和第二贯通组装件由此等效于具有良好受控比率的两个分流电阻器。

由此非常准确地知晓待测量电流Im与主电流Ip之间的比率。测量待测量电流Im使得能够非常准确地估计主电流Ip,同时减小主电流以减小所需要的退磁电流。

待测量电流Im通过使用上面提到的变压器12来测量。

变压器12包括印刷电路40,或者更精确而言,假定印刷电路还携带数字部分15和模拟部分16,则变压器12包括印刷电路40的一部分。

如上所述的第二贯通组装件在本文中也被称为“初级贯通组装件”。第二电镀通孔48是“初级电镀通孔”。

印刷电路40还包括第三贯通组装件和第四贯通组装件,该第三贯通组装件包括延伸穿过绝缘层43的至少一个第三电镀通孔56,该第四贯通组装件包括延伸穿过绝缘层43的至少一个第四电镀通孔57。在该示例中并且具体而言,第三贯通组装件包括多个第三电镀通孔56,并且第四贯通组装件包括多个第四电镀通孔57。在该示例中,第三电镀通孔56和第四电镀通孔57都具有相同的第二直径,出于可用空间的原因,该第二直径小于第一电镀通孔47和第二电镀通孔48的第一直径。第三电镀通孔56的数目等于第四电镀通孔57的数目。

第三和第四贯通组装件一起形成在本文中被称为“次级贯通组装件”的组装件。在次级贯通组装件中,第三电镀通孔56形成至少一个、并且具体而言多个“第一次级电镀通孔”56,而第四电镀通孔57形成至少一个、并且具体而言多个“第二次级电镀通孔”57。

变压器12还包括磁芯13。磁芯13沿印刷电路40的厚度延伸。

磁芯13具有管的形状,该管具有矩形的内侧和外侧剖面。应当观察到,磁芯13自然地可以具有不同的形状。磁芯13包括初级磁芯部分60和次级磁芯部分61。

初级贯通组装件在磁芯13的内部、在初级磁芯部分60的附近延伸。

初级贯通组装件由此形成变压器12的初级绕组的一部分,所述初级绕组在该示例中仅具有一匝。

第一次级电镀通孔56在磁芯13的内部、在次级磁芯部分61的附近延伸。第二次级电镀通孔57在磁芯13外部、在次级磁芯部分61的附近延伸。

可以看到,第一次级电镀通孔56和第二次级电镀通孔57通过在第一导电层41中和第二导电层42中延伸的导电元件65(举例而言但并非必然,迹线)连接在一起。图7中仅示出了两个导电元件65。

第三贯通组装件由此形成变压器12的次级绕组的第一部分。第四贯通组装件由此形成变压器的次级绕组的第二部分。次级贯通组装件由此形成变压器12的次级绕组的一部分。

次级绕组具有多个匝,每一匝包括第一次级电镀通孔56、第二次级电镀通孔57、以及导体元件65。

由此可见,变压器12的次级绕组是上面提到的测量绕组14。

下文描述如何制造印刷电路40和沿印刷电路40的厚度延伸的磁芯13。

印刷电路40包括第一预浸层和第二预浸层(其中“预浸(prepreg)”是“预浸渍(pre-impregnated)的简称)。第一和第二预浸层未被聚合。

磁芯13包括磁粉和构成磁粉粘合剂的树脂的混合物。

磁粉由晶体结构、特别是钇铁石榴石(Y

树脂是环氧树脂。

磁芯13通过丝网印刷被沉积在第一预浸层上。

之后,用第二预浸层覆盖磁芯13。

随后使印刷电路40通过烘箱。

随后对印刷电路40钻孔以制作上述电镀通孔。

替换地,可以使用增材制造技术通过激光烧结来制造磁芯13。

磁粉被沉积在第一预浸层上。之后,使用激光束将磁粉层聚结在预定义区域中以形成磁芯13。

随后用第二预浸层覆盖磁芯13。

通过激光烧结制造磁芯13看起来更加有效。具体而言,当通过丝网印刷进行制造时,观察到在磁粉和树脂的混合物中将发现与磁粉颗粒中一样多的气隙。这些气隙降低磁芯13的性能。利用激光烧结,磁粉颗粒被熔化,这避免了产生所述气隙。

自然地,本发明不限于所描述的实施例,而是涵盖了落入如由权利要求书限定的本发明范围内的任何变型。

阐述了磁通门电流传感器包括数字部分和模拟部分,并且ADC和DAC形成模拟部分的一部分。自然地,可以考虑这些组件是数字组件,并且甚至可以考虑这些组件被直接纳入FPGA中(或微控制器中或某种其他组件中),在该情形中它们将形成数字部分的一部分。

上面阐述了包括第一迹线的第一导电层和包括第二迹线的第二导电层中的每一者在印刷电路的各个相对面上延伸。自然地,第一导电层和第二导电层可以是印刷电路的内部层,这些层由一个或多个绝缘层分隔开。

上面,每个贯通组装件被描述为包括一个或多个电镀通孔。上面,电镀通孔都穿过单个绝缘层。自然地,电镀通孔可以穿过多个绝缘层,或者甚至穿过一个或多个绝缘层以及一个或多个导电层。不同的贯通组装件同样可以很好地穿过不同的层堆叠。

上面阐述了次级贯通组装件包括位于磁芯的次级磁芯部分的相对侧的至少一个第一次级电镀通孔和至少一个第二次级电镀通孔。自然地,也可以使初级贯通组装件包括位于磁芯的初级磁芯部分的相对侧的至少一个第一初级电镀通孔和至少一个第二初级电镀通孔。也可以使这两种配置共存。

- 具有磁通门的电流传感器

- 一种具有开口气隙的磁通门电流传感器磁芯