用于针对非二进制码的消息传递解码的基本校验节点处理的排序设备和方法

文献发布时间:2023-06-19 10:08:35

技术领域

本发明总体上涉及数字通信,并且具体地涉及用于对使用纠错码编码的信号进行解码的方法和设备。

背景技术

纠错码在若干数据处理和存储设备及系统中实现,以提供可靠且无错误的传输,以及允许在存在噪声和/或干扰的情况下可靠地存储数据。

其中使用纠错码的示例性应用包括例如在无线自组织网(例如,在Wi-Fi

纠错码可以被分类为两个种类:线性码和非线性码。与非线性纠错码相比,线性纠错码的实现方式复杂度低,因此特别有利。示例性线性纠错码包括卷积码和线性块码,例如,Hamming码、Reed-Solomon码、Turbo码、极化码和低密度奇偶校验(LDPC)码。

LDPC码已经被证明是非常高效的码。特别地,非二进制LDPC码提供的传输速率被证明接近可以在传输信道上发送的最大信息量。非二进制LDPC码提供高频谱效率编码,并且性能优于二进制LDPC码。

给定线性纠错码的线性结构,可以在接收机设备中使用迭代消息传递算法来对使用(多个)线性纠错码编码的信号进行解码。

消息传递算法使用用于解码数据的码的图形表示,其被称为“Tanner图”。Tanner图包括节点的两个集合,其分别被称为“变量节点”和“校验节点”。每个变量节点与码的奇偶校验矩阵的一列相关联。每个校验节点与奇偶校验矩阵的一行相关联,即,与奇偶校验等式相关联。变量节点和校验节点经由边缘(edge)连接。变量节点与校验节点之间的连接由奇偶校验矩阵的非零条目确定。

变量节点和校验节点形成处理单元。消息传递算法基于在校验节点处理单元与变量节点处理单元之间交换表示编码的数据的消息,该消息与用于编码数据的码的图形表示相关联。解码过程包括通过计算变量节点消息进行的变量节点更新、通过计算校验节点消息进行的校验节点更新以及码字决策制订。每个校验节点消息和变量节点消息包括一个或多个分量,这些分量包括符号以及与该符号相关联的可靠性度量。

针对非二进制码(例如,非二进制LDPC码)的示例性解码算法包括:

-例如在L.Barnault和D.Declercq的“Fast decoding algorithm for LDPC overGF(q)”(Proceedings of IEEE Information Theory Workshop,第70-73页,2003年4月)中公开的“q-aray和积(sum-product)”算法;

-例如在V.Savin的“Min-max decoding for non-binary LDPC codes”(Proceedings of IEEE International Symposium on Information Theory,第960-964页,2008年7月)中公开的“最小-最大”算法;

-例如在D.Declercq和M.Fossorier的“Decoding algorithms for non-binaryLDPC codes over GF”(IEEE Transactions on Communications,vol.55,no.4,第633-643页,2007年4月)中公开的“扩展最小和(EMS)”算法,以及

-例如在J.O.Lacruz、F.García-Herrero、J.Valls和D.Declercq的“One MinimumOnly Trellis Decoder for Non-Binary Low-Density Parity-Check Codes”(IEEETransactions on Circuits and Systems I:Regular Papers,vol.62,no.1,第177-184页,2015年1月)和E.Li、F.García-Herrero、D.Declercq、K.Gunnam、J.O.Lacruz和J.Valls的“Low latency T-EMS decoder for non-binary LDPC codes”(2013AsilomarConference on Signals,Systems and Computers,Pacific Grove,CA,2013年,第831-835页)中公开的“Trellis EMS解码器(T-EMS”)。

EMS算法基于对数尺度计算,以通过将乘积运算转换为简单求和运算来降低计算复杂度。

EMS算法的最大复杂度是在校验节点处理单元处执行的计算。为了进一步减轻在校验节点处理单元处的计算复杂度和存储器要求,EMS算法还对变量节点消息和校验节点消息应用排序和截断操作。根据与给定消息(变量节点消息或校验节点消息)中包括的符号相关联的可靠性度量的次序来执行消息排序。执行消息截断以保留给定消息(变量节点消息或校验节点消息)中包括的预定义数量的最可靠的符号。

可以根据各种架构来执行在校验节点处理单元级别处对校验节点消息的计算。现有的校验节点架构包括在C.Marchand等人的“Extended-Forward Architecture forSimplified Check Node Processing in NB-LDPC Decoders”(SIPS,2017年,法国)中公开的“基于校验子的架构”、“向前-向后架构”和被称为“扩展向前架构”的近期架构。

使用基于校验子的架构,校验节点处理单元通过执行两个步骤来计算校验节点消息。第一步骤专用于根据所有接收到的变量节点消息计算被称为“校验子”的值的集合。第二步骤的目的是根据计算出的校验子的集合来生成(多个)校验节点消息。因此,与要被递送到给定变量节点处理单元的每个校验节点消息相关联地执行去相关操作。去相关操作包括从计算出的校验子中消除先前从被配置为接收计算出的校验节点消息的变量节点处理单元接收到的变量节点消息的贡献。在P.Schlafer、N.When、M.Alles、T.Lehnigk-Emden和E.Boutillon的“Syndrome based check node processing of high order NB-LDPCdecoders”(Proceedings of the International Conference on Telecommunications,第156-162页,2015年4月)和P.Schlafer等人的“A new Architecture for High Speed,Low Latency NB-LDPC Check Node Processing”(Proceedings of IEEE InternationalSymposium on Personal,Indoor and Mobile Radio Communications,2015年8月)中公开了基于校验子的架构。

基于校验子的架构允许并行计算,这对于对在高阶Galois域上构造的码进行解码特别有利。然而,利用这样的架构,计算复杂度由计算出的校验子的数量主导,该校验子的数量随着接收到的变量节点消息的数量的增加而增加。

在向前-向后架构中,由校验节点处理单元执行的计算被划分为涉及多个基本校验节点处理单元(下文称为“基本校验节点处理器”)的多个基本计算,每个基本校验节点处理器被配置为:根据从接收到的变量节点消息导出的第一消息和第二消息来确定基本校验节点消息。根据由基本校验节点处理器确定的基本校验节点消息来递归地构造/确定校验节点消息。

在向前-向后架构中实现的基本校验节点处理器的作用是:在第一消息和第二消息中包括的分量的所有可能的组合之中,确定预定义数量的分量,这些分量包括最可靠的且全部彼此不同的符号。因此,基本校验节点处理器通过应用计算操作,随后应用排序操作和冗余消除操作,来确定基本校验节点消息。在计算操作期间,基本校验节点处理器通过对第一消息和第二消息的分量中包括的符号和可靠性度量应用加法运算来确定辅助分量(也被称为“气泡(bubble)”)。排序操作的目的是根据辅助分量中包括的符号的可靠性来对辅助分量进行排序。冗余消除操作的目的是在包括冗余符号的辅助分量之中保留包括最可靠的冗余符号的辅助分量。

针对基本校验节点处理器的设计的早期工作包括在E.Boutillon和L.Conde-Canencia的“Bubble check:a simplified algorithm for elementary check nodeprocessing in extended min-sum non-binary LDPC decoders”(Electronics Letters,vol.46,no.9,第633-634页,2010年4月)中公开的气泡校验算法。

第一消息和第二消息中包括的分量的可能组合的数量可能导致排序操作和冗余消除操作的高复杂度。针对基本校验节点处理器的近期算法已经被设计来处理该复杂度问题,这些算法包括:

-在E.Boutillon、L.Conde-Canencia和A.Al Ghouwayel的“Design of a GF(64)-LDPC Decoder based on the EMS algorithm”(IEEE Transactions on Circuits andSystems,vol.60,no.10,第2644-2656页,2013年10月)中公开的“L-气泡校验”算法,以及

-在O.Abassi、L.Conde-Canencia、A.Al Ghouwayel和E.Boutillon的“A NovelArchitecture For Elementary Check Node Processing In Non-Binary LDPCDecoders”(IEEE Transactions on Circuits and Systems II:Express Briefs,vol.64,no.2,第136-140页,2017年)中公开的“S-气泡校验”算法。

L-气泡和S-气泡算法既基于基本校验节点处理的矩阵表示,还基于针对确定基本校验节点消息的分量考虑的第一消息和第二消息的分量的组合数量的减少。矩阵的元素对应于辅助分量(气泡)。矩阵元素的总数对应于第一消息和第二消息的分量的所有可能的组合。L-气泡算法通过将在排序操作和冗余消除操作期间处理的辅助分量减少到表示基本校验节点处理的矩阵的前两行和前两列中包括的气泡,从而降低了排序操作和冗余消除操作的复杂度。S-气泡算法是L-气泡算法的变型,其中表示在表示基本校验节点处理的矩阵中的辅助分量的选择次序的路径被优化,从而实现了对基本校验节点处理器的硬件设计的简化。

根据扩展向前架构,多个基本校验节点处理器用于校验子的计算,因此利用了基于验证子的架构的并行化优势和基本校验节点处理的线性复杂度。为了使用该架构达到最佳性能,基本校验节点处理器可能不执行冗余消除操作。该步骤可以在去相关操作之后应用。

与其他现有的迭代解码算法相比,EMS算法在硬件复杂度和通信性能之间提供了很好的折中。特别地,使用基本校验节点处理来将处理划分为多个计算可以有利地提供校验节点处理单元的高速率和低成本设计。达到这样的性能要求进一步减少基本校验节点处理中涉及的计算操作,实质上是减少排序操作的复杂度。

因此,需要针对在校验节点处理单元中实现的基本校验节点处理器开发低复杂度的架构,以对通常使用非二进制线性纠错码(特别是使用非二进制LDPC码)编码的信号进行解码。

发明内容

为了解决这些问题和其他问题,提供了一种排序设备,该排序设备用于通过对辅助分量进行排序来确定在非二进制纠错码解码器中实现的基本校验节点处理器中的基本校验节点分量,该辅助分量被存储在多个FIFO存储器中,每个FIFO存储器被指派有FIFO编号索引,被存储在给定FIFO存储器中的每个辅助分量包括辅助符号、表示辅助符号的可靠性的辅助可靠性度量以及被指派给给定FIFO存储器的FIFO编号索引。排序设备包括顺序布置的多个复用器,这些复用器被配置为初始化候选基本校验节点分量的集合,每个候选基本校验节点分量是根据FIFO存储器中的一个被确定的,并且其对应于被存储在FIFO存储器中的辅助分量之中包括最可靠的辅助符号的辅助分量。根据辅助符号的可靠性度量对候选基本校验节点分量进行排序。每个复用器34-m被配置为执行以下步骤的一次或多次迭代:

-接收从FIFO存储器中提取的包括最可靠的候选符号的辅助分量,该FIFO存储器被指派有在先前迭代中确定出的候选基本校验节点分量中包括的FIFO编号索引;以及

-通过在接收到的辅助分量、由复用器34-m在先前迭代中确定出的候选基本校验节点分量以及由后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量之中选择一个分量,来更新在先前迭代中确定出的候选基本校验节点分量。

排序设备被配置为通过选择包括最可靠的候选符号的候选基本校验节点分量,在一次或多次迭代中的每次迭代中确定基本校验节点分量。

根据一些实施例,基本校验节点处理器可以被配置为接收从两个或更多个变量节点消息导出的第一消息和第二消息,该基本校验节点处理器包括计算单元,该计算单元被配置为根据第一消息和第二消息确定辅助分量。

根据一些实施例,第一消息包括第一给定数量的分量,并且第二消息包括第二给定数量的分量,第一消息和第二消息的每个分量包括符号和关联于该符号的可靠性度量,计算单元被配置为根据第一消息中包括的分量和第二消息中包括的分量来确定辅助分量之中的每个辅助分量,计算单元被配置为:

-通过在非二进制纠错码的构造的代数结构上应用第一加法运算,来确定每个辅助分量中包括的辅助符号,该第一加法运算被应用于第一消息的分量中包括的符号和第二消息的分量中包括的符号;

-通过在预定义的代数结构上应用第二加法运算来确定与每个辅助符号相关联的辅助可靠性度量,该第二加法运算被应用于与第一消息的分量中包括的符号相关联的可靠性度量以及与第二消息的分量中包括的符号相关联的可靠性度量;

可以根据辅助符号的递减的可靠性来对被存储在每个FIFO存储器中的辅助分量进行排序。

根据一些实施例,可以在包括实数域、整数域和自然数域的组中选择预定义的代数结构。

根据一些实施例,分量的第一给定数量和分量的第二给定数量可以相等。

根据其他实施例,分量的第一给定数量和分量的第二给定数量可以不同。

根据一些实施例,其中,基本校验节点处理器在校验节点处理单元中实现,该校验节点处理单元被配置为在多次消息交换迭代期间与在非二进制纠错码中实现的至少一个变量节点处理单元交换两个或更多个变量节点消息,基本校验节点处理器可以被配置为取决于在包括以下各项的组中选择的至少一个参数来预先确定辅助分量的数量:消息交换迭代的次数、非二进制纠错码的构造的代数结构、信噪比、第一消息的分量的第一预定义数量或第二消息的分量的第二预定义数量中的一个或多个、以及基本校验节点处理器在校验节点处理单元内的位置。

根据一些实施例,候选基本校验节点分量可以包括候选符号和关联于候选符号的候选可靠性度量,每个复用器34-m与可靠性度量比较器36-m相关联,该可靠性度量比较器36-m被配置为在接收到的辅助分量中包括的辅助可靠性度量与由复用器34-m在先前迭代中确定出的候选基本校验节点分量中包括的候选可靠性度量之间执行比较,每个复用器34-m被配置为执行用于进行以下操作的控制动作:取决于由与复用器34-m相关联的可靠性度量比较器36-m执行的比较以及由与后续复用器34-(m+1)相关联的可靠性度量比较器36-(m+1)执行的比较,在接收到的辅助分量和由复用器34-m和后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量之中选择分量。

根据一些实施例,每个复用器34-m可以被配置为:

-通过以下操作来执行保持动作:在确定接收到的辅助分量中包括的辅助符号比由复用器34-m在先前迭代中确定出的候选基本校验节点分量中包括的候选符号更可靠时,将候选基本校验节点分量设置为由复用器34-m在先前迭代中确定出的候选基本校验节点分量;

-通过以下操作来执行插入动作:在确定辅助分量中包括的辅助符号不如由复用器34-m在先前迭代中确定出的候选基本校验节点分量中包括的候选符号可靠,且辅助符号比由后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量中包括的候选符号更可靠时,将候选基本校验节点分量设置为接收到的辅助分量;

-通过以下操作来执行移位动作:在确定接收到的辅助分量中包括的辅助符号比由后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量中包括的候选符号更可靠时,将候选基本校验节点分量设置为由后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量。

还提供了一种用于通过对辅助分量进行排序来确定在非二进制纠错码解码器中实现的基本校验节点处理器中的基本校验节点分量的排序方法,该辅助分量被存储在多个FIFO存储器(33-n)中,每个FIFO存储器(33-n)被指派有FIFO编号索引。被存储在给定FIFO存储器中的每个辅助分量包括辅助符号、表示辅助符号的可靠性的辅助可靠性度量以及被指派给给定FIFO存储器的FIFO编号索引。排序方法包括通过多个复用器(34-m)执行候选基本校验节点分量的集合的初始化,每个候选基本校验节点分量是根据FIFO存储器中的一个被确定的,并且其对应于被存储在FIFO存储器中的辅助分量之中包括最可靠的辅助符号的辅助分量。根据辅助符号的辅助可靠性度量对候选基本校验节点分量进行排序。方法包括通过每个复用器(34-m)执行以下步骤的一次或多次迭代:

-接收从FIFO存储器(33-n)中提取的包括最可靠的候选符号的辅助分量,该FIFO存储器(33-n)被指派有在先前迭代中确定出的候选基本校验节点分量中包括的FIFO编号索引;以及

-通过在接收到的辅助分量、由复用器34-m在先前迭代中确定出的候选基本校验节点分量以及由后续复用器34-(m+1)在先前迭代中确定出的候选基本校验节点分量之中选择一个分量,来更新在先前迭代中确定出的候选基本校验节点分量;

方法还包括通过选择包括最可靠的候选符号的候选基本校验节点分量,在一次或多次迭代中的每次迭代中确定基本校验节点分量。

有利地,与现有技术相比,特别是在考虑大量气泡时,根据本发明的各种实施例的排序操作实现延迟和复杂度的降低。

有利地,提出的排序操作的复杂度根据排序气泡的数量是线性的,并且其延迟不取决于排序气泡的数量。

有利地,根据本发明的各种实施例的排序操作使得能够以减少的关键路径对已经使用非二进制纠错码编码的信号进行解码。

在查看附图和下面的具体实施方式之后,本发明的其他优点对于技术人员将变得显而易见。

附图说明

并入并构成本说明书一部分的附图示出了本发明的各种实施例以及上面给出的本发明的一般描述以及下面给出的实施例的详细描述。

图1是根据一些实施例的本发明在通信系统中的示例性应用的框图;

图2是根据其中使用EMS解码算法的一些实施例的非二进制纠错码解码器的框图;

图3是示出根据其中使用EMS算法的一些实施例的在校验节点处理单元中实现的基本校验节点处理器的结构的框图;

图4示出了根据一些实施例的将辅助分量分组到路径中的两个示例性分组;

图5是描绘根据其中执行迭代排序的一些实施例的用于根据第一消息和第二消息确定基本校验节点消息的方法的流程图;以及

图6是描绘根据一些实施例的用于执行控制动作的方法的流程图。

具体实施方式

本公开的实施例提供了用于以低计算复杂度和低延迟来对使用非二进制纠错码编码的信号进行解码的设备、方法和计算机程序产品。特别地,这些设备、方法和计算机程序产品为在校验节点处理单元中实现的基本校验节点处理器提供了高效的减少延迟且减少复杂度的架构,该架构在迭代消息传递解码器中使用以对使用非二进制纠错码编码的信号进行解码。

根据公开的各种实施例的方法、设备和计算机程序产品可以在若干类型的应用中使用的若干类型的数字数据传输和存储设备以及系统中实现。示例性设备和系统包括但不限于:计算机、磁盘、膝上型计算机、电话、智能电话、记录器、基站、无人机、卫星、物联网设备(IoT)、嵌入式设备等。示例性应用包括磁和光记录、数字电视和视频广播、数字通信等。

仅出于说明的目的,将参考数字通信系统对本公开的一些实施例进行以下描述。然而,技术人员将容易地理解,本公开的各种实施例可以被集成在用于其他应用的其他类型的系统(例如,定位系统、存储器和存储系统以及航天器系统)中。

参考图1,示出了本公开在数字通信系统100中的示例性应用。通信系统100可以是例如:

-有线;

-无线(例如,无线电或可见光通信系统);

-光学(例如,基于光纤的、基于激光的);

-声学(例如,水下声学通信系统);

-分子(例如,用于地下结构,例如隧道和管道或水下环境)。

通信系统100可以至少包括发射机设备10和接收机设备12。发射机设备10(在下文中也被称为“发射机”)可以被配置为经由传输信道11将数据信息传送给接收机设备12(在下文中也被称为“接收机”)。

在本公开在诸如计算机联网系统之类的有线通信系统中的应用中,发射机10和/或接收机12可以是被配置为在有线网络中操作的任何设备。在这种应用中的示例性设备包括连接到小型或大型区域有线网络的计算机、路由器或交换机。在这种情况下,传输信道11可以是用于确保在不同连接的设备之间的数据传输的任何类型的物理电缆。

在本公开在诸如自组织无线网络、无线传感器网络和无线电通信系统之类的无线通信系统中的应用中,发射机10和接收机12可以是被配置为在无线环境中操作的任何类型的固定或移动无线设备。在这种应用中的示例性设备包括膝上型计算机、移动电话、基站和任何计算机设备。在这种情况下,传输信道11可以是任何无线传播介质。此外,传输信道11可以容纳若干发射机10和/或若干接收机12。在这样的实施例中,可以结合纠错码来使用多址技术和/或网络编码技术。示例性多址技术包括时分多址(TDMA)、频分多址(FDMA)、码分多址(CDMA)和空分多址(SDMA)。

在本公开在诸如基于光纤的系统之类的光学通信系统中的应用中,发射机10和接收机12可以是被配置为分别发送和接收在光学链路上传播的数据信息的任何光学收发机设备。传输信道11可以是被设计为在短距离或长距离上承载数据的任何光纤链路。在短距离上使用光纤链路的示例性应用包括诸如数据中心互连之类的高容量网络。在长距离上使用光纤链路的示例性应用包括地面和越洋传输。在这样的实施例中,由发射机10传送的信息符号可以由根据光纤的不同偏振状态被偏振的光学信号携带。根据一种或多种传播模式,光学信号沿着基于光纤的传输信道11传播,直到到达接收机12为止。示例性光学通信系统包括偏振分复用(PDM)系统和模式分复用(MDM)系统。

对于任何类型的有线、无线或光学通信系统,传输信道11可以是任何有噪信道。噪声可能是由于系统组件的热噪声或由天线截获的干扰辐射引起的。其他示例性噪声源包括切换、手动中断、电火花和闪电。在一些实施例中,总噪声可以通过加性高斯白噪声(AWGN)来建模。

此外,根据应用于数字大容量存储装置的一些实施例,可以例如通过擦除信道、二进制对称信道或高斯信道来对传输信道11进行建模。在这样的实施例中,传输信道11可以是可以向其发送(写入)和从其接收(读取)的任何类型的存储设备。

另外地,发射机10和接收机12可以配备有单个或多个天线。特别地,在存在多个发射天线和/或接收天线的情况下,空时编码和解码技术可以结合纠错编码和解码使用。

此外,可以在一个或多个频带上发送编码的数据。当在多个频带上发送编码的数据时,调制器105可以使用诸如OFDM(正交频分复用(Orthogonal Frequency DivisionMultiplexing)的缩写)和FBMC(滤波器组多载波(Filter Bank Multi-Carrier)的缩写)之类的多载波调制格式。

根据本公开的一些实施例,发射机10包括纠错码(ECC)编码器103,其被配置为使用非二进制纠错码将表示为u的数字输入数据块101编码为表示为c的码字向量。接收机12可以被配置为通过传输信道11接收编码的数据或码字向量的有噪副本p。接收机12可以包括纠错码解码器123,其被配置为递送数字输出数据块125作为对原始数字输入数据块101的估计

数字输入数据101可以在被ECC编码器103编码之前被预先压缩。适合于增加信息吞吐量的任何源编码方案(图1中未示出)可以用于执行压缩。由ECC编码器103编码的数据可以由调制器105进一步调制。调制器105可以被配置为将编码的数据映射到模拟信号s上并通过传输信道11发送该模拟信号s。

接收机12可以包括被配置为执行相反功能的相应的处理块。接收机12可以包括解调器121,其被配置为通过在由ECC解码器123对来自传输信道的接收到的信号p进行ECC解码之前对该接收到的信号p执行解调来生成信号y。解调器121可以被配置为将接收到的信号或信道输出移动回到基带,并执行低通滤波、采样和量化。由ECC解码器123解码的数据可以使用任何源解码器(图1中未示出)进一步解压缩。ECC解码器123可以被配置为实现根据本公开的各种实施例的涉及校验节点处理单元和变量节点处理单元的迭代解码器(其被称为“迭代解码算法”)。

仅出于说明的目的,将参考线性块非二进制纠错码对本公开的一些实施例进行以下描述。然而,技术人员将容易地理解,本公开的各种实施例应用于包括非二进制卷积码的任何线性非二进制纠错码。

因此,ECC编码器103可以实现由C(n,K)指定的线性块非二进制纠错码;n和K分别指代码字向量的长度和编码的数据块的长度。ECC编码器103相应地将长度为K的数据块u编码为码字向量c,其中c=(c

线性码C(n,K)可以使用由G表示的生成器矩阵和由H表示的奇偶校验矩阵以矩阵形式表示。使用向量的行表示法,生成器矩阵G的维度为K×n,而奇偶校验矩阵的维度为(n-K)×n。这两个矩阵通过关系G.H

结合矩阵表示,可以使用由

每个变量节点vn∈{1,2,...,n}对应于奇偶校验矩阵的一列。每个校验节点cn∈{1,2,...,n-K}对应于奇偶校验矩阵的一行,即,对应于奇偶校验等式。如果奇偶校验矩阵的条目H

变量节点vn的度d

根据一些实施例,非二进制纠错码C(n,K)的构造的代数结构可以是任何非零交换除法环(commutative division ring),例如,“Galois域”。

仅出于说明的目的,将参考有限域对一些实施例进行以下描述。然而,技术人员将容易地理解,本公开可以应用于诸如非零交换除法环之类的任何除法环状代数结构以及诸如有限除法近环之类的任何近环。可以在文章“Non-binary LDPC codes over finitedivision near rings”(23

对于在Galois域上构造的非二进制线性码,通常用GF(q)表示,其中q>2表示码的基数,这些符号取GF(q)中的值。因此,码字向量c是n个符号的向量,每个符号都属于GF(q)。

仅出于说明的目的,将参考使用非二进制LDPC码对数据进行编码的ECC编码器103对一些实施例进行以下描述。然而,技术人员将容易地理解,本公开的各种实施例也应用于其他非二进制码,例如,非二进制极化码、非二进制卷积码、非二进制turbo码,并且通常应用于非二进制线性块纠错码。非二进制纠错码可以有利地用于高频谱效率编码。

出于示例性目的,在一个实施例中,ECC解码器123实现非二进制LDPC码解码器,以用于对使用非二进制LDPC码由ECC编码器103编码的数据进行解码。

参考EMS算法对本公开进行描述。然而,技术人员将容易地理解,各种实施例应用于诸如最小-最大之类的任何迭代非二进制LDPC码解码器。

为了易于呈现本公开的各种实施例,在说明书的其余部分中将使用以下定义。

基于基本校验节点的架构指代包括一个或多个基本校验节点处理器的校验节点处理单元的任何实现方式架构。

由变量节点处理单元27-vn生成的消息被称为“变量节点消息”。由校验节点处理单元25-cn生成的消息被称为“校验节点消息”。

变量节点消息和校验节点消息可以包括携带表示符号的数据的分量。变量节点消息中包括的分量被称为“变量节点分量”,并且校验节点消息中包括的分量被称为“校验节点分量”。

固有消息(intrinsic message)指代包括被称为固有分量的分量的消息,每个固有分量包括固有符号和与该固有符号相关联的固有可靠性度量。固有可靠性度量是仅根据接收到的序列被计算出的。因此,“固有”一词指代固有可靠性度量仅依赖于(传输)信道。

由基本校验节点处理器处理的第一消息和第二消息指代从由其中实现基本校验节点处理单元的校验节点处理单元接收到的变量节点消息导出的消息。第一消息包括第一预定义数量的分量,并且第二消息包括第二预定义数量的分量。

基本校验节点消息指代由基本校验节点处理器根据第一消息和第二消息计算出的消息。基本校验节点消息的分量被称为基本校验节点分量。

辅助分量(也被称为“气泡”)指代由基本校验节点处理器根据第一消息中包括的分量和第二消息中包括的分量确定出的分量。辅助分量包括辅助符号和与该辅助符号相关联的辅助可靠性度量。

候选基本校验节点分量指代由基本校验节点处理器在由所述基本校验节点处理器执行的对辅助分量的迭代排序的给定迭代中确定出的分量。

参考图2,示出了根据使用EMS算法的一些实施例的迭代非二进制LDPC解码器123的结构。

迭代解码器123可以被配置为根据由向量y=(y

迭代解码器123可以被配置为基于在发射机10处使用的码C(n,K)的Tanner图表示来确定估计

因此,迭代解码器123可以包括n个变量节点处理单元27(也用27-1至27-n或27-vn表示,其中vn=1,...,n)和n-K个校验节点处理单元25(也用25-1至25-(n-K)或25-cn表示,其中cn=1,...,n-K)。

变量节点处理单元27-vn(vn=1,...,n)和校验节点处理单元25-cn(cn=1,...,n-K)可以被配置为在多个消息交换迭代期间迭代地交换变量节点消息和校验节点消息,以根据有噪序列y估计最可靠的码字

根据一些实施例,变量节点消息和校验节点消息中分别包括的变量节点分量和校验节点分量可以携带符号和测量其可靠性的度量(在下文中也被称为“可靠性度量”)的值。可靠性度量的值与符号的可靠性相关。在这样的实施例中,每个变量节点消息(或者校验节点消息)可以包括q个变量节点分量(或者校验节点分量),分量(校验节点分量或变量节点分量)包括:

-GF(q)中的符号的值,以及

-与符号相关联的可靠性度量。

在一些实施例中,符号的可靠性度量可以对应于符号的估计出的概率密度函数,该概率密度函数表示符号正确的概率。特别地,可靠性度量可以在对数域中由对数似然比(LLR)值表示。

取决于可靠性度量的表示,最可靠的符号可以与可靠性度量的最小值或最大值相关联。

LLR度量的一种定义涉及由β

β

在等式(1)中,α

因此,在Galois域中的符号是等概率的假设下,对于第i个符号c

使用LLR度量的这种定义,根据等式(2),最可靠的符号是与最小的LLR值相关联的那些符号。

仅出于说明的目的,将参考在对数域中由对数似然比(LLR)值表示的可靠性度量对一些实施例进行以下描述。然而,技术人员将容易地理解,可以使用其他类型的解码和可靠性度量来测量符号的可靠性。例如,可靠性度量可以是符号的概率密度函数的二次距离或任何单调函数。

根据使用EMS算法的一些实施例,可以根据变量节点消息和/或校验节点消息的可靠性(即,根据变量节点分量和校验节点分量中包括的可靠性度量的给定次序(例如,递增或递减))来对变量节点消息和/或校验节点消息进行排序。此外,变量节点消息可以被截断以便仅保留包括最可靠的符号的预定义数量n

在实施例中,变量节点分量的预定义数量n

在另一实施例中,变量节点分量的预定义数量n

将参考被排序和截断的变量节点消息和校验节点消息来对本公开的实施例进行以下描述,校验节点分量和变量节点分量的数量相等或不同。

由各种变量节点处理单元27-vn和校验节点处理单元25-cn执行的处理可以根据包括但不限于以下描述的三个示例的若干调度机制来实现。

根据第一实现方式,所有变量节点处理单元27-vn(vn=1,...,n)被配置为在第一轮中操作;然后所有校验节点处理单元25-cn(cn=1,...,n-K)可以被配置为更新在其对应集合

根据基于“水平调度”的第二实现方式,校验节点处理单元25-cn(cn=1,...,n-K)被配置为串行操作,从而更新与其连接的所有变量节点处理单元27-vn。特别地,一组校验节点处理单元25-cn可以被配置为并行操作,从而更新所有连接的变量节点处理单元27-vn。

根据基于“垂直调度”的第三实现方式,变量节点处理单元27-vn被配置为串行操作,从而更新与其连接的所有校验节点处理单元25-cn。

消息的交换可以由变量节点处理单元27-vn开始。在解码过程开始时发送给校验节点处理单元25-cn的变量节点消息可以包括固有消息。

迭代解码器123可以相应地包括数据处理单元23,该数据处理单元23被配置为根据接收到的序列来确定固有符号和固有可靠性度量,被表示为x∈GF(q)且属于Galois域(通常属于非二进制纠错码的代数结构)的固有符号与被表示为I

更具体地,数据处理单元23可以包括:

-符号生成器231,其被配置为生成属于其上构造非二进制纠错码的代数结构的固有符号x,以及

-固有可靠性度量生成器233,其被配置为根据接收到的序列y生成与每个固有符号x相关联的固有可靠性度量I

使用等式(2)的LLR表示法,可以根据下式以对数尺度确定与符号x相关联的固有可靠性度量:

在等式(3)中,β

根据一些实施例,固有可靠性度量生成器单元233被配置为从存储单元21加载接收到的信号y,存储单元21被配置为存储接收到的信号y。

在图2中示出的一些实施例中,存储单元21被包括在数据处理单元23内。

在其他实施例中(图2中未示出),存储单元21被包括在数据处理单元23外部的迭代解码器123中。

根据一些实施例,固有可靠性度量生成器233被配置为在迭代解码过程开始之前离线确定固有可靠性度量的至少一部分。在这样的实施例中,固有可靠性度量生成器单元233还可以被配置为将计算出的固有可靠性度量的至少一部分存储在存储单元21中。可以有利地实现这样的实施例以用于对在小阶的代数结构上构造的码进行解码,以将计算出的所有固有可靠性度量存储在存储单元21中。对于高阶的代数结构,可以仅将计算出的固有可靠性度量的一部分存储在存储单元21中。

在一些实施例中,固有可靠性度量生成器233被配置为在迭代解码过程期间在线确定固有可靠性度量。可以有利地实现这样的实施例以用于对高阶非二进制纠错码进行解码,从而实现存储器节省。

在一些实施例中,固有可靠性度量生成器单元233被配置为离线确定固有可靠性度量中的至少一些,并且在线确定其余的固有可靠性度量。

根据一些实施例(在图2中示出),迭代解码器123包括单个数据处理单元23,其被配置为确定要被递送到所有变量节点处理单元27-vn(vn=1,...,n)的固有可靠性度量。

在其他实施例中(未示出),迭代解码器123包括多个数据处理单元23-vn(vn=1,...,n),每个数据处理单元23-vn被包括在变量节点处理单元23-vn(vn=1,...,n)中。

变量节点处理单元27-vn可以被配置为接收从接收到的信号y导出的固有可靠性度量,并且从与集合

类似地,校验节点处理单元25-cn可以被配置为处理由对应于集合

如果处理后的信号满足奇偶校验等式,或者如果在不满足所有奇偶校验约束的情况下达到了消息交换迭代的最大数量,则解码过程可以终止。

因此,迭代解码器123可以包括解码决策单元29,其被配置为在解码过程的每次迭代中接收由变量节点处理单元27-vn计算出的局部决策,并且:

-如果处理后的信号满足奇偶校验等式,则递送处理后的信号作为对原始码字向量的估计;或者

-声明解码失败,但如果在不满足所有奇偶校验约束的情况下达到了迭代的最大数量,则输出最后一次迭代中估计出的码字向量。

本公开的各种实施例提供了在校验节点处理单元25-cn(cn∈{1,...,n-K})中实现的基本校验节点处理器的高效的低复杂度且低成本架构。

根据本公开的各种实施例,校验节点处理单元25-cn实现一个或多个基本校验节点处理器,并且被配置为基于由所述一个或多个基本校验节点处理器执行的多个基本计算来确定至少一个校验节点消息。

在校验节点处理单元25-cn中实现的每个基本校验节点处理器可以被配置为:

-接收从由校验节点处理单元25-cn接收到的三个或更多个变量节点消息导出的第一消息和第二消息,以及

-根据第一消息和第二消息确定基本校验节点消息,该基本校验节点消息包括一个或多个基本校验节点分量。

根据一些实施例,迭代解码器123可以包括两个或更多个校验节点处理单元25-cn(其中cn=1,...,(n-K)),所述两个或更多个校验节点处理单元25-cn中的每一个实现基于基本校验节点的架构。

本公开的各种实施例提供了用于在基本校验节点处理器中进行迭代排序的高效的减少复杂度且减少延迟的技术。

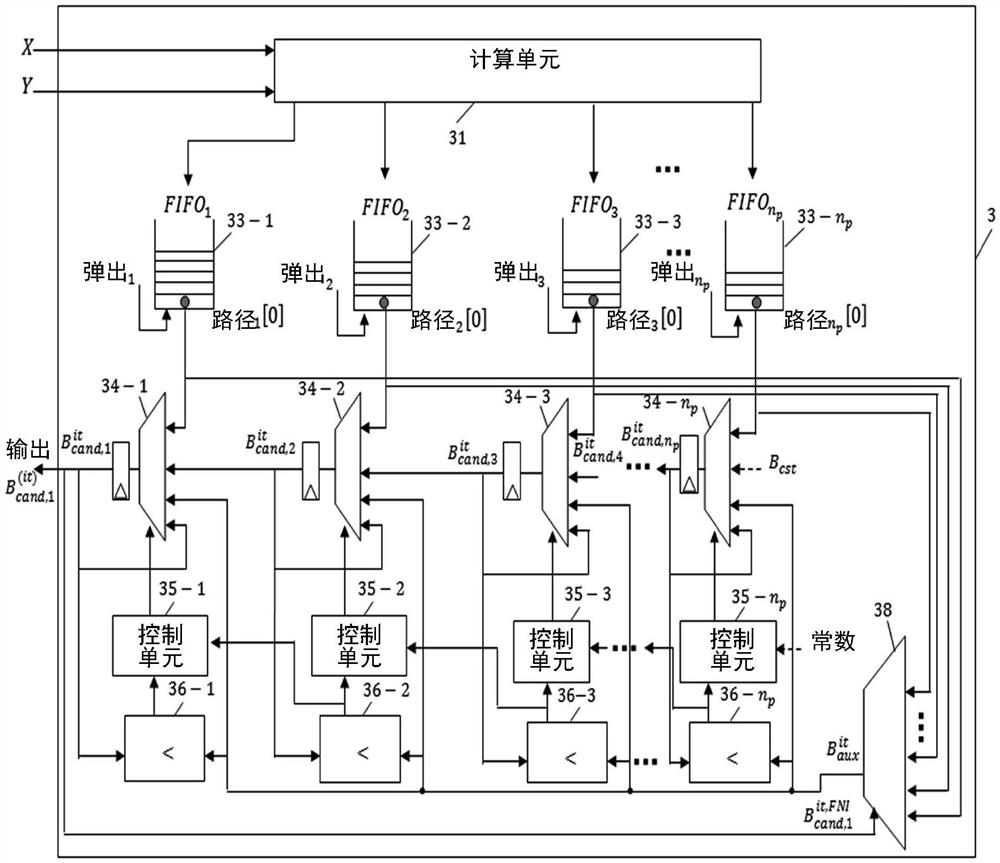

图3是示出在度为d

-从集合

-根据接收到的变量节点消息

根据使用EMS算法与校验节点消息和变量节点消息的排序和截断的一些实施例,每个变量节点消息U

类似地,每个校验节点消息V

在不失一般性的情况下,仅出于说明目的,将参考与符号相关联的可靠性度量的递增次序相对应的递减的可靠性对一些实施例进行以下描述。

基本校验节点处理器3可以被配置为接收由X表示的第一消息,该第一消息包括由

i)X

ii)包括最可靠的符号的分量分别为

根据一些实施例,第一消息和第二消息可以包括相同数量的分量,据此,第一给定数量和第二给定数量相等,即,n

在另一实施例中,第一消息和第二消息可以包括不同数量的分量,据此,第一给定数量和第二给定数量不同,即,n

基本校验节点处理器3被配置为根据第一消息X和第二消息Y确定由E表示的基本校验节点消息,基本校验节点消息E包括由

i)E[e]

ii)包括最可靠的符号的基本校验节点分量为

根据一些实施例,基本校验节点处理器3可以被配置为根据从第一消息X和第二消息Y中包括的分量的组合导出的辅助分量来确定基本校验节点消息E的基本校验节点分量,基本校验节点处理器3被配置为通过对辅助分量进行排序并选择包括最可靠的符号的n

因此,如图3中描绘的,基本校验节点处理器3可以包括:

-计算单元31,其被配置为根据第一消息X和第二消息Y来确定由

-由

-由B

辅助分量的最大可能数量可以由第一消息中包括的分量和第二消息中包括的分量的可能组合的总数给出。辅助分量的最大可能数量可以等于n

辅助分量的预定义数量n

根据一些实施例,计算单元31可以被配置为:

-通过在非二进制纠错码的构造的代数结构上应用第一加法运算,来确定每个辅助分量B

对于在Galois域上构造的纠错码,在Galois域GF(q)上执行等式(4)的第一加法运算。

-通过在包括实数域、整数域和自然数域的组中选择的预定义的代数结构上应用第二加法运算,来确定与每个辅助符号

B

根据一些实施例,基本校验节点处理器3可以被配置为取决于在包括以下各项的组中选择的至少一个参数来预先确定辅助分量的预定义数量n

-在集合

-非二进制纠错码的构造的代数结构(例如,用于在Galois域上构造的码的Galois域),

-信噪比,

-第一消息X的分量的第一预定义数量n

-基本校验节点处理器3在校验节点处理单元25-cn内的位置。

在一些实施例中,计算单元31可以串行地接收第一消息和第二消息的分量,使得在每个时钟周期接收第一消息的一个分量或第二消息的一个分量。

在这样的实施例中,计算单元31可以被配置为取决于接收到的第一消息的分量和第二消息的分量来确定n

取决于第一消息的分量和第二消息的分量的接收次序来对辅助分量进行串行计算,使得能够将计算出的辅助分量分组到由

可以根据辅助符号的递减的可靠性将辅助分量分组到路径中,使得:

-根据满足

-根据辅助符号的递减的可靠性,对每条路径的包括最可靠的辅助符号的辅助分量进行排序,使得

根据一些实施例,如图3中描绘的,在辅助分量的计算期间构造的每条路径Path

参考图4,示出了路径的两个示例性构造,同时根据第一消息和第二消息计算辅助分量。辅助分量的计算相应地使用二维表示来说明。垂直轴指定第一消息的处理后的分量。水平轴指定第二消息的处理后的分量。计算出的辅助分量由实心圆表示。

图4A描绘了四条路径的第一示例性构造,使得:

-根据第二消息的分量Y[0]和第一消息的分量X[x]确定路径Path

-根据第一消息的分量X[0]和第二消息的分量Y[y]确定路径Path

-根据第二消息的分量Y[1]和第一消息的分量X[x]确定路径Path

-根据第一消息的分量X[1]和第二消息的分量Y[y]确定路径Path

图4B描绘了五条路径的第二示例性构造,使得:

-根据第二消息的分量Y[0]和第一消息的分量X[x]确定路径Path

-根据第二消息的分量Y[1]和第一消息的分量X[x]确定路径Path

-根据第二消息的分量Y[2]和第一消息的分量X[x]确定路径Path

-根据第二消息的分量Y[3]和第一消息的分量X[x]确定路径Path

-根据第一消息的分量X[0]和第二消息的分量Y[y]确定路径Path

图4中描绘的两个示例示出了在计算辅助分量时可能的路径构造。然而,技术人员将容易地理解,取决于第一消息和第二消息的分量的接收次序,可以获得其他路径构造。特别地,可以考虑第一消息和第二消息的分量的接收次序,以便尽快计算FIFO存储器的第一元素,即,元素Path

本公开的各种实施例提供了在基本校验节点处理器3中实现的高效且低复杂度的排序设备,以通过对从第一消息和第二消息导出的辅助分量迭代地排序来确定至少一个基本校验节点消息的n

为了促进对本公开的理解,结合下文中在一些实施例的描述中使用的表示法来提供以下定义:

-n

-n

-n

-

-

-

参考图3,基本校验节点处理器3可以包括排序设备,该排序设备被配置为通过根据辅助可靠性度量的给定次序在数量n

因此,在排序过程的第一次迭代中,根据与可靠性度量

每个候选基本校验节点分量

对于每个下一次迭代it=2,...,n

-接收从候选FIFO存储器33-n中提取的且包括最可靠的候选符号的由

-通过执行用于在接收到的辅助分量

在排序过程的每次迭代中对辅助分量的处理在每次迭代中提供n

-包括最可靠的候选符号的候选基本校验节点分量是也由

-每第m个候选基本校验节点分量

换言之,对于可靠性度量的递减(或者递增)次序,在每次迭代中确定出的候选基本校验节点分量满足

排序设备可以被配置为通过在总共n

在第it次迭代中生成包括最可靠的候选符号的候选基本校验节点分量

在至少n

排序设备还可以包括多个(n

在一些实施例中,由复用器34-m执行的控制动作可以是例如保持动作、插入动作或移位动作。然而,技术人员将容易地理解,可以执行其他控制动作。

例如,在每次迭代it=2,...,n

-通过以下操作来执行保持动作:在确定在第it次迭代中接收到的辅助分量

-通过以下操作来执行插入动作:在确定辅助分量中包括的辅助符号

-通过以下操作来执行移位动作:在确定接收到的辅助分量中包括的辅助符号不如由复用器315-(m+1)在先前迭代中确定出的候选基本校验节点分量

由每个复用器34-m执行的控制动作可以取决于由与复用器34-m相关联的可靠性度量比较器36-m以及与复用器34-(m+1)(在复用器34-m的右侧相邻的复用器)相关联的可靠性度量比较器36-(m+1)执行的可靠性度量比较的结果。假定复用器34-n

参考图5,示出了用于确定在非二进制纠错码解码器中实现的基本校验节点处理器中的基本校验节点分量的排序方法。该方法包括根据从变量节点消息导出的第一消息和第二消息计算辅助分量,并在n

因此,在步骤501处,可以接收从三个或更多个变量节点消息

根据一些实施例,第一消息X可以包括由X[x]表示的第一给定数量n

根据一些实施例,第一消息和第二消息可以包括相同数量的分量,据此,第一给定数量和第二给定数量可以相等,即,n

在其他实施例中,第一消息和第二消息包括不同数量的分量,据此,第一给定数量和第二给定数量可以不同,即,n

在步骤503处,可以根据第一消息X和第二消息Y来确定由

-由

-由B

根据一些实施例,步骤503可以包括:

-通过在非二进制纠错码的构造的代数结构上应用第一加法运算,来确定每个辅助分量B

-通过在预定义的代数结构上应用第二加法运算,来确定与每个辅助符号

根据一些实施例,在包括实数域、整数域和自然数域的组中选择对其执行第二加法运算的预定义的代数结构。

根据一些实施例,可以取决于在包括以下各项的组中选择的至少一个参数来确定辅助分量的数量n

确定出的辅助分量可以被分组到由

可以根据辅助符号的递减的可靠性将辅助分量分组到路径中,使得:

-根据满足

-根据辅助符号的递减的可靠性,对每条路径的包括最可靠的辅助符号的辅助分量进行排序,使得

在步骤507处,每条路径Path

可以执行步骤509至525,以通过执行n

根据一些实施例,每个基本校验节点分量E[e]可以包括符号

在一个实施例中,迭代可以对应于时钟周期。

迭代排序的每次迭代可以提供n

-包括最可靠的候选符号的候选基本校验节点分量是候选基本校验节点分量

-第m个候选基本校验节点分量

取决于比较结果,可以在每次迭代中决定并执行控制动作,以通过更新在先前迭代中预先确定出的候选分量来确定候选基本校验节点分量。

控制动作可以是例如保持动作、插入动作或移位动作。

在步骤509处,可以根据it=1来执行迭代排序过程的多个迭代的初始化。在其中在时钟周期期间执行迭代的实施例中,排序过程的迭代次数可以对应于排序处理时间段,即,就时钟周期数而言的延迟。

在步骤509处,可以在迭代排序过程的第一迭代(it=1)时执行初始化动作。初始化动作可以包括将候选基本校验节点分量

在步骤511处,可以递增排序过程的迭代次数。

在步骤513处,可以通过检查排序过程的迭代次数it是否达到n

如果在步骤513处确定it=n

如果在步骤513处确定it≠n

在步骤515处,可以确定候选FIFO存储器,该候选FIFO存储器被指派有FIFO编号索引,该FIFO编号索引

在步骤519处,可以从在步骤515处确定出的候选FIFO存储器中提取辅助分量,该辅助分量是候选FIFO存储器中紧接候选基本校验节点分量

在步骤521处,可以执行在接收到的辅助分量

在步骤523处,可以通过取决于在步骤521处执行的比较来执行控制动作,从而确定n

在步骤525处,可以选择并递送包括最可靠的候选符号的更新后的候选基本校验节点分量

图6是示出取决于在接收到的辅助分量中包括的辅助可靠性度量与候选基本校验节点分量

在步骤601处,可以接收候选基本校验节点分量

可以在步骤605、609和611处执行控制动作,以取决于可靠性度量比较的结果来并行地确定n

-在步骤601处可以通过以下操作来执行保持动作:在步骤603处确定在第it次迭代中接收到的辅助分量

-在步骤609处可以通过以下操作来执行插入动作:在步骤603处确定辅助分量中包括的辅助符号

-在步骤611处可以通过以下操作来执行移位动作:在步骤607处确定接收到的辅助分量中包括的辅助符号不如在先前迭代中确定出的候选基本校验节点分量

应当注意,考虑到恒定候选分量

本文描述的方法和设备可以通过各种方式来实现。例如,可以以硬件、软件或其组合来实现这些技术。对于硬件实现方式,可以例如根据仅硬件配置(例如,在具有对应存储器的一个或多个FPGA、ASIC或VLSI集成电路中)或根据使用VLSI和DSP两者的配置来实现迭代解码器123的处理元件。

虽然已经通过对各种示例的描述示出了本公开的实施例,并且虽然已经相当详细地描述了这些实施例,但是申请人的意图不是将所附权利要求书的范围限制或以任何方式局限于此类细节。

特别地,虽然已经参考EMS算法的特定实现方式对本公开的一些实施例进行了描述,但是应当注意,本公开还可以应用于诸如最小-最大算法之类的其他迭代解码算法。

此外,尽管已经参考在Galois域上构造的纠错码描述了本公开的一些实施例,但是本领域技术人员将容易地理解,所提出的实施例也可以应用于在非交换组上构造的任何非二进制LDPC码和任何非二进制图纠错码,例如,多项式码(例如,循环码)。

此外,即使本公开在通信系统的应用中具有一些优点,也应当注意,本公开不限于这样的通信设备,并且可以被集成在诸如数据存储设备之类的许多设备中。

可以通过供应给任何类型的计算机的处理器以产生具有执行指令以实现本文指定的功能/动作处理器的机器的计算机程序指令来实现本文描述的方法。这些计算机程序指令还可以存储在计算机可读介质中,该计算机可读介质可以指导计算机以特定方式起作用。为此,可以将计算机程序指令加载到计算机上以引起一系列操作步骤的执行,并由此产生计算机实现的过程,使得所执行的指令提供用于实现本文指定的功能的过程。

- 用于针对非二进制码的消息传递解码的基本校验节点处理的排序设备和方法

- 非二进制码的消息传递解码的可变节点处理方法和设备