一种多核CPU运行模式的平台架构设计方法

文献发布时间:2023-06-19 10:08:35

技术领域

本发明属于电力系统二次设备的嵌入式技术领域,涉及一种多核CPU运行模式的平台架构设计方法。

背景技术

在电力二次设备中,随着嵌入式芯片技术的更新升级,多核CPU的使用越来越普遍。目前多核CPU的常用运行模式包括AMP(Asymmetric Multi-Processing非对称多处理)、SMP(Symmetric Multi-Processing对称多处理)。AMP模式下各个内核独立运行各自的程序,多核之间的耦合度较低,既可以单核裸跑获得极佳的实时性及可靠性,也可以单核运行操作系统完成非实时任务处理。SMP模式可以在一个操作系统下统一调度多个内核,将单系统的处理能力提升多倍,适合功能复杂的非实时应用。

电力二次设备包含继电保护、安全自动装置、测控、网关机、PMU、时钟等设备,有的产品对可靠性和实时性要求高,适合选用AMP裸跑方案;有的产品不要求实时性,但是功能较为复杂、对CPU处理能力要求较高,适合选用SMP操作系统方案;因此,很难使用传统的AMP或SMP模式中的一种兼顾各类电力二次设备的需求,从而导致多核CPU平台底层框架的软件版本繁多,既增加了开发维护的工作量,也对系统可靠性造成了不利影响。

此外,传统AMP模式的主核通常运行操作系统,主核负责从核的启动和引导,是多核AMP系统的核心,操作系统的启动速度相对较慢,且代码庞大复杂难以实现完全的安全可控,一定程度上降低了AMP系统的可靠性。

发明内容

为了解决现有技术存在的问题,本发明的目的在于,提供了一种多核CPU运行模式的平台架构设计方法:增强混合型多核处理模式,亦称EHMP(Enhanced Hybrid Multi-processing)。解决了电力二次设备中多核处理器底层架构不统一,难以同时兼顾可靠性、实时性和CPU处理能力的问题。

本发明采用如下的技术方案:

一种多核CPU运行模式的平台架构设计方法,所述平台架构设计方法包括以下步骤:

步骤1,同构多核CPU首先启动主核,

其中,主核为同构多核CPU的core0;

步骤2,主核启动后即进入初始化阶段,在初始化阶段的预设时长内主核唤醒从核;

步骤3,主核唤醒从核之后,从核立即启动,从核以AMP方式运行,或以SMP方式运行;

步骤4,主核运行平台化的通用底层软件,用于负责外设通信接口的扩展以及监视从核运行状态;

其中,CPU为中央处理器,AMP为非对称多处理,SMP为对称多处理。

在步骤1中,CPU上电后首先确认主核和从核,首先启动的单个核即主核,其余核为从核。

所述从核的启动顺序由主核进行控制。

在步骤2中,主核启动完成后根据多核CPU运行模式配置依次唤醒从核,未使用的从核将不被唤醒,并始终处于休眠状态以降低功耗。

在步骤2中,所述预设时长为500ms。

在步骤3中,从核启动完成后,根据多核CPU运行模式配置,从核可以任意组合部署运行模式,所有从核各自单核运行裸跑程序/操作系统,即从核AMP运行模式;所有从核共同运行一个操作系统,即从核SMP运行模式;部分从核运行一个操作系统,其余单核运行裸跑程序/操作系统,所有从核处于SMP/AMP混合运行模式。

在四核CPU中从核数目为1~3。

在步骤3中,如果存在多个以SMP模式运行操作系统的场景,操作系统不限,能支持在同构多核CPU上运行即可;操作系统支持应用程序绑定特定核。

在步骤4中,主核在唤醒并启动从核之后,将继续独立运行裸跑程序实现底层通用功能,主核实现外设通信接口的扩展,并采用核间实时侦测策略监视每个从核的运行状态,对运行异常的从核进行自恢复处理。

在步骤4中,同构多核CPU系统的主核以裸跑形式运行平台化的通用底层软件。

与现有技术相比,本发明的有益效果在于:

本发明提出了EHMP(Enhanced Hybrid Multi-processing)多核同构CPU平台架构设计方案,遵循裸跑方式实现高可靠及高实时性功能、操作系统方式实现非强实时性功能的原则,统一了各类电力二次设备中多核处理器的底层架构,主核采用裸跑方式实现底层通用功能,保证了多核CPU底层基础架构的稳定安全可靠,具有极佳的实时性及灵活扩展能力,从核可以根据应用功能需求自由选择AMP或SMP组合配置,有效兼顾了产品的可靠性、实时性、处理能力。本发明可适用于继电保护、安全自动装置、测控、网关机、PMU、时钟等各类电力二次设备,大幅度提升了多核CPU运行的安全性及系统可靠性。

附图说明

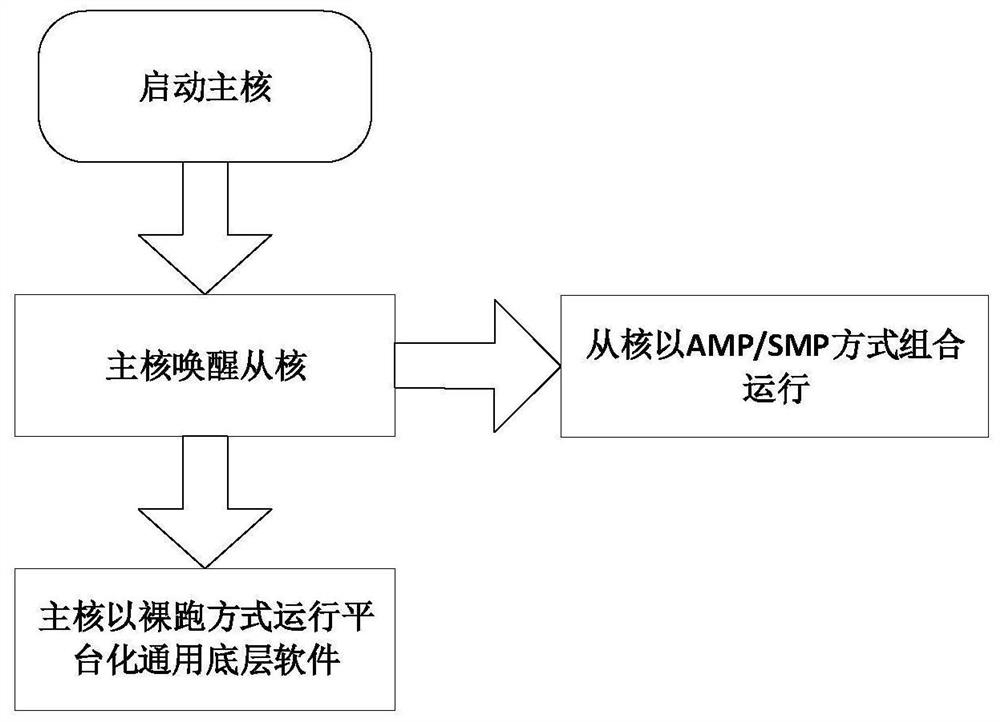

图1为多核CPU运行模式方法示意图;

图2为多核CPU运行模式中从核SMP运行模式状态示意图;

图3为多核CPU运行模式中从核混合运行模式状态示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明的技术方案进行清楚、完整地描述。本申请所描述的实施例仅仅是本发明一部分的实施例,而不是全部实施例。基于本发明精神,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明的保护范围。

以下实施例均以全志T3 CPU作为多核CPU样本,全志T3为四核CPU。

实施例1

图1为多核CPU运行模式方法示意图,如图1所述,多核增强混合型处理模式的实现步骤包括:

步骤1,多核CPU上电后首先启动主核。

在本步骤中,首先启动core0,即把core0作为为主核,其余三个核作为从核。

步骤2,主核唤醒从核。

在本步骤中,主核core0要依次唤醒core1、core2、core3三个从核。

步骤3,从核进行运行模式的自由组合。

在本步骤中,三个从核运行同一个操作系统及应用程序。

步骤4,主核运行裸跑业务。

在本步骤中,core0运行自身裸跑业务程序,对于实时性和可靠性高的任务均在core0的裸跑程序中运行。

此时各个核心及操作系统和应用的运行状态如图2所示。在当前实施例中,对于电力系统嵌入式装置来说,高可靠性和强实时性的任务放在core0的裸跑程序中;对实时性要求不严格的高级应用功能部署在从核以SMP模式共同运行的操作系统中。

图3为多核CPU运行模式中从核混合运行模式状态示意图。

实施例2

图1为多核CPU增强混合型多核处理模式的方法示意图,如图1所述,所述多核增强型对称多处理的方法的步骤包括:

步骤1,多核CPU上电后首先启动主核。

在本步骤中,首先启动core0,即把core0作为主核,其余三个核作为从核。

步骤2,主核唤醒从核。

在本步骤中,主核core0要依次唤醒core1、core2、core3三个从核。

步骤3,从核进行运行模式的自由组合。

在本步骤中,三个从核中的core1裸跑运行,core2休眠不运行程序,core3运行操作系统,core1和core3各自独立运行应用程序。

步骤4,主核运行裸跑业务。

在本步骤中,core0、core1运行裸跑程序,高实时性和高可靠性的任务均在裸跑核中运行,对实时性要求一般的复杂应用功能在core3的操作系统上运行。

上面对本专利的较佳实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域的普通技术人员所具备的知识范围内,还可以在不脱离本专利宗旨的前提下做出各种变化。

最后应当说明的是:以上实施例仅用以说明本发明的技术方案而非对其限制,尽管参照上述实施例对本发明进行了详细的说明,所属领域的普通技术人员应当理解:依然可以对本发明的具体实施方式进行修改或者等同替换,而未脱离本发明精神和范围的任何修改或者等同替换,其均应涵盖在本发明的权利要求保护范围之内。

- 一种多核CPU运行模式的平台架构设计方法

- 一种级联多核CPU间VCPU均衡分担控制方法及其装置