显示装置和电子设备

文献发布时间:2023-06-19 10:40:10

技术领域

本技术涉及一种包括发光元件和电子设备的显示装置。

背景技术

使用有机电致发光二极管(有机发光二极管,以下有时称为OLED)的有机电致发光显示装置(以下称为有机EL显示装置)是发光元件,由于自发光而具有低功耗的特性,并且已经被开发用于实际用途。

特别地,已经提出通过硅半导体精细工艺在同一单晶硅基板上形成有机EL显示装置的像素电路及其外围电路,并将该有机EL显示装置应用于例如小显示器的电子设备的取景器(例如,参见专利文献1)。

通常,在构成电路的晶体管中,在扩散层中形成通过使硅基板和金属反应以减小接触金属和硅基板之间的接触电阻而形成的硅化物。

引文列表

专利文献

专利文献1:JP-A-2013-44890

发明内容

技术问题

当形成上述硅化物以构成有机EL显示装置时,未反应的金属可能扩散到硅基板中而成为不必要的泄漏源。如果这种未反应的金属成为泄漏源并且不必要的泄漏电流流入OLED,则可能发生诸如OLED的不必要的发光的辉点缺陷。

鉴于上述情况,本技术的目的是提供一种显示装置和电子设备,其中抑制了辉点缺陷的发生。

问题的解决方案

为了实现上述目的,根据本技术的实施例的显示装置包括发光部分和驱动电路。

该驱动电路包括驱动发光部分并包括第一扩散层和第一接触电极的晶体管,第一扩散层不包括在硅区域中形成的硅化物,第一接触电极电连接至第一扩散层。

根据这样的配置,在硅化物形成步骤时未形成硅化物的扩散层上未形成金属层,并因此抑制了在硅化物形成步骤时产生的未反应金属被扩散到其中没有形成硅化物的扩散层中。这抑制了由于未反应的金属引起的由于不必要的泄漏电流流入发光部分而导致的辉点缺陷的发生。

驱动电路可以包括晶体管,该晶体管包括第二扩散层和第二接触电极,第二扩散层包括在硅区域中形成的硅化物,第二接触电极电连接到第二扩散层。

第一扩散层可以具有比第二扩散层更低的扩散层表面的杂质浓度。

第一扩散层可以包括比第二扩散层更深的区域。

驱动电路可以包括晶体管,该晶体管包括经由第一接触电极连接至发光部分的第一扩散层。

包括第一扩散层的晶体管可以是作为电流限制元件工作的驱动晶体管。

驱动电路可以包括图像信号写入晶体管,图像信号写入晶体管包括第一扩散层并且导通或截止流过发光部分的驱动电流。

驱动电路还可以包括覆盖第一扩散层的绝缘膜。

发光部分可以是有机电致发光二极管。

为了实现上述目的,根据本技术的实施例的电子设备包括显示装置。

该显示装置包括发光部分和驱动电路,该驱动电路包括驱动发光部分并包括第一扩散层和第一接触电极的晶体管,第一扩散层不包括在硅区域中形成的硅化物,第一接触电极电连接至第一扩散层。

附图说明

[图1]是示出根据本公开的实施例的显示装置的示意性配置的图。

[图2]是上述显示装置的等效电路图。

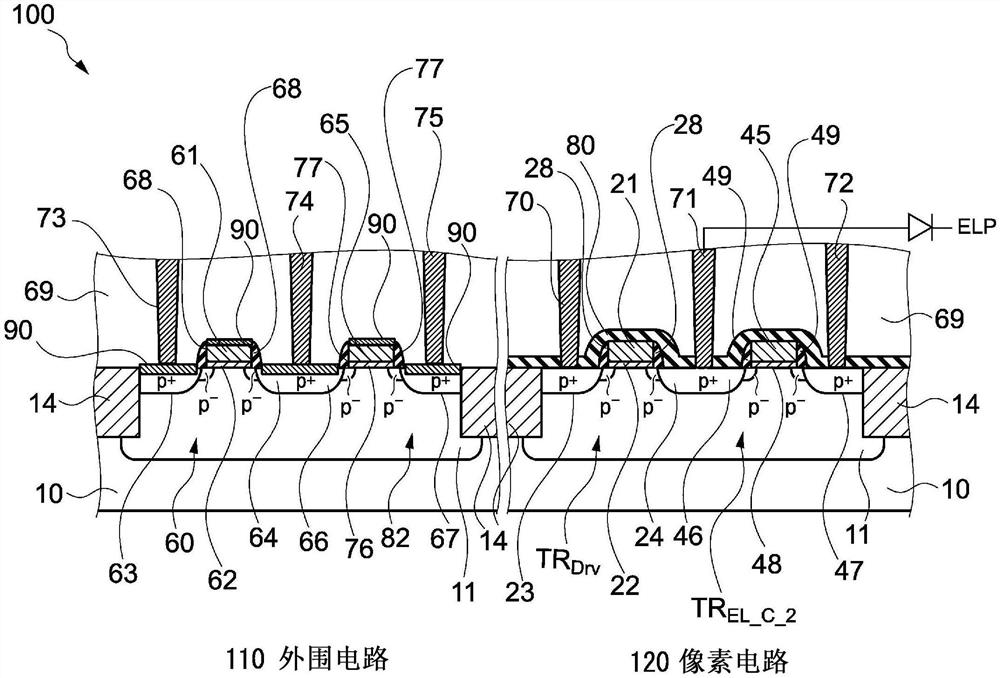

[图3]是第一实施例的显示装置的像素电路的主要部分和外围电路的截面示意图。

[图4]是第二实施例的显示装置的像素电路的主要部分和外围电路的截面示意图。

[图5]是示出第二实施例的显示装置的电路的制造过程的一部分的制造过程图。

[图6]是用于描述在扩散层中形成硅化物时的构造与不形成硅化物时的构造之间的差异的图。

[图7]是示出第三实施例的显示装置的电路的制造过程的一部分的制造过程图。

[图8]是示出第四实施例的显示装置的电路的制造过程的一部分的制造过程图。

[图9]是示出第四实施例的显示装置的电路的另一制造过程的一部分的制造过程图。

[图10]是示出作为电子设备的电视装置的外观的图。

[图11]是示出作为电子设备的数码相机的外观的图。

[图12]是示出作为电子设备的笔记本个人计算机的外观的图。

[图13]是示出作为电子设备的摄像机的外观的图。

[图14]是示出作为电子设备的移动电话的外观的图。

[图15]是示出作为电子设备的头戴式显示器的外观的图。

具体实施方式

在下文中,根据本公开的实施例的显示装置,具体地,包括有机电致发光(EL)二极管(在下文中,称为OLED)作为发光元件的有机电致发光(EL)显示装置将参考附图进行描述。在下文中,有机EL显示装置可以简称为显示装置。

[有机EL显示装置的配置]

图1示出了显示装置100的示意性配置。

图2是在显示装置中包括驱动电路的发光元件的等效电路图。图2是像素电路是包括四个晶体管TRDrv,TRSig,TREl_c和TREl_c_2以及两个电容部分C1和C2的驱动电路(4Tr/2C驱动电路)的示例。

如图1所示,显示装置100包括外围电路110和像素电路120,它们是驱动电路,并且同时形成在包括硅区域的单晶硅半导体基板(以下有时称为硅半导体基板)10上。硅半导体基板10包括被配置为使得柔性布线板可连接至其的输入和输出端子116。

像素电路120对应于显示装置100的图像显示区域。显示区域包括在整个表面上沿行方向和列方向二维地布置的多个像素。在显示区域中,通过驱动每个像素来显示基于从外围电路输入的视频信号的图像。

外围电路110包括水平驱动电路(V驱动器)111和112,垂直驱动电路(H驱动器)113,伽马电压发生器电路(Gam)114和时序控制器(Tcon)115。

水平驱动电路111和112对应于稍后将描述的扫描电路103和发光控制晶体管控制电路104。

垂直驱动电路113对应于稍后描述的图像信号输出电路105。

像素电路120和外围电路110均包括晶体管。

如图2所示,显示装置100包括第一电流供应单元101和第二电流供应单元102,以及扫描电路103,发光控制晶体管控制电路104和图像信号输出电路105作为外围电路。

此外,显示装置100在显示区域中包括发光元件1,电流供应线(第一电流供应线CSL1),第二电流供应线CSL2,扫描线SCL,第一发射控制线CLEl_c_1,第二发射控制线CLEl_c_2和数据线DTL。

多条第一电流供应线CSL1被布置并连接到第一电流供应单元101。

从第一电流供应单元101向第一电流供应线CSL1供应固定电压Vcc。

多条第二电流供应线CSL2连接到第二电流供应单元102,并被布置成在与第一电流供应线CSL1的布置方向正交的方向上延伸。

从第二电流供应单元102向第二电流供应线CSL2供应固定电压Vcc。

多条扫描线SCL连接到扫描电路103,并且被布置成在与第一电流供应线CSL1的布置方向平行的方向上延伸。

从扫描电路103向扫描线SCL依次提供扫描信号。

多条第一发射控制线CLEl_c_1连接至发光控制晶体管控制电路104,并且被布置为在与第一电流供应线CSL1的布置方向平行的方向上延伸。

从发光控制晶体管控制电路104向第一发射控制线CLEl_c_1依次提供发光控制信号。

第二发射控制线CLEl_c_2连接至发光控制晶体管控制电路104。从发光控制晶体管控制电路104向第二发射控制线CLEl_c_2依次提供发光控制信号。

多条数据线DTL连接到图像信号输出电路105,并被布置成在与第一电流供应线CSL1的布置方向正交的方向上延伸。

图像信号(驱动信号或亮度信号)VSig和预定基准电位Vofs被切换并从图像信号输出电路105供应到数据线DTL。

发光元件1包括发光部分(具体地,有机EL发光部分)ELP和用于驱动发光部分ELP的像素电路120。

用于显示图像的显示区域包括以二维矩阵布置的发光元件1。发光元件1构成像素。

显示装置100可以在显示区域中具有用于单色显示的配置,或者可以在其中具有用于彩色显示的配置。在彩色显示配置的情况下,一个像素包括例如三个子像素(发射红光的红色发光子像素,发射绿光的绿色发光子像素和发射蓝光的蓝色发光子像素)。

发光部分ELP经由层间绝缘层形成在构成像素电路120的多个晶体管之上。

发光部分ELP是电流驱动的光学元件,其发光亮度根据流过发光部分ELP的电流而变化。在该实施例中,发光部分ELP由OLED构成。发光部分ELP具有包括阳极电极51,有机材料层,阴极电极53等的公知结构。有机材料层具有其中堆叠例如空穴传输层、发光层和电子传输层的结构。

用于驱动发光部分ELP的像素电路120包括驱动晶体管TRDrv,图像信号写入晶体管TRSig,第一发光控制晶体管TREl_c_1,第二发光控制晶体管TREl_c_2,第一电容部分C1,以及第二电容部分C2。

阳极电极51连接到驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46。

阴极电极53连接到地线,并且预定的阴极电压Vcath被供应给地线。注意,在图2中,附图标记CEL表示发光部分ELP的寄生电容。

在该实施例中,驱动晶体管TRDrv,图像信号写入晶体管TRSig,第一发光控制晶体管TREl_c_1和第二发光控制晶体管TREl_c_2均由p型沟道MOSFET制成并且形成在形成于p型硅半导体基板10中的n型阱中。

驱动晶体管TRDrv基于保持在电容部分C1中的图像信号(驱动信号或亮度信号)VSig来驱动发光部分ELP。驱动晶体管TRDrv用作电流限制元件。

驱动晶体管TRDrv包括栅极电极21、一个源极/漏极区域23和另一源极/漏极区域24。

在驱动晶体管TRDrv中,一个源极/漏极区域23经由形成在稍后将描述的层间绝缘层中形成的接触电极70连接到第一电容部分C1的一个电极41,并进一步连接到第一发光控制晶体管TREl_c_1的另一源极/漏极区域37。

一个源极/漏极区域23连接到第一电容部分C1的一个电极41,并且构成第二节点ND2。

在本实施例中,当发光部分ELP发光时,一个源极/漏极区域23具体地用作源极区域。

另一源极/漏极区域24经由形成在稍后将描述的层间绝缘层中形成的另一接触电极71和接触焊盘连接到发光部分(有机EL发光部分)ELP的阳极电极51。

在实施例中,当发光部分ELP发光时,另一源极/漏极区域24具体地用作漏极区域。

栅极电极21经由形成在层间绝缘层中的接触焊盘和形成在层间绝缘层中的又一接触电极连接到第一电容部分C1的另一电极42,并构成第一节点ND1。栅极电极21还连接到图像信号写入晶体管TRSig的另一源极/漏极区域34。

图像信号写入晶体管TRSig使电容部分C1保持图像信号VSig。

图像信号写入晶体管TRSig包括栅极电极31、一个源极/漏极区域33和另一源极/漏极区域34。

在图像信号写入晶体管TRSig中,一个源极/漏极区域33经由形成在层间绝缘层中的又一接触电极、接触焊盘和数据线DTL连接到图像信号输出电路105。

在实施例中,当写入图像信号时,一个源极/漏极区域33具体地用作源极区域。

栅极电极31经由形成在层间绝缘层中的又一接触电极、接触焊盘和扫描线SCL连接到操作电路103。

另一源极/漏极区域34经由形成在层间绝缘层中的又一接触电极连接到驱动晶体管TRDrv的栅极电极21和第一电容部分C1的另一端42。

在该实施例中,当写入图像信号时,另一源极/漏极区域34具体地用作漏极区域。

在显示装置100中,操作信号通过来自扫描电路103的图像信号写入晶体管TRSig的栅极电极31被供应给每个子像素,并且图像信号通过来自图像信号输出电路105的图像信号写入晶体管TRSig被保持在电容部分C1中。驱动晶体管TRDrv被控制为响应于保持在电容部分C1中的信号而导通或截止。因此,驱动电流流入发光部分ELP,空穴和电子在发光层中重新结合,并且引起发射。

第一发光控制晶体管TREl_c_1包括栅极电极35、一个源极/漏极区域36和另一源极/漏极区域37。

栅极电极35经由形成在层间绝缘层中的又一接触电极连接到第一发射控制线CLEl_c_1。

一个源极/漏极区域36经由形成在层间绝缘层中的又一接触电极连接到电流供应线CSL1。

另一源极/漏极区域37经由形成在层间绝缘层中的又一接触电极连接至驱动晶体管TRDrv的一个源极/漏极区域23和第一电容部分C1的一端41。

第二发光控制晶体管TREl_c_2包括栅极电极45、一个源极/漏极区域46和另一源极/漏极区域47。

栅极电极45经由形成在层间绝缘层中的又一接触电极连接到第二发射控制线CLEl_c_2。

一个源极/漏极区域46经由形成在层间绝缘层中的又一接触电极连接到驱动晶体管TRDrv的另一源极/漏极区域24。

另一源极/漏极区域47具有电势VSS。

第一电容部分C1包括一个电极(一端)41、另一电极(另一端)42以及夹在电极41和42之间的介电层(绝缘层)。

第一电容部分C1的一端41经由第二电容部分C2连接到第二电流供应线CSL2,并且连接到驱动晶体管TRDrv的一个源极/漏极区域23和第一发光控制晶体管TREl_c_1的另一源极/漏极区域37。

第一电容部分C1的另一端42连接到驱动晶体管TRDrv的栅极电极21。

第二电容部分C2包括一个电极(一端)、另一电极(另一端)以及夹在这些电极之间的介电层(绝缘层)。

第二电容部分C2的一端连接到第二电流供应线CSL2。

第二电容部分C2的另一端连接至第一电容部分C1等的一端41。

上述每个源极/漏极区域包括形成在包括硅区域的硅半导体基板10上的高浓度p型扩散层和低浓度p型扩散层。在后述的图3和图4中,将具有相对较低杂质浓度的扩散层表示为p-,且将具有较高杂质浓度的扩散层表示为p+。

上述接触电极是形成在层间绝缘层中并且将穿过层间绝缘层布置的一对导电层彼此电连接的导电层。穿过层间绝缘层布置的导电层包括扩散层,诸如信号线、扫描线、电流供应线和引线的布线,诸如栅极电极的电极、形成电容部分的电极以及形成发光部分的电极等。

这里,通常,为了减小接触电阻,在接触电极与形成在硅半导体基板10上的扩散层之间的边界处设置硅化物。

在本技术中,在形成在硅半导体基板10上的像素电路120中,构成多个晶体管的一部分的全部或一部分扩散层具有不形成硅化物的结构。

具体地,根据后述的第一实施例的显示装置具有在构成像素电路120的多个晶体管的全部扩散层中未形成硅化物的结构。稍后将参考图3描述第一实施例的细节。

根据后述的第二实施例的显示装置具有在构成像素电路120的多个晶体管的一部分扩散层中未形成硅化物的结构。稍后将参考图4描述第二实施例的细节。

注意,在第一实施例和第二实施例中,构成形成外围电路110的晶体管的扩散层具有其中形成硅化物以便减小与接触电极的接触电阻的配置。

图3和图4分别示出在右侧构成像素电路120的一部分的驱动晶体管TRDrv和第二发光控制晶体管TREl_c_2在扩散层中彼此电连接的情况的局部截面示意图,以及在左侧构成外围电路110的一部分的晶体管60和晶体管82在扩散层中彼此电连接的情况的局部截面示意图。在图3和图4中,附图标记14表示元件隔离区域。

如图3和图4所示,驱动晶体管TRDrv包括栅极电极21、栅极绝缘膜22、一个源极/漏极区域23、另一源极/漏极区域24和侧壁28。

一个源极/漏极区域23与接触电极70电连接。另一源极/漏极区域24与接触电极71电连接。

第二发光控制晶体管TREl_c_2包括栅极电极45、栅极绝缘膜48、一个源极/漏极区域46、另一源极/漏极区域47以及侧壁49。

一个源极/漏极区域46与接触电极71电连接。另一源极/漏极区域47与接触电极72电连接。

驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46彼此电连接,其连接是通过共享扩散层进行的。

如图3和图4所示,在外围电路110中,晶体管80包括栅极电极61、栅极绝缘膜62、一个源极/漏极区域63、另一源极/漏极区域64和侧壁68。

一个源极/漏极区域63与接触电极73电连接。另一源极/漏极区域64与接触电极74电连接。

晶体管82包括栅极电极65、栅极绝缘膜76、一个源极/漏极区域66、另一源极/漏极区域67和侧壁77。

一个源极/漏极区域66与接触电极74电连接。另一源极/漏极区域67与接触电极75电连接。

晶体管60的另一源极/漏极区域64和晶体管82的一个源极/漏极区域66彼此电连接,其连接是通过共享扩散层进行的。

<第一实施例>

(显示装置的截面图)

如图3所示,在显示装置100中,像素电路120(外围电路110)包括形成在硅半导体基板10的n型扩散层(n阱)11中的源极/漏极区域(扩散层包括高浓度p型扩散层和低浓度p型扩散层)23、24、46和47(63、64、66和67)。

在像素电路120中,栅极电极21(45)经由栅极绝缘膜22(48)形成在硅半导体基板10上。侧壁28(49)形成在栅极电极21(45)和栅极绝缘膜22(48)的侧壁上。

此外,在包括栅极绝缘膜22(48)、栅极电极21(45)和侧壁28(49)的硅半导体基板10的整个表面上形成绝缘膜80和层间绝缘层69。接触电极70、71和72形成在绝缘膜80和层间绝缘层69中。

接触电极70电连接驱动晶体管TRDrv的一个源极/漏极区域23和第一发光控制晶体管TREl_c_1(未示出)的另一源极/漏极区域37。

接触电极71将驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46连接至发光部分ELP(未示出),更具体地,连接到发光部分ELP的阳极电极51。

接触电极72将第二发光控制晶体管TREl_c_2的另一源极/漏极区域47和连接电源VSS(未示出)的布线电连接。

栅极电极21可以由例如多晶硅形成。

绝缘膜80可以由氧化膜、氮化膜或它们的堆叠膜形成。

绝缘膜80被形成为至少覆盖没有形成硅化物的区域中的扩散层。换句话说,绝缘膜80形成在硅化物非形成区域中。

在外围电路110中,栅极电极61(65)、一个源极/漏极区域63(66)和另一源极/漏极区域64(67)中的每一个通过在晶体管60(80)上形成的层间绝缘层69中形成的接触电极73和74(74和75)等电连接至布线(未示出)。

在外围电路110中,栅极电极61(65)经由栅极绝缘膜62(76)形成在硅半导体基板10上。侧壁68(77)形成在栅极电极61(65)和栅极绝缘膜62(76)的侧壁上。

层间绝缘层69形成在包括栅极绝缘膜62(76),栅极电极61(65)和侧壁68(77)的硅半导体基板10的整个表面上。接触电极73、74和75形成在层间绝缘层69中。

硅化物90形成在作为扩散层的一个源极/漏极区域63和66、另一源极/漏极区域64和67以及栅极电极61和65的每个表面上。即,硅化物90形成在一个源极/漏极区域63和66以及另一源极/漏极区域64和67的每个表面上,它们是接触电极73、74和75电连接到的扩散层。硅化物90还形成在栅极电极61的与另一接触电极(未示出)电连接的表面上。

如上所述,在本实施例中,形成在硅区域中并构成像素电路120的多个晶体管的扩散层具有不形成硅化物的构造。即,显示装置100具有在像素电路120中不形成硅化物而在外围电路110中形成硅化物的结构。

在这个实施例中,驱动晶体管TRDrv、图像信号写入晶体管TRSig、第一发光控制晶体管TREL_c_1和第二发光控制晶体管TREL_c_2的源极/漏极区域23、24、33、34、36、37、46和47各自对应于第一扩散层,其是其中未形成硅化物的扩散层。然后,电连接到各个第一扩散层的接触电极(其在图3中由附图标记70、71和72表示的配置)分别对应于第一接触电极。

形成在外围电路120中的晶体管60和82的源极/漏极区域63、64、66和67分别对应于第二扩散层,其是其中形成有硅化物的扩散层。然后,电连接到各个第二扩散层的接触电极(其在图4中由附图标记73、74和75表示的配置)分别对应于第二接触电极。

这里,通过在扩散层上形成金属层,且然后进行热处理以使硅原子与金属层的金属原子反应来形成硅化物。硅化物形成在扩散层的表面上。随后,去除未与硅原子反应的金属层,并使硅化物退火以稳定硅化物。

在本实施例中,在形成有像素电路120的显示区域中,在设置有绝缘膜80的状态下进行硅化物形成工艺。因此,用于形成硅化物的金属层不直接形成在被设置在硅化物非形成区域的区域中的绝缘膜80覆盖的扩散层上。因此,抑制了金属层的未反应的金属扩散到硅半导体基板10中。

这抑制了由于未反应的金属扩散到硅半导体基板10中而导致的结电流的突然增加的发生,抑制不必要的漏电流流入发光部分ELP以不必要地从OLED发光,并且抑制辉点缺陷的产生。另外,可以改善黑色亮度。

以这种方式,可以获得具有高显示质量的显示装置,其中可以抑制辉点缺陷。

注意,在本技术中,在扩散层中未形成硅化物的状态是指故意防止硅化的状态。因此,例如,排除了除了用于形成硅化物的金属以外的金属意外地混合的状态。

<第二实施例>

(发光元件的主截面图)

在下文中,将参照图4描述第二实施例。与上述相似的配置由相似的附图标记表示,并且可以省略其描述。

由于外围电路110与图3所示的类似,因此将省略其描述。

在该实施例中,驱动晶体管TRDrv的另一源极/漏极区域24和发光控制晶体管TREl_c_2的一个源极/漏极区域46分别对应于第一扩散层,其是其中未形成硅化物的扩散层,并且接触电极71电连接到另一源极/漏极区域24并且一个源极/漏极区域46对应于第一接触电极。

驱动晶体管TRDrv的一个源极/漏极区域23、第二发光控制晶体管TREl_c_2的另一源极/漏极区域47以及图像信号写入晶体管TRSig的源极/漏极区域33、34、36、37、63、64、66和67,第一发光控制晶体管TREl_c_1以及形成在外围电路120中的晶体管60和82分别对应于第二扩散层,其是其中形成有硅化物的扩散层。然后,电连接到各个第二扩散层的接触电极(其在图4中由附图标记70、72至75表示的配置)分别对应于第二接触电极。

如图4所示,像素电路120(外围电路110)包括形成在硅半导体基板10的n型扩散层11中的源极/漏极区域(扩散层包括高浓度p型扩散层和低浓度p型扩散层)23、24、46和47(63、64、66和67)。

在像素电路120中,栅极电极21(45)经由栅极绝缘膜22(48)形成在硅半导体基板10上。侧壁28(49)形成在栅极电极21(45)和栅极绝缘膜22(48)的侧壁上。

绝缘膜80形成为覆盖另一源极/漏极区域24、一个源极/漏极区域46,一部分栅极电极21和45以及一部分侧壁28和49。

硅化物90形成在栅极电极21(45)的表面中未形成绝缘膜80的区域中。

硅化物90形成在一个源极/漏极区域23和另一源极/漏极区域47的每个表面上。

在另一源极/漏极区域24和一个源极/漏极区域46的每个表面上未形成硅化物90。

层间绝缘层69形成在包括栅极绝缘膜22和48、栅极电极21和45、侧壁28和49以及绝缘膜80的硅半导体基板10的整个表面上。接触电极70和72形成在层间绝缘层69中,并且接触电极71形成在绝缘膜80和层间绝缘层69中。

接触电极70电连接驱动晶体管TRDrv的一个源极/漏极区域23和第一发光控制晶体管TREl_c_1(未示出)的另一源极/漏极区域37。

接触电极71将驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46电连接到发光部分ELP的阳极电极51(未示出)。

接触电极72连接到第二发光控制晶体管TREl_c_2的另一源极/漏极区域47和连接电源VSS(未示出)的布线。

在本实施例中,提供以下配置:在形成在硅区域中并构成像素电路120的多个晶体管的扩散层中,硅化物不形成在驱动晶体管TRDrv的另一源极/漏极区域(扩散层)24和电连接到发光部分ELP的阳极电极51的第二发光控制晶体管TREl_c_2的一个源极/漏极区域46中,并且硅化物形成在另一扩散层中。

以这种方式,当像素电路120具有其中部分地设置绝缘膜80并且在一些扩散层中未形成硅化物的配置时,与在所有扩散层中形成硅化物的情况相比,绝缘膜80抑制未反应的金属扩散到硅半导体基板10中。因此,抑制了由于不必要的泄漏电流流入发光部分ELP而引起的辉点缺陷的发生。

此外,在本实施例中,由于硅化物形成在除驱动晶体管TRDrv的另一源极/漏极区域(扩散层)24和像素电路120中的第二发光控制晶体管TREl_c_2的一个源极/漏极区域46之外的扩散层中,可以降低接触金属与源极/漏极区域之间的接触电阻。所以,可以在像素电路120中高速执行信号处理。

如上所述,在本实施例的显示装置中,抑制了由于不必要的泄漏电流流入发光部分ELP而导致的辉点缺陷的发生,并且使得高速信号处理成为可能。因此,可以获得显示质量高且显示特性优异的显示装置。

注意,本实施例提供了其中在驱动晶体管TRDrv的另一源极/漏极区域(扩散层)24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46中没有形成硅化物的配置,它们(TRDrv和TREl_c_2)电连接到发光部分ELP的阳极电极51,但是本技术不限于此。例如,可以提供在图像信号写入晶体管TRSig的扩散层中不形成硅化物的结构。另外,可以提供在驱动晶体管TRDrv的扩散层和图像信号写入晶体管TRSig的扩散层均未形成硅化物的配置。

(制造方法)

接下来,将参照图5描述根据第二实施例的显示装置100的制造方法。这里,将描述制造图4所示的驱动晶体管TRDrv和第二发光控制晶体管TREL_c_2的一部分的示例。注意,除了形成绝缘膜80的区域彼此不同之外,第一实施例的制造方法和第二实施例的制造方法基本相同。

图5是示出第二实施例的显示装置100的像素电路120的制造过程的一部分的制造过程图。

首先,如图5的(A)所示,在硅半导体基板10中形成元素间分离区14之后,进行杂质离子注入以形成n型扩散层11,然后沉积栅极绝缘膜22'。

接下来,通过化学气相沉积(CVD)方法将用作栅极电极的多晶硅(多晶硅)沉积在栅极绝缘膜22'上,以进一步形成与栅极电极相对应的抗蚀剂图案。使用抗蚀剂图案作为掩模蚀刻多晶硅和栅极绝缘膜22',以形成栅极电极21和45以及栅极绝缘膜22和48。

接下来,如图5的(B)所示,进行离子注入以形成浅结区23'和24'。

接下来,通过CVD方法在硅半导体基板10的整个表面上形成氧化硅膜,并且执行干法蚀刻以形成侧壁28和49。接下来,如图5的(C)所示,进行离子注入以形成一个源极/漏极区域23和46以及另一源极/漏极区域(扩散层)24和47。

接下来,在硅半导体基板10的整个表面上形成栅极绝缘膜80'。如图5的(D)所示,在栅极绝缘膜80'上形成与硅化物非形成区域相对应的抗蚀剂图案,并且栅极绝缘膜80'以抗蚀剂图案用作掩模,通过干法蚀刻等进行图案刻蚀以形成的绝缘膜80。在第二实施例中,绝缘膜80被形成为覆盖驱动晶体管TRDrv的另一源极/漏极区域(扩散层)24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域(扩散层)46的表面,并且不形成在其他扩散层上。

这里,在根据第一实施例的用于显示装置的制造方法中的绝缘膜80的形成过程中,绝缘膜80形成在要成为像素电路120的所有区域中,并且绝缘膜80不形成在外围电路110的区域中。

接下来,通过溅射将金属层沉积在硅半导体基板10的整个表面上并加热以形成硅化物90。注意,用于硅化物的金属的实例包括钴、镍和钛。

在该过程中,通过加热包括形成在其表面上的金属层的硅半导体基板10,金属层的硅原子和金属原子发生反应,并且硅和金属层彼此接触的部分改变为硅化物90。注意,即使金属层形成在绝缘膜80上然后被加热,绝缘膜80上的金属层仍然是金属。

接下来,去除未与硅原子反应的金属层。因此,硅化物90残留在其上未形成绝缘膜80的栅极电极21、一个源极/漏极区域23和另一源极/漏极区域47上。此外,使硅化物90退火以稳定硅化物90。随后,如图5的(E)所示,形成层间绝缘层69,并且形成接触电极70、71和72。

注意,图5示出了形成绝缘膜80以覆盖栅极电极21的一部分的示例,但是可以形成绝缘膜80以覆盖栅极电极21的全部,或者可以形成绝缘膜80以暴露出栅极电极21。在栅极电极21的未形成绝缘膜80的表面部分中形成硅化物。

在上述制造过程中,当形成侧壁28和49时,可以同时形成对应于硅化物非形成区域而设置的绝缘膜80。如上所述,在通过CVD方法形成氧化硅膜之后,通过干法蚀刻形成侧壁28和49。在干法蚀刻时,蚀刻氧化硅膜以使其也残留在与硅化物非形成区域相对应的部分中,并且绝缘膜80可以与侧壁28和49一起形成。

图6的(A)和(B)是驱动晶体管TRDrv和第二发光控制晶体管TREl_c_2的局部放大截面图。

图6的(A)对应于仅形成侧壁28和49的情况的视图。在这样的配置中,侧壁28和49限定了硅化物非形成区域。

如上所述,图6的(B)对应于同时形成绝缘膜和与硅化物非形成区域相对应的侧壁的情况的视图。在图6的(B)中,设置在包括侧壁的硅化物非形成区域中的绝缘膜由附图标记81表示。

在图6中,附图标记91表示用于形成接触电极时使用的接触蚀刻停止层的氮化膜。

如图6的(A)所示,侧壁28和49确定了硅化物90的形成区域,并且在扩散层的被侧壁28和49覆盖的区域中未形成硅化物。

沿栅极电极21的形状形成侧壁28(49),同时覆盖栅极电极21(45)的侧壁。侧壁28(49)的一端位于另一源极/漏极区域24(一个源极/漏极区域46)上,而侧壁28(49)的另一端位于栅极电极21(45)上。位于另一源极/漏极区域24(一个源极/漏极区域46)上的侧壁28(49)的一端形成阶梯(step)85(87)。

当在阶梯85(87)上形成接触电极71时,由于连接失败而导致打开失败。因此,为了在阶梯85(87)上不形成接触电极71,在设计上需要将栅极电极21(45)和接触电极71隔开一定距离86。

相反,在根据本技术的显示装置100中,如图6的(B)所示,由于在另一源极/漏极区域24和一个源极/漏极区域46中没有形成硅化物,因此,形成绝缘膜81以覆盖另一源极/漏极区域24和一个源极/漏极区域46的表面。

在图6的(B)所示的配置中,绝缘膜81的端部81a位于栅极电极21、45上,并且绝缘膜81的端部不位于另一源极/漏极区域24和一个源极/漏极区域46的表面上。如图6的(A)所示,阶梯85(87)不存在于另一源极/漏极区域24(一个源极/漏极区域46)的表面上。

因此,与设置阶梯85和87的情况相比,可以将栅极电极21、45和接触电极71布置在彼此靠近的位置,并且可以缩短在栅极电极21、45和接触电极71之间的距离86。

因此,改善了设计的自由度,例如晶体管的栅极电极、源极/漏极区域等的布置。

例如,可以在保持晶体管的布置面积的同时减小像素间距。此外,通过比较图6的(A)和(B)可以看出,在根据本技术的显示装置100中,可以增大栅极电极的长度,即,增大沟道长度。

这里,在简单地减小晶体管的尺寸的情况下,晶体管容易受到工艺变化的影响,并且晶体管的特性易于变化。

相对于此,在本实施例中,能够维持晶体管的配置面积,并因此,能够减少各晶体管的特性的偏差,且能够得到提高基板面的亮度均匀性的显示装置。此外,可以减小像素间距,并且因此可以获得高清晰度的显示装置。

此外,例如,当提高设计的自由度时,可以增加接触电极的数量,并且可以增加针对接触电极的打开失败的冗余度。

此外,例如,可以增加接触电极的布置的自由度,并因此改善了连接到接触电极的布线的迹线的自由度。

<第三实施例>

在通过上述图5所示的制造过程制造的显示装置中,当OLED用作发光部分时,在阳极电极51和硅半导体基板10之间施加诸如7V或更高的高反向偏置电压。当施加这样高的反向偏置电压时,向p-n结施加较大的反向电压会导致击穿现象(击穿)流过较大的结泄漏电流,并且在某些情况下无法获得所需的显示质量。这是因为在离子注入期间必须防止杂质离子通过栅极氧化膜从栅极电极渗透到沟道层,并且在形成浅结区的过程中,离子注入的高加速受到限制。

相反,在本实施例中,如图7所示,在形成栅极电极之前,在不形成硅化物且要施加高电压的扩散层上,以高注入加速度选择性地进行深离子注入,(在该实施例中,驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46将被电连接到发光部分ELP,以形成低浓度p区域)。

因此,如在图7的(E)中所示的显示装置100中,可以使另一源极/漏极区域24和一个源极/漏极区域46的p-n结的深度(扩散层的深度)(是要对其施加高压的扩散层,),大于一个源极/漏极区域23和另一源极/漏极区域47的p-n结的深度(扩散层的深度)。此外,尽管未示出,但是可以使另一源极/漏极区域24和一个源极/漏极区域46的p-n结的深度大于除驱动晶体管TRDrv和第二发光控制晶体管TREl_c_2之外的晶体管的扩散层中的p-n结的深度。

以这种方式,将要施加高压的扩散层设置在比其他扩散层更深的区域,因此可以减小电场。

在下文中,将参照图7描述根据本实施例的显示装置的制造方法。

图7是示出第三实施例的显示装置100的电路的制造过程的一部分的制造过程图。同样在图7中,将使用像素电路120中的驱动晶体管TRDrv和第二发光控制晶体管TREl_c_2的制造部分的示例给出描述。

与上述实施例中相似的配置由相似的附图标记表示,并且可以省略其描述。

图7是示出第三实施例的显示装置的像素电路的制造过程的一部分的制造过程图。

首先,在硅半导体基板10中形成元素间分离区域14之后,进行杂质的离子注入以形成n型扩散层11。随后,仅在成为另一源极/漏极区域24和一个源极/漏极区域46(扩散层)的区域中,以高的注入加速度深注入离子,它们将被电连接到阳极电极51并且将被施加高压,以形成深的低浓度p区域24'和46'。随后,如图7的(A)所示,形成栅极绝缘膜22'。

接下来,通过化学气相沉积(CVD)方法将用作栅极电极的多晶硅(多晶硅)形成在栅极绝缘膜22'上,以进一步形成与栅极电极相对应的抗蚀剂图案。随后,使用抗蚀剂图案作为掩模蚀刻多晶硅和栅极绝缘膜22',以形成栅极电极21和45以及栅极绝缘膜22和48。

接下来,形成抗蚀剂图案95,从而覆盖将成为驱动晶体管TRDrv的另一源极/漏极区域24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46的低浓度p区域24'和46',并暴露其他扩散层。

接下来,如图7的(B)所示,使用抗蚀剂图案95作为掩模进行离子注入,以在低浓度p区域24'和46'以外的其他扩散层中形成浅结区域(图7仅示出浅结区域23'和47'),它们是要成为另一源极/漏极区域24和一个源极/漏极区域46的扩散层。随后,去除抗蚀剂图案95。

接下来,通过CVD方法在硅半导体基板10的整个表面上沉积氧化硅膜,并且执行干法蚀刻以形成侧壁28和49。接下来,如图7的(C)所示,进行离子注入以形成一个源极/漏极区域23和另一源极/漏极区域47。

因此,如图7的(C)所示,另一源极/漏极区域24和一个源极/漏极区域46在硅半导体基板10的厚度方向上均具有比除那些源极/漏极区域以外的扩散层更深的区域。此外,另一源极/漏极区域24和一个源极/漏极区域46分别是在硅半导体基板10的厚度方向上具有杂质浓度梯度的区域。

注意,如在第二实施例中所述,可以提供这样的构造,其中,在形成侧壁的同时形成与后述的硅化物非形成区域相对应的绝缘膜。

接下来,在硅半导体基板10的整个表面上沉积绝缘膜。如图7的(D)所示,在绝缘膜上形成与硅化物非形成区域相对应的抗蚀剂图案,并且通过将抗蚀剂图案用作掩模通过干法蚀刻等对绝缘膜进行图案化,以形成绝缘膜80。在第三实施例中,绝缘膜80被形成为覆盖驱动晶体管TRDrv的另一源极/漏极区域(扩散层)24和第二发光控制晶体管TREl_c_2的一个源极/漏极区域46,并且不形成在其他扩散层上。

接下来,通过溅射将金属层沉积在硅半导体基板10的整个表面上,并加热以形成硅化物90。

接下来,去除未与硅原子反应的金属层。因此,硅化物90残留在未形成绝缘膜80的扩散层上(在图7中,栅极电极21、一个源极/漏极区域23和一个源极/漏极区域46的一部分)。此外,对硅化物90进行退火以使硅化物90稳定。随后,如图7的(E)所示,形成层间绝缘层69,并形成接触电极70、71和72。

因此,除了将要施加高电压的扩散层设置到其中没有形成硅化物的扩散层的配置之外,并且这样的扩散层设置为比形成硅化物的其他扩散层更深的扩散层,并因此,可以减轻电场并抑制击穿现象的发生。这种配置适合于要施加高电压的显示装置,例如有机EL显示装置。

作为示例,其中未形成硅化物的扩散层的深度可以为300nm或更小,并且其中形成有硅化物的扩散层的深度可以大于300nm。注意,那些数值根据像素间距等适当地设置。

<第四实施例>

在图2所示的像素电路中,可以通过使用为每个像素形成的电容元件(例如,第一电容部分C1),执行使像素电路之间的驱动晶体管TRDrv的阈值电压Vth的制造变化均匀的操作(Vth校正)。

这里,在显示装置中,当通过实现高清晰度来使晶体管小型化时,电容元件(电容值)也减小,并且寄生电容的比率相对增加,并且Vth校正功能不能充分发挥作用。例如,在图2所示的像素电路中,在图像信号写入晶体管TRSig中,驱动晶体管TRDrv的栅极电极21侧上的节点34的寄生电容的比率相对增加。特别地,当在硅半导体基板10上形成构成像素电路120的晶体管时,在另一源极/漏极区域24与硅半导体基板10的p-n结中形成的寄生电容增加。

另一方面,在本实施例中,不执行离子注入以形成另一源极/漏极区域24的杂质区,并因此,另一源极/漏极区域24的表面具有比其他扩散层的表面低的杂质浓度。

具体地,在第二实施例中描述的制造过程中,在形成侧壁28和49之后执行离子注入。然而,在该实施例中,在形成侧壁28和侧壁49之后,如图8的(A)所示,在另一源极/漏极区域24和一个源极/漏极区域46被抗蚀剂图案96覆盖的状态下进行离子注入。因此,另一源极/漏极区域24的表面具有比其他扩散层的表面更低的杂质浓度。

随后,如图8的(B)所示,通过第二实施例中描述的制造过程形成绝缘层80。

这里,在显示装置中,当执行图像信号的写入操作时,驱动晶体管的源极电压增加到发光部分ELP的发射电压。由于源极电压的这种波动,由于保持电容的耦合,驱动晶体管的栅极电压也增加。栅极电压的上升与源极电压的上升之比称为自举增益。由于像素电路中的晶体管的寄生电容,可以减小这种自举增益。像素电路中的晶体管的寄生电容具有该晶体管的阈值电压Vth作为参数。因此,由于像素电路中晶体管的阈值电压Vth的变化,自举增益可能针对每个像素而变化。在这种情况下,每个像素的发光亮度变化,并且损害了屏幕的亮度均匀性。

相反,在本实施例中,通过将要施加高电压的另一源极/漏极区域(扩散层)24的表面设置为杂质离子浓度低于其他扩散层表面浓度的区域,可以增加耗尽层宽度。因此,可以减轻另一源极/漏极区域24和n型扩散层(n阱)11之间的电场,可以减小另一源极/漏极区域24和n型扩散层(n阱)11之间的寄生电容,并且可以提高自举增益。

因此,提高了驱动晶体管的阈值电压Vth的变化的校正精度,并且可以提高屏幕的亮度均匀性。

注意,在图8的(A)的工序之后,如图9所示,在另一源极/漏极区域24和一个源极/漏极区域46以外的扩散层上覆盖有抗蚀剂图案97的状态,如果在制造中未执行参考图8所述的离子注入并且接触电阻成为问题,则另一源极/漏极区域24和一个源极/漏极区域46可以在最佳的离子注入条件(其中寄生电容的减小和接触电阻彼此兼容)下形成。

[电子设备的实施例]

本公开的有机EL显示装置例如结合在后述的应用示例1至6的各种电气装置中。注意,应用示例不限于这些,并且本公开的有机EL显示装置可以应用于例如其他电子设备,诸如便携式信息终端、智能电话、便携式音乐播放器、游戏器、电子书、电子词典中的各种显示单元和电子取景器。

如上所述的本公开的有机EL显示装置即使小型化也具有稳定的显示质量并且提供高清晰度,并因此可以向其中结合有有机EL显示装置的电子设备的用户提供高显示质量的图像。

(应用示例1)

图10示出了作为电子设备的电视装置300的外观。该电视装置包括例如包括前面板310和滤光玻璃320的视频显示屏单元301。视频显示屏单元301包括根据上述实施例的显示装置。

(应用示例2)

图11示出了作为电子设备的数码相机400的外观。数码相机包括例如用于闪光的发光部分410、显示单元420、菜单开关430和快门按钮440。显示单元420包括根据上述实施例的显示装置。

(应用示例3)

图12示出了作为电子设备的笔记本个人计算机500的外观。笔记本个人计算机包括例如主体510、用于输入字符等的操作的键盘520以及用于显示图像的显示单元530。显示单元530包括根据上述实施例的显示装置。

(应用示例4)

图13示出了作为电子设备的摄像机600的外观。该摄像机例如包括主体610、设置在主体610的前侧面上的用于对被摄体进行成像的透镜620、用于成像的开始/停止开关630以及显示单元640。显示单元640包括根据上述实施例的显示装置。

(应用示例5)

图14示出了作为电子设备的移动电话700的外观。例如,通过将上壳体710和下壳体720与连接部分(铰链部分)730连接来获得移动电话,并且该移动电话包括显示器740、子显示器750、图片灯760和相机770。显示器740或子显示器750包括根据上述实施例的显示装置。

(应用示例6)

图15示出了作为电子设备的头戴式显示器800的外观。通过将安装有眼镜的单眼显示器810安装在诸如眼镜、护目镜或太阳镜的眼镜800上来获得该头戴式显示器。装有眼镜的单眼显示器810包括根据上述实施例的显示装置。

此外,根据上述实施例的显示装置可以应用于例如用于虚拟现实(VR)、增强现实(AR)或混合现实(MR)的头戴式显示器,作为头戴式显示器的另一种形式。

本技术的实施例不限于上述实施例,并且在不脱离本技术的要旨的情况下可以进行各种修改。

例如,在上述实施例中,已经描述了在硅半导体基板上形成晶体管的示例,但是晶体管可以配置为形成在玻璃等的基板上,在该基板上形成有半导体膜作为硅区域。

在上述实施例中,已经示例了其中各种晶体管的沟道的导电类型是p型的PMOS,但是可以使用n型NMOS。

此外,在上述实施例中,已经例示了包括四个晶体管(驱动晶体管TRDrv,图像信号写入晶体管TRSig,第一发光控制晶体管TREl_c_1和第二发光控制晶体管TREl_c_2)和两个电容部分(第一电容部分C1和第二电容部分C2)的像素电路。然而,本技术不限于此,并且包括至少多个晶体管就足够了。例如,像素电路可以包括三个晶体管和一个电容部分,三个晶体管和两个电容部分,或者四个晶体管和一个电容部分。

此外,在上述实施例中,已经描述了在外围电路中没有硅化物非形成区域的情况,但是也可以在外围电路中提供硅化物非形成区域。

此外,在上述实施例中,在使用OLED构造发光部分的情况下,但是,可以使用自发光类型的另一个发光部分,例如使用无机电致发光部分、发光二极管(LED)发光部分或半导体激光发光部分作为发光部分。

注意,本技术可以采用以下配置。

(1)一种显示装置,包括:

发光部分;以及

驱动电路,包括驱动发光部分并包括第一扩散层和第一接触电极的晶体管,第一扩散层不包括在硅区域中形成的硅化物,第一接触电极电连接至第一扩散层。

(2)根据(1)的显示装置,其中,

驱动电路包括晶体管,该晶体管包括第二扩散层和第二接触电极,第二扩散层包括在硅区域中形成的硅化物,第二接触电极电连接到第二扩散层。

(3)根据(2)的显示装置,其中,

第一扩散层的扩散层表面的杂质浓度比第二扩散层的低。

(4)根据(2)或(3)的显示装置,其中,

第一扩散层包括比第二扩散层更深的区域。

(5)根据(1)至(4)中任一项的显示装置,其中,

驱动电路包括具有经由第一接触电极连接至发光部分的第一扩散层的晶体管。

(6)根据(5)的显示装置,其中,

包括第一扩散层的晶体管是作为电流限制元件工作的驱动晶体管。

(7)根据(1)至(6)中任一项的显示装置,其中,

驱动电路包括图像信号写入晶体管,图像信号写入晶体管包括第一扩散层并且导通或截止流过发光部分的驱动电流。

(8)根据(1)至(7)中任一项的显示装置,其中,

驱动电路还包括覆盖第一扩散层的绝缘膜。

(9)根据(1)至(8)中任一项的显示装置,其中,

发光部分是有机电致发光二极管。

(10)一种电子设备,包括

显示装置,包括

发光部分,以及

驱动电路,包括驱动发光部分并包括第一扩散层和第一接触电极的晶体管,第一扩散层不包括在硅区域中形成的硅化物,

第一接触电极电连接至第一扩散层。

参考标号列表

10硅半导体基板(硅区域)

21、31、35、61栅极电极(扩散层)

23驱动晶体管TRDrv的一个源极/漏极区域(第一扩散层,第二扩散层)

24驱动晶体管TRDrv的另一源电极/漏电极(第一扩散层)

33图像信号写入晶体管TRSig的一个源极/漏极区域(第一扩散层,第二扩散层)

34图像信号写入晶体管TRSig的另一源极/漏极区域(第一扩散层,第二扩散层)

36第一发光控制晶体管TREl_c_1的一个源极/漏极区域(第一扩散层,第二扩散层)

37第一发光控制晶体管TREl_c_1的另一源极/漏极区域(第一扩散层,第二扩散层)

46第二发光控制晶体管TREl_c_2的一个源极/漏极区域(第一扩散层)

47第二发光控制晶体管TREl_c_2的另一源电极/漏电极(第一扩散层)

63外围电路的晶体管的另一源极/漏极区域(第二扩散层)

64外围电路的晶体管的另一源极/漏极区域(第二扩散层)

60外围电路的晶体管(晶体管)

70接触电极(第一接触电极,第二接触电极)

71接触电极(第一接触电极)

73、74接触电极(第二接触电极)

80、81绝缘膜

90硅化物

100显示装置

110外围电路(驱动电路)

120像素电路(驱动电路)

300电视装置(电子设备)

301视频显示屏单元(显示装置)

400数码相机(电子设备)

420显示单元(显示装置)

500笔记本个人计算机(电子设备)

530显示单元(显示装置)

600摄像机(电子设备)

640显示单元(显示装置)

700移动电话(电子设备)

740显示器(显示装置)

750子显示器(显示装置)

800头戴式显示器(电子设备)

810单眼显示器(显示装置)

ELP发光部分

TRDrv驱动晶体管(晶体管)

TRSig图像信号写入晶体管(晶体管)

TREl_c_1第一发光控制晶体管(晶体管)

TREl_c_2第二发光控制晶体管(晶体管)。

- 显示装置、包括该显示装置的电子设备以及操作该电子设备的方法

- 电子设备的显示装置和包括该显示装置的电子设备