半导体装置

文献发布时间:2023-06-19 10:51:07

技术领域

本发明涉及半导体装置。

背景技术

在半导体装置中包含各种电路区域,作为电路区域的一例,存在标准单元区域。在标准单元区域中包含各种逻辑电路和电源开关电路。

电源开关电路例如设置于向半导体装置供给的VDD的电位的电源线与向逻辑电路的晶体管供给VDDV的电位的电源线之间,切换对该晶体管的VDDV的电源电位的供给的导通/截止。通过使用电源开关电路,在不需要使逻辑电路进行动作时使电源供给截止,抑制在构成逻辑电路的晶体管中产生的漏电电流,能够降低消耗电力。

另外,提出如下的技术:在主要的半导体芯片的里侧粘贴包含布线的从属半导体芯片,并经由从属半导体芯片的布线而向主半导体芯片的晶体管供给电源电位。

专利文献1:美国专利第6355950号说明书;

专利文献2:美国专利第9754923号说明书;

专利文献3:日本特开2014-072488号公报。

然而,在包含电源开关电路的半导体装置中,关于从属半导体芯片内的各种电源线的布置这样的具体的结构,未进行详细的研究。

发明内容

本发明的目的在于,提供在从属半导体芯片内具有研究了具体的结构的各种电源线的半导体装置。

发明技术的半导体装置具有第一半导体芯片和第二半导体芯片。第一半导体芯片具有:基板,具有与第二半导体芯片对置的第一主面和与第一主面相反的第二主面;第一电源线和第二电源线,设置在基板的第二主面侧;电源开关电路,电设置在第一电源线与第二电源线之间;第一导通孔,设置于基板并从第一电源线到达第一主面;以及第二导通孔,设置于基板并从第二电源线到达第一主面。第二半导体芯片具有:第三电源线,与第一导通孔连接;以及第四电源线,与第二导通孔连接。

根据发明的技术,能够提高在包含电源开关电路的半导体芯片内的布线的布置的自由度。

附图说明

图1是表示第一实施方式的半导体装置的概况的剖视图。

图2是表示第一实施方式的第一半导体芯片的布局的图。

图3是表示第一实施方式的电源开关电路的结构的电路图。

图4是表示缓冲器的结构的电路图。

图5是表示第一实施方式的标准单元区域的平面结构的示意图。

图6是表示第一实施方式的标准单元区域的剖视图(其1)。

图7是表示第一实施方式的标准单元区域的剖视图(其2)。

图8是表示第一实施方式的标准单元区域的剖视图(其3)。

图9是表示第一实施方式的第二半导体芯片的平面结构的示意图。

图10是表示第一实施方式的第二半导体芯片的剖视图(其1)。

图11是表示第一实施方式的第二半导体芯片的剖视图(其2)。

图12是表示第一实施方式的第二半导体芯片的剖视图(其3)。

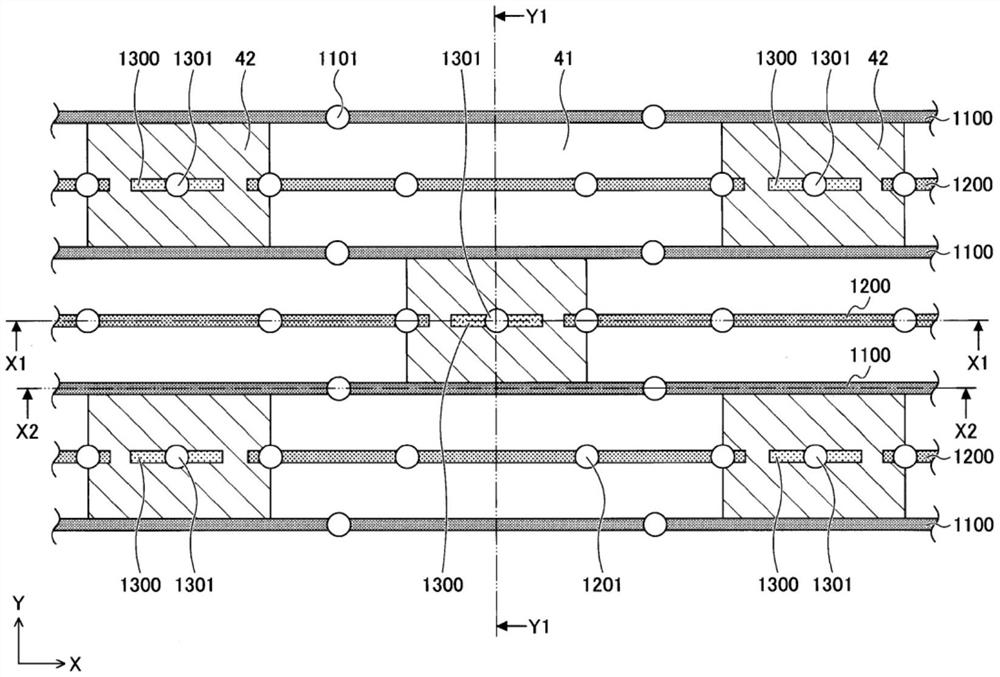

图13是表示第一实施方式的标准单元区域和第二半导体芯片的平面结构的示意图。

图14是表示第一实施方式的标准单元区域和第二半导体芯片的剖视图(其1)。

图15是表示第一实施方式的标准单元区域和第二半导体芯片的剖视图(其2)。

图16是表示第一实施方式的标准单元区域和第二半导体芯片的剖视图(其3)。

图17是表示第一半导体芯片的导通孔与第二半导体芯片的信号线的连接部的一例的剖视图。

图18是表示第一实施方式的电源开关电路的平面结构的示意图(其1)。

图19是表示第一实施方式的电源开关电路的平面结构的示意图(其2)。

图20是表示第一实施方式的电源开关电路的平面结构的示意图(其3)。

图21是表示第二实施方式的标准单元区域和第二半导体芯片的平面结构的示意图。

图22是表示第三实施方式的电源开关电路的平面结构的示意图(其1)。

图23是表示第三实施方式的电源开关电路的平面结构的示意图(其2)。

图24是表示第四实施方式的第二半导体芯片的平面结构的示意图(其1)。

图25是表示第四实施方式的第二半导体芯片的平面结构的示意图(其2)。

图26是表示第四实施方式的第二半导体芯片的剖视图(其1)。

图27是表示第四实施方式的第二半导体芯片的剖视图(其2)。

图28是表示第四实施方式的标准单元区域和第二半导体芯片的平面结构的示意图。

图29是表示第五实施方式的电源开关电路的平面结构的示意图。

图30是表示第六实施方式的电源开关电路的平面结构的示意图。

图31是表示第七实施方式的标准单元区域和第二半导体芯片的平面结构的示意图。

图32是表示第七实施方式的标准单元区域和第二半导体芯片的剖视图。

图33是表示第七实施方式的电源开关电路的平面结构的示意图。

图34是表示第八实施方式的电源开关电路的结构的电路图。

图35是表示第八实施方式的电源开关电路的平面结构的示意图。

具体实施方式

以下,一边参照附图一边具体地说明实施方式。此外,在本说明书和附图中,对于实质上具有相同的功能结构的构成要素,有时标注相同的附图标记而省略重复的说明。另外,在以下的说明中,将与基板的表面平行且相互正交的两个方向设为X方向、Y方向,将与基板的表面垂直的方向设为Z方向。另外,本发明中的布置的一致并不是严格地排除因制造上的偏差引起的不一致的情况,即使在由于制造上的偏差而在布置中产生偏移的情况下,也能够视为布置一致。

(第一实施方式)

首先,对第一实施方式进行说明。图1是表示第一实施方式的半导体装置的概况的剖视图。

如图1所示,第一实施方式的半导体装置包含第一半导体芯片10和第二半导体芯片20。

第一半导体芯片10例如包含基板11和布线层12。基板11例如是硅基板,在基板11的表面侧形成有晶体管等半导体元件。晶体管例如是在源极、漏极和沟道中包含鳍片13的FinFET。布线层12形成在基板11的表面上,包含布线14和绝缘层15。布线14的一部分与鳍片13连接。而且,例如在基板11的表面侧形成有与布线14连接的电源线16,在基板11设置有从电源线16相连到基板11的里面的导通孔17。导通孔17例如是硅导通孔(through-siliconvia:TSV)。此外,也可以如图1所示,布线14的一部分具有导通孔这样的形状,与电源线16连接。

第二半导体芯片20与第一半导体芯片10的基板11的里面对置地布置。第二半导体芯片20例如包含基板21、布线部22和焊盘23。基板21例如为硅基板。布线部22形成在基板21的表面上,包含布线24和绝缘层25。布线部22的上表面例如与第一半导体芯片10的基板11的里面对置。即,布线部22位于基板11与基板21之间。此外,也可以如图1所示,布线部22具有多层的布线24。另外,多层的布线24也可以经由设置于布线部22的导通孔28而连接。焊盘23例如是与布线基板、板等连接的外部连接端子。布线24的一部分与导通孔17连接。焊盘23设置于基板21的里面,在基板21设置有将布线24和焊盘23连接的导通孔26。导通孔26例如是TSV。

在图1中,在俯视时第二半导体芯片20比第一半导体芯片10大,但第二半导体芯片20也可以具有与第一半导体芯片10相同程度的尺寸,也可以具有比第一半导体芯片10大的尺寸。另外,焊盘23也可以在与第一半导体芯片10对置的一侧的第二半导体芯片20的面上,在俯视时设置于第一半导体芯片10的外侧。

此外,图1所示的剖视图表示半导体装置的概况,详细内容如图6~图8、图10~图12、图14~图16所示。

接下来,对第一半导体芯片10进行说明。图2是表示第一半导体芯片10的布局的图。图3是表示在第一半导体芯片10中包含的电源开关电路的结构的电路图。

如图2所示,第一半导体芯片10包含多个标准单元区域31以及布置于其周边的输入输出(I/O)单元区域32。此外,标准单元区域31的布置数量可以是1个,也可以是3个以上。如图3所示,标准单元区域31包含标准单元41和电源开关电路42。标准单元41例如包含NAND电路、逆变器电路等各种逻辑电路。在标准单元区域31布置有对标准单元41供给接地电位的VSS布线和供给电源电位的VDDV布线。在标准单元区域31还布置有从外部对电源开关电路42供给电源电位的VDD布线。

如图3所示,电源开关电路42包含开关晶体管51和电源开关控制电路52。开关晶体管51例如是P沟道MOS晶体管,连接在VDD布线与VDDV布线之间。电源开关控制电路52与开关晶体管51的栅极连接,控制开关晶体管51的动作。通过电源开关控制电路52而切换开关晶体管51的导通/截止,控制VDD布线与VDDV布线之间的导通。电源开关控制电路52例如是缓冲器。

接下来,对电源开关控制电路52所使用的缓冲器的结构进行说明。图4是表示缓冲器的结构的电路图。

如图4所示,电源开关控制电路52所使用的缓冲器60具有逆变器61和逆变器62。将输入信号IN向逆变器61输入,将逆变器61的输出向开关晶体管51的栅极和逆变器62输入,将输出信号OUT从逆变器62输出。逆变器61和62都包含1对P沟道MOS晶体管和N沟道MOS晶体管。此外,逆变器61和62的结构是一例,例如,逆变器61和62中包含的P沟道MOS晶体管和N沟道MOS晶体管的对也可以是2个以上。

接下来,对标准单元区域31的构造进行说明。图5是表示第一实施方式的标准单元区域31的平面结构的示意图。图6~图8是表示第一实施方式的标准单元区域31的剖视图。图6相当于沿着图5中的X1-X1线的剖视图,图7相当于沿着图5中的X2-X2线的剖视图,图8相当于沿着图5中的Y1-Y1线的剖视图。

如图5~图8所示,在标准单元区域31,沿X方向延伸的电源线1100与沿X方向延伸的电源线1200在Y方向上交替地布置。电源线1200主要布置在标准单元41中。另外,在电源开关电路42中布置有X方向延伸的电源线1300。例如,电源线1300在Y方向上相邻的2根电源线1100之间,布置于在X方向上将电源开关电路42夹在中间的2根电源线1200之间,位于与电源线1200相同的Y坐标。例如,电源线1100相当于VDDV布线,电源线1200相当于VSS布线,电源线1300相当于VDD布线。

如图6~图8所示,在基板11的表面形成有元件分离膜102。元件分离膜102例如通过STI(Shallow Trench Isolation:浅沟槽隔离)法而形成。在基板11和元件分离膜102形成有沿X方向延伸的多个槽,电源线1100、1200和1300形成于这些槽内。例如,电源线1100、1200和1300的表面被绝缘膜103覆盖。例如,元件分离膜102的表面和绝缘膜103的表面可以与基板11的表面为同一面,也可以不是同一面。这样的构造的电源线1100、1200和1300有时被称为BPR(Buried Power Rail:埋入式电源导轨)。

在基板11的上方形成有绝缘膜104,在绝缘膜104中形成有局部布线9000。局部布线9000的一部分通过形成于绝缘膜103的开口部而与电源线1100、1200或者1300连接。另外,局部布线9000的一部分与鳍片8000连接。鳍片8000是鳍片13的一部分,局部布线9000是布线14的一部分。

在绝缘膜104上形成有绝缘膜105,在绝缘膜105中形成有各种布线。绝缘膜103、104和105是绝缘层15的一部分。

在基板11形成有将基板11贯通到里面的导通孔1101、1201和1301。导通孔1101形成在电源线1100下,导通孔1201形成在电源线1200下,导通孔1301形成在电源线1300下。多个导通孔1101在沿Y方向延伸的直线上排列,多个导通孔1201在沿Y方向延伸的直线上排列,多个导通孔1301在沿Y方向延伸的直线上排列。而且,这些直线在X方向上相互错开。此外,在导通孔1101、1201和1301与基板11之间形成有绝缘膜。电源线1100、1200和1300是电源线16的一部分,导通孔1101、1201和1301是导通孔17的一部分。

接下来,对第二半导体芯片20进行说明。图9是表示第一实施方式的第二半导体芯片20的平面结构的示意图。在图9中,表示在俯视时与图5所示的部分重叠的部分。图10~图12是表示第一实施方式的第二半导体芯片20的剖视图。图10相当于沿着图9中的X1-X1线的剖视图,图11相当于沿着图9中的X2-X2线的剖视图,图12相当于沿着图9中的Y1-Y1线的剖视图。

如图9~图12所示,第二半导体芯片20例如包含形成在基板21上的绝缘膜203、以及形成于绝缘膜203的表层部的电源线3100、3200和3300。电源线3100、3200和3300沿X方向延伸。在绝缘膜203上形成覆盖电源线3100、3200和3300的绝缘膜204,在绝缘膜204内形成有电源线2100、2200和2300。电源线2100、2200和2300沿Y方向延伸。电源线2100、2200和2300的上表面从绝缘膜204露出。电源线2100布置于与多个导通孔1101排列的直线重叠的位置,电源线2200布置于与多个导通孔1201排列的直线重叠的位置,电源线2300布置于与多个导通孔1301排列的直线重叠的位置。电源线3100经由在绝缘膜204中形成的导通孔2101而相互与电源线2100连接。电源线3200经由在绝缘膜204中形成的导通孔2201而相互与电源线2200连接。电源线3300经由在绝缘膜204中形成的导通孔2301而相互与电源线2300连接。电源线2100、2200、2300、3100、3200和3300是布线24的一部分,导通孔2101、2201和2301是导通孔28的一部分。绝缘膜204是绝缘层25的一部分。

省略图9~图12中的图示,但与电源线3200连接的导通孔和与电源线3300连接的导通孔形成于绝缘膜203和基板21,与它们连接的焊盘形成于基板21的里面。这些导通孔和焊盘是导通孔26和焊盘23的一部分。

而且,使标准单元区域31的图5~图8所示的部分与第二半导体芯片20的图9~图12所示的部分在俯视时重合而将第一半导体芯片10布置在第二半导体芯片20上。图13是表示第一实施方式的标准单元区域31和第二半导体芯片20的平面结构的示意图。图14~图16是表示第一实施方式的标准单元区域31和第二半导体芯片20的剖视图。图14相当于沿着图13中的X1-X1线的剖视图,图15相当于沿着图13中的X2-X2线的剖视图,图16相当于沿着图13中的Y1-Y1线的剖视图。

如图13~图16所示,与电源线1100连接的导通孔1101与电源线2100连接,与电源线1200连接的导通孔1201与电源线2200连接,与电源线1300连接的导通孔1301与电源线2300连接。另外,电源线2100、2200、2300、3100、3200和3300与电源线1100、1200和1300相比,例如宽度较宽,为低电阻。但是,电源线2100、2200、2300、3100、3200和3300的宽度也可以与电源线1100、1200和1300的宽度相同、或比电源线1100、1200和1300的宽度窄。

此外,导通孔1101、1201和1301不需要与电源线2100、2200和2300直接接触,只要将它们电连接即可。例如,也可以在它们之间夹有导电材料。

图17是表示导通孔1301与电源线2300的连接部的一例的剖视图。例如,如图17所示,电源线2300被绝缘膜301覆盖,在绝缘膜301形成有开口部302。而且,也可以在开口部302的内侧,导通孔1301和电源线2300经由凸块304而相互电连接。凸块304例如是焊锡等的微凸块。绝缘膜301例如是硅氧化膜、硅氮化膜或者有机绝缘膜。在接合前的阶段,凸块304也可以设置在导通孔1301上,也可以设置在电源线2300上。例如,第一半导体芯片10和第二半导体芯片20也可以通过粘接剂305而相互接合。

也可以取代凸块304,而使用锡(Sn)等金属膜。另外,也可以在开口部302的内侧,在电源线2300上设置有焊盘。在该情况下也是,能够将凸块304或者金属膜用于与导通孔1301的连接。

导通孔1101和1201与电源线2100和2200的关系也相同。

另外,也可以是,第一半导体芯片10的导通孔1101、1201和1301从基板11的里面突出,该突出的部分与电源线2100、2200和2300接触。另外,也可以在第一半导体芯片10的里面设置再布线,在俯视时,使导通孔1101、1201和1301的位置和与电源线2100、2200和2300的接合部的位置错开。

例如,电源线1100、1200和1300的材料使用钴(Co)、钌(Ru)或者钨(W)等。例如,电源线2100、2200、2300、3100、3200和3300的材料使用铜(Cu)、铝(Al)、钨(W)或者钴(Co)等。例如,第一布线层或者第二布线层等、设置于基板11的上方的布线的材料使用铜(Cu)、铝(Al)、钨(W)或者钴(Co)等。

接下来,对第一实施方式的电源开关电路42的构造进行说明。图18~图20是表示第一实施方式的电源开关电路42的平面结构的示意图。图18主要表示电源线、布线和栅极电极的布局。图19主要表示栅极电极和电源线的布局。图20主要表示第一布线层和第二布线层的布局。

如上述那样,电源开关电路42包含开关晶体管51和电源开关控制电路52。另外,电源开关电路42具有沿Y方向延伸的多个局部布线、沿X方向延伸的多个布线、以及沿Y方向延伸的多个布线。例如,局部布线与晶体管的鳍片或者栅极电极接触。例如,沿X方向延伸的布线形成于局部布线的上方的第一布线层,沿Y方向延伸的布线形成于第一布线层的上方的第二布线层。在以下的说明中,导通孔1500是局部布线与其下方的电源线之间的导通孔,导通孔8500是设置于局部布线与其上方的第一布线层之间的导通孔,导通孔4500是设置于第一布线层与其上方的第二布线层之间的导通孔。

开关晶体管51包含沿Y方向延伸且沿X方向排列的多个栅极电极511。开关晶体管51还包含沿X方向延伸且沿Y方向排列的多个鳍片8511。例如,鳍片8511的一部分作为源极发挥功能,另一部分作为漏极发挥功能,另一部分作为沟道发挥功能。在栅极电极511的两侧布置有多个局部布线9511。局部布线9511与源极或者漏极连接。与源极连接的局部布线9511经由导通孔8500而与布线4001连接,与漏极连接的局部布线9511经由导通孔1500而与电源线1100连接。另外,栅极电极511经由局部布线9512和导通孔8500而与布线4002连接。布线4001和4002沿X方向延伸。

电源开关控制电路52包含逆变器61和62。逆变器61包含P沟道MOS晶体管610P和N沟道MOS晶体管610N。逆变器62包含P沟道MOS晶体管620P和N沟道MOS晶体管620N。

逆变器61包含在P沟道MOS晶体管610P和N沟道MOS晶体管610N中共用的沿Y方向延伸的栅极电极611。栅极电极611经由局部布线9613和导通孔8500而与布线4005连接。布线4005沿X方向延伸。将输入信号IN向布线4005输入(参照图4)。

P沟道MOS晶体管610P包含沿X方向延伸且沿Y方向排列的多个鳍片8611。例如,鳍片8611的一部分作为源极发挥功能,另一部分作为漏极发挥功能,另一部分作为沟道发挥功能。在栅极电极611的两侧布置有局部布线9611。局部布线9611与源极或者漏极连接。与源极连接的局部布线9611经由导通孔8500而与布线4001连接,与漏极连接的局部布线9611经由导通孔8500、布线4003和导通孔4500而与布线5001连接。布线4003沿X方向延伸,布线5001沿Y方向延伸。

N沟道MOS晶体管610N包含沿X方向延伸且沿Y方向排列的多个鳍片8612。例如,鳍片8612的一部分作为源极发挥功能,另一部分作为漏极发挥功能,另一部分作为沟道发挥功能。在栅极电极611的两侧布置有局部布线9612。局部布线9612与源极或者漏极连接。与源极连接的局部布线9612经由导通孔1500而与电源线1200连接,与漏极连接的局部布线9612经由导通孔8500、布线4004和导通孔4500而与布线5001连接。布线4004沿X方向延伸。

逆变器62包含在P沟道MOS晶体管620P和N沟道MOS晶体管620N中共用的沿Y方向延伸的栅极电极621。栅极电极621经由局部布线9623和导通孔8500而与布线4008连接。布线4008沿X方向延伸。

P沟道MOS晶体管620P包含沿X方向延伸且沿Y方向排列的多个鳍片8621。例如,鳍片8621的一部分作为源极发挥功能,另一部分作为漏极发挥功能,另一部分作为沟道发挥功能。在栅极电极621的两侧布置有局部布线9621。局部布线9621与源极或者漏极连接。与源极连接的局部布线9621经由导通孔8500而与布线4001连接,与漏极连接的局部布线9621经由导通孔8500、布线4006和导通孔4500而与布线5002连接。布线4006沿X方向延伸,布线5002沿Y方向延伸。

N沟道MOS晶体管620N包含沿X方向延伸且沿Y方向排列的多个鳍片8622。例如,鳍片8622的一部分作为源极发挥功能,另一部分作为漏极发挥功能,另一部分作为沟道发挥功能。在栅极电极621的两侧布置有局部布线9622。局部布线9622与源极或者漏极连接。与源极连接的局部布线9622经由导通孔1500而与电源线1200连接,与漏极连接的局部布线9622经由导通孔8500、布线4007和导通孔4500而与布线5002连接。布线4007沿X方向延伸。将输出信号OUT从布线5002输出(参照图4)。

布线4004和4008经由导通孔8500、局部布线9521和导通孔8500而与布线4002连接。

设置有经由导通孔8500而与布线4001连接的局部布线9001。局部布线9001经由导通孔1500而与电源线1300连接。电源线1300经由导通孔1301而与第二半导体芯片20的电源线2300连接。因此,对布线4001供给VDD布线的电源电位。此外,在图18~图20中,省略导通孔1301的图示,例如在电源线1300与电源线2300在俯视时重叠的位置布置有导通孔1301。

在与局部布线9622之间,以在X方向上夹着开关晶体管51的方式设置有局部布线9002。局部布线9622经由导通孔8500而与布线4009连接。布线4009沿X方向延伸。局部布线9002也经由导通孔8500而与布线4009连接。局部布线9002经由导通孔1500而与电源线1200连接。因此,在X方向上将电源开关电路42夹在中间的2根电源线1200在第一半导体芯片10内,经由布线4009而相互连接。

在第一实施方式中,第一半导体芯片10内的电源线1100、1200和1300沿X方向延伸,它们分别与在第二半导体芯片20内沿Y方向延伸的电源线2100、2200和2300连接。另外,电源线2100、2200和2300分别与在第二半导体芯片20内沿X方向延伸的电源线3100、3200和3300连接。这样,在第一实施方式中,VDDV布线、VDD布线和VSS布线分别构成电源网络。因此,能够抑制对标准单元41和电源开关电路42供给的电源电位的偏差。而且,由于电源线2100、2200和2300设置于第二半导体芯片20,因此能够提高第一半导体芯片10内的布线的布置的自由度。特别是,由于电源线1100、1200和1300是BPR,因此能够提高设置于第一布线层和第二布线层的其他布线的布置的自由度。

而且,关于电源开关电路42,向开关晶体管51和电源开关控制电路52供给VDD的电源电位的供给源即导通孔1301在俯视时位于开关晶体管51和电源开关控制电路52之间。因此,用于向开关晶体管51供给VDD的电源电位的布线的布局和用于向电源开关控制电路52供给VDD的电源电位的布线的布局变得容易。

此外,也可以是在第二半导体芯片20内设置于第一半导体芯片10侧的电源线(例如电源线2100、2200和2300)沿X方向延伸,设置于远离第一半导体芯片10的一侧的电源线(例如电源线3100、3200和3300)沿Y方向延伸。

另外,各导通孔的平面形状没有特别限定,例如能够采用圆形、椭圆形、正方形或者矩形等。

另外,电源开关电路42的尺寸没有特别限定。在图5等所示的例子中,电源开关电路42在Y方向上跨越2根电源线1100而布置,但例如电源开关电路42也可以在Y方向上跨越3根或者4根电源线1100而布置。

(第二实施方式)

接下来,对第二实施方式进行说明。第二实施方式在电源开关电路42内的电源线的布置等方面与第一实施方式不同。图21是表示第二实施方式的标准单元区域31和第二半导体芯片20的平面结构的示意图。

如图21所示,在第二实施方式中,在电源开关电路42内设置有将在X方向上将该电源开关电路42夹在中间的2根电源线1200相连的联络电源线1400。联络电源线1400与电源线1100、1200和1300同样,形成于在基板11和元件分离膜102中形成的槽内,联络电源线1400的表面也被绝缘膜103覆盖。即,联络电源线1400也为BPR。

另外,在第一实施方式中,与电源线1200连接的电源线2200在俯视时与电源开关电路42邻接,但在第二实施方式中,电源线2200与电源开关电路42分离地布置。另外,电源线2100在俯视时与电源开关电路42邻接地布置。

其他结构与第一实施方式相同。

通过第二实施方式也能够得到与第一实施方式相同的效果。另外,在第二实施方式中,在第一半导体芯片10内经由联络电源线1400而在X方向上连接电源线1200,因此通过电源线1200和2200以及联络电源线1400构成VSS布线的电源网络。因此,能够省略电源线3200。因此,电源线2100、3100、3300的布置的自由度提高。另外,也可以省略电源线3100。

此外,联络电源线1400不需要为BPR,也可以设置于第一布线层等基板11的上方的布线层。此时,联络电源线1400的一部分也可以布置为在俯视时与电源线1300重叠。

(第三实施方式)

接下来,对第三实施方式进行说明。第三实施方式在电源开关电路42的平面结构的方面与第一实施方式不同。图22~图23是表示第三实施方式的电源开关电路42的平面结构的示意图。图22主要表示电源线、布线和栅极电极的布局。图23主要表示第一布线层和第二布线层的布局。

如图22~图23所示,在第三实施方式中,在电源开关电路42设置有沿X方向延伸的布线4011和4012。布线4011经由局部布线9511而与开关晶体管51的源极连接,布线4012经由局部布线9511而与开关晶体管51的漏极连接。在Y方向上,布线4011布置在布线4001与布线4002之间,布线4012布置在布线4001与布线4011之间。布线4011经由导通孔8500而与局部布线9001连接。布线4011和4012形成于第一布线层。此外,也可以如图22所示,将布线4002布置成在俯视时与电源线1100重叠。

在电源开关电路42设置有沿Y方向延伸的多个布线5011。布线5011布置在局部布线9511的上方,经由导通孔4500等而与局部布线9511连接。布线5011形成于第二布线层。

其他结构与第一实施方式相同。

在第三实施方式中,在开关晶体管51处于导通状态时不仅是局部布线9511,而且布线5011也成为电流路径。因此,降低布线电阻。因此,能够抑制电迁移(ElectroMigration:RM)和电压下降(IR降)。

特别是,由于将布线4012与开关晶体管51的漏极连接,将布线4011与源极连接,因此能够进一步强化电源电位的供给。

此外,优选在多个布线5011之间Y方向的端部的位置一致。这是因为,在制造工序中,图案变得均匀,能够抑制尺寸的偏差等的影响。另外,电源开关控制电路52内的布线5001和5002的Y方向的端部的位置也可以与布线5011的Y方向的端部的位置一致。其中,Y方向的端部的位置也可以不一致。

(第四实施方式)

接下来,对第四实施方式进行说明。第四实施方式在第二半导体芯片20的结构的方面与第一实施方式不同。图24~图25是表示第四实施方式的第二半导体芯片20的平面结构的示意图。图24主要表示最靠第一半导体芯片10侧的布线层的布局。图25主要表示剩余的布线层的布局。图26~图27是表示第四实施方式的第二半导体芯片20的剖视图。图26相当于沿着图24~图25中的X1-X1线的剖视图,图27相当于沿着图24~图25中的X2-X2线的剖视图。图28是表示第四实施方式的标准单元区域和第二半导体芯片的平面结构的示意图。

如图24~图28所示,在第四实施方式中,在绝缘膜204上形成有绝缘膜205,在绝缘膜205的表面形成有全面状的导电膜6100。在导电膜6100的与第一半导体芯片10的导通孔1201或者1301重叠的部分形成有开口部6110。在与导通孔1201重叠的部分,在开口部6110的内侧形成有导电膜6200,在与导通孔1301重叠的部分,在开口部6110的内侧形成有导电膜6300。在与导通孔1101重叠的部分未形成开口部6110,而设置有导电膜6100。在绝缘膜205内形成有将导电膜6200和电源线2200连接的导通孔6201以及将导电膜6300和电源线2300连接的导通孔6301。导电膜6100、6200和6300以及导通孔6201和6301是布线24的一部分。绝缘膜205是绝缘层25的一部分。

与第一实施方式不同,在第二半导体芯片20未设置电源线2100和3100。

其他结构与第一实施方式相同。

在第四实施方式中,由于导电膜6100作为VDDV布线发挥功能,因此能够进一步强化VDDV布线的电源网络,能够更均匀地对标准单元41供给VDDV的电源电位。

(第五实施方式)

接下来,对第五实施方式进行说明。第五实施方式在电源开关电路42的平面结构的方面与第一实施方式不同。图29是表示第五实施方式的电源开关电路42的平面结构的示意图。

如图29所示,在第五实施方式中,在俯视时与第二半导体芯片20的电源开关电路42重合的部分设置有2根电源线2300,第一半导体芯片10内的电源线1300形成为在俯视时与该2根电源线2300重合。而且,电源线1300经由2个部位的导通孔1301而与该2根电源线2300连接。导通孔1301例如布置于电源线1300与电源线2300在俯视时重叠的位置即2个部位。另外,布线4001与局部布线9611或者9621和局部布线9001连接,但未延伸到局部布线9511。局部布线9511中的与开关晶体管51的源极连接的局部布线延伸到布线4002,经由导通孔1500而与布线4002连接。

其他结构与第一实施方式相同。

在第五实施方式中,从布线4002向局部布线9511供给VDD的电源电位而不经由局部布线9001。另外,经由2根电源线2300和2个部位的导通孔1301而向电源线1300供给VDD的电源电位。因此,能够通过开关晶体管51而稳定地供给VDD的电源电位。

此外,即使按每个电源开关电路42设置的电源线2300与导通孔1301的组为1组,也能够从布线4002对局部布线9511稳定地供给VDD的电源电位。

另外,在图29中,位于右侧的电源线2300布置在电源开关电路42的右边缘,但也可以布置于在俯视时与开关晶体管51重合的位置,与该电源线2300连接的导通孔1301也可以布置在电源开关电路42内。

(第六实施方式)

接下来,对第六实施方式进行说明。第六实施方式在电源开关电路42的平面结构的方面与第五实施方式不同。图30是表示第六实施方式的电源开关电路42的平面结构的示意图。

如图30所示,在第六实施方式中,按每个电源线2300独立地设置有电源线1300。导通孔1301例如布置于电源线1300与电源线2300在俯视时重叠的位置即2个部位。电源开关电路42包含在2个部位,经由导通孔1600而与电源线1300连接的布线4012。导通孔1600是设置于电源线与其上方的第一布线层之间的导通孔,布线4012设置于第一布线层。布线4012经由导通孔8500而与和开关晶体管51的源极连接的局部布线9511连接。布线4002在Y方向上布置于电源线1100与电源线1200之间,经由局部布线9512而与栅极电极511连接。而且,在Y方向上相邻的2根电源线1100之间,在比第五实施方式更宽的范围内形成有鳍片8511。即,在第五实施方式中,由于设置有电源线1300,因此在Y方向上相邻的2根电源线1100的中心附近的区域未形成鳍片8511,但在第六实施方式中,在该区域也形成有鳍片8511。

其他结构与第五实施方式相同。

通过第六实施方式也能够得到与第五实施方式相同的效果。另外,根据第六实施方式,能够使关于开关晶体管51的鳍片8511的数量和布置等的自由度更高。因此,例如能够提高鳍片8511的布置密度,缩小芯片面积。

(第七实施方式)

接下来,对第七实施方式进行说明。第七实施方式在电源线1100、1200和1300的布置等方面与第一实施方式不同。图31是表示第七实施方式的标准单元区域31和第二半导体芯片20的平面结构的示意图。图32是表示第七实施方式的标准单元区域和第二半导体芯片的剖视图。图32相当于沿着图31中的Y1-Y1线的剖视图。

在第一实施方式中,在形成于基板11和元件分离膜102的槽内形成有电源线1100、1200和1300,与此相对,如图32所示,在第七实施方式中,电源线1100、1200和1300形成于第一布线层。即,在绝缘膜104上形成有绝缘膜106,在绝缘膜106的表面形成有第一布线层。电源线1100、1200和1300分别经由导通孔而与局部布线9000连接。另外,电源线1100经由导通孔1102而与电源线2100连接,电源线1200经由导通孔1202而与电源线2200连接,电源线1300经由导通孔1302而与电源线2300连接。导通孔1102、1202和1302是贯通基板11、元件分离膜102和绝缘膜104并到达绝缘膜106内的第一布线层的里面的导通孔。

在绝缘膜106上形成有绝缘膜107,在绝缘膜107中形成有各种布线(第二布线层等)。绝缘膜106和107是绝缘层15的一部分。

接下来,对第七实施方式的电源开关电路42的构造进行说明。图33是表示第七实施方式的电源开关电路42的平面结构的示意图。

如图33所示,在第七实施方式中,在X方向上,局部布线9001位于比电源线2300靠开关晶体管51侧的位置,局部布线9521位于比局部布线9001靠开关晶体管51侧的位置。这是因为,电源线1300形成于第一布线层。电源线1300经由导通孔8600(1301)而与电源线2300连接。导通孔8600是从基板11的里面到达第一布线层的导通孔。

在第七实施方式中,也与第一实施方式同样,VDDV布线、VDD布线和VSS布线分别构成电源网络。因此,能够抑制对标准单元41和电源开关电路42供给的电源电位的偏差。而且,由于将电源线2100、2200和2300设置于第二半导体芯片20,因此能够提高第一半导体芯片10内的布线的布置的自由度。

此外,在第二~第六实施方式中,也可以与第七实施方式同样,将电源线1100、1200和1300设置于第一布线层。其中,在第五实施方式中,像第六实施方式那样按每个电源线2300设置电源线1300,按每个电源线1300设置导通孔1301。

(第八实施方式)

接下来,对第八实施方式进行说明。第八实施方式在电源开关电路42的结构等方面与第一实施方式不同。图34是表示第八实施方式的电源开关电路的结构的电路图。图35是表示第八实施方式的电源开关电路的平面结构的示意图。

如图34~图35所示,在第八实施方式中,按电源开关电路42的每个单元设置有对来自设置于单元的外部的电源开关控制电路的控制信号进行传递的控制信号线2400,在电源开关电路42的单元内未设置电源开关控制电路。此时,电源开关控制电路也可以设置在标准单元区域31外。例如,控制信号线2400与电源线2100、2200和2300同样,设置于第二半导体芯片20,沿Y方向延伸。在第一半导体芯片10设置有与控制信号线2400连接的信号线2401。信号线2401与电源线1100、1200和1300同样,形成于在基板11和元件分离膜102形成的槽内,信号线2401的表面也被绝缘膜103覆盖。即,信号线2401也是BPR。在信号线2401的基板11的里面侧形成有到达基板11的里面且与控制信号线2400连接的导通孔。

信号线2401经由导通孔1500、局部布线2402和导通孔8500而与布线4002连接。

其他结构与第一实施方式相同。

在第八实施方式中,在电源开关电路42的单元中未包含电源开关控制电路,因此能够缩小电源开关电路42的单元的面积。

此外,在第二半导体芯片20中,也可以与电源线2100、2200和2300同样,将控制信号线2400连接成网络状。另外,也可以将一个或者连接成网络状的控制信号线2400与多个电源开关电路42连接,同时控制多个开关晶体管51。

另外,在第二~第七实施方式中,也可以与第八实施方式同样,将电源开关控制电路设置于电源开关电路42的单元的外部。

此外,在本发明中,开关晶体管也可以设置在VSS布线侧,而不设置在VDD布线侧。即,也可以设置有对标准单元供给接地电位的VSSV布线,将开关晶体管连接在VSS布线与VSSV布线之间。

另外,设置于电源开关电路的晶体管也可以不是FinFET。例如,也可以是平面型的场效应晶体管。另外,也可以是使用纳米线的晶体管。另外,也可以使用具有层叠了多个晶体管的构造的互补型场效应晶体管(Complementary Field Effect Transistor:CFET)。CFET例如适合于逆变器。

以上,基于各实施方式进行了本发明的说明,但本发明不限于上述实施方式所示的要件。关于这些方面,能够在不损害本发明的主旨的范围中进行变更,能够根据其应用方式而适当地确定。

附图标记的说明

10...第一半导体芯片;20...第二半导体芯片;31...标准单元区域;32...输入输出(I/O)单元区域;41...标准单元;42...电源开关电路;51...开关晶体管;52...电源开关控制电路;1100、1200,1300、2100、2200、2300、3100、3200、3300...电源线;1400...联络电源线;1101、1102、1201、1202、1301、1302...导通孔;2400...控制信号线;6100、6200、6300...导电膜;6110...开口部。

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置