半导体装置

文献发布时间:2023-06-19 10:58:46

技术领域

本发明涉及半导体装置。

背景技术

以往,已知具有自举电容的半导体装置(例如,参照欧洲专利申请公开第743752号说明书)。自举电容包含于自举电路中,该自举电路是为了确保向被偏置为高电位的驱动电路供给正确的功率而使用的。就上述那样的半导体装置而言,基本上是作为充电对象元件的自举电容在非常短的时间被充电。因此,如上述欧洲专利申请公开第743752号说明书所公开的那样,自举电容的充电是经由能够替代性地模拟出高耐压二极管的动作的LDMOS(Laterally Diffused Metal Oxide Semiconductor)晶体管进行的。

就上述半导体装置而言,从防止由于包含LDMOS晶体管的构造中的寄生晶体管的动作而导致的半导体装置的损伤的观点出发,连接有源极电位控制电路以及背栅极电位控制电路。这些控制电路为了防止寄生晶体管进行动作而对上述LDMOS晶体管的源极电极以及背栅极电极的电位进行控制。上述源极电位控制电路以及背栅极电位控制电路这样的复杂的控制电路成为半导体装置的制造成本增加的主要原因。

发明内容

本发明是为了解决上述课题而提出的,本发明的目的在于提供一种能够抑制成本增加的半导体装置。

本发明所涉及的半导体装置向充电对象元件供给充电电流,该半导体装置具有第1导电型的半导体层、第2导电型的第1半导体区域、第1导电型的第2半导体区域、第2导电型的第3半导体区域、源极电极、漏极电极、背栅极电极以及栅极电极。第1半导体区域与充电对象元件的第1电极电连接。第1半导体区域形成于半导体层的主表面。第2半导体区域在半导体层的主表面形成于与第1半导体区域相邻的位置。第3半导体区域被供给电源电压,形成于第2半导体区域的表面。源极电极与第3半导体区域连接并且被供给电源电压。漏极电极与第1半导体区域连接并且与第1电极电连接。背栅极电极在第2半导体区域连接至与第3半导体区域分离的区域,并且接地。栅极电极以隔着栅极绝缘膜与沟道区域相对的方式配置,该沟道区域位于第3半导体区域与第1半导体区域之间的第2半导体区域。源极电极与背栅极电极之间的耐压大于电源电压。

本发明的上述以及其它目的、特征、方案以及优点根据与附图关联地理解的关于本发明的下面的详细说明而变得明确。

附图说明

图1是实施方式1所涉及的半导体装置的自举充电系统的电路图。

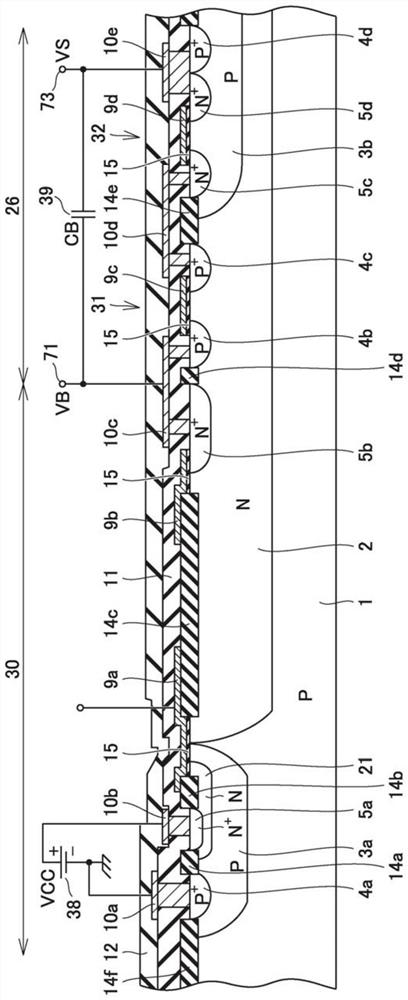

图2是图1所示的半导体装置的局部剖面示意图。

图3是参考例的半导体装置的自举充电系统的电路图。

图4是图3所示的参考例的半导体装置的局部剖面示意图。

图5是实施方式2所涉及的半导体装置的自举充电系统的电路图。

图6是图5所示的半导体装置的局部剖面示意图。

图7是实施方式3所涉及的半导体装置的局部平面示意图。

图8是图7的线段VIII-VIII处的剖面示意图。

图9是图7的线段IX-IX处的剖面示意图。

图10是实施方式4所涉及的半导体装置的局部平面示意图。

图11是图10的线段XI-XI处的剖面示意图。

图12是图10的线段XII-XII处的剖面示意图。

图13是实施方式5所涉及的半导体装置的电位检测电路的电路图。

图14是安装有图13所示的电路的半导体装置的局部平面示意图。

图15是图14的线段XV-XV处的剖面示意图。

图16是图14的线段XVI-XVI处的剖面示意图。

图17是图14的线段XVII-XVII处的剖面示意图。

图18是图14的线段XVIII-XVIII处的剖面示意图。

图19是实施方式6所涉及的半导体装置的局部平面示意图。

图20是图19的线段XX-XX处的剖面示意图。

图21是图19的线段XXI-XXI处的剖面示意图。

图22是图19的线段XXII-XXII处的剖面示意图。

图23是实施方式7所涉及的半导体装置的电位检测电路的电路图。

具体实施方式

下面,说明本发明的实施方式。此外,对相同的结构标注相同的参照编号,不重复其说明。

实施方式1.

<半导体装置的结构>

图1是实施方式1所涉及的半导体装置的自举充电系统的电路图。图2是图1所示的半导体装置的局部剖面示意图。图2示出了半导体装置处形成了高耐压的N沟道MOS晶体管30(也记载为NchMOS)的区域和高电位侧电路区域的剖面构造。

图1以及图2所示的半导体装置是主要包含高耐压控制IC 25和自举电容39的半导体装置,对晶体管36以及晶体管35进行控制。高耐压控制IC 25主要包含作为高耐压NchMOS晶体管的晶体管30、高电位侧电路26和低电位侧电路27。高电位侧电路26包含作为P沟道MOS晶体管的晶体管31和作为N沟道MOS晶体管的晶体管32。低电位侧电路27包含作为P沟道MOS晶体管的晶体管33和作为N沟道MOS晶体管的晶体管34。

高耐压控制IC 25具有第1节点71~第7节点77。自举电容39的第1电极与第1节点71(节点VB)连接。晶体管31的源极与第1节点71连接。晶体管31的漏极与晶体管32的漏极以及第2节点72连接。晶体管32的源极与第3节点73(节点VS)连接。自举电容39的第2电极经由第8节点78与第3节点73连接。作为高压侧功率半导体元件的晶体管36的栅极电极与第2节点72连接。晶体管36的漏极与高电压电源节点70连接。晶体管36的源极与第8节点78连接。

低电位侧电路27的晶体管33的源极与第7节点77(节点VCC)连接。晶体管33的漏极与晶体管34的漏极以及第4节点74连接。晶体管34的源极与第5节点75(节点COM)以及第6节点76(节点COM)连接。作为低压侧功率半导体元件的晶体管35的栅极电极与第4节点74连接。晶体管35的漏极与第8节点78连接。晶体管35的源极经由第9节点79与第5节点75连接。第9节点79接地。

电源38的正极与第7节点77连接。电源38的负极与第6节点76连接。栅极驱动电路37与晶体管30的栅极电极连接。栅极驱动电路37与第6节点76以及第7节点77连接。晶体管30的源极与第7节点77连接。晶体管30的漏极与晶体管31的源极以及第1节点71连接。晶体管30的背栅极电极经由第5节点75接地。

图2示出图1所示的半导体装置的晶体管30以及高电位侧电路26的剖面示意图。如图2所示,半导体装置例如形成于作为第1导电型的P型的半导体基板即半导体层1。在半导体层1的主表面,导电型为N型的N型扩散区域2以及导电型为P型的P型扩散区域3a相邻地形成。N型扩散区域2作为晶体管30的漂移层而有助于电气传导和耐压保持。在P型扩散区域3a的主面形成有P+型扩散区域4a和N型扩散层21。P+型扩散区域4a与N型扩散层21相互隔开间隔而形成。在N型扩散层21的表面的一部分形成有N+型扩散区域5a。N型扩散层21以及N+型扩散区域5a作为晶体管30的源极区域起作用。以夹着P+型扩散区域4a的方式,在半导体层1的主表面形成有由LOCOS氧化膜等构成的隔离绝缘膜14f、14a。隔离绝缘膜14a配置于P+型扩散区域4a与N+型扩散区域5a之间。以夹着N+型扩散区域5a的方式,形成有隔离绝缘膜14a和隔离绝缘膜14b。隔离绝缘膜14b配置于N型扩散层21的与N型扩散区域2侧的端部分离的位置。

在从隔离绝缘膜14b观察时与N+扩散区域5a相反侧的区域,在N型扩散层21、P型扩散区域3a和N型扩散区域2的表面形成有作为晶体管30的栅极绝缘膜的绝缘膜15。在从绝缘膜15观察时与隔离绝缘膜14b相反侧,在N型扩散区域2的表面形成有隔离绝缘膜14c。在该绝缘膜15之上形成有晶体管30的栅极电极9a。栅极电极9a从绝缘膜15之上延伸至隔离绝缘膜14b以及隔离绝缘膜14c的表面之上。晶体管30的背栅极电极10a与P+型扩散区域4a连接。晶体管30的源极电极10b与N+型扩散区域5a连接。源极电极10b与电源38的正极连接。背栅极电极10a接地。

在N型扩散区域2的表面,在从隔离绝缘膜14c观察时与栅极电极9a相反侧形成有N+型扩散区域5b。N+型扩散区域5b与隔离绝缘膜14c隔开间隔而形成。从N+型扩散区域5b的端部之上至隔离绝缘膜14c,在N型扩散区域2的表面之上形成有绝缘膜15。以从绝缘膜15之上延伸至隔离绝缘膜14c之上的方式形成有多晶硅电极9b。多晶硅电极9b作为场板起作用。

晶体管30的漏极电极10c与N+型扩散区域5b连接。漏极电极10c与第1节点71以及自举电容39的第1电极连接。

在高电位侧电路26中,在N型扩散区域2的表面形成有P型扩散区域3b。晶体管31形成于N型扩散区域2的表面。晶体管32形成于P型扩散区域3b的表面。具体而言,在N型扩散区域2的表面形成有P+型扩散区域4b、4c。P+型扩散区域4b配置于夹着隔离绝缘膜14d与N+型扩散区域5b相对的位置。P+型扩散区域4b是晶体管31的源极区域。P+型扩散区域4c与P+型扩散区域4b隔开间隔而配置。P+型扩散区域4c是晶体管31的漏极区域。P+型扩散区域4b与P+型扩散区域4c之间的区域是成为晶体管31的沟道区域的部分。以从P+型扩散区域4b之上延伸至P+型扩散区域4c之上的方式,在N型扩散区域2的表面之上形成有绝缘膜15。位于P+型扩散区域4b与P+型扩散区域4c之间的绝缘膜15作为晶体管31的栅极绝缘膜起作用。在绝缘膜15之上形成有晶体管31的栅极电极9c。

在P型扩散区域3b的表面形成有N+型扩散区域5c、5d。N+型扩散区域5c配置于夹着隔离绝缘膜14e而与P+型扩散区域4c相对的位置。N+型扩散区域5c是晶体管32的漏极区域。N+型扩散区域5d与N+型扩散区域5c隔开间隔而配置。N+型扩散区域5d是晶体管32的源极区域。N+型扩散区域5c与N+型扩散区域5d之间的区域是成为晶体管32的沟道区域的部分。以从N+型扩散区域5c之上延伸至N+型扩散区域5d之上的方式,在P型扩散区域3b的表面之上形成有绝缘膜15。位于N+型扩散区域5c与N+型扩散区域5d之间的绝缘膜15作为晶体管32的栅极绝缘膜起作用。在绝缘膜15之上形成有晶体管32的栅极电极9d。在P型扩散区域3b的表面,以与N+型扩散区域5d相邻的方式形成有P+型扩散区域4d。

晶体管30的漏极电极10c与晶体管31的P+型扩散区域4b电连接。晶体管31的漏极区域即P+型扩散区域4c通过电极10d与晶体管31的N+型扩散区域5c连接。以与N+型扩散区域5d以及P+型扩散区域4d双方连接的方式,形成有电极10e。电极10e与第3节点73以及自举电容39的第2电极电连接。

以将栅极电极9a、9c、9d以及多晶硅电极9b之上覆盖的方式形成有层间绝缘膜11。背栅极电极10a、源极电极10b、漏极电极10c、电极10d、10e的一部分在层间绝缘膜11的上部表面之上延伸。在层间绝缘膜11之上形成有钝化膜12。

就上述半导体装置而言,N型扩散层21构成晶体管30的源极区域的一部分,并且维持大于或等于针对背栅极层即P+型扩散区域4a的电源电压的耐压。此外,能够通过变更N型扩散层21的杂质浓度、N型扩散层21的尺寸等,任意地调整该耐压。

构成上述的背栅极电极10a、源极电极10b、漏极电极10c、电极10d、10e的材料例如是铝(Al)。作为构成这些电极的材料,能够使用其他任意的金属等导电体。另外,作为构成栅极电极9a、9c、9d的材料,例如使用硅。

此外,N型扩散区域2也作为将高电位侧电路26与半导体层1电隔离的阱起作用,但是用于将高电位侧电路26与半导体层1电隔离的结构也可以使用其他结构。例如,也可以通过在高电位侧电路26的正下方导入填埋扩散层,从而将高电位侧电路26与半导体层1电隔离。另外,P型扩散区域3a、3b也能够用作晶体管30、32的背栅极。如图2所示,晶体管30的漏极区域优选与形成高电位侧电路26的N型扩散区域2连续地形成。在该情况下,能够缩小半导体装置的芯片面积。如果不影响半导体装置的耐压,则也可以导入填埋扩散层,经由该填埋扩散层将形成高电位侧电路26的区域的N型扩散区域2与晶体管30的漏极区域电连接。

<半导体装置的作用效果>

本发明所涉及的半导体装置向作为充电对象元件的自举电容39供给充电电流,该半导体装置例如具有:第1导电型(P型)的半导体层1,其是P型基板;作为第2导电型(N型)的第1半导体区域的N+型扩散区域5b以及N型扩散区域2;作为第1导电型的第2半导体区域的P+型扩散区域4a以及P型扩散区域3a;作为第2导电型的第3半导体区域的N+型扩散区域5a;源极电极10b;漏极电极10c;背栅极电极10a;以及栅极电极9a。第1半导体区域(N+型扩散区域5b以及N型扩散区域2)与自举电容39的第1电极电连接。第1半导体区域(N+型扩散区域5b以及N型扩散区域2)形成于半导体层1的主表面。第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)在半导体层1的主表面形成于与第1半导体区域(N型扩散区域2)相邻的位置。电源电压(Vcc)被供给至作为第3半导体区域的N+型扩散区域5a。N+型扩散区域5a形成于第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)的表面。源极电极10b与第3半导体区域(N+型扩散区域5a)连接并且被供给电源电压。漏极电极10c与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)连接并且与自举电容39的第1电极电连接。背栅极电极10a在第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)连接至与作为第3半导体区域的N+型扩散区域5a分离的区域,并且接地。栅极电极9a以隔着作为栅极绝缘膜的绝缘膜15而与沟道区域相对的方式配置,该沟道区域在第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)位于作为第3半导体区域的N+型扩散区域5a与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)之间。源极电极10b与背栅极电极10a之间的耐压大于电源电压。

如果这样,则能够对源极电极10b施加比电源电压(Vcc)高的电压,并且将背栅极电极10a固定为接地电位,因此不需要配置以往那样的用于对源极电极以及背栅极电极的电位进行控制的追加电路,就能够进行向自举电容39的充电动作。即,通过分别对源极电极10b以及背栅极电极10a的电位进行固定,仅对栅极电极9a的电压进行控制,就能够实施向自举电容39的充电动作。其结果,能够简化自举电容39的充电所需的电路的结构,因此能够降低半导体装置的制造成本。

上述半导体装置具有作为第2导电型的第4半导体区域的N型扩散层21。第4半导体区域(N型扩散层21)在第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)将第3半导体区域(N+型扩散区域5a)的周围包围,并且将第3半导体区域(N+型扩散区域5a)与第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)隔离。N型扩散层21从N+型扩散区域5a的周围延伸至在第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)相对并且与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)分离的区域。沟道区域是在第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)位于N型扩散层21与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)之间的区域。

在该情况下,通过形成N型扩散层21,从而使源极电极10b与背栅极电极10a之间的耐压大于电源电压。通过这样的结构,能够实现可进行上述那样的向自举电容39的充电动作的半导体装置。

上述半导体装置的耐压也可以大于或等于300V。此外,这里,耐压是指能够施加于漏极电极10c与源极电极10b之间的最大电压。

在该情况下,能够利用本发明所涉及的半导体装置作为进行功率半导体的栅极驱动的高耐压半导体,其中,该功率半导体对电动机等的电源这样的高压电源进行控制。

一边与作为参考例的半导体装置进行对比,一边对上述本实施方式所涉及的半导体装置的作用效果进行更详细的说明。图3是参考例的半导体装置的自举充电系统的电路图。图4是图3所示的参考例的半导体装置的局部剖面示意图。

图3所示的参考例的半导体装置具有基本上与图1所示的本实施方式所涉及的半导体装置相同的电路结构,但在作为高耐压MOS晶体管的晶体管30的源极电极连接有源极电位控制电路140。另外,背栅极电位控制电路139与晶体管30的背栅极电极连接。另外,在图4中示出图3所示的半导体装置的晶体管30以及高电位侧电路26的剖面示意图。图4所示的参考例的半导体装置具有基本上与图2所示的本实施方式所涉及的半导体装置相同的结构,但晶体管30的结构与图2所示的半导体装置不同。具体而言,就图4所示的半导体装置而言,P型扩散区域6被包含于N型扩散区域2内。在P型扩散区域6的表面隔开间隔而形成有P+型扩散区域4a和N+型扩散区域5a。另外,在半导体层1的主表面,在隔着隔离绝缘膜14a而与P型扩散区域6分离的位置形成有P+型扩散区域4e。背栅极电极10a与P+型扩散区域4a连接。源极电极10b与N+型扩散区域5a连接。电极10f与P+型扩散区域4e连接。如上所述,背栅极电位控制电路139与背栅极电极10a连接。源极电位控制电路140与源极电极10b连接。电极10f接地。

就上述参考例的半导体装置而言,为了防止晶体管30的偶发性的动作而抑制寄生双极元件的动作,设置有上述那样的背栅极电位控制电路139以及源极电位控制电路140。因此,参考例的半导体装置的电路结构复杂,导致制造成本增加。

另一方面,就本实施方式所涉及的半导体装置而言,形成有N型扩散层21,以使得能够向作为源极区域的N+型扩散区域5a施加相对于电源电压(Vcc)足够高的电压。并且,将背栅极电极10a固定为接地电位。因此,无需设置参考例那样的背栅极电位控制电路139以及源极电位控制电路140,而通过简单的电路结构,就能够抑制寄生双极元件动作这一问题的产生。

另外,在晶体管30向自举电容39充电的情况下,在高电位侧电路26的输出为LOW(低)、作为开关元件的晶体管36为截止状态、并且低电位侧电路27的输出为HIGH(高)、作为开关元件的晶体管35为导通状态时,高电位侧电路26转变为低电位。在该状态下,能够进行作为高耐压NchMOS晶体管的晶体管30对自举电容39的充电动作。该可充电期间由分别向充电系统上的高电位侧电路26以及低电位侧电路27的输出命令决定。因此,能够在系统上逻辑性地判别可充电期间。通过将上述逻辑信息发送给晶体管30的栅极驱动电路37,从而能够在最佳定时(timing)进行晶体管30的栅极控制,进行自举电容39的充电动作。

另外,根据本实施方式所涉及的半导体装置,由于晶体管30的背栅极电极10a被固定为接地电位,因此如图2所示,构成背栅极的P型扩散区域3a能够不被包含在构成晶体管30的漏极层的N型扩散区域2内,而是以与半导体层1相接的方式形成。这意味着,排除了在参考例所涉及的半导体装置中成为问题的由背栅极/漏极/半导体层1构成的寄生PNP晶体管。

此外,关于由源极/背栅极/漏极构成的寄生NPN晶体管,就本实施方式所涉及的半导体装置而言,源极-背栅极间始终以电源电压(Vcc)被反向偏置。因此,能够充分抑制在将晶体管30的源极作为NPN晶体管的发射极的状态(即晶体管30的漏极侧成为高电位状态而作为集电极工作的状态)下的寄生动作。其结果,能够降低因该寄生动作而使半导体装置损坏的风险。此外,相反方向的动作即在晶体管30的漏极成为NPN晶体管的发射极的状态下的寄生动作,对应于向自举电容39的充电动作,因此没有问题。另外,如果晶体管30的漏极电极的电位变成至少大于或等于电源电压(Vcc),则该充电动作自动结束。

这样,就本实施方式所涉及的半导体装置而言,能够简化系统结构,同时能够实现寄生双极晶体管构造的排除和寄生动作的抑制。其结果,能够实现半导体装置的低成本化以及可靠性的提高(稳健性的提高)。

实施方式2.

<半导体装置的结构>

图5是实施方式2所涉及的半导体装置的自举充电系统的电路图。图6是图5所示的半导体装置的局部剖面示意图。图6示出了半导体装置的晶体管30的局部剖面示意图。

图5以及图6所示的半导体装置具有基本上与图1以及图2所示的半导体装置相同的结构,但在晶体管30的源极连接有限制电阻41这一点上与图1以及图2所示的半导体装置不同。

根据图5可知,晶体管30的源极经由限制电阻41而与第7节点77连接。作为限制电阻41的结构,能够采用任意的结构。例如,如图6所示,以使得N+型扩散区域5a与栅极电极9a之下的沟道区域之间的距离L1相对变长的方式,变更N型扩散层21的平面形状。其结果,位于连接有源极电极10b的N+型扩散区域5a与栅极电极9a之下的沟道区域之间的N型扩散层21作为限制电阻起作用。此外,限制电阻的电阻值能够通过变更N型扩散层21的杂质浓度以及N型扩散层21的形状来调整。这样的限制电阻具有如下效果,即,抑制当在半导体装置中寄生NPN晶体管进行了动作的情况下突入电流从晶体管30的源极流至漏极时自举电容39或者构成半导体装置的元件的损坏。

<半导体装置的作用效果>

本实施方式所涉及的半导体装置也可以还具有限制电阻41。限制电阻41配置于从电源电压(Vcc)的供给源即电源38至沟道区域的电流路径上。

在该情况下,通过具有限制电阻41,从而即使半导体装置中寄生NPN晶体管进行了动作时从源极电极10b侧向漏极电极10c侧产生突入电流,也能够降低由于该突入电流而使自举电容39等损坏的可能性。

就上述半导体装置而言,限制电阻41也可以是作为第4半导体区域的N型扩散层21的位于作为第3半导体区域的N+型扩散区域5a与沟道区域之间的部分。在该情况下,通过对N型扩散层21的形状、杂质浓度等进行调整,能够容易地实现限制电阻41。

这里,在应用了本实施方式所涉及的半导体装置的功率级驱动电路中,将大电流供给至电动机等具有大电感的负载。因此,开关元件的中间连接点即第3节点73(VS)的电位有时由于电感的浪涌的影响而成为负电位。在该情况下,如果第3节点73的电压值变成小于或等于(第1节点71的电位(VB)-第3节点的电位(VS))的负电压值,则第1节点71的电位也被偏置为负电压。其结果,晶体管30的漏极成为负电位,可能会诱发寄生NPN晶体管的动作。

具体而言,晶体管30的漏极成为发射极,半导体层1以及晶体管30的背栅极相对于漏极被正向偏置,向漏极(发射极)注入空穴,因此作为基极起作用。而且,源极作为寄生NPN晶体管的集电极向发射极(漏极)注入电子。由于基本上双极晶体管的动作是低阻抗,因此从晶体管30的源极至漏极产生突入电流,有可能损坏自举电容39等构成半导体装置的元件。但是,通过如图5以及图6所示地构成N型扩散层21,从而能够对晶体管30的源极赋予适度的电阻。其结果,能够使N型扩散层21发挥在寄生NPN晶体管进行了动作时的限制电阻的作用。

实施方式3.

<半导体装置的结构>

图7是实施方式3所涉及的半导体装置的局部平面示意图。图8是图7的线段VIII-VIII处的剖面示意图。图9是图7的线段IX-IX处的剖面示意图。图7~图9所示的半导体装置具有基本上与图1以及图2所示的半导体装置相同的结构,但晶体管30的栅极的结构以及维持相对于背栅极来说的源极的耐压的构造不同。

即,就图7~图9所示的半导体装置而言,晶体管30具有沟槽栅极构造。具体而言,以将成为晶体管30的源极区域的N+型扩散区域5a包围的方式形成有槽51。P型扩散区域3a包含位于槽51的外部的第1区域3aa和位于槽51的内部的第2区域3ab。在槽51的内部,第2区域3ab以与N+型扩散区域5a之下相接的方式配置。第1区域3aa以与P+型扩散区域4a之下相接的方式配置。P型扩散区域6从第1区域3aa之下延伸至槽51内部的第2区域3ab的一部分之下。另外,N型扩散区域2经由槽51的一部分51a的下侧延伸至槽51的内部。经由槽51的另一部分51b的下侧延伸至槽51内部的P型扩散区域6在槽51内部与N型扩散区域2相接。为了将P型扩散区域3a的第2区域3ab固定为接地电位,P型扩散区域6在槽51的内侧与第2区域3ab相接。N型扩散区域2在槽51的内部与P型扩散区域3a的第2区域3ab相接。在槽51的内壁之上形成有应成为栅极绝缘膜的绝缘膜15。在绝缘膜15之上形成有栅极电极9a。在第2区域3ab,面向槽51的一部分51a的区域成为晶体管30的沟道区域。栅极电极9a以将槽51的内部填充的方式形成。槽51从半导体层1的主表面延伸至P型扩散区域6或者N型扩散区域2中的与第2区域3ab的下表面相比的下侧。

此外,在隔离绝缘膜14c,在槽51侧的区域之上以及与该槽51侧相反侧的区域配置有由导电体膜构成的场板20。

<半导体装置的作用效果>

就本实施方式所涉及的半导体装置而言,在半导体层1的主表面形成槽51。槽51的一部分51a对沟道区域与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)进行划分。在槽的一部分51a,在面向沟道区域的内壁面之上形成有应成为栅极绝缘膜的绝缘膜15。栅极电极9a形成于槽51的内部。槽51从半导体层1的主表面到达与第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)的底部相比的下方。槽51的另一部分51b形成于背栅极电极10a与源极电极10b之间的区域。第2半导体区域(P型扩散区域3a)包含第1区域3aa和第2区域3ab。第1区域3aa与槽51的另一部分51b相比位于背栅极电极10a侧。第2区域3ab与槽51的另一部分51b相比位于源极电极10b侧,包含沟道区域。第1半导体区域(N型扩散区域2)以经由位于槽51的一部分51a下侧的区域而与沟道区域相接的方式延伸。半导体装置还具有第1导电型(P型)的延伸区域(P型扩散区域6)。作为延伸区域的P型扩散区域6在半导体层1以与第1区域3aa和第2区域3ab接触的方式形成。P型扩散区域6经由位于槽51的另一部分51b下侧的区域,从第1区域3aa之下延伸至第2区域3ab之下。

在该情况下,能够通过形成利用了槽51的所谓沟槽栅极构造,从而提高源极电极10b与背栅极电极10a之间的耐压,使源极电极10b与背栅极电极10a之间的耐压大于电源电压(Vcc)。

就上述半导体装置而言,槽51也可以在半导体层1的主表面以包围第3半导体区域(N+型扩散区域5a)的方式形成。在该情况下,能够将源极电极10b所连接的N+型扩散区域5a与周围的区域隔离,因此能够在形成有高耐压NchMOS晶体管30的区域配置具有与自举电路不同功能的元件。

这里,就实施方式1所示的半导体装置的构造而言,为了提高源极区域相对于背栅极的耐压而形成了N型扩散层21。在该情况下,为了防止由于N型扩散层21的端部的弯曲部处的电场集中而引起的耐压降低,通常需要引入深的扩散层,或者将与背栅极电连接的P型扩散区域3a设为低浓度等对策。如果没有适当的构造设计,则这些应对会使寄生NPN晶体管的电流增益增加,结果有可能降低半导体装置的可靠性。

因此,在本实施方式中,为了提高源极与背栅极之间的耐压,将成为源极区域的N+型扩散区域5a形成于沟槽栅极构造的槽51的内侧。其结果,能够消除图2所示的N型扩散层21的弯曲部,降低由于电场集中而引起的耐压降低的可能性。另外,如图8所示,就源极与背栅极之间的结而言,槽51的内侧的N+型扩散区域5a的下部与P型扩散区域的第2区域3ab的上部的一维结成为主要结部。并且,槽51内部的栅极电极9a作为场板使耗尽层进行延伸,具有缓和电场的效果。因此,在与槽51相接的区域,耐压提高。因此,源极与背栅极之间的耐压不会由图2所示的N型扩散层21的端部等边界部决定。其结果,就半导体装置而言,能够提高耐压,并且得到稳定的耐压。

实施方式4.

<半导体装置的结构>

图10是实施方式4所涉及的半导体装置的局部平面示意图。图11是图10的线段XI-XI处的剖面示意图。图12是图10的线段XII-XII处的剖面示意图。图10~图12所示的半导体装置具有基本上与图7~图9所示的半导体装置相同的结构,但P型扩散区域3a的构造与图7~图9所示的半导体装置不同。即,就图10~图12所示的半导体装置而言,从槽51观察,P型扩散区域3a局部地延伸至隔离绝缘膜14c侧。P型扩散区域3a包含:位于P+型扩散区域4a之下的第1区域3aa;位于N+型扩散区域5a之下且位于槽51内侧的第2区域3ab;与槽51相比位于隔离绝缘膜14c侧的第3区域3ac;以及以将第1区域3aa与第3区域3ac连接的方式将槽51的外周围绕的第4区域3ad。如图10所示,槽51沿P型扩散区域3a与N型扩散区域2的边界部隔开间隔而形成有多个。在多个槽51之间配置有第4区域3ad。第3区域3ac与N型扩散区域2相接。第3区域3ac从槽51的表面延伸至隔离绝缘膜14c。

<半导体装置的作用效果>

就本实施方式所涉及的半导体装置而言,第2半导体区域(P+型扩散区域4a以及P型扩散区域3a)还包含第3区域3ac和第4区域3ad。从槽51的一部分51a观察,第3区域3ac位于与第2区域3ab侧相反侧。第4区域3ad位于槽51的外侧,将第1区域3aa与第3区域3ac连接。

在该情况下,由于通过第4区域3ad将第1区域3aa与第3区域3ac连接,因此结果是第3区域3ac成为接地电位。因此,促进了与第3区域3ac相邻的N型扩散区域2的耗尽化。其结果,能够实现半导体装置的耐压的提高以及稳定性的提高。

实施方式5.

<半导体装置的结构>

图13是实施方式5所涉及的半导体装置的电位检测电路的电路图。图14是安装有图13所示的电路的半导体装置的局部平面示意图。图15是图14的线段XV-XV处的剖面示意图。图16是图14的线段XVI-XVI处的剖面示意图。图17是图14的线段XVII-XVII处的剖面示意图。图18是图14的线段XVIII-XVIII处的剖面示意图。

图13~18所示的半导体装置具有基本上与图1以及图2所示的半导体装置相同的结构,但具有判定电路80,该判定电路80用于对与自举电容39的第1电极连接的第1节点71的电位进行判定。判定电路80主要包含第1充电电路81、第2充电电路82、第1开关元件83、第2开关元件84、第3开关元件85、比较器62、和栅极控制电路61。第1充电电路81包含第1电容81a、第1充电电路节点81b、第1电阻81c和第1二极管81d。第1电容81a具有2个电极。第1电容81a的一个电极接地。第1电容81a的另一个电极与第1充电电路节点81b电连接。第1二极管81d与第1电容81a并联连接。

第2充电电路82包含第2电容82a、第2充电电路节点82b、第2电阻82c和第2二极管82d。第2电容82a具有2个电极。第2电容82a的一个电极接地。第2电容82a的另一个电极与第2充电电路节点82b电连接。第2二极管82d与第2电容82a并联连接。

第1开关元件83的源极与作为电源电压(Vcc)的供给源的第7节点77连接。第1开关元件83的漏极与第1充电电路节点81b连接。第1充电电路节点81b与比较器62连接。

第2开关元件84的源极与作为电源电压(Vcc)的供给源的第7节点77连接。第2开关元件84的漏极与第2充电电路节点82b连接。第2充电电路节点82b与比较器62连接。另外,第2充电电路节点82b与第3开关元件85的源极连接。第3开关元件85的漏极与第1节点71连接。晶体管30的漏极与第1节点71连接。晶体管30的源极与第7节点77连接。晶体管30、第1开关元件83、第2开关元件84以及第3开关元件85各自的栅极电极与栅极控制电路61连接。比较器62的输出被输入至栅极控制电路61。

电源电压(Vcc)经由第1开关元件83供给至第1充电电路节点81b。电源电压(Vcc)经由第2开关元件84供给至第2充电电路节点82b。第1电容81a与第2电容82a具有相同的电容量。第2充电电路节点82b经由第3开关元件85而与第1节点71连接。在第2充电电路节点82b的电压高于第1充电电路节点81b的电压的情况下,判定电路80判定为第1节点71的电压高于电源电压(Vcc)。

图14示出了安装有图13所示的电路的半导体装置的平面布局。在图14中,示出了晶体管30、第1开关元件83、第2开关元件84以及第3开关元件85的成为栅极电极的电极层、和成为源极区域或者漏极区域的N+型扩散区域5a、5f、5g的平面形状。上述晶体管30等沿N型扩散区域2与P型扩散区域3a的边界部而配置。具体而言,以沿该边界部延伸的方式在P型扩散区域3a的表面形成有N+型扩散区域5a。在沿上述边界部与N+型扩散区域5a隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5f。N+型扩散区域5f向远离上述边界部的方向延伸。在沿上述边界部与N+型扩散区域5f隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5g。N+型扩散区域5g向远离上述边界部的方向延伸。即,N+型扩散区域5f与N+型扩散区域5g以大致平行地延伸的方式形成。在沿上述边界部与N+型扩散区域5g隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5a。N+型扩散区域5a沿上述边界部延伸。

从与N+型扩散区域5a相邻的位置起通过P型扩散区域3a的表面之上而直至N型扩散区域2之上,形成有栅极电极9g。在栅极电极9g之下配置有成为栅极绝缘膜的绝缘膜15。沿上述边界部与栅极电极9g隔开间隔而形成有第1电极层9e。在第1电极层9e之下形成有应成为栅极绝缘膜的绝缘膜15。第1电极层9e以与N+型扩散区域5a相邻并且将N+型扩散区域5f的一部分覆盖的方式配置。第1电极层9e从P型扩散区域3a之上起越过上述边界部而延伸至N型扩散区域2之上。

沿上述边界部与第1电极层9e隔开间隔而形成有第2电极层9f。在第2电极层9f之下形成有应成为栅极绝缘膜的绝缘膜15。第2电极层9f以与其他N+型扩散区域5a相邻,并且将N+型扩散区域5g的一部分覆盖的方式配置。第2电极层9f仅形成于P型扩散区域3a之上。第2电极层9f配置于与上述边界部隔开距离的位置。从与其他N+型扩散区域5a相邻的位置起通过P型扩散区域3a的表面之上而直至N型扩散区域2之上,形成有栅极电极9h。在栅极电极9h之下配置有成为栅极绝缘膜的绝缘膜15。

如图14所示,在N+型扩散区域5a与N型扩散区域2之间配置晶体管30的栅极电极9g。另外,位于N+型扩散区域5a与N型扩散区域2之间的第1电极层9e的部分成为晶体管30的栅极电极。另外,位于N+型扩散区域5a与N+型扩散区域5f之间的第1电极层9e的部分成为第2开关元件84的栅极电极。位于N+型扩散区域5f与N型扩散区域2之间的第1电极层9e的部分成为第3开关元件85的栅极电极。位于其他N+型扩散区域5a与N+型扩散区域5g之间的第2电极层9f的部分成为第1开关元件83的栅极电极。在其他N+型扩散区域5a与N型扩散区域2之间配置晶体管30的栅极电极9g。

<半导体装置的作用效果>

本实施方式所涉及的半导体装置具有判定电路80。判定电路80对自举电容39的第1电极与第1半导体区域(N+型扩散区域5b以及N型扩散区域2)之间的电流路径上的第1节点71处的电压是否大于电源电压(Vcc)进行判定。判定电路80包含第1充电电路81、第2充电电路82、第1开关元件83、第2开关元件84、和第3开关元件85。第1充电电路81包含第1电容81a和第1充电电路节点81b。第1电容81a具有2个电极。第1电容81a的一个电极接地。第1电容81a的另一个电极与第1充电电路节点81b电连接。

第2充电电路82包含第2电容82a和第2充电电路节点82b。第2电容82a具有2个电极。第2电容82a的一个电极接地。第2电容82a的另一个电极与第2充电电路节点82b电连接。电源电压(Vcc)经由第1开关元件83供给至第1充电电路节点81b。电源电压(Vcc)经由第2开关元件84供给至第2充电电路节点82b。第1电容81a与第2电容82a具有相同的电容量。第2充电电路节点82b经由第3开关元件85与第1节点71连接。第1充电电路81与第2充电电路82优选彼此具有相同的电气特性。另外,第1开关元件83与第2开关元件84优选彼此具有相同的电气特性。在第2充电电路节点82b的电压高于第1充电电路节点81b的电压的情况下,判定电路80判定为第1节点71的电压高于电源电压(Vcc)。

在该情况下,由于能够通过上述判定电路80对第1节点71的电压是否高于电源电压进行判定,因此能够基于该判定结果对向自举电容39的充电动作的实施/停止进行切换。

这里,在上述的各实施方式所涉及的半导体装置所包含的自举充电系统中,优选在第1节点71的电位(VB)大于第3节点73的电位(VS)或者电源电压(Vcc)的期间,可靠地停止自举电容39的充电动作。因此,优选能够在低电位侧间接地对第1节点71的电位(VB)进行监测。

这里,在图13所示的判定电路80中,使用相同特性的开关元件作为第1开关元件83以及第2开关元件84。另外,使用相同电阻值的电阻作为第1电阻81c以及第2电阻82c。使用相同电容值的元件作为第1电容81a以及第2电容82a。使用相同特性的二极管作为第1二极管81d以及第2二极管82d。这样构成2个充电电路。而且,将这些节点与比较器62连接,以使得能够对各个第1充电电路节点81b以及第2充电电路节点82b的电压进行监测。如图13所示,与晶体管30相同地,作为高耐压MOST晶体管的第3开关元件85的源极与第2充电电路节点82b连接。第3开关元件85的漏极与第1节点71连接。另一方面,在第1充电电路节点81b,如图17的剖面图所示,以使得成为高耐压NchMOS晶体管的栅极电极的第2电极层9f之下的P型扩散区域3a的表面层不形成沟道的方式,构成为在第2电极层9f与第1电极层9e之间具有间隙。电源电压(Vcc)被施加于第1开关元件83以及第2开关元件84的源极,这些元件由栅极控制电路61驱动。

在第1开关元件83以及第2开关元件84的栅极是导通状态的情况下,流过第1开关元件83以及第2开关元件84的电流经由第1电阻81c以及第2电阻82c向第1电容81a以及第2电容82a充电。此时,在第2开关元件84侧,第3开关元件85也是导通状态。因此,在第1节点71的电位(VB)小于电源电压(Vcc)的情况下,第2开关元件84的电流的一部分经由第3开关元件85流向第1节点71侧。其结果,流过第2电阻82c的电流小于流过第1电阻81c的电流,第1充电电路节点81b的电位(V1)大于第2充电电路节点82b的电位(V2)这一关系成立。

在第1节点71的电位(VB)大于电源电压(Vcc)并且第2充电电路节点82b的电位(V2)小于电源电压(Vcc)的情况下,来自第2开关元件84以及第3开关元件85双方的电流流过第2电阻82c。在该情况下,第1充电电路节点81b的电位(V1)小于第2充电电路节点82b的电位(V2)这一关系成立。由于第1充电电路节点81b的电位(V1)小于或等于电源电压(Vcc),因此,即使第2充电电路节点82b的电位(V2)上升而大于电源电压(Vcc),第1充电电路节点81b的电位(V1)小于第2充电电路节点82b的电位(V2)这一关系也成立。

通过由比较器62对第1充电电路节点81b的电位(V1)与第2充电电路节点82b的电位(V2)进行比较,能够对第1节点71的电位(VB)大于或等于电源电压(Vcc)这一情况进行检测。通过将该结果向栅极控制电路61进行反馈,从而将第1开关元件83、第2开关元件84以及第3开关元件85的栅极设置为截止,由此能够使经由第1节点71的自举电容39的充电动作停止。在该判定电路80中,为了进一步提高检测精度,也能够将电源电压(Vcc)作为第1充电电路节点81b的电位(V1)以及第2充电电路节点82b的电位(V2)的参考而输入至比较器62。

实施方式6.

<半导体装置的结构>

图19是实施方式6所涉及的半导体装置的局部平面示意图。图20是图19的线段XX-XX处的剖面示意图。图21是图19的线段XXI-XXI处的剖面示意图。图22是图19的线段XXII-XXII处的剖面示意图。

图19~图22所示的半导体装置具有基本上与图13~图18所示的半导体层相同的结构,但构成各开关元件等的N+型扩散区域5h、5i、5j、第1电极层9e以及第2电极层9f的平面形状与图13~图18所示的半导体装置不同。

在图19中,与图14相同地,示出了晶体管30、第1开关元件83、第2开关元件84以及第3开关元件85的成为栅极电极的电极层、和成为源极区域或者漏极区域的N+型扩散区域5a、5h、5i、5j、5k的平面形状。具体而言,以沿N型扩散区域2与P型扩散区域3a的边界部延伸的方式,在P型扩散区域3a的表面形成有N+型扩散区域5a。在沿上述边界部与N+型扩散区域5a隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5h。N+型扩散区域5h包含沿上述边界部延伸的第1部分5ha、和与第1部分5ha相连并向远离边界部的方向延伸的第2部分5hb。在从第1部分5ha观察时与边界部相反侧的区域,形成有N+型扩散区域5j。

在沿上述边界部与N+型扩散区域5h隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5i。N+型扩散区域5i包含沿上述边界部延伸的第1部分5ia、和与第1部分5ia相连并向远离边界部的方向延伸的第2部分5ib。在从第1部分5ia观察时与边界部相反侧的区域,形成有N+型扩散区域5k。N+型扩散区域5h、5j的平面形状与N+型扩散区域5i、5k的平面形状,以位于第2部分5hb与第2部分5ib之间且与第2部分5hb平行地延伸的中心线为中心呈线对称。在沿上述边界部与N+型扩散区域5i隔开间隔的位置,在P型扩散区域3a的表面形成有N+型扩散区域5a。N+型扩散区域5a沿上述边界部延伸。

从与N+型扩散区域5a相邻的位置起通过P型扩散区域3a的表面之上而直至N型扩散区域2之上形成有栅极电极9g。在栅极电极9g之下配置有成为栅极绝缘膜的绝缘膜15。沿上述边界部与栅极电极9g隔开间隔而形成有第1电极层9e。在第1电极层9e之下形成有应成为栅极绝缘膜的绝缘膜15。第1电极层9e以与N+型扩散区域5j相邻并且将N+型扩散区域5h的第1部分5ha覆盖的方式配置。第1电极层9e从P型扩散区域3a之上起越过上述边界部而延伸至N型扩散区域2之上。在俯视观察时,N+型扩散区域5h以将第1电极层9e划分为N+型扩散区域5j侧的第1电极部分9ea和N型扩散区域2侧的第2电极部分9eb的方式形成。

沿上述边界部与第1电极层9e隔开间隔而形成有第2电极层9f。在第2电极层9f之下形成有应成为栅极绝缘膜的绝缘膜15。第2电极层9f以与其他N+型扩散区域5a相邻并且将N+型扩散区域5g的一部分覆盖的方式配置。第2电极层9f仅形成于P型扩散区域3a之上。第2电极层9f配置于与上述边界部隔开距离的位置。从与其他N+型扩散区域5a相邻的位置起通过P型扩散区域3a的表面之上而直至N型扩散区域2之上,形成有栅极电极9g。在栅极电极9g之下配置有成为栅极绝缘膜的绝缘膜15。

如图19所示,在N+型扩散区域5a与N型扩散区域2之间配置晶体管30的栅极电极9g。另外,位于N+型扩散区域5j与N+型扩散区域5h的第1部分5ha之间的第1电极层9e的部分成为第2开关元件84的栅极电极。另外,位于N+型扩散区域5h的第1部分5ha与N型扩散区域2之间的第1电极层9e的部分成为第3开关元件85的栅极电极。位于N+型扩散区域5k和N+型扩散区域5i的第1部分5ia之间的第2电极层9f的部分成为第1开关元件83的栅极电极。在其他N+型扩散区域5a与N型扩散区域2之间配置晶体管30的栅极电极9g。

<半导体装置的作用效果>

本实施方式所涉及的半导体装置具有第2导电型的第5半导体区域(N+型扩散区域5j)、第2导电型的第6半导体区域(N+型扩散区域5h)、第2导电型的第7半导体区域(N+型扩散区域5k)、和第2导电型的第8半导体区域(N+型扩散区域5i)。第5半导体区域(N+型扩散区域5j)在第2半导体区域(P型扩散区域3a)形成于与第3半导体区域(N+型扩散区域5a)分离的区域。第6半导体区域(N+型扩散区域5h)在第2半导体区域(P型扩散区域3a)与第5半导体区域(N+型扩散区域5j)隔开间隔而形成。第7半导体区域(N+型扩散区域5k)在第2半导体区域(P型扩散区域3a)形成于与第5半导体区域(N+型扩散区域5j)分离的区域。第8半导体区域(N+型扩散区域5i)在第2半导体区域(P型扩散区域3a)与第7半导体区域(N+型扩散区域5k)隔开间隔而形成。第6半导体区域(N+型扩散区域5h)包含第1部分5ha,该第1部分5ha从第5半导体区域(N+型扩散区域5j)观察时位于第1半导体区域(N型扩散区域2)侧并且形成于与第1半导体区域(N型扩散区域2)分离的位置。半导体装置还具有第1电极层9e和第2电极层9f。第1电极层9e从第5半导体区域(N+型扩散区域5j)与第1部分5ha之间的区域之上起经由第1部分5ha之上而延伸至第1半导体区域(N型扩散区域2)之上,隔着第1绝缘膜(绝缘膜15)配置。第2电极层9f从第7半导体区域(N+型扩散区域5k)与第8半导体区域(N+型扩散区域5i)之间的区域之上起延伸至第8半导体区域(N+型扩散区域5i)之上,隔着第2绝缘膜(绝缘膜15)配置。第2电极层9f配置于与第1半导体区域(N型扩散区域2)和第2半导体区域(P型扩散区域3a)的边界部分离的位置。在俯视观察时,第6半导体区域(N+型扩散区域5h)以将第1电极层9e划分为第5半导体区域(N+型扩散区域5j)侧的第1电极部分9ea和所述第1半导体区域(N型扩散区域2)侧的第2电极部分9eb的方式形成。第5半导体区域(N+型扩散区域5j)是第2开关元件84的源极区域。第1部分5ha是第2开关元件84的漏极区域并且是第3开关元件85的源极区域。第1半导体区域(N型扩散区域2)是第3开关元件85的漏极区域。第1电极层9e的第1电极部分9ea是第2开关元件84的栅极电极。第1电极层9e的第2电极部分9eb是第3开关元件85的栅极电极。第7半导体区域(N+型扩散区域5k)是第1开关元件83的源极区域。第8半导体区域(N+型扩散区域5i)是第1开关元件83的漏极区域。第2电极层9f是第1开关元件83的栅极电极。

在该情况下,由于N+型扩散区域5h以将第1电极层9e划分为第5半导体区域(N+型扩散区域5j)侧的第1电极部分9ea和所述第1半导体区域(N型扩散区域2)侧的第2电极部分9eb的方式形成,因此能够抑制第5半导体区域(N+型扩散区域5j)作为第3开关元件85的源极区域起作用。

如果从不同的观点来说,N+型扩散区域5h以包围N+型扩散区域5j的方式布局。通过采取该布局,能够使作为第2开关元件84的源极的N+型扩散区域5j尽量不作为第3开关元件85的源极发挥作用。此外,关于第2电极层9f,与图14所示的半导体装置相同地,在与第1电极层9e之间形成有间隔,在N+型扩散区域5i的第1部分5ia与N型扩散区域2之间使高耐压NchMOS晶体管不动作。通过采取这样的布局,能够抑制由电路图中没有的寄生MOS构造引起的电流。其结果,能够使判定电路80中的对第1节点71的电位(VB)进行检测的输出信号电压的产生变得稳定,抑制该判定电路80的误动作。

实施方式7.

<半导体装置的结构>

图23是实施方式7所涉及的半导体装置的电位检测电路的电路图。图23所示的半导体装置具有基本上与图13所示的半导体装置相同的结构,但判定电路80的第1充电电路81以及第2充电电路82的结构与图13所示的半导体装置不同。即,就图23所示的半导体装置而言,第1充电电路81包含第4开关元件81e,第2充电电路82包含第5开关元件82e。第4开关元件81e与第1电容81a并联连接。第5开关元件82e与第2电容82a并联连接。

<半导体装置的作用效果>

本实施方式所涉及的半导体装置具有第4开关元件81e和第5开关元件82e。第4开关元件81e与第1电容81a并联连接。第5开关元件82e与第2电容82a并联连接。在第1开关元件83以及第2开关元件84为断开状态时,第4开关元件81e以及第5开关元件82e成为接通状态,第1电容81a以及第2电容82a被放电。

在该情况下,通过对第4开关元件81e以及第5开关元件82e进行控制,从而能够使第1充电电路81的第1电容81a以及第2充电电路82的第2电容82a可靠地放电而重置为初始状态。

这里,就图13所示的半导体装置的判定电路80而言,第1电容81a以及第2电容82a的状态受到上一次的充电期间刚刚结束后、之后的放电的影响。因此,有可能每次充电动作时的第1电容81a以及第2电容82a的初始状态不同。因此,与针对图13所示的半导体装置设想的电路动作不同,例如,如果第2充电电路节点82b的电位(V2)在初始状态下大于第1充电电路节点81b的电位(V1),则立即判定为第1节点71的电位(VB)大于电源电压(Vcc),充电动作有可能停止。

因此,如图23所示的半导体装置那样,如果第1充电电路81包含第4开关元件81e,第2充电电路82包含第5开关元件82e,则在判定电路80中,能够使第1电容81a以及第2电容82a的电压(VC1以及VC2)稳定。其结果,稳定了判定电路80的动作。例如,在进行充电动作的第1开关元件83以及第2开关元件84的栅极截止期间,使第4开关元件81e以及第5开关元件82e的栅极导通。如果这样,就能够释放第1电容81a以及第2电容82a的残留电荷,将这些电容重置为初始状态。其结果,能够防止判定电路80中的误动作。

对本发明的实施方式进行了说明,但应理解为本次公开的实施方式在所有方面均为例示,并不是限制性内容。本发明的范围通过权利要求书示出,意在包含与权利要求书等同的含义以及范围内的所有变更。

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置