一种优化电流舵DAC的sigma-delta ADC调制器及电子设备

文献发布时间:2023-06-19 11:06:50

【技术领域】

本发明涉及集成电路技术领域,特别是涉及一种优化电流舵DAC的sigma-deltaADC调制器及电子设备。

【背景技术】

创新是中国经济高质量发展的关键词,面对国内外的大环境,新一轮科技革命和产业变革都在加速演变,科技自强已经成为促进发展的“支撑点”,创新解决“卡脖子”问题变得尤为重要。

在电子科技领域中,模数转换器(Analog-to-Digital Converter,简称ADC)在现实世界和数字世界中已经成为不可或缺的媒介,尤其在通信系统中,ADC是连接模拟模块和数字基带的重要模块,它的性能要求随着通信系统的发展不断提高。采用过采样和噪声整形技术,Sigma-delta ADC因结构简单且元件匹配度依赖低等优点,具有低功耗高信噪比的性能,方便与数字电路集成,成为了ADC设计的重要研究方向。

现有技术的Sigma-delta ADC系统包括电性连接的多级积分器,量化器,校正模块,延时DAC模块,主要采用过采样技术采样信号,经过调制器,使量化噪声分布更广,并且输出一位一位的数据位流。而积分器的内部电路结构绝大多数采用折叠套筒式的运算放大器(Operational Transconductance Amplifier,简称OTA)和电流舵数模转换器(Digital-to-Analog Converter,简称DAC)。经过研究发现,电流舵DAC直接由sigma-delta ADC的数字输出控制,其开关切换及共模电平的波动会导致DAC上电流波动,加上输出阻抗不够导致电流线性度低,同时,ADC频率始终较高,引入DAC的杂散信号频率也很高,从而带来高频杂散信号和噪声的影响。

因此,有必要提供一种优化电流舵DAC的sigma-delta ADC调制器及电子设备以解决现有技术问题。

【发明内容】

为了解决上述技术问题,本发明的目的在于提供一种优化电流舵DAC的sigma-delta ADC调制器及电子设备。

本发明的技术方案如下:一种优化电流舵DAC的sigma-delta ADC调制器,包括电流舵DAC,该电流舵DAC包括共源共栅电路,其内包括至少一个晶体管,所述电流舵DAC进一步包括第二电阻和第二调节模块,所述共源共栅电路包括第十二晶体管,所述第十二晶体管的源极与所述第二电阻的第一端连接,所述第二电阻的第二端接地,所述第二调节模块与所述第二电阻并联。

在一些实施例中,所述第二调节模块包括至少一个调节电容,所述调节电容的第一端与所述第十二晶体管的源极和所述第二电阻的第一端均连接,所述调节电容的第二端与所述第二电阻的第二端均接地形成并联连接。

在一些实施例中,所述第二调节模块包括一个第三调节电容,所述第三调节电容的第一端与所述第十二晶体管的源极和所述第二电阻的第一端均连接,所述第三调节电容的第二端与所述第二电阻的第二端均接地形成并联连接。

在一些实施例中,所述共源共栅电路包括第十三晶体管,所述第十三晶体管的源极和所述第十二晶体管的漏极连接。

在一些实施例中,所述第十二晶体管和所述第十三晶体管均为NMOS管。

一种电子设备,包括存储器和微处理器,所述存储器用于存储一个或多个程序,所述微处理器执行一个或多个程序,以控制上述的优化电流舵DAC的sigma-delta ADC调制器。

与现有技术相比,本发明的有益效果在于:

1、电流舵DAC包括共源共栅电路,其内包括至少一个晶体管,该电流舵DAC进一步包括第二电阻和第二调节模块,该共源共栅电路包括第十二晶体管,第十二晶体管的源极与第二电阻的第一端连接,第二电阻的第二端接地,第二调节模块与第二电阻并联。第二调节模块包括至少一个调节电容,且调节电容均与第二电阻并联。具体地,第二调节模块包括一个第三调节电容,第三调节电容的第一端与第十二晶体管的源极连接,第三调节电容的第二端接地。因此,第二调节模块与第二电阻构成滤波网络,提高电流舵DAC线性度,减少了电路的面积代价,也抑制了高频杂散信号和噪声的影响。另外,提供了较高的对地阻抗,优化了电流舵DAC对晶体管二级效应的抵抗。

2、一种电子设备,包括存储器和微处理器,所述存储器用于存储一个或多个程序,所述微处理器执行一个或多个程序,以控制上述优化电流舵DAC的sigma-delta ADC调制器。因此,所述电子设备也具有与上述的sigma-delta ADC调制器相同的有益效果,在此不再赘述。

【附图说明】

图1为Sigma-delta ADC调制器的电路框图;

图2为Sigma-delta ADC调制器中积分器的电路结构示意图;

图3为Sigma-delta ADC调制器中延时DAC模块的电路结构示意图;

图4为本发明第一实施例的折叠套筒式OTA的电路结构示意图;

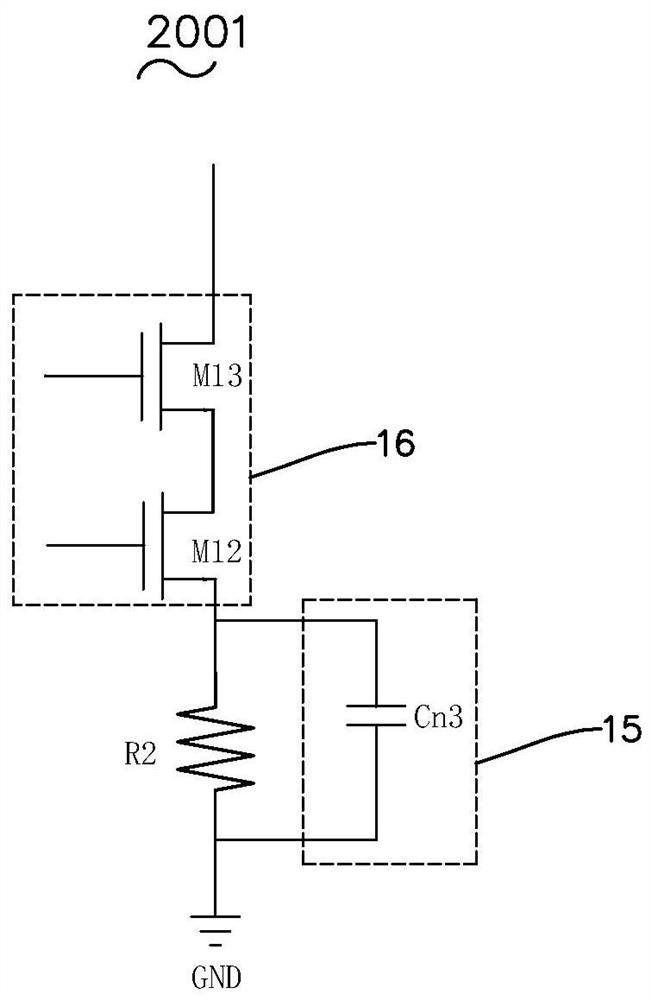

图5为本发明第二实施例的电流舵DAC的电路结构示意图;

图6为本发明第三实施例的电子设备模块示意图。

附图标记说明:

M1、第一晶体管;M2、第二晶体管;M3、第三晶体管;M4、第四晶体管;M5、第五晶体管;M6、第六晶体管;M7、第七晶体管;M8、第八晶体管;M9、第九晶体管;M10、第十晶体管;M11、第十一晶体管;M12、第十二晶体管;M13、第十三晶体管;R1、第一电阻;R2、第二电阻;C1、第一电容;C

【具体实施方式】

下面结合附图和实施方式对本发明作进一步说明。以使本发明的优点和特征能更易于被本领域技术人员理解,从而对本发明的保护范围做出更为清楚明确的界定。显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所得到的所有其它实施例,都属于本发明所保护的范围。

本发明的说明书和权利要求书及上述附图说明中的术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排他的包含。本发明的说明书和权利要求书或上述附图中的术语“第一”、“第二”等是用于区别不同对象,而不是用于描述特定顺序。本发明的说明书和权利要求书或上述附图中的“上”“下”“左”“右”“前”“后”“侧”等方位词是针对提供的附图作相对的位置说明,并不是用于描述实际产品特定顺序。

请参阅图1-图3,sigma-delta ADC调制器包括电性连接的多级积分器100和延时DAC模块200,该延时DAC模块200包括以单元形式阵列排布的电流舵DAC2001,直接由sigma-delta ADC调制器的数字输出控制,这样单元的复用有利于提高了DAC的一致性。

请参阅图2,积分器100包括电性连接的阻容网络与运算放大器(OTA),具体地,积分器包括第一电阻R1、第一电容C1和运算放大器,第一电阻R1的第一端作为信号输入IN,第一电阻R1的第二端和第一电容C1的第一端均与运算放大器的第一端连接、第一电容C1的第二端与运算放大器的第三端连接作为信号输出OUT,运算放大器的第二端接地。由于该积分器中的运算放大器对一定频率的信号都有相应的相位移动作用,这样的信号反馈到输入端会使得运算放大电路不稳定甚至发生振荡,因此,第一电容C1予以一定的相位补偿,改变反馈网络相移,补偿运算放大器的相位滞后,提高积分器的准确性和稳定性。第一电阻R1可以让第一电容C1在充电的时候速度变慢,起到电压平缓和限流作用。

请参阅图4,本发明第一实施例提供sigma-delta ADC调制器,其积分器100包括折叠套筒式OTA、内部输入信号源(V

请继续参阅图4,次主极点决定模块12包括第一晶体管M1和第二晶体管M2,第一晶体管M1的栅极与第二晶体管M2的栅极连接,第一晶体管M1的源极和第二晶体管M2的源极均接地GND;第一调节模块13包括第一调节电容C

输入模块10包括第三晶体管M3、第四晶体管M4和第五晶体管M5,第三晶体管M3的源极与内部器件电压源VDD电性连接,第三晶体管M3的漏极与第四晶体管M4的源极、第五晶体管M5的源极连接,第四晶体管M4的栅极和第五晶体管M5的栅极分别连接到内部输入信号源(V

主极点决定模块11包括第六晶体管M6、第七晶体管M7、第八晶体管M8、第九晶体管M9、第十晶体管M10和第十一晶体管M11以及负载电容C

需要说明的是,第三晶体管M3、第四晶体管M4、第五晶体管M5、第六晶体管M6、第七晶体管M7、第十晶体管M10和第十一晶体管M11均为PMOS管,第一晶体管M1、第二晶体管M2、第八晶体管M8和第九晶体管M9均为NMOS管。

需要理解的是,第一调节模块13不仅只有第一调节电容C

电路结构确定后,折叠套筒式OTA的相位裕度PM基本确定,这时当主极点决定模块11输出的负载电容C

电路的主极点为

其中R

电路的次主极点为

其中C

结合上述(1)和(2),可知相位裕度PM=180-arctan(P

请参阅图5,本发明第二实施例提供优化电流舵DAC的sigma-delta ADC调制器包括电流舵DAC2001,该电流舵DAC2001包括共源共栅电路16,其内包括至少一个晶体管。具体地,本实施例电流舵DAC2001进一步包括第二电阻R2和第二调节模块15,共源共栅电路16包括第十二晶体管M12和第十三晶体管M13,第十二晶体管M12的源极与第二电阻R2的第一端连接,第二电阻R2的第二端接地,第十三晶体管M13的源极和第十二晶体管M12的漏极连接。

需要理解的是,第十三晶体管M13的漏极、第十二晶体管M12的栅极和第十三晶体管M13的栅极连接关系并不是本发明的技术点,这里并不作具体说明。因此,第十三晶体管M13的漏极、第十二晶体管M12的栅极和第十三晶体管M13的栅极均分别与sigma-delta ADC调制器的内部系统相应管脚连接即可。

第二调节模块15与该第二电阻R2并联,即第二调节模块15的第一端与第十二晶体管M12的源极连接,第二调节模块15的第二端接地。具体地,该第二调节模块15包括至少一个调节电容,调节电容的第一端与第十二晶体管M12的源极和第二电阻R2的第一端均连接,调节电容的第二端与第二电阻R2的第二端均接地形成并联连接。例如,本实施例第二调节模块15包括一个第三调节电容C

关于第二调节模块15与第二电阻R2构成的滤波网络抑制噪声的效果,其具体分析如下:

1)引入滤波网络前,

2)引入滤波网络后,

其中,

i

当信号频率S极小,此时有:

又因为,g

所以,

对比式(5)和(13),在引入滤波网络后,电流舵DAC的输出噪声电流的平方值由4KT·γ

请参阅图6,本发明第三实施例提供一种电子设备,包括存储器17和微处理器18,存储器17用于存储一个或多个程序,微处理器18执行一个或多个程序,以控制上述优化OTA的sigma-delta ADC调制器19。

需要说明的是,上述第一调节电容C

与现有技术相比,本发明的有益效果在于:

1、电流舵DAC包括共源共栅电路,其内包括至少一个晶体管,该电流舵DAC进一步包括第二电阻和第二调节模块,该共源共栅电路包括第十二晶体管,第十二晶体管的源极与第二电阻的第一端连接,第二电阻的第二端接地,第二调节模块与第二电阻并联。第二调节模块包括至少一个调节电容,且调节电容均与第二电阻并联。具体地,第二调节模块包括一个第三调节电容,第三调节电容的第一端与第十二晶体管的源极连接,第三调节电容的第二端接地。因此,第二调节模块与第二电阻构成滤波网络,提高电流舵DAC线性度,减少了电路的面积代价,也抑制了高频杂散信号和噪声的影响。另外,提供了较高的对地阻抗,优化了电流舵DAC对晶体管二级效应的抵抗。

2、一种电子设备,包括存储器和微处理器,所述存储器用于存储一个或多个程序,所述微处理器执行一个或多个程序,以控制上述优化电流舵DAC的sigma-delta ADC调制器。因此,所述电子设备也具有与上述的sigma-delta ADC调制器相同的有益效果,在此不再赘述。

以上所述的仅是本发明的实施方式,在此应当指出,对于本领域的普通技术人员来说,在不脱离本发明创造构思的前提下,还可以做出改进,但这些均属于本发明的保护范围。

- 一种优化电流舵DAC的sigma-delta ADC调制器及电子设备

- 一种优化OTA的sigma-delta ADC调制器及电子设备