显示基板和显示面板

文献发布时间:2023-06-19 11:08:20

技术领域

本公开涉及显示领域,尤其涉及一种显示基板和显示面板。

背景技术

在薄膜晶体管型液晶显示面板(TFT-LCD)的设计中,由于显示区周边的TFT器件所处的工艺环境与显示区中间处的TFT器件不同,因此,有可能导致显示不均匀的问题。为此,在实际中,在边框尺寸空间允许的情况下,在显示区的周围会设计一定数量的虚拟像素(Dummy Pixel)。

发明内容

本公开的实施例提供了一种显示基板,包括:衬底基板;设置在衬底基板上的显示区和显示区外围的周边区,在所述周边区中设置有虚拟像素单元和虚拟数据线,所述虚拟像素单元包括薄膜晶体管,所述薄膜晶体管包括第一电极和第二电极,所述第一电极为源极和漏极中的一者,所述第二电极为所述源极和漏极中的另一者,所述第一电极与虚拟数据线电连接,所述第二电极具有由第一断口间隔开的第一部分和第二部分。

在一些实施例中,所述虚拟像素单元还包括像素电极,所述第二电极的所述第二部分与所述像素电极电连接,所述薄膜晶体管还包括有源层和栅极,在同一薄膜晶体管中,所述栅极在衬底基板上的正投影与有源层在衬底基板上的正投影至少部分地重叠,且与所述第二电极的所述第一部分在衬底基板上的正投影至少部分地重叠。

在一些实施例中,在同一薄膜晶体管中,所述有源层在衬底基板上的正投影与所述第二电极的第一部分在衬底基板上的正投影至少部分地重叠,与所述第二电极的第二部分在衬底基板上的正投影不重叠,且所述第一断口在衬底基板上的正投影与所述有源层在衬底基板上的正投影不重叠,与所述栅极在衬底基板上的正投影也不重叠。

在一些实施例中,在同一薄膜晶体管中,所述有源层在衬底基板上的正投影与所述第二电极的第一部分在衬底基板上的正投影至少部分地重叠,且与所述第二电极的第二部分在衬底基板上的正投影至少部分地重叠,所述第一断口在衬底基板上的正投影落入所述有源层在衬底基板上的正投影及所述栅极在衬底基板上的正投影中。

在一些实施例中,在同一薄膜晶体管中,所述第二电极的第一部分靠近所述第一断口的边缘在衬底基板上的正投影与所述栅极在衬底基板上的正投影的一边缘平齐。

在一些实施例中,在同一薄膜晶体管中,所述栅极在衬底基板上的正投影完全覆盖所述第二电极的第一部分在衬底基板上的正投影。

在一些实施例中,在同一薄膜晶体管中,所述栅极在衬底基板上的正投影与所述第二电极的第二部分在衬底基板上的正投影部分地重叠。

在一些实施例中,所述第二电极还具有第三部分,所述第二部分和第三部分由第二断口间隔开,第一断口和第二断口中的每一个在衬底基板上的正投影与栅极在衬底基板上的正投影不重叠且与有源层在衬底基板上的正投影不重叠,第二电极的第一部分和第三部分中的至少一者在衬底基板上的正投影与栅极在衬底基板上的正投影至少部分地重叠且与有源层在衬底基板上的正投影也至少部分地重叠,所述第二电极的所述第二部分通过第一过孔结构与所述像素电极电连接。

在一些实施例中,所述显示基板还包括公共电极,其中,所述周边区中还设置有电极扩展层,所述电极扩展层与所述公共电极电连接,所述电极扩展层与所述第一电极、第二电极和虚拟数据线由相同材料同层布置,所述电极扩展层与虚拟数据线电连接。

在一些实施例中,同一虚拟数据线的两端均与所述电极扩展层电连接以形成经过所述同一虚拟数据线和电极扩展层的导电回路。

在一些实施例中,所述显示基板还包括公共电极和连接层,其中,所述周边区中还设置有电极扩展层,所述电极扩展层与所述公共电极电连接,所述连接层与所述像素电极由相同的材料制成且同层设置,所述连接层通过第二过孔结构与公共电极电连接,并通过第三过孔结构与所述电极扩展层电连接。

在一些实施例中,所述公共电极包括相互连接的第一公共电极延伸部和第二公共电极延伸部,所述第一公共电极延伸部的延伸方向和第二公共电极延伸部的延伸方向相互交叉,所述连接层在衬底基板上的正投影与第二公共电极延伸部在衬底基板上的正投影至少部分地重叠,所述第一公共电极延伸部在衬底基板上的正投影与像素电极在衬底基板上的正投影至少部分地交叠。

在一些实施例中,所述显示基板还包括公共电极和栅极线,其中,所述周边区中还设置有电极扩展层,所述电极扩展层与所述公共电极电连接,所述电极扩展层与所述第一电极、第二电极和虚拟数据线由相同材料同层布置,所述栅极线与所述栅极由相同的材料同层布置,所述栅极线在衬底基板上的正投影与所述电极扩展层在衬底基板上的正投影具有重叠区域。

在一些实施例中,所述电极扩展层包括镂空区,所述镂空区在衬底基板上的正投影与所述栅极线在衬底基板上的正投影至少部分地重叠。

本公开的实施例还提供了一种显示面板,包括如上述任一实施例所述的显示基板。

附图说明

为了更清楚地说明本公开文本的实施例的技术方案,下面将对实施例的附图进行简要说明,应当知道,以下描述的附图仅仅涉及本公开文本的一些实施例,而非对本公开文本的限制,其中:

图1A示出根据本公开的实施例的一种显示基板的示意图;

图1B示出图1A中的虚线框P中的局部示意图;

图2示出根据本公开的实施例的显示基板中的显示区的薄膜晶体管的结构示意图;

图3示出根据本公开的一些实施例的显示基板中的周边区的虚拟薄膜晶体管的结构示意图;

图4示出根据本公开的另一些实施例的显示基板中的周边区的虚拟薄膜晶体管的结构示意图;

图5示出根据本公开的又一些实施例的显示基板中的周边区的虚拟薄膜晶体管的结构示意图;

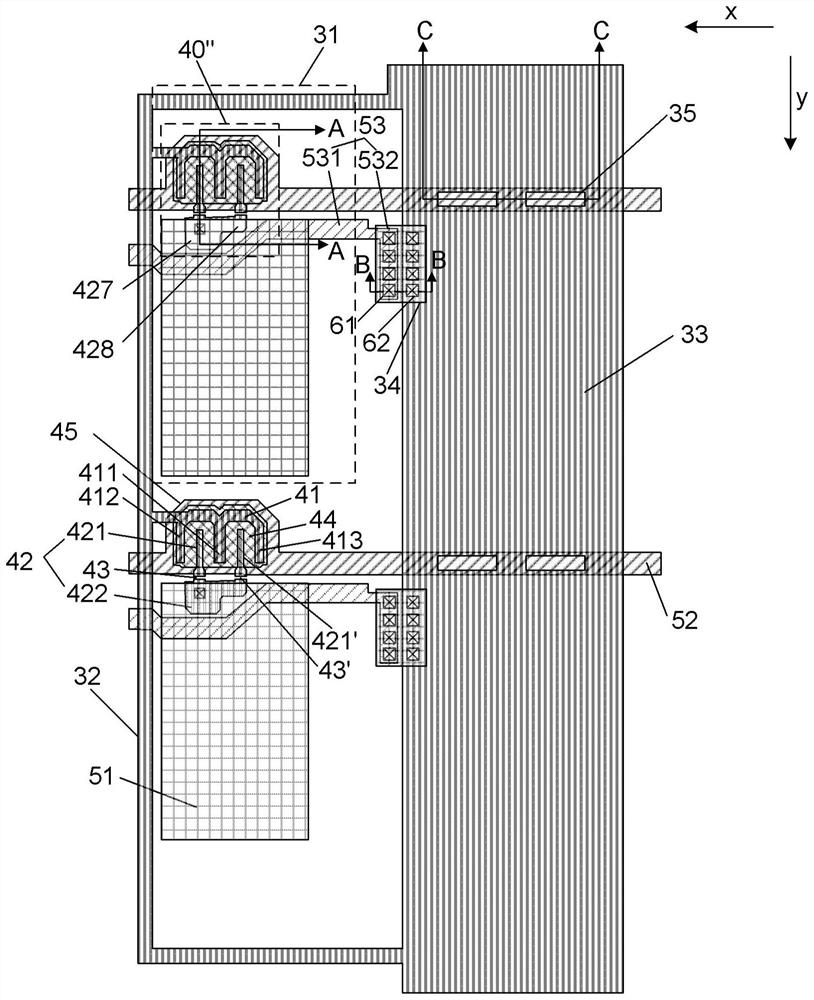

图6示出根据本公开的再一些实施例的显示基板中的周边区的局部结构示意图;

图7示出图6中沿着线AA截得的剖视图;

图8示出图6中沿着线BB截得的剖视图;以及

图9示出图6中沿着线CC截得的剖视图。

具体实施方式

为更清楚地阐述本公开的目的、技术方案及优点,以下将结合附图对本公开的实施例进行详细的说明。应当理解,下文对于实施例的描述旨在对本公开的总体构思进行解释和说明,而不应当理解为是对本公开的限制。在说明书和附图中,相同或相似的附图标记指代相同或相似的部件或构件。为了清晰起见,附图不一定按比例绘制,并且附图中可能省略了一些公知部件和结构。

除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。措词“一”或“一个”不排除多个。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”、“顶”或“底”等等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。当诸如层、膜、区域或衬底基板之类的元件被称作位于另一元件“上”或“下”时,该元件可以“直接”位于另一元件“上”或“下”,或者可以存在中间元件。

本公开的实施例提供了一种显示基板100。图1A示出了该显示基板100的示意性的平面图。在图1A中示出了显示区20和周边区30。图1B示出了图1A中右下虚线框中的局部的细节,在图1B中,为了清楚起见,显示区20和周边区30之间的边界用点划线表示。该显示基板100包括:衬底基板10(可参见图7至图9的剖视图)以及设置在衬底基板10上的显示区20和周边区30。该周边区30设置在显示区20的外围。显示区20用于显示图像,例如可以设置有多个像素单元21以及数据线、栅极线等结构。周边区30则不用于显示图像,而例如可用于布设走线等。在所述周边区30中可设置有虚拟像素单元31和虚拟数据线32。虚拟像素单元31和虚拟数据线32在结构上与显示区20中的像素单元21和数据线22相似,这有助于为显示区20中靠近周边区30的像素单元21提供与位于显示区20中远离周边区30的像素单元21相类似的环境。所述虚拟像素单元31可以包括薄膜晶体管40。

由于图幅所限,在图1A和图1B中均没有示出显示区20中的薄膜晶体管40’和周边区30中的薄膜晶体管40的具体结构。它们的具体结构的示例可参见图2至图6。

如图3至图5所示,所述薄膜晶体管40可包括第一电极41和第二电极42,所述第一电极41与虚拟数据线32电连接,所述第二电极42具有由断口(为了与后续实施例区分,在此可称为第一断口43)间隔开的第一部分421和第二部分422。在下面的示例中,以所述第一电极41为源极且第二电极42为漏极的情形为例。然而,本领域技术人员应当理解,本公开的实施例不限于此,例如,第一电极41也可以为漏极而第二电极42可以为源极。除去第一电极41和第二电极42(第一电极41和第二电极42中一者为源极,另一者为漏极)之外,所述薄膜晶体管40还可包括有源层44和栅极45,栅极45与栅极线52电连接。

在本公开的实施例中,虚拟像素单元31中的薄膜晶体管40的源极或漏极是通过断口断开的。在这种情况下,即使虚拟数据线32输入信号,薄膜晶体管40也无法将虚拟数据线32与像素电极51连通,因此,可以降低与薄膜晶体管40的栅极45电连接的栅极线52的负载。这既可以降低虚拟像素单元31所造成的功耗,又有利于提高亮度的均匀性。如前所述,虚拟像素单元31和虚拟数据线32是为了保证显示区20中靠近周边区30的像素单元21具有与显示区20中远离周边区30的像素单元21相似的工艺环境,而不需要实现具体的图像显示功能。因此,在薄膜晶体管40的源极或漏极是通过断口(如第一断口43)断开的情况下,虚拟数据线32与虚拟像素单元31也断开连接,这样,虚拟数据线32也可以被用于实现一些独立的功能,比如说传导测试信号,连接公共电极等等。在本公开的实施例中,栅极线52可以与对应的薄膜晶体管40的栅极45电连接,而且,栅极线52在衬底基板10上的正投影还可以与虚拟数据线32在衬底基板10上的正投影彼此交叉。

而且,薄膜晶体管40的源极或漏极的断开仅仅通过断口(如第一断口43)来实现,对于虚拟像素单元31的整体层结构布局的影响并不大,这可以使虚拟像素单元31在层结构上与显示区20中的像素单元21具有很高的相似度,从而到达为显示区20中的各个像素单元21提供相似的工艺环境的目的。这对于保持显示区20的显示亮度的均一性是有益的。

图2示出了显示区20中的像素单元21中的薄膜晶体管40’的示例。如图所示,在该薄膜晶体管40’中,第一电极41’与数据线22电连接,第二电极42’是完整的,并不包括断口。与之对照,图3至图5分别示出了周边区30中的虚拟像素单元31中的薄膜晶体管40的三种示例。在这三种示例中,第一电极41均与虚拟数据线32电连接,但第一断口43的位置不同。在图3所示的示例和图4所示的示例中,第一断口43在衬底基板上的正投影与栅极45在衬底基板10上的正投影不重叠且与有源层44在衬底基板10上的正投影不重叠。但在图3所示的示例中,第二电极42的第一部分421在衬底基板10上的正投影的一部分落入栅极45在衬底基板10上的正投影中,而另一部分则延伸到栅极45在衬底基板10上的正投影之外。而在图4所示的示例中,第二电极42的第一部分421在衬底基板10上的正投影完全落入栅极45在衬底基板10上的正投影中。在图5所示的示例中,第一断口43在衬底基板10上的正投影落入到栅极45在衬底基板10上的正投影及有源层44在衬底基板10上的正投影中,第二电极42的第二部分422的一部分在衬底基板10上的正投影落入到了栅极45在衬底基板10上的正投影及有源层44在衬底基板10上的正投影中。

在本公开的实施例中,当第一断口43在衬底基板10上的正投影落入到栅极45在衬底基板10上的正投影及有源层44在衬底基板10上的正投影中时,第二电极42的第二部分422的一部分可能会与栅极45及有源层44存在一定的交叠。这种情况与第一断口43在衬底基板10上的正投影落在栅极45及有源层44在衬底基板10上的正投影之外的情况相比,可能使栅极线52的负载更大。因此,第一断口43在衬底基板10上的正投影落在栅极45及有源层44在衬底基板10上的正投影之外的示例对比之下更具优势。另外,期望第一断口43的宽度尽可能窄,这样可以使得虚拟像素单元31的结构与显示区20中的像素单元21的结构尽可能相似。这对于减小负载和提高显示均匀性是有帮助的。

在一些实施例中,在同一薄膜晶体管中,如图3至图6所示,所述栅极45在衬底基板10上的正投影与有源层44在衬底基板10上的正投影至少部分地(部分或全部)重叠,与所述第二电极42的所述第一部分421在衬底基板10上的正投影也至少部分地(部分或全部)重叠。

而在另一些实施例中,在同一薄膜晶体管中,如图3和图4所示,所述有源层44在衬底基板10上的正投影与所述第二电极42的第一部分421在衬底基板10上的正投影至少部分地(部分或全部)重叠,与所述第二电极42的第二部分422在衬底基板10上的正投影不重叠。

在一些实施例中,在同一薄膜晶体管中,如图5所示,所述有源层44在衬底基板10上的正投影与所述第二电极42的第一部分421在衬底基板10上的正投影至少部分地(部分或全部)重叠,且与所述第二电极42的第二部分422在衬底基板10上的正投影至少部分地(部分或全部)重叠。

在一些实施例中,在同一薄膜晶体管中,如图3至图6所示,所述栅极45在衬底基板10上的正投影与所述第二电极42的第一部分421在衬底基板10上的正投影至少部分地(部分或全部)重叠。

在一些实施例中,在同一薄膜晶体管中,如图4所示,所述第二电极42的第一部分421靠近所述第一断口43的边缘431在衬底基板上的正投影与所述栅极45在衬底基板10上的正投影的一边缘451平齐。这种方式既可以使第二电极42的第二部分422不与栅极45交叠,又能够尽可能地减小第一断口43的宽度。

在一些实施例中,在同一薄膜晶体管中,如图4和图5所示,所述栅极45在衬底基板10上的正投影完全覆盖所述第二电极42的第一部分421在衬底基板10上的正投影。这可以避免第二电极42的第一部分421过度地延伸。

在另一些实施例中,在同一薄膜晶体管中,如图5所示,所述栅极45在衬底基板10上的正投影与所述第二电极42的第二部分422在衬底基板10上的正投影部分地重叠。

在本公开的一些实施例中,在同一薄膜晶体管中,栅极45在衬底基板10上的正投影覆盖有源层44在衬底基板10上的正投影。然而,本公开的实施例不限于此。

图6给出了根据本公开的再一些实施例的显示基板中的周边区30的局部结构示意图。其中示出了两个虚拟像素单元31和一条虚拟数据线32。在前述图3至图5所示的示例中,仅仅示出了一种薄膜晶体管40的结构。然而,在本公开的实施例中,在一个虚拟像素单元31中不仅可以仅包括一个薄膜晶体管,还可以包括多个薄膜晶体管。而同一薄膜晶体管还可以有更为复杂的结构。在图6所示的示例中,所述虚拟像素单元31中的薄膜晶体管40”也可包括栅极45、有源层44、第一电极41和第二电极42。在该薄膜晶体管40”中设有两个断口,即第一断口43和第二断口43’。第一电极41与虚拟数据线32电连接。第二电极42具有第一部分421、第二部分422和第三部分421’。第一部分421与第二部分422由第一断口43间隔开,第二部分422和第三部分421’由第二断口43’间隔开。在同一薄膜晶体管40”中,第三部分421’例如可以比第一部分421更远离与第一电极41所连接的虚拟数据线32。在一些实施例中,第二电极42的第三部分421’的延伸方向可以与第二电极42的第一部分421的延伸方向平行。

在一些实施例中,第一断口43在衬底基板上的正投影与栅极45在衬底基板10上的正投影不重叠且与有源层44在衬底基板10上的正投影不重叠。类似地,在一些实施例中,第二断口43’在衬底基板上的正投影与栅极45在衬底基板10上的正投影也不重叠且与有源层44在衬底基板10上的正投影也不重叠。而第二电极42的第一部分421和第三部分421’中的至少一者在衬底基板上的正投影可以与栅极45在衬底基板10上的正投影具有重叠部分且与有源层44在衬底基板10上的正投影也具有重叠部分。

在一些实施例中,第二电极42的第二部分422可包括与第一断口43邻接的第一段427和与第二断口43’邻接的第二段428。在一些实施例中,在第二电极42的第一部分421的延伸方向上(例如如图6中的y方向),第一段427的宽度大于第二段428的宽度,从而第二电极42的第二部分422在衬底基板10上的投影整体成“L”形。第一段427具有较大的宽度,利于在第一段427中设置过孔结构以与其他导电层(例如像素电极51)电连接。

在一些实施例中,薄膜晶体管40”中的第一电极41可具有相互电连接的第一延伸部411、第二延伸部412和第三延伸部413,这三个延伸部的延伸方向可以与第二电极42的第一部分421或第三部分421’的延伸方向平行。如图6所示,第一延伸部411可位于第二电极42的第一部分421和第三部分421’之间,第二延伸部412可位于第二电极42的第一部分421的远离第二电极42的第三部分421’的一侧,第三延伸部413可位于第二电极42的第三部分421’的远离第二电极42的第一部分421的一侧。在一些实施例中,如图6所示,虚拟像素单元31还可以包括像素电极51,所述第二电极42的所述第二部分422可与所述像素电极51电连接。上述这种薄膜晶体管40”的结构,相比于如图3所示的薄膜晶体管结构,可以提高栅极线的负载能力。

在本公开的实施例中,所述第一断口43和第二断口43’的宽度例如可为2微米至5微米。

图7是沿着图6中的线AA截得的剖视图。从图7中可以更清楚地看出薄膜晶体管40”的膜层结构。如图7所示,显示基板100可以包括第一绝缘层71和第二绝缘层72。第一绝缘层71,例如栅极绝缘层,位于所述栅极45和有源层44之间。第二绝缘层72,例如平坦化层或层间介质层,位于像素电极51所在层与薄膜晶体管40之间。作为示例,第一电极41和第二电极42的第一部分421、第二部分422和第三部分421’可以由相同材料(例如钛铝等金属或合金材料)制成并布置在同一层。第一断口43将第二电极42的第一部分421和第二部分422分隔开。有源层44位于第一电极41及第二电极42所在层和第一绝缘层71之间。像素电极51例如可以通过第一过孔结构511与第二电极42的第二部分422电连接。第一过孔结构511可以通过在第二绝缘层72中形成穿孔后在该穿孔中涂覆导电层来形成。如图7所示,第一过孔结构511中的导电层(例如金属层)可以与像素电极51由相同材料制成且同层设置。第一过孔结构511可以穿透第二绝缘层72与第二电极42的第二部分422相接触。从图6中可以看出,显示基板100还可以包括公共电极53。公共电极53可以与像素电极51一起为像素单元施加必要的电压以实现显示功能。在一些实施例中,周边区30中还设置有电极扩展层33,所述电极扩展层33与所述公共电极53电连接。该电极扩展层33可以用于增加公共电极53的面积以提高信号的稳定性。电极扩展层33例如可以布置成大片的导电层的形式,如图6所示。在一些实施例中,所述电极扩展层33可以与所述第一电极41、第二电极42和虚拟数据线43由相同材料同层布置,以简化工艺。

在一些实施例中,还可以设置连接层34以方便公共电极53与电极扩展层33的电连接。所述连接层34与所述像素电极51可以由相同的材料制成且同层设置,所述连接层34通过第二过孔结构61与公共电极53电连接,并通过第三过孔结构62与所述电极扩展层33电连接。第二过孔结构61可以通过形成穿过第一绝缘层71和第二绝缘层72的贯通孔后在该贯通孔中涂覆导电层(例如金属层)形成。第三过孔结构62可以通过形成穿过第二绝缘层72的穿孔后在该穿孔中涂覆导电层形成。从图8可以清楚地看出,第二过孔结构61中的导电层可以与连接层34由相同材料制成且同层设置。第二过孔结构61可以穿透第一绝缘层71和第二绝缘层72以与公共电极53相接触。类似地,第三过孔结构62可以与连接层34由相同材料制成且同层设置。第三过孔结构62可以穿透第二绝缘层72以与电极扩展层33相接触。然而,本公开的实施例不限于此,例如,公共电极53与电极扩展层33也可以不通过连接层34而直接电连接。

在一些实施例中,如图6所示,公共电极53可包括相互连接的第一公共电极延伸部531和第二公共电极延伸部532。其中,第二过孔结构61形成于该第二公共电极延伸部532处,用于将第二公共电极延伸部532与连接层34电连接。第二公共电极延伸部532可以设置成沿着电极扩展层33的边缘延伸,以便更好地布置第二过孔结构61,尤其是设置有多个第二过孔结构61时更为有利。而公共电极53的第一公共电极延伸部531可以从第二公共电极延伸部532与栅极线52大体并排地延伸。这不意味着公共电极53的第一公共电极延伸部531的延伸方向与栅极线52的延伸方向必定平行,例如,第一公共电极延伸部531可以为了绕开晶体管等结构而曲折地延伸(如图6所示)。例如,第一公共电极延伸部531可以与虚拟数据线32相交叉。作为示例,可以将第一公共电极延伸部531从第二公共电极延伸部532起的总体延伸方向定义成第一方向(如图6中的x方向),而将第二公共电极延伸部532的延伸方向定义成第二方向(如图6中的y方向)。在图6所示的示例中,第一方向和第二方向成大致九十度,公共电极53的第一公共电极延伸部531和第二公共电极延伸部532构成了一个L形结构。这种结构的设计有利于公共电极53与连接层34的电连接。然而,本公开的实施例不限于此,例如,第一公共电极延伸部531的总体延伸方向与第二公共电极延伸部532的延伸方向可以是不垂直的。

在一些实施例中,如图6所示,连接层34在衬底基板10上的正投影与第二公共电极延伸部532在衬底基板10上的正投影至少部分地重叠,例如,连接层34在衬底基板10上的正投影完全覆盖第二公共电极延伸部532在衬底基板10上的正投影。这有利于第二过孔结构61的布设。而第一公共电极延伸部532在衬底基板10上的正投影可以与像素电极51在衬底基板10上的正投影至少部分地交叠。在一些实施例中,所述第一公共电极延伸部531在衬底基板10上的正投影与所述虚拟数据线32在衬底基板10上的正投影相互交叉。

在一些实施例中,所述电极扩展层33与虚拟数据线32电连接。这使得虚拟数据线32也可以与公共电极53电连接,进一步增加公共电极53的实际面积,提高信号的稳定性。

如图6所示,在一些实施例中,同一虚拟数据线32的两端可均与所述电极扩展层33电连接以形成经过所述同一虚拟数据线32和电极扩展层33的导电回路。这种结构可以使得公共电极53上的电位分布更加均匀。例如,如果虚拟数据线32是断开的,不能与电极扩展层33构成导电回路,那么在虚拟数据线32的断口的两边可能会有比较大的电位差。而同一虚拟数据线32和电极扩展层33构成导电回路有助于尽可能地削弱这种过大的电位差异,这对于实现显示区20中的显示像素的亮度均匀性是有益的。

在一些实施例中,如图6至图8所示,第一绝缘层71可位于所述公共电极53的远离衬底基板10的一侧和所述电极扩展层33朝向衬底基板10的一侧;第二绝缘层72可位于所述电极扩展层33和所述连接层34之间且位于所述有源层44的远离衬底基板10的一侧。

在一些实施例中,如图6所示,显示基板100上设有栅极线52,所述电极扩展层33与所述第一电极42、第二电极42和虚拟数据线32由相同材料同层布置,所述栅极线52与所述栅极45由相同的材料同层布置。所述栅极线52在衬底基板10上的正投影与所述电极扩展层33在衬底基板10上的正投影具有重叠区域。电极扩展层33与栅极线52交叠,有利于显示基板100上的布线,且也可以使电极扩展层33具有尽可能大的面积来提高信号稳定性。

在一些实施例中,如图9所示,电极扩展层33可以包括镂空区35。镂空区35在衬底基板10上的正投影与所述栅极线52在衬底基板10上的正投影至少部分地(部分或全部)重叠。在镂空区35处,电极扩展层33的导电层部分被去除。在栅极线52与电极扩展层33交叠处设置一个或更多个镂空区35,这可以减小电极扩展层33(例如第一电极41和第二电极42所在层)与栅极线52所在层之间的寄生电容,避免由于电极扩展层33所导致的该导电层的面积增加来明显增大寄生电容,从而防止由于寄生电容的差异导致亮度不均匀。

本领域技术人员应当理解,尽管图6中仅示出了两个虚拟像素单元31,但是本公开的实施例不限于此,显示基板100上还可以包括更多个虚拟像素单元。

本公开的实施例还提供了一种显示面板,该显示面板可以包括根据上述任一实施例所述的显示基板100。根据本公开的实施例的显示基板及显示面板,不仅可以用于薄膜晶体管型液晶显示装置,还可以用于诸如有机发光二极管(OLED)等其他类型的显示装置。本公开的实施例中的显示面板例如可以是薄膜晶体管型液晶显示面板,也可以是如有机发光二极管(OLED)显示面板等本领域已知的任何其他类型的显示面板。需要说明的是,本公开的实施例中的显示装置可以为:电子纸、手机、平板电脑、电视机、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

在本公开中所涉及的“同层设置”是指所涉及的层在同一工艺步骤中同时形成,而并不意味着这些层在横截面视图中必然具有同样的厚度或高度。利用“同层设置”这样的设计,可以尽可能地简化显示基板及显示面板的制作工艺。

在本公开的实施例中的各个导电层可以由导电金属制成,也可以由非金属导电材料制成。

虽然结合附图对本公开进行了说明,但是附图中公开的实施例旨在对本公开的实施例进行示例性说明,而不能理解为对本公开的一种限制。附图中的尺寸比例仅仅是示意性的,并不能理解为对本公开的限制。

上述实施例仅例示性的说明了本公开的原理及构造,而非用于限制本公开,本领域的技术人员应明白,在不偏离本公开的总体构思的情况下,对本公开所作的任何改变和改进都在本公开的范围内。本公开的保护范围,应如本申请的权利要求书所界定的范围为准。

- 显示面板用基板、具有该基板的显示面板、显示面板用基板的制造方法和显示面板的制造方法

- 显示面板用的基板、显示面板、显示面板用的基板的制造方法以及显示面板的制造方法